# HEWLETT-PACKARD JOURNAL

**APRIL 1987**

© Copr. 1949-1998 Hewlett-Packard Co.

# HEWLETT-PACKARD JOURNAL

April 1987 Volume 38 . Number 4

#### Articles

4 Digital Signal Generator Combines Digital and Analog Worlds, by Uwe Neumann, Michael Vogt, Friedhelm Brilhaus, and Frank Husfeld With an arbitrary waveform generator option, it can generate synchronous digital and analog outputs.

12 User Interface and Software Architecture for a Data and Arbitrary Waveform Generator, by Ulrich Hakenjos, Wolfgang Srok, and Rüdiger Kreiser Timing diagrams and arbitrary waveforms are easily created by means of a powerful graphic editor.

A Planning Solution for the Semiconductor Industry, by Edward L. Wilson, Kelly A. Sznaider, and Clemen Jue Semiconductor manufacturing, with no work orders, an inverse part structure, and fluctuating yields, needs a special planning tool.

#### Research Reports

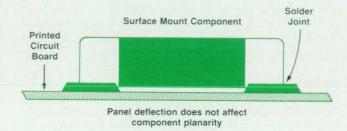

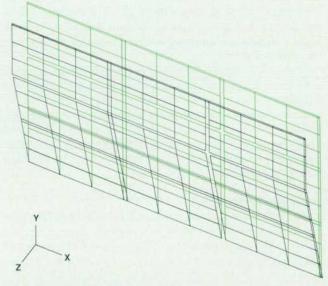

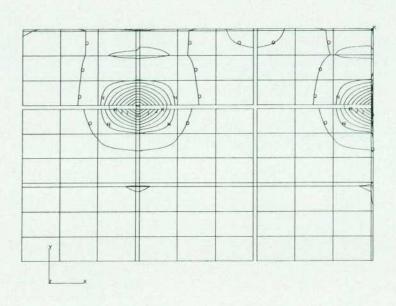

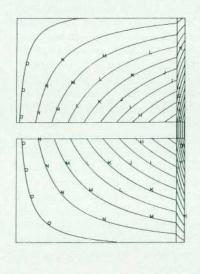

29 A Study of Panel Deflection of Partially Routed Printed Circuit Boards, by George E. Barrett and John H. Lau Finite element analysis shows that the deflection will not exceed the maximum allowable.

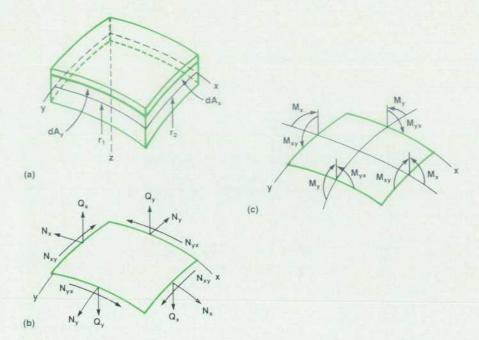

33 Deflections, Forces, and Moments of a Printed Circuit Board

35 Reliability Theory Applied to Software Testing, by H. Dean Drake and Duane E. Wolting A modified execution-time theory makes failure rates in testing useful for predicting postrelease reliability.

39 Appendix: Derivation of the Software Reliability Model

#### Departments

- 3 In this Issue

- 3 What's Ahead

- 27 Authors

- 40 Reader Forum

Editor, Richard P. Dolan • Associate Editor, Business Manager, Kenneth A. Shaw • Assistant Editor, Nancy R. Teater • Art Director, Photographer, Arvid A. Danielson Support Supervisor, Susan E. Wright • Administrative Services, Typography, Anne S. LoPresti • European Production Supervisor, Michael Zandwijken

#### In this Issue

Like other instruments, signal generators are getting more and more built-in intelligence. One result is that some are beginning to offer more than the usual sine, square, triangle, and pulse waveforms. Arbitrary waveform generators that will reproduce whatever waveform you program into them are now commercially available. This means that testing can be more realistic, using signals that simulate all of the conditions a device is likely to encounter in normal operation. The HP 8175A Digital Signal Generator offers arbitrary waveform generation as an optional capability of a digital data generator. Depending on how you configure it, it can produce 24-channel parallel data

patterns or two-channel serial data for testing digital hardware, two arbitrary analog waveforms for testing analog circuits, or a combination of digital and analog waveforms for testing such things as analog-to-digital and digital-to-analog converters. Its outputs can be independent or synchronized. In the articles on pages 4 and 12, the HP 8175A's designers tell us how it works. Noteworthy is their program-controlled looping scheme that makes a 1K-bit memory look much deeper. They use variable timing to conserve data memory, and they've been careful to make the arbitrary waveform generator easy to program—you can enter a series of levels or a mathematical formula, or point with a cursor on the display.

HP's Semiconductor Productivity Network (SPN) was an early approach to computer-integrated manufacturing for the semiconductor manufacturing industry. SPN consists of several software modules, each controlling or monitoring a particular aspect of the semiconductor manufacturing process. Recently, HP decided to withdraw from this business, to support only the current SPN users, and not to work on further enhancements. However, one development effort was allowed to proceed, so that current SPN users could have a complete system. The final SPN module, PL-10, is a master planning tool. In the article on page 21, PL-10's designers describe its operation and explain why semiconductor manufacturing needs a special planning system.

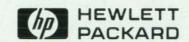

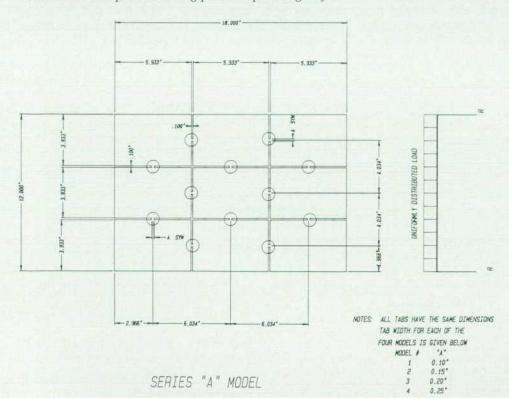

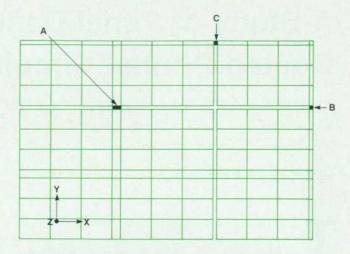

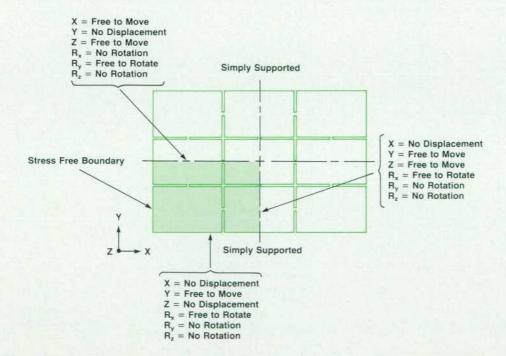

Small printed circuit boards are often manufactured several at a time on large boards called subpanels. At a certain point in the manufacturing process, a router path is cut around each board, leaving only small tabs holding the subpanel together. This, of course, reduces the rigidity of the panel. To see whether a partially routed panel would deflect enough during subsequent handling to affect the components and solder joints on it, HP Laboratories researchers used finite element analysis (cover photo). They report their results on page 29. Their conclusion? The panel deflection will not exceed the maximum allowable, so costly modifications of the manufacturing process are not needed.

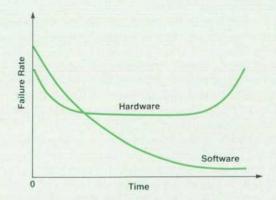

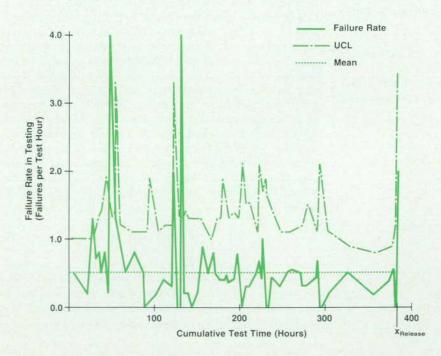

Conventional reliability theory often describes hardware reliability in terms of a failure rate—the percentage of the units in service that can be expected to fail in a given period of time. For hardware, the rate is usually higher for very new or very old equipment, and lower in between. Application of the failure rate concept to software is in its early stages. In the report on page 35, two HP engineers tell how they have modified an existing software failure rate theory to include the testing process, so that the failure rate observed at the end of testing can be used to predict the in-service failure rate after release of the product.

-R. P. Dolan

#### What's Ahead

The development of ME Series 5/10, a mechanical engineering CAD product for HP's Design Center workstations, is the primary subject of the May issue. In addition, a short report discusses the potential use of ac power lines for data communications in buildings.

## Digital Signal Generator Combines Digital and Analog Worlds

This new generator provides 24 parallel or two serial data channels, two arbitrary waveform analog channels, or a combination of digital and analog outputs.

by Uwe Neumann, Michael Vogt, Friedhelm Brilhaus, and Frank Husfeld

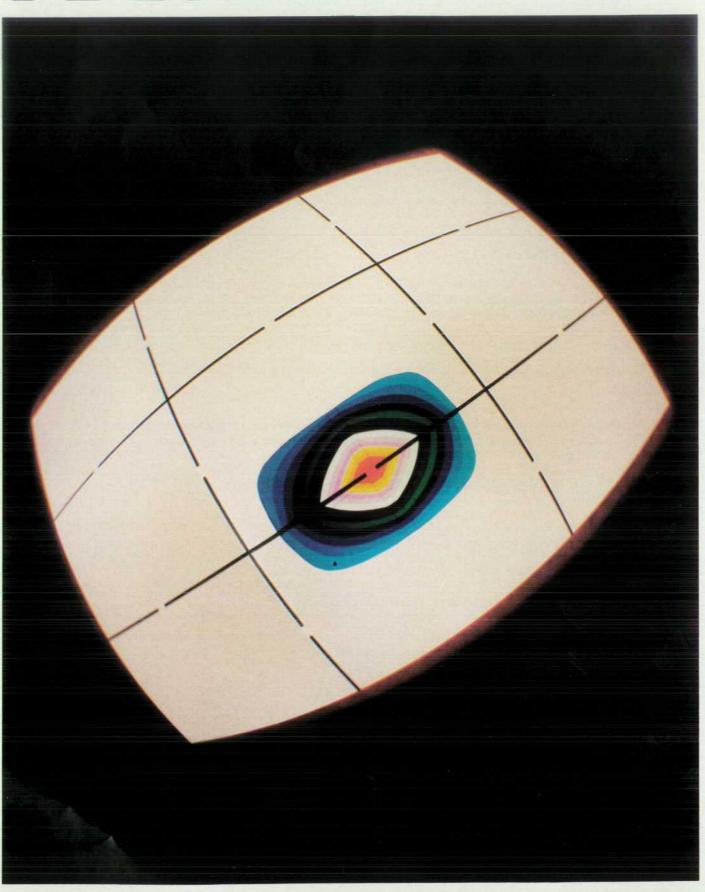

HE HP 8175A DIGITAL SIGNAL GENERATOR, Fig. 1, is capable of providing up to three different types of output stimuli depending on the selected configuration. It can be configured by simple keystroke as either a 24-channel parallel data generator, a two-channel serial data generator, or a two-channel arbitrarily programmable waveform generator. A combination of two types of output stimuli is also possible. For instance, a digital data sequence can be generated while the analog equivalent or a different analog function is generated by the analog part of the machine.

A large number of different applications can be supported by this type of stimulus capability. The HP 8175A can generate digital patterns for at-speed functional testing, simulation, and stimulation of digital hardware, and analog functions for medical applications (e.g., electrocardiographic and plethysmographic signals) and mechanical applications (e.g., ignition-point measurements in the au-

tomobile industry). Simultaneous generation of arbitrary waveforms and digital patterns bridges the gap between the analog and digital worlds, and is very useful for testing digital-to-analog and analog-to-digital converters, because the analog and the digital signals are available at different outputs of the same source. Add a comparator, and a go/nogo test can be performed. Testing of mixed ICs or circuits that include both analog and digital components is very easy, since it is possible to generate independent synchronous analog and digital data streams. For example, to test a programmable filter, the data patterns can control the filter's Q factor and center or corner frequency, while the analog output stimulates the IC.

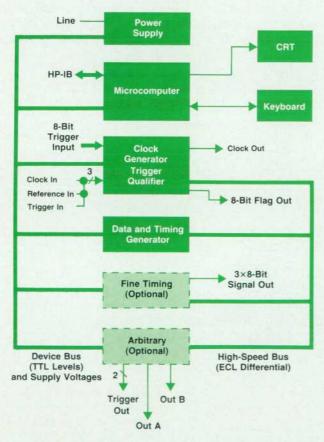

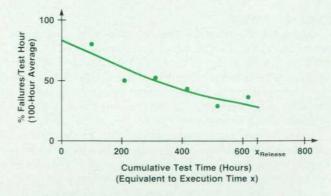

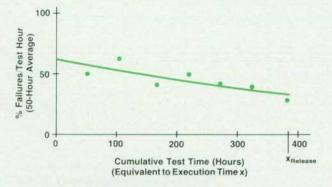

Fig. 2 shows the HP 8175A system. Fig. 3 is a block diagram of the HP 8175A.

#### Parallel Data Generator

Data patterns can be generated on 24 channels, each 1K

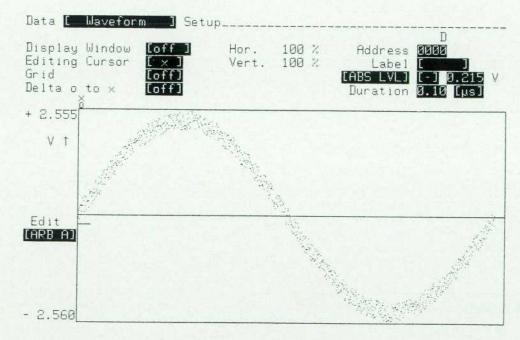

Fig. 1. The HP 8175A Digital Signal Generator can be used as a 24-channel, 50-Mbit/s parallel data generator, a two-channel, 100-Mbit/s serial data generator, a two-channel arbitrarily programmable waveform generator (display shown), or a combination data and waveform generator.

bits deep, at 50 Mbits/s. Two machines can work together in a master/slave configuration to generate up to 48 channels. To overcome the depth limitation, two enhancements help the customer minimize the number of memory locations used. One is virtual memory expansion—a pattern sequence that is to be used repeatedly needs to be stored only once in the machine and can then be included in the output data stream as often as required. The other is programmable pattern duration—each pattern consists of data and duration parameters, so sequences of fast bursts and long steady-state signals can be generated by using only a few memory locations.

Interaction with the device under test is facilitated by a trigger input, which can indicate start, stop, continue cycling, enable or disable outputs, or branch to other data cycles. Branching can be implemented, for example, when a DUT requires initialization routines. The trigger pins can be assigned to monitor logic states at various points of the DUT.

A fine-timing option provides a programmable delay on four channels. The delay can range from 20 ns to 40 ns with 100-ps resolution.

The HP 8175A Digital Signal Generator and an HP 163x Logic Analyzer form a versatile stimulus-response system for efficient digital testing.

#### Serial Data Generator

Internal serializing of eight parallel channels generates a data stream with 8K-bit depth and a bit rate of 100 Mbits/s on two channels, and a clock signal. The switch from parallel mode to serial configuration is done by a single keystroke. The same interaction features are available as for the parallel data generator.

#### Arbitrary Waveform Generator

If Option 002 is installed, the digital signal generator acts as an analog stimulus. The HP 8175A delivers an analog waveform on two fully synchronized channels with 10-bit amplitude resolution and up to 1024 data points. Virtual memory expansion and programmable pattern duration are also available to save internal memory locations, and the same DUT interaction capability is available as for the parallel data generator. The two channels can also be operated independently.

The maximum sample update rate of 50 MHz, the large amplitude range of up to 16V into  $50\Omega$ , and the minimum resolution of 0.2 mV meet the needs of a wide range of applications in electrical, medical, and mechanical environments. Other useful features include dc offset, settling times less than 20 ns, and synchronized parallel data channels if only one analog channel is used.

Different methods of entering the arbitrary waveform to be generated are possible. Waveforms can be generated by entry of a series of levels, by entry of a mathematical formula, or by pointing with the cursor on the CRT screen. More information on entering waveforms is given in the article on page 12.

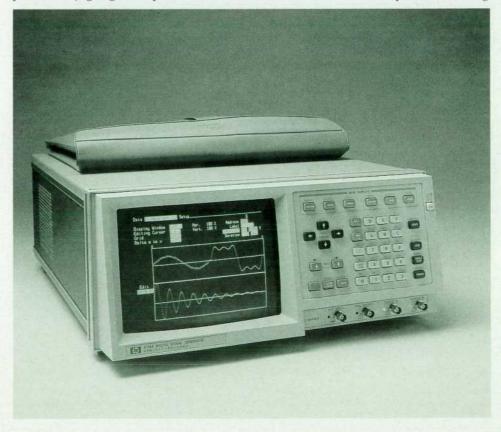

#### Pods and Accessories

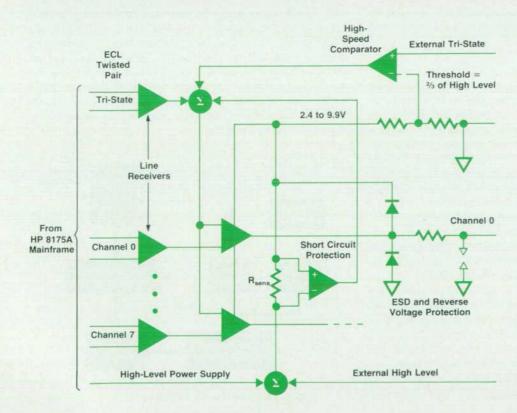

One trigger pod and three output pods are available to serve all interconnections to the device under test. The function of the HP 15461A ECL Pod, the HP 15462A TTL/CMOS Pod, or the fixed-level HP 15464A TTL Pod is to translate the internal signals of the HP 8175A into signals used by standard IC families like 10K, 10KH, or 100K ECL, 54/74 TTL, or 4000 CMOS. Each pod provides 8 of the 24 channels of the HP 8175A. The eight outputs of a pod can

Fig. 2. The HP 8175A system includes a trigger pod, three kinds of data or flag pods (ECL, TTL/CMOS, TTL), cables, connectors, and various probe accessories.

be disabled, which for the TTL and TTL/CMOS pods means the outputs have a high impedance (tri-state outputs) and for the ECL pod means that the outputs are low to allow wired-OR connections in the device under test. In the TTL/CMOS pod the high level can be programmed by the HP 8175A from 2.4V to 9.9V. This provides flexibility for CMOS ICs, which operate at nominal supply voltages from 2V in low-power circuits up to 10V. An additional feature of the TTL/CMOS pod is direct control of the high level by the device under test. This requires that the external high-level control input of the pod be connected to the desired high-level voltage (Fig. 4).

The outputs of a pod are connected by coaxial cables to connectors of the type used on the HP 8182A Data Analyzer.¹ For this connector family a large number of accessories like plug-ins, crimps, and BNC or SMB plugs are available. The HP 8175A transmits its internal ECL signals via twisted-pair cables in the differential mode to the pods. Here, ECL differential line receivers amplify the signal either to ECL levels for the ECL and TTL/CMOS pods or to TTL levels for the fixed-level TTL pod. In the TTL pod, special TTL line drivers amplify the signal before it is connected to the outputs. In the TTL/CMOS pod, discrete output amplifiers are used to get the desired pulse performance at the outputs. All pod inputs and outputs are protected against electrostatic discharge (ESD), reverse voltage, and short circuits.

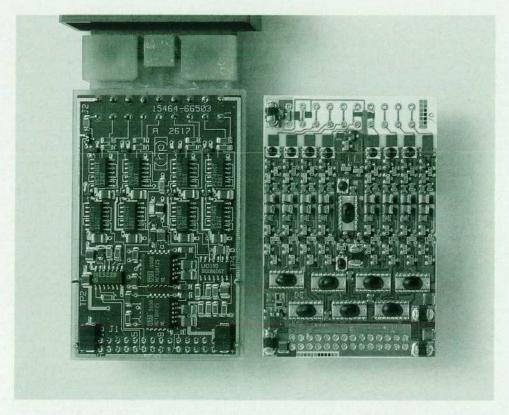

One of the design objectives was to have the pod housing

Fig. 3. HP 8175A block diagram.

as small as possible, because the space near the device under test is normally limited. Therefore, two techniques are used to miniaturize the pods. The ECL and TTL/CMOS pods are fabricated using ceramic thick-film technology. The fixed-level TTL pod, a low-cost version, is produced using surface mounted device technology (Fig. 5).

#### User Interface

A major aspect of this project was the firmware development. A requirement was that the user interface be similar to that of the HP 163x logic analyzer family so that a customer who needs a stimulus/response system will find it easy to understand both machines.

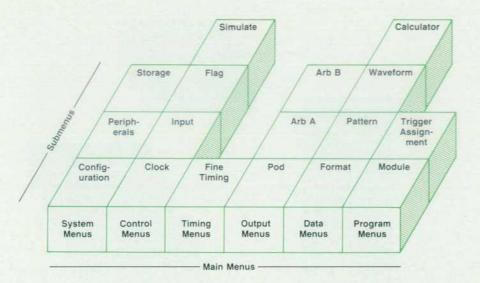

A cursor-driven menu interface was selected. Any one of six major pages (System, Control, Timing, Output, Data, Program) can be selected by a single keystroke. The content of the main pages and their subpages depends on the chosen generator configuration, selected on the System page. The possibility of choosing different configurations depends on the hardware configuration.

The storage capability is also accessible via the System page. The nonvolatile memory can save two complete machine settings plus the current setup. Up to 255 different setups can be supported without an additional controller if an external disc drive is connected to the HP 8175A. Hard-copy output of data or screen settings to an external printer is also possible.

#### Implementation

As shown in Fig. 3, the HP 8175A Data Generator consists of a power supply, the microprocessor board, the clock board, which processes the input trigger signals and creates the clock signals for the whole machine, and the data board. The data board stores the patterns and generates the parallel data signals depending on the stored patterns, the pattern duration, and the programmed data stream. A buffer board drives the external pods, and if the fine timing option is installed, contains the delay lines for four channels. Also optional is the dual-channel arbitrary board, which provides the arbitrary analog waveform generation capability.

Interconnection between boards is the function of a motherboard, which provides the supply voltages, a TTL control bus for data interchange between the microprocessor and the other boards, and an ECL high-speed bus, which carries data and clock signals between the data board and the clock, buffer, and arbitrary boards. For easy servicing, a connector that can accept any board is provided on top of the motherboard. The internal self-test is capable of detecting almost any fault on any board and displaying an appropriate error code on the display. This helps minimize troubleshooting time and keep service costs low.

#### **Data Board**

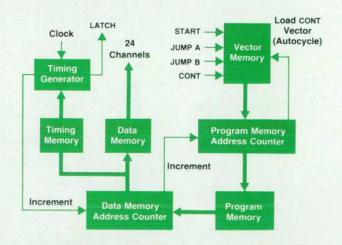

The data board (Fig. 6) stores the information for the 24 channels and generates the timing of the data stream for the 24 channels. Behind each data channel is a high-speed ECL memory that has 1K-bit depth and a data access time of 10 ns. The timing generated by the data board is dependent on the clock frequency. With the internal 100-MHz clock, the shortest time interval is 20 ns and the longest is 9.99 s. The shortest increment is 10 ns. With an external

clock, the shortest interval is one clock period and the longest is 1,000,000 clock periods. The external clock input accepts clock frequencies from dc up to 100 MHz. For efficient use of the data memories, two special techniques are used to generate the data stream:

- Program-controlled looping of information

- Generation of variable timing.

In a data stream, certain patterns, synchronization information for example, are frequently repeated. The HP 8175A allows the user to create 256 information modules, each specifying a data pattern. The sequence in which these modules are used is controlled by the program.

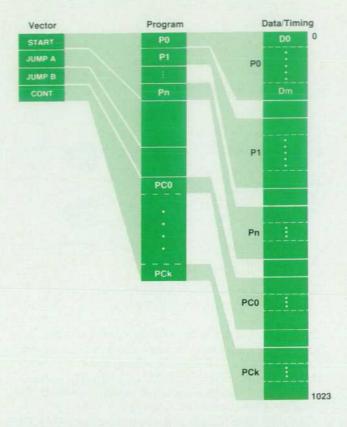

Three different programs are available. The one to be used is selected by an external trigger event called the START, JUMP A, JUMP B vector. The START, JUMP A, JUMP B vector points to one of three entrance points of different programs (see Fig. 7). Another event called the CONT vector causes a program to be repeated continuously in the autocycle mode.

A vector, the START vector for example, represents an entrance point P0 and an endpoint Pn of a program. P0 through Pn are program sequences, and there can be up to 256 such sequences in the HP 8175A (n≤255). Each program sequence refers to an entrance point D0 and an endpoint Dm in the data memory, which is 1024 bits deep (m≤1023).

By this technique of program-controlled looping, the 1K bits of physical memory depth is increased to a much larger virtual memory depth.

Operation of the data board is as follows (see Fig. 6). The vector memory is addressed by the START, JUMP A, JUMP B or CONT vector received from the clock board. The program memory address counter reads the start and stop informa-

tion of the program out of the vector memory and addresses the program memory, which contains the start and stop information for the data and timing memories. This information is loaded into the data memory address counter, which addresses the data and timing memories in parallel. From the timing memory, the pattern duration is loaded into the timing generator. At the end of each pattern, the timing generator increments the data memory address counter. The LATCH signal from the timing generator writes the pattern information from the data memory via the fine timing/buffer board to the outside world with precise timing. The increment signal of the data memory address counter fetches new data and timing information out of the data and timing memories. When the endpoint in the data memory address counter is reached, a new program sequence will be addressed, because the last data memory address counter increment also increments the program memory address counter. In single-cycle mode, the data stream stops when the last pattern of the last program sequence is completed. In autocycle mode the CONT vector will occur and start the program again.

#### Variable Timing

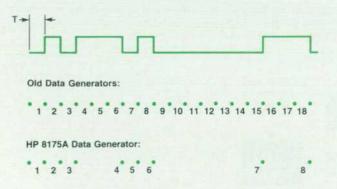

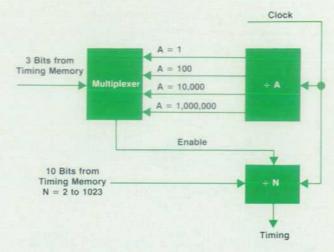

Because a normal data stream will rarely be a square wave, fixed timing of a data steam is inefficient. For example, a traditional data generator needs 18 memory locations for the data stream illustrated in Fig. 8. The HP 8175A, which has variable timing, needs only 8 memory locations for the same data stream. Fig. 9 is a diagram of the divider/timing generator that implements variable timing. The HP 8175A system clock is connected to the divider-counter blocks A and N. The divide-by-A counter has four constant division ratios: 1, 100, 10,000, and 1,000,000. These result

Fig. 4. Diagram of the TTL/CMOS pod. This pod provides for control of its output high level by the user or by the device under test.

Fig. 5. The TTL pod (left) uses surface mount technology. The TTL/CMOS pod (right) and the ECL pod use ceramic thick-film technology.

in clock periods of 10 ns, 1  $\mu$ s, 100  $\mu$ s, and 10 ms, respectively, if the internal 100-MHz clock is used. The divide-by-N counter multiplies one of the basic periods by N, which is programmed by the timing RAM. The smallest value of N is 2 and the largest is 1023. The multiplexer, also controlled by the timing RAM, decides which basic period (value of A) is in use. This technique allows the user to program a 20-ns interval followed by a 9.99-s interval with the same memory consumption for both.

#### Clock Board

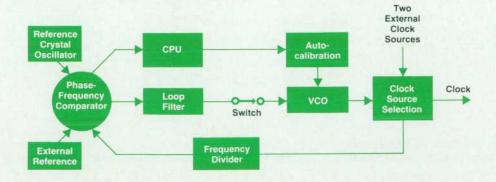

The internal system clock is a 100-MHz oscillator that has synchronous start/stop functions and an asynchronous function: the oscillator can be controlled by a phase-locked loop. Normally, if an oscillator is controlled by a phase-locked loop, it runs continously, and a start/stop signal can only gate its output. In a data generator like the HP 8175A, this could result in a timing deviation of up to one clock period (10 ns) in the output data patterns. In some applications when the generator must react to conditions in a DUT this might be a problem, so a synchronous start/stop oscillator that can be started and stopped in real time is required. In the HP 8175A the system clock can be switched between phase-locked operation and synchronous start-stop operation either from the front panel or via the HP-IB.

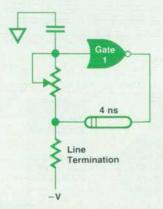

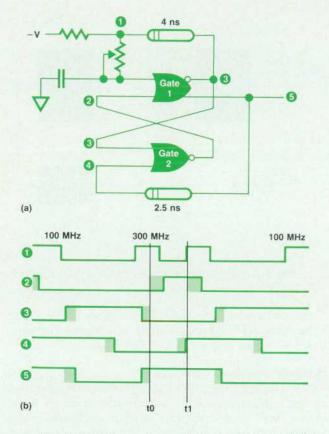

To ensure a high-performance start/stop oscillator we decided on a delay-line oscillator with a defined delay line and 100K ECL gates. The frequency of this oscillator type depends on the length of the delay line (nearly 4 ns fixed) and the propagation delay of the 100K ECL gate. This delay is 0.5 ns to 1.3 ns, which means that different gates can result in frequencies between 92.5 MHz and 108.5 MHz. Investigations proved that this was the case, so we included

an adjustment circuit to provide an adjustment of  $-9\,\mathrm{MHz}$  to  $+11\,\mathrm{MHz}$ . This adjustment is done by a variable resistor at the input of the gate, as shown in Fig. 10.

Addition of the resistor influenced the time constant of the feedback signal at the gate input. Now the problem was that the oscillator could oscillate at its third harmonic (300 MHz in this case). To avoid this problem we decided on a flip-flop circuit that shuts itself off for 4 ns. The timing diagram and circuit in Fig. 11 show how it works. The original 100K ECL gate is shown as gate 1 in Fig. 11. Low signals at time t0 at inputs 3 and 4 of gate 2, which depend on the output of gate 1, set the output of gate 2 to high. This output is connected to input 2 of gate 1 and closes this gate for a wrong oscillator edge, which can occur at time t1 at input 1 of gate 1.

Fig. 6. Data board block diagram.

Fig. 7. The START, JUMP A, JUMP B vector selects one of three programs. Each program can have up to 256 sequences, each of which occupies a section of the data memory, which is 1024 bits deep. This arrangement gives a virtual memory depth much greater than 1024 bits.

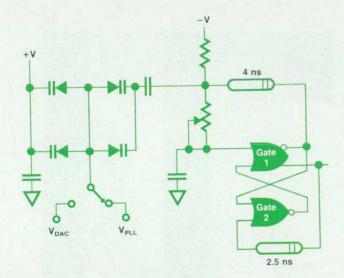

The next step was to develop a phase-locked loop circuit. A standard phase-locked loop is used (Fig. 12), which supplies a voltage proportional to the phase error between the internal quartz reference (an external reference can also be used) and the divided clock signal. This voltage is fed to a varicap diode circuit (see Fig. 13) which influences the slew rate of the falling edge by varying the capacitive load of the gate output. It provides a controllable frequency range of  $\pm 2.4$  MHz.

The diode circuit can also be switched to the output of

Fig. 8. A traditional data generator needs 18 memory locations for the data stream illustrated. The HP 8175A has variable timing and needs only eight.

Fig. 9. Variable timing is implemented by this divider/timing generator.

a digital-to-analog converter. This provides the capability of recalibrating the oscillator in the synchronous function mode, when the phase-locked loop isn't locked.

#### **Arbitrary Waveform Generator**

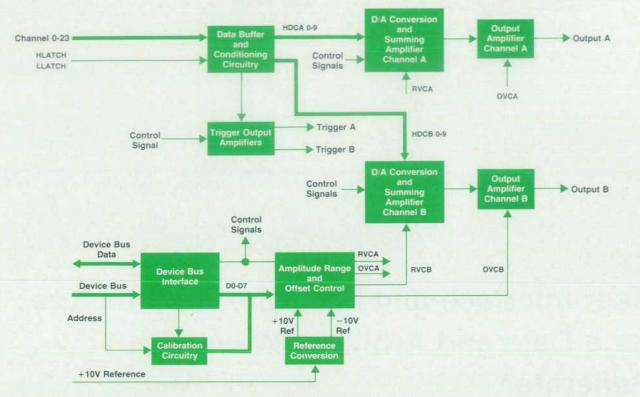

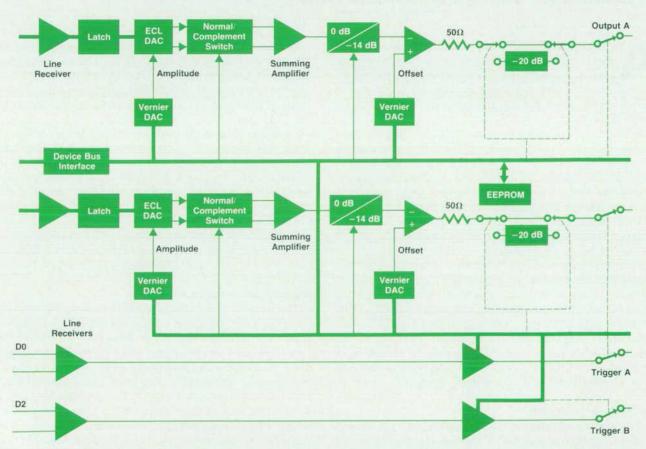

The main function of the arbitrary board is the generation of two independent analog signals—the arbitrary waveforms. These are derived from the data and timing values entered by the user. The values are stored on the data board. Under control of the microprocessor, the arbitrary board generates the output signals for channels A and B and the two corresponding trigger outputs.

The arbitrary board consists of six functional areas, as shown in Fig. 14:

- Device bus interface. This is the interface to the microprocessor-produced control signals.

- Vernier control circuitry. This produces the amplitude range and offset control voltages.

- Trigger circuitry. This produces ECL or TTL trigger signals as required.

- Output A. This provides digital-to-analog conversion and power amplification. It buffers the channel A data from the data board and feeds it to the fast DAC and the

Fig. 10. Delay-line oscillator has an adjustment for gate delay variations.

Fig. 11. Flip-flop circuit prevents third-harmonic oscillations.

power amplifier and attenuators for the channel A output.

- Output B. This provides the same functions as output A, but for the channel B output.

- Calibration circuitry. This performs an autocalibration of the amplitude and offset DACs each time the HP 8175A is powered up.

Fig. 15 is a more detailed block diagram of the arbitrary waveform generation circuitry. The binary data streams from the data board, ten bits wide for each channel, go through differential line receivers, which act as buffers, and a set of ECL latches to the multiplying ECL DAC, a Plessey SP9770B. The multiplying input of the DAC is used for coarse and fine control of the output amplitude. The amplitude factors are  $\times 1, \times 0.8, \times 0.5,$  and  $\times 0.4.$  These factors can be fine-tuned  $\pm 3.2\%, \pm 4\%, \pm 6.4\%,$  and  $\pm 8\%,$  respectively, for calibration purposes.

Fig. 13. A varicap diode circuit provides a controllable frequency range of ±2.4 MHz at 100 MHz.

The complementary outputs of the multiplying DAC can be interchanged by a relay to perform the normal/complement function, and are fed to a summing amplifier stage to obtain a single-ended signal. This signal passes through a switchable 1/5 attenuator to the power amplifier. The amplifier delivers up to  $\pm 8 V$  into a  $50\Omega$  load or  $\pm 16 V$  into an open circuit. Its design is derived from the HP 8116A and HP 8111A power amplifier designs.  $^2$  A switchable 20-dB attenuator follows the power amplifier.

The amplitude range and offset controls are generated in four independent 12-bit AD7548 DACs. The amplitude range controls influence the multiplying inputs of the high-speed ECL DACs. The offset control DACs generate the voltages for the offset voltage inputs of the output power amplifiers.

All control signals for the normal/complement switches and the various attenuator relays are delivered from the device bus interface. Data for the amplitude range and offset control DACs also comes from the microprocessor via this interface. The DACs' control function requires two eight-bit addresses for each DAC.

Two of the 24 data channels of the data board can be programmed for trigger purposes. These two channels bypass the bus buffers on the arbitrary board and go instead through differential power amplifiers capable of delivering ECL and TTL levels into a  $50\Omega$  load. The trigger circuitry

(continued on page 12)

Fig. 12. For phase-locked operation, the delay-line oscillator is embedded in a standard phaselocked loop.

Fig. 14. Arbitrary board block diagram.

Fig. 15. Arbitrary waveform generator functional block diagram.

is controlled by the microprocessor through the device bus interface.

The calibration circuitry consists essentially of an electrically erasable programmable read-only memory (EE-PROM). During the adjustment process, which takes place only in production or field service, correction values for each amplitude range and voltage range are measured for  $50\Omega$  and open-circuit loads. These values are stored in the EEPROM. They are read under control of the microprocessor each time the board is powered up.

#### Acknowledgments

We want to thank Peter Aue and Georg Trappe, who defined the instrument. Kurt Kuebler, Helmut Rossner, Thomas Fischer, and Emmerich Mueller contributed to the software, hardware, and mechanical design. Thanks also to the HP 1630 design team at the Colorado Springs Division for their support.

#### References

- 1. D. Kible, et al, "High-Speed Data Analyzer Tests Threshold and Timing Parameters," Hewlett-Packard Journal, Vol. 34, no. 7, July 1983.

- 2. M. Fleischer, et al, "A New Family of Pulse and Pulse/Function Generators," Hewlett-Packard Journal, Vol. 34, no. 6, June 1983.

# User Interface and Software Architecture for a Data and Arbitrary Waveform Generator

by Ulrich Hakenjos, Wolfgang Srok, and Rüdiger Kreiser

COMPLEX, VERSATILE, AND POWERFUL instrument like the HP 8175A Data Generator requires a human interface that is easy to learn and comfortable to use. The HP 8175A human interface is based on a cursor-driven menu concept similar to that of the HP 1630 Logic Analyzer.

A 9-inch CRT provides the user with all necessary information like status, parameters, etc. All instrument settings (data, operation conditions, etc.) are distributed over six main display pages, or menus (Fig. 1). Each main page allows the user to make particular types of settings. To enter or change a parameter, the cursor must be moved into the highlighted field, where the current value is displayed. Then the value or condition can be changed via the keyboard.

A special feature of the HP 8175A is that the user can preset changes of settings or conditions, such as data patterns or cycling conditions, while the HP 8175A is running. The new conditions can then be transferred to the outputs at some convenient time. A powerful new capability is the creation of timing diagrams (data generator) and waveforms (optional arbitrary waveform generator) by means of a graphic editor that includes several interpolation capabilities, a pattern editor, or a calculator mode.

#### Software Architecture

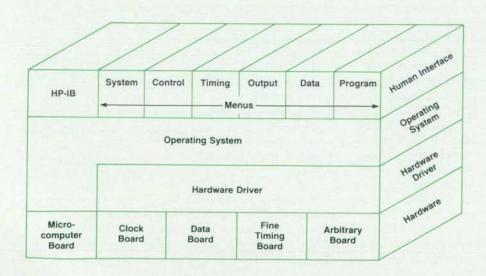

The system architecture can be described as a layered model consisting of four layers, the first three software and the last hardware (Fig. 2). The top layer contains the human interface, which is the bridge between the outside world and the instrument and contains the various menus and the HP-IB interface. The next layer is a real-time multitasking operating system, which performs the internal system control. The lowest software layer contains the drivers for the hardware.

Each data field on the menus is assigned to a corresponding driver number. If a parameter has changed, the corresponding driver number will be stored in a FIFO buffer called the driver queue. A specific task of the operating system (the hardware task) is to read the content of this queue periodically. If the queue contains a driver number, the hardware task takes this number and calls the corresponding driver routine to change the hardware state.

The lowest layer, the hardware layer, consists of the microcomputer, clock, data, fine-timing, and arbitrary boards.

#### Memory and I/O Allocation

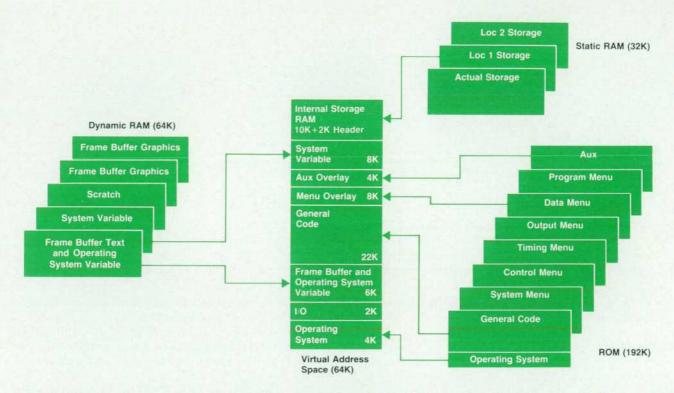

The memory size exceeds the direct addressing capability of the microprocessor, a Motorola 6809. This microprocessor can address 64K bytes. To access the HP 8175A system memory of 288K bytes, the addressing capabilities of the microprocessor are extended by means of a memory management unit (MMU). The MMU transforms a virtual address into a physical address. The physical memory is subdivided into 2K-byte segments. To allocate a physical segment to a virtual segment, the system needs the virtual page number and the physical address of the segment. The operating system supplies these numbers and controls the

Fig. 1. The user interface of the HP 8175A Data Generator distributes all instrument settings over six main display pages, or menus.

operation of the MMU. Fig. 3 shows a typical memory configuration.

#### **Editing Data**

The HP 8175A provides comprehensive data editing support. Data can be edited in several modes, using either the pattern editor or the waveform editor. The arbitrary waveform generator provides two additional modes: a waveform calculator, which allows the creation of a waveform using a mathematical expression, and several interpolation functions, including linear interpolation and natural and periodic spline interpolation.

The pattern editor allows the entry of data in different formats including binary, octal, decimal, hexadecimal, and level (arbitrary waveform generator option), and provides a set of useful editor functions. An overview of the functions of the pattern editor is shown in Fig. 4.

#### Graphics

A significant feature of the HP 8175A is its graphics capability. Data set up using the pattern editing capabilities, the calculator, or the interpolation functions and stored in tabular form can be displayed graphically. A

waveform displayed graphically is obviously far more meaningful than several pages of data.

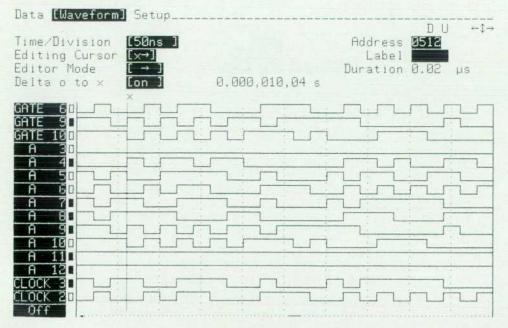

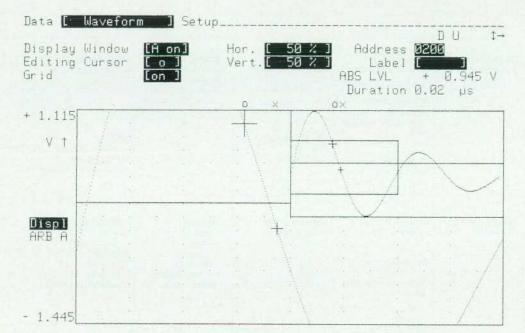

The HP 8175A has a bit-mapped graphic capability with  $512 \times 256$ -pixel resolution. There are two graphic displays: one for the parallel/serial data generator configuration and one for the arbitrary waveform generator (see Figs. 5 and 6). For either case, numerical and graphical editing are possible.

On either graphic display, the values in the upper right numerical part of the display (address, label, duration, etc.) relate to the position of the currently active editing cursor. A window in which a specific part of a waveform is displayed can be defined (Fig. 6). The window can be scrolled. The active cursor remains within the window, so if the cursor tries to "escape" from the window, the window will also move.

By means of the editor, columns (addresses) on the display can be inserted or deleted.

#### Parallel/Serial Data Generator Graphics

The graphic display for the parallel/serial data generator is generated by means of a hardware formatter, which converts the information stored in memory to a form suitable

Fig. 2. HP 8175A system architecture has four layers, three software and one hardware.

Fig. 3. Typical HP 8175A internal memory allocations.

for the CRT.

The required large dynamic range for time intervals, from 0.01  $\mu$ s to 9.99 s for the internal clock and from 1 to 999,999 cycles pattern for an external clock, led to the following implementation for the data generator graphic display. The screen is horizontally divided into ten vertical sectors. Time per division (or sector) can be set from 50 ns to 5 s in nine steps (Fig. 5). A small value expands the display, creating a small window. A large value compresses the display, creating a large window.

The position and width of the window and the cursor position within the window are displayed as bars on the lowest pixel row.

Up to 16 channels can be chosen for simultaneous display.

#### **Arbitrary Waveform Generator Graphics**

For displaying arbitrary waveforms, 1024 addresses with ten-bit resolution can be represented on a  $512 \times 256$ -pixel CRT. To ensure that no information is lost when 1024 addresses have to be accommodated in 512 pixel columns, each pixel column has two memory locations available for level information for an address pair.

The user can define a window as a subset of the full range to increase the resolution (zooming). For this purpose, in the upper right corner of the display, the full range of addresses and amplitudes is displayed. Within this full range, the user can define a window with width selectable from 100% down to 25% in three steps, and height selectable from 100% down to 3% in six steps (Fig. 6).

Two graphics cursors are available. Fast positioning of the active cursor and/or the window is possible by:

- Cursor swap

- Label quick search

- Scrolling

- Directly entering numerical addresses.

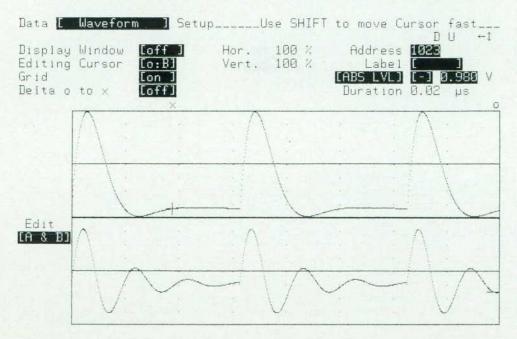

The physical screen can be divided vertically into as many as four logical screens (Fig. 7). The following modes are available:

- Only one curve

- Curve and associated trigger

- Two curves

- Two analog curves and their associated digital triggers.

Editing is possible in all of the previously described modes. However, the level increment depends on the chosen display mode. Other capabilities include voltage and time measurements between the two graphics cursors, and setting and deleting triggers.

#### Simulating Waveforms

In practice, it is not always possible or practical to describe a waveform mathematically. Instead, many waveforms need to be simulated (Fig. 8). Examples of such waveforms are:

- Medicine: heartbeats, nerve responses

- Material/electromechanical testing: disc drives, switching motors, relays

- Radar and sonar signals

- Waveforms for stimulating electrical/electronic components.

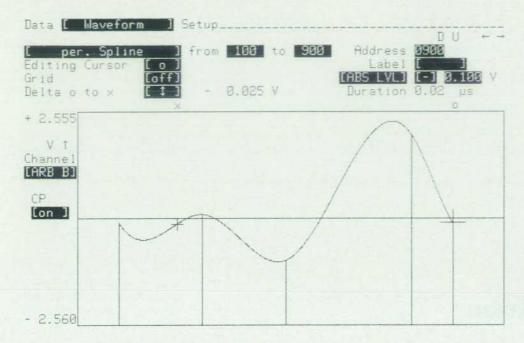

Waveforms are simulated with the HP 8175A by entering characteristic points and interpolating between them. Characteristic points can be graphically set and deleted in either of two ways, and can be interpolated by means of linear, normal, or periodic splines within any user-defina-

|                                         | Insert                                                             | Delete                   | Сору                                                       | Move                           | Modify                                                      | Function                                                             |

|-----------------------------------------|--------------------------------------------------------------------|--------------------------|------------------------------------------------------------|--------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------|

| itor                                    | Insert data line<br>before pending<br>line                         | Delete pending data line | Copy data line from # to # →#                              | Move data line from # to # → # | Modify data and<br>duration to new<br>values<br>from # to # | Increment or<br>Decrement counter<br>from # to #                     |

| HP 8175A<br>Data Generator              | Data in inserted                                                   |                          | Store data line from # to # → #                            |                                |                                                             |                                                                      |

| Ge                                      | set to zero                                                        |                          | (overwrites existing                                       |                                |                                                             |                                                                      |

| Date                                    |                                                                    |                          | data)                                                      | Exchange data                  |                                                             | PRBS<br>from # with shift                                            |

|                                         |                                                                    |                          | Copy data channel from # to #                              | channel<br>from # to #         |                                                             | register length x<br>and feedback patter                             |

| c                                       | Insert data line before pending line                               | Delete pending data line | Copy data line from # to # → #                             | Move data line from # to #     | Modify<br>-data<br>-level                                   | Interpolation<br>-linear<br>-natural spline                          |

| form Option<br>002                      | Data in inserted line<br>is default set to data<br>in pending line |                          | Store data line from # to # → # (overwrites existing data) |                                | -trigger<br>-duration<br>to new values<br>- from # to #     | -periodic spline<br>from # to #<br>and given<br>characteristic point |

| Arbitrary Waveform Option<br>Option 002 |                                                                    |                          | Copy data from channel A to channel B from # to # → #      | Exchange data from             |                                                             |                                                                      |

| q                                       |                                                                    |                          | Copy data from channel B to channel A from # to # → #      | channel A with<br>channel B    |                                                             |                                                                      |

Fig. 4. Overview of the functions of the pattern editor.

ble address range. Characteristic points can be deleted in blocks.

#### Interpolation

There are two principal methods of interpolating N characteristic points: by polynomials or by splines.<sup>1</sup>

When polynomials are used, N characteristic points are interpolated with a best-fit (N-1)th-order polynomial.

From the N characteristic points, N equations are derived, from which the unknown coefficients of the polynomial can be determined.

Since, normally, the matrix of this set of equations has no zeros, the Gauss procedure can be used for solution. However, the computation time is proportional to the square of the number of unknown coefficients and can be

Fig. 5. Graphic display for the data generator configuration.

Fig. 6. Graphic display for the arbitrary waveform generator configuration.

very long. It is also possible to use the Horner formula, for which the computation time is linearly proportional to N. However, in cases where a large number of characteristic points are defined, this function oscillates at the interval margins.<sup>2</sup>

#### **Splines**

Because of these disadvantages of polynomial interpolation, the HP 8175A uses splines. The term spline can be traced back to the early days of shipbuilding, and relates to the way in which the hull curves were formed. With splines, the time required to compute the coefficients of a waveform is proportional to N, and the time required to determine an interpolated value is constant.

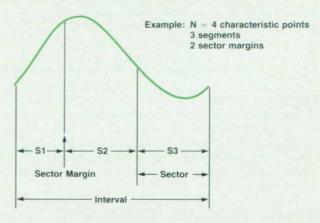

In spline interpolation, between each two consecutive

characteristic points, third-order polynomial interpolation is done (Fig. 9). Thus, there are (N-1) sectors, and (N-1) third-order polynomials to be computed.

To determine the coefficients, four conditions must be satisfied. Two conditions are related to the requirement that the two characteristic points at the ends of a sector have to be elements of the resulting function. The other two conditions are related to the requirement that the slopes at the two margins of a sector must merge smoothly. That is, the first and second derivatives at the sector margins must be identical.

Additional conditions apply at the start and end of the interval to be interpolated. For example, for a periodic spline, the slopes at the start and the end of the interval have to be identical.<sup>3,4</sup>

Fig. 7. The physical screen can be divided vertically into as many as four logical screens.

Fig. 8. Waveforms that are impractical to describe mathematically can be simulated by entering characteristic points.

For spline interpolation, the matrix of the set of equations is a cyclic tridiagonal matrix. Therefore, a simplified Gauss procedure can be used. The computation time is linearly proportional to N instead of  $N^2$ .

The user can estimate the trend of a natural spline function to be computed simply by imagining how a flexible ruler would be bent if it were confined within or supported by the characteristic points. There is no problem of oscillation at the sector margins.

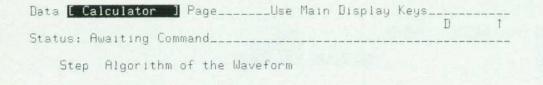

#### The Calculator

The waveform calculator is a special capability of the arbitrary waveform generator option that enables the user to write and run programs to set up most complex mathematical waveforms by directly entering the formula in its written form. This can be done using only the HP 8175A keyboard; no separate computer is needed.

A comprehensive selection of standard statements and mathematical functions is available via softkeys. It is not necessary to type every character, so programs can be written very quickly.

The process that does the actual calculation and transfers the new amplitude and timing values to memory includes editing (setting up the function), setting the parameters, and finally, running the module. The following example shows how to set up and run a simple sinusoidal waveform.

#### **Deriving the Mathematical Function**

As already mentioned, using the calculator involves setting up the mathematical expression that represents the waveform. In practice, the first step is to derive this for the waveform. This is done as follows:

A sinusoidal waveform can be expressed as

$$y = \sin(\omega t) = \sin(2\pi f t) = \sin(2\pi f T_x)$$

where  $T_{\rm x}$  is the instantaneous time. Within any amplitude range, waveform accuracy depends on the combination of

maximum and minimum level values and the number of data points used. We will use 1000 data points for one cycle, which means that 1000 steps (level values) must be calculated (1024 steps are available but 1000 is an easier number to work with).

For a frequency of 10 kHz, the period is 100  $\mu$ s. The timing window (the duration that the waveform will be calculated for) must be set to 100  $\mu$ s and each incremental step of  $T_x$  must therefore be 0.1  $\mu$ s. Calculator functions are set up as one or more modules, each of which consists of a header and an algorithm part. In this example the header defines the required time window of 100  $\mu$ s and the incremental step duration of 0.1  $\mu$ s. The algorithm part is the expression for the waveform. The complete module is shown in Fig. 10, where line 0 represents the header and line 1 the algorithm.

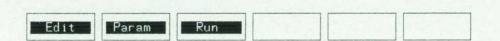

#### Syntax, Restrictions, and Limitations

The module syntax is similar to normal computer program statements. Fig. 11 shows the syntax diagrams. All

Fig. 9. Third-order polynomial interpolation is done between characteristic points.

Fig. 10. To define a waveform using the waveform calculator, functions are set up as one or more modules, each consisting of a header (line 0 here) and an algorithm (line 1).

items enclosed by rounded envelopes are available directly via a corresponding softkey. Words enclosed by a rectangular box are names of items used in the statements.

The complete function can consist of 750 bytes. Each ASCII character, including spaces, requires one byte. Keywords such as FOR, STEP, etc. and standard functions such as SIN, LOG, etc. also require only one byte each. The step duration must be within the HP 8175A's timing (20 ns to 9.99 s) and resolution (10 ns to 0.01 s) capabilities. All calculations are done by means of a floating-point library with an internal 32-bit format. Therefore, the calculation time for the sinusoidal waveform is about 7 seconds, because most of the standard functions including SIN are derived from truncated series. The maximum relative error in these approximations is less than 0.00039% for the SIN function.

#### Setting the Parameters and Running the Module

After the function has been edited, it is compiled automatically by leaving the editor. If a syntax error is discovered, an appropriate error message will be displayed and the location of the error within the function will be indicated by the cursor. In such cases, any corrections required must be made before it will be possible to end the edit mode. If there is more than one error, another error message will be displayed after the first error is corrected. Only when all errors have been corrected is leaving the edit mode possible.

The next step is to define the relation between the edited function and the desired output voltage and arbitrary waveform channel. In Fig. 12, the first field defines which output channel the function is to be calculated for, and the second defines how to consider the levels, either with or without offset.

The amplitude range previously set on the output page, 5V for example, will be displayed. The required maximum and minimum levels can now be set. These are the amplitude values that are assigned to the maximum and

minimum data values calculated from the function.

The Calculate from Address is the address from which the calculated data patterns will start.

The last step is to start the calculating process. The resulting amplitude and timing values are transferred to the HP 8175A's memory.

Fig. 11. Waveform calculator syntax diagrams.

Data Calculator Page\_\_\_\_\_Use Main Display Keys\_\_\_ Status: Parameter Setup\_\_\_\_\_\_ Amplitude Range: [ 5 V ] (max. + 2.555 V)Max.Level: (min. - 2.560 V Min.Level: Calculate from Address MMM or Label [ Combine [Off] Fig. 12. Defining output parameters for a waveform calculator End\_para function For the sine wave example, the original sine wave mod-Local Overlaying ule must be deleted and replaced with the noisy function. Crosstalk simulation often requires noise, spikes, or other The Combine field of the parameter setup page must be set functions to be overlaid in a specific part of an existing to On (Fig. 14). The Combine mode and the ratio of the two waveform. The HP 8175A's Combine feature makes this possignals can then be set. sible and offers great flexibility. A function can be com-After calculation is completed, the HP 8175A's memory bined in a variety of ways with any part of an existing will contain the new waveform calculated from the old waveform. This is useful in cases where, for example, a pattern and the new function (Fig. 15). waveform that is very difficult to describe mathematically and has therefore been set up graphically or by spline interpolation needs to have noise added to it. The noise waveform can be set up using the calculator and then combined (add, subtract, multiply, divide) with the original waveform. The signals can be combined in any ratio between +60 dB and -60 dB. An example illustrating the use of this capability is shown in Fig. 13. Data [ Calculator ] Page\_\_\_\_\_Use Main Display Keys\_. Status: Awaiting Command\_\_\_\_\_ Step Algorithm of the Waveform 0 FOR 100 US STEP 0.1 US 1 1 (RND) Fig. 13. Definition of a random noise waveform to be added to a Param Run

sine function.

Fig. 14. To combine functions, the Combine field is set to On, and the ratio of the two signals is specified.

End\_para

#### References

- F.B. Hildebrand, Methods of Applied Mathematics, Prentice-Hall, 1965.

- G. Alefeld and R.D. Grigorieff, Fundamentals of Numerical Computation (Computer Oriented Numerical Analysis), Springer-Verlag, 1980.

- 3. J.H. Ahlberg, E.N. Nilson, and J.L. Walsh, The Theory of Splines and their Application, Academic Press, 1967.

- 4. C. Reinsch, "Smoothing by Spline Functions I/II," Numerische Mathematik, Vol. 10 (1967), pp. 177-183.

Fig. 15. The result of combining noise and a sine wave.

## A Planning Solution for the Semiconductor Industry

Semiconductor device manufacturing has several situations that complicate normal production scheduling and medium-range planning. PL-10, part of HP's Semiconductor Productivity Network, was developed to deal with these peculiarities.

by Edward L. Wilson, Kelly A. Sznaider, and Clemen Jue

L-10 IS A MASTER PLANNING TOOL developed by Hewlett-Packard for the semiconductor manufacturing industry. It addresses the task of mediumrange production planning (up to 2 years) for a geographically distributed semiconductor division or company.

PL-10 helps the planner develop master production schedules for all major areas of a semiconductor company: wafer fab, sort, assembly, and test. The planner enters basic planning parameters—product demand forecasts, time-phased WIP (work-in-process) availability, product yields, and lead times—either manually or through batch files (see Fig. 1). PL-10 works backward from product demand to determine wafer requirements, which the planner can review and modify. It then projects forward from planned wafer starts to expected shipments. The planner can review rough-cut capacity use projections and associate component requirements with product demand. Repeated iterations of this process result in a workable companywide production plan.

PL-10 is currently in use in several HP semiconductor facilities and is being installed at several customer sites inside and outside the U.S.A. The release of the product unfortunately comes at a time when HP has decided to withdraw from the semiconductor CIM business. Despite this decision, development of PL-10 was deemed critical enough to continue with release plans, but the product will not be sold outside the current SPN user base and no further enhancements will be funded.

#### Semiconductor Manufacturing Planning

The semiconductor industry is a complex hybrid of batch and process manufacturing. While the basic job of scheduling production is the same in any industry, there are problems that make traditional MRP (material requirements planning) solutions difficult to implement:

No work orders. Semiconductor wafers are processed in lots which are sized according to the equipment they will be processed on. Typically they are not tracked by specific work order; rather, they are treated as a continuous flow of material. This creates problems for MRP systems that schedule work orders to meet end-item demand.

**Inverse part structure.** Semiconductor devices are grown from simple raw materials. Assembly (placing the semiconductor die into a ceramic or plastic package) occurs late in

the manufacturing process. A single integrated circuit, or die, can be made into a variety of products depending on the circuit layout, the type of package used, and the tests administered. ROM chips have additional variations when a generic ROM wafer is programmed by a customized interconnection pattern defined in a final mask layer. This inverse part structure—simple bills of material with thousands of end items made from a few basic components—does not work well with traditional MRP. MRP helps planners answer the question, "What must I order to build the products I need?" The semiconductor planner must also answer the question, "What can I make with the material already in-process?"

Fluctuating yields. Semiconductor device yields can be unpredictable, especially for new processes. Normal MRP systems can handle the possibility of scrap, but may be unable to deal with situations such as:

Fig. 1. Planning cycle

- Wafer-to-die conversion. The number of good parts (die) on a wafer can vary widely. The planner must estimate the number of wafers needed to make a required number of parts. This is different from the standard MRP "Quantity Per" in which a truck, for example, always needs four wheels and cannot be built unless those wheels are available.

- Yield improvements. While yields fluctuate, they tend to improve over time. A planner who does not consider this gradual improvement will risk scheduling too many wafer starts in later periods.

- Binning. Not only does the yield of good material vary, but the very output of the process is not completely controlled. Finished circuits are subjected to a variety of electrical and environmental tests to determine the specifications under which they may be sold. The outcome of this binning process is subject to statistical distribution but is also influenced by the desired outcome of the process. That is, the set of tests done on the material depends on which grades of product are in demand. Material that fails a test may also be retested to a less-stringent specification (downgrading).

Worldwide planning. Nearly all semiconductor manufacturers do assembly in the Far East. Any planning system for the semiconductor industry must be able to schedule multiple sites at once. This involves allocating production between factories that have different delivery times and work schedules. To be fully functional, the planning system must be able to send and receive data to and from these factories without manual rekeying.

The semiconductor industry has gone through a radical shift in the last few years. When business was booming, manufacturers could sell everything they made. Accordingly, the emphasis was on improving yields and process throughput. With business currently declining, there is an increased emphasis on production planning—building the right product—and on matching capacity to uncertain demand.

#### History

As mentioned earlier, PL-10 is the last of the Semiconductor Productivity Network (SPN, see Fig. 2) products to be developed. The precursor to PL-10 was created at HP's Corporate Manufacturing Information Systems (CMIS) to be a standard scheduling system for internal HP divisions that would eventually converge with HP's MM/3000 master scheduling package. Instead, the software was used as the starting point for PL-10, with much of the original code and functionality carried over.

The first version of PL-10 was released in early 1985 to HP's Northwest IC Division and Loveland Technology Center, and one outside customer. Based on the feedback of these users, a substantial redesign was done. The second version was completed in August 1986, and included major changes to the data base, the production calendar, and the MRP Explode logic. New interface programs and the Roll Forward program were also added.

#### Integration with SPN

PL-10 extracts essential parametric and production data from IC-10, the SPN lot tracking system. The systems are loosely coupled by file interfaces.

Shop floor calendars, process yields, cycle times, part numbers, and part information such as cost and probe yields are examples of parametric data that can be extracted from IC-10. PL-10 obtains WIP status from a standard IC-10 extract file containing a snapshot of production—ending on-hand quantities for each process location. Using IC-10 process yields and cycle times, PL-10 forecasts these out to finished goods inventory to determine expected outs quantities and their expected due dates.

PL-10's Part Mapping function allows the planner to consolidate several production parts, spanning several IC-10 WIP and stockroom areas, into one planning part. Consolidation can be done on the basis of similarities in the part numbers; this is particularly useful for planning families of parts. The goal is to reduce the number of items that the planner has to forecast.

Since IC-10 and PL-10 are loosely coupled, either system can be installed first. The interface allows any inventory tracking system, such as MM/3000, to feed data into PL-10. PL-10 can thus be used to do production planning and scheduling for several tracking systems, either on the same computer and/or at remote computer sites. This flexible interface approach also applies to PL-10's customer order and forecast interface, which allows any order processing system to enter demand into PL-10. Forecasts can be uploaded from spreadsheet programs using the same interface.

Fig. 2. HP's Semiconductor Productivity Network is a collection of hardware and software products designed to aid microelectronic product fabrication personnel in controlling, monitoring, improving, and managing many of the levels of the complex manufacturing process.

#### PL-10 as a Manufacturing Tool

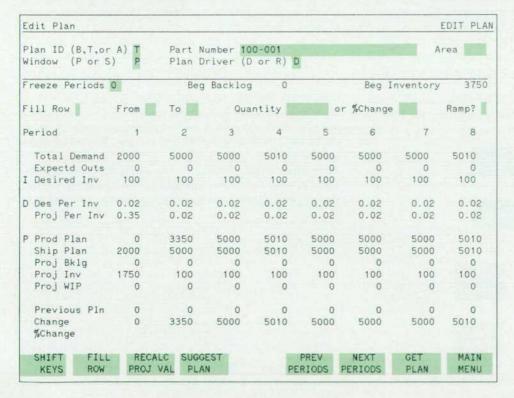

Editing the Plan. PL-10 allows the user to manipulate the production plan on-line in real time, unlike most conventional MRP systems. The planner can perform simulations or make last-minute changes to the plan depending on the manufacturing environment. To plan more effectively, it is very important to be able to assess various tentative plans and schedules by varying some or all factors. This what-if analysis is one of PL-10's capabilities, called Edit Plan. The consequences of a proposed production plan can be determined before finalizing and implementing it.

Edit Plan can suggest the optimal production plan based on various factors, such as lead time, yield, work-in-process, inventory, and demand. One or all factors can be varied to view how the changes will affect the production plan. This provides flexibility for adjusting to the rapid changes in the manufacturing environment. The planner can be assured that the production plan is the best plan possible under the current manufacturing conditions.

Since the planner needs to access a large variety of data to create a reliable production plan, Edit Plan can access the information by three different windows (see Fig. 3 for one example). The windowing feature in Edit Plan is performed by using parent and child forms in VPLUS/3000. The result is a planning spreadsheet that can be manipulated by adjusting individual period values or by applying any of several precoded algorithms.

Edit Plan has another special feature called Fill Column. The Fill Column function allows the planner to simulate or modify arrays of data easily and quickly. This feature, used throughout the system, gives the user functionality similar to that provided by 1-2-3 ™ from Lotus ™ Fill Column can set a range of period values to a constant, or adjust 1-2-3 and Lotus are U.S. trademarks of Lotus Development Corp.

them by a constant or a percent increase or decrease. Within Fill Column is a feature called ramping, defined as adding the quantity entered to the existing quantity and storing the result in the next period on the horizon. This algorithm continues until all the specified periods are filled.

Since the Fill Column function is used in multiple programs, it was decided to include it as a Segmented Library procedure. This provides for easy maintenance and more quality in the PL-10 product.

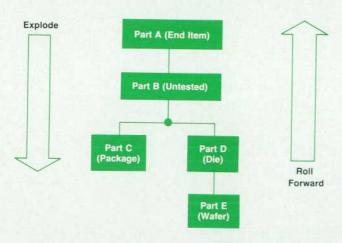

Explode and Roll Forward. PL-10 has scheduling functions known as the Explode and Roll Forward transactions. Explode is similar to standard MRP explosion (with some extras). Roll Forward is a bottom-up MRP implosion.

The scheduling function is a process of maintaining the production plan to satisfy the total demands. A finished goods item, also referred to as the end item, is demanded by customers. This end-item demand generates requirements for intermediate parts. The intermediate parts generate requirements for raw materials and so forth. Explode in PL-10 calculates the total of each component in the bill of material required to manufacture the planned quantities of end items. Based on this, it will then suggest what will be made by date and quantity for each part. These plans are based on the part information, planning bill structure information, demand already entered, current inventory, and work-in-process.

Explode starts with the end item and works downward (see Fig. 4). A schedule based on top-down demand alone will not show when a schedule is impractical because Explode does not know the lead-time requirements of component parts. For example, if a customer orders product A to be shipped tomorrow, but it takes seven days to produce component B of product A, the earliest Product A can be shipped is one week from today. Explode would suggest

Fig. 3. Edit Plan screen display.

the factory begin producing Product A today because it has no way to adjust the parent's schedule for the component's lead time.

This problem is solved by using Roll Forward, a bottomup approach, often referred as implosion (see Fig. 4). This function in PL-10 begins with the requirements (from Explode) for the lowest-level parts in the bill of material and calculates when these parts should be produced and how many. Once produced, they can be allocated to the next higher-level part to arrive at the parent part's dates and quantities. This continues until the dates and quantities are calculated for the end item. Roll Forward shows how feasible the schedule is, based on both work-in-process and planned starts (building the part from scratch).

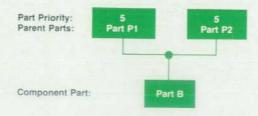

Implosion logic quickly becomes unmanageable when many components are assembled into one parent, which is why standard MRP does not have this feature. Since semiconductor bills are short and simple, PL-10 handles Roll Forward for multiple components by having one part act as the driver. In the example shown in Fig. 4, only the die supply is rolled forward. Package requirements are calculated by Explode, but Roll Forward assumes that sufficient packages will always be available.

On the technical side, both of these programs use external files that are loaded into memory at the beginning, then read from and written to throughout the program. For the Explode program, the files are requirement files. These files state the demanded quantity and date. There is one requirement file for each level in the bill of material. The Roll Forward program reads the requirement files from Explode and generates supply files for the parent parts. If the planner is unsure of the results from either Explode or Roll Forward, these files can be used to analyze the production plan.

By using Edit Plan, Explode, and Roll Forward, the planner can make more intelligent decisions. Since the production plan is considered the company's game plan, it is very important for the plans to be realistic and reliable.

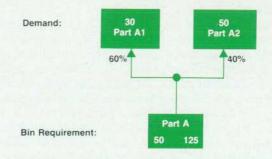

**Binning.** A common process in the semiconductor industry is binning: a part generates multiple byproduct parts based on sorting or testing. This can create excess inventory.

When Explode processes a part that bins into byproducts, the requirements are optimized by generating requirements that satisfy demand while minimizing the excess inventory.

Fig. 4. Explode and Roll Forward processes

Fig. 5. Binning example.

For example, component Part A bins into two parts, Part A1 and Part A2, as shown in Fig. 5. If demand for Part A1 is 30 and demand for Part A2 is 50, then how much of Part A should be produced?

The first consideration is the expected bin-out percentages for Part A1 and Part A2. In this example, the bin percentages are 60% and 40% respectively. A traditional MRP system, using these percentages, would start 50 units of Part A to build Part A1, plus 125 units of Part A to build Part A2, for a total of 175 units started. At bin-out time, this would result in 105 units of Part A1 and 70 units of Part A2, clearly a waste of material.

PL-10 optimizes the plan by considering all the by-products of Part A together. In this example, 125 would be the minimum quantity of Part A to satisfy the demand. However, this still results in excess inventory of 45 units for Part A1. True optimization occurs when the entire planning horizon is considered. The excess inventory of one period may be used to meet the demand in another period, thus minimizing the need to produce more Part As than are necessary.

To illustrate this better, consider a planning horizon (Table I) that is three periods long. The maximum requirements come from Part A2 in periods 1 and 2 and Part A1 in period 3. Notice the excess inventory is kept to a minimum and all demand is satisfied with this method.

In this example, the 125 units planned for Part A in Period 1 satisfy the demand for both Part A1 and A2. They also create enough excess inventory (45 units of A1) to satisfy demand for A1 and A2 in Period 2 without additional starts. In Period 3 the only demand is for 15 units of A1 not covered by inventory, so only 25 Part A units are started.

**Allocation Rules.** Allocation of supply is performed by Roll Forward in PL-10. Allocation is needed when several parent parts (different package configurations, for example)

| Three             | -Perio | d Pl  |     | ble I<br>Horizon f | or B | inned | Parts |       |       |

|-------------------|--------|-------|-----|--------------------|------|-------|-------|-------|-------|

| Part              |        | art A |     |                    | rt A |       |       | art A |       |

| Period:           | 1      | 2     | 3   | 1                  | 2    | 3     | 1     | 2     | 3     |

| Demand:           | 30     | 30    | 30  | 50                 | 0    | 0     |       |       | 3.770 |

| Bin Requirement:  | 50     | 50    | 50  | 125                | 0    | 0     |       |       |       |

| Cumulative Need:  | 50     | 100   | 150 | 125                | 25   | 125   |       |       |       |

| Max Cum Need:     |        |       |     |                    |      |       | 125   | 125   | 150   |

| Net Bin Need:     |        |       |     |                    |      |       | 125   | 0     | 25    |

| Excess Inventory: | 45     | 15    | 0   | 0                  | 0    | 10    |       |       |       |

Fig. 6. Allocation example for equal part priority

can be made from a single component, such as a die. It differs from binning in that the planner must decide how to allocate the available dice. Roll Forward suggests a default allocation using parameters set by the planner. The transaction will not allocate more than the amount requested for any part. Any excess inventory will remain as the part's inventory.

In the bill of material, many parent items can be structured to a single component. Likewise, a single parent item can be obtained from several sources of supply (components). The planner can set parameters in PL-10 to allocate these supplies effectively.

Each part contains a field called Priority. This signifies that the supply should be allocated first to the highest priority to meet all its demand. If priorities are the same, then the supply is allocated based on demand. If there is insufficient demand, the ratio of each part's demand to the total demand will be calculated and the supply allocated by that fraction. An example will illustrate this better. Fig. 6 and Table II show the results when the part priorities are the same.

Consider the same example, but with different priorities where Part P1 has a priority of 5 and Part P2 has a priority of 7. The results are given in Table III. Notice that Part P2's demand is satisfied before allocating to Part P1.

The allocation shows if the production plan generated by the explosion process is indeed workable. In the example above, the plan is considered impractical because of insufficient supply.

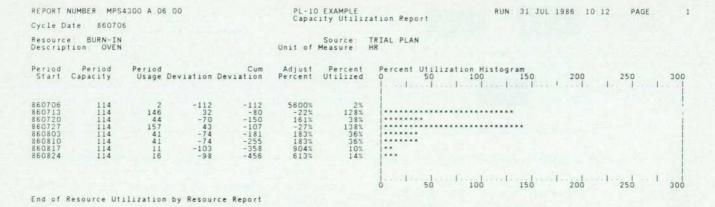

Resource and Capacity Planning. Semiconductor facilities are equipment and capital-intensive. Equipment is sophisticated and expensive, and capacity utilization is a very important factor in increasing productivity and decreasing costs and long cycle times. Equipment underutilization is no better than equipment overutilization.

A major feature of PL-10 is a vehicle to report utilization (over and/or under) of resources predicted by the production plan. Rough-estimate resource utilization reports show the planner any periods where there are potential capacity bottlenecks or excess idle time. With this information the

|                 | -  | Alloca |    | ble II<br>h Same | Prio   | rity |    |       |    |

|-----------------|----|--------|----|------------------|--------|------|----|-------|----|

| Part:           | Pa | rt P1  |    | Pa               | art Pa | 2    | P  | art B |    |

| Period:         | 1  | 2      | 3  | 1                | 2      | 3    | 1  | 2     | 3  |

| Demand:         | 10 | 20     | 10 | 20               | 20     | 30   |    |       |    |

| Demand Ratio %: | 33 | 50     | 25 | 67               | 50     | 75   |    |       |    |

| Supply:         |    |        |    |                  |        |      | 15 | 30    | 40 |

| Allocation:     | 5  | 15     | 10 | 10               | 15     | 30   |    |       |    |

|             | Table III Allocation with Different Priority |          |  |  |  |  |  |

|-------------|----------------------------------------------|----------|--|--|--|--|--|

| Part        | Part P1                                      | Part P2  |  |  |  |  |  |

| Period:     | 1 2 3                                        | 1 2 3    |  |  |  |  |  |

| Allocation: | 0 10 10                                      | 15 20 30 |  |  |  |  |  |

planner can adjust the schedule by pulling up or pushing out production, or by reallocating resources.

Resources in PL-10 can be defined for any critical item at a facility, such as overall process capacity, machine capacity, or labor. Resources can be tied to a shop calendar depicting the days the resource will or will not be available.

Resources have a certain amount of capacity and downtime, which are not usually evenly distributed across the planning horizon. To accommodate this situation, the user can adjust all planning parameters of a resource by time period.

The next step for the planner is to specify the production parts that will use each resource. PL-10 lets the planner map the following parameters to the part-resource pair:

- 1. Resource requirement for one unit of the part.

- Resource lead time to define the number of working days before the part's completion date when the resource is required.

- 3. Resource yielding factor (%) to compensate for anticipated yield loss between the number of units scheduled and the number that will use the resource.

A part in a semiconductor device fabrication process can return several times to the same equipment or process step, such as the photomasking step for a wafer. To accommodate this situation, PL-10 can assign a part to the same resource for several steps in the manufacturing process.

PL-10 extracts production plan data and calculates the required resource use given the factors listed above. A summary report for a resource is given in Fig. 7.

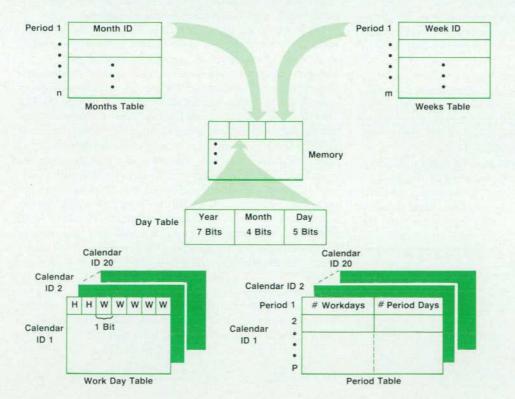

Memory-Resident Shop Calendars. PL-10 makes intensive use of date calculations. Because the system schedules manufacturing areas having different work schedules, PL-10's date calculations must take into consideration multiple shop calendar parameters. Production Starts, Outs, and Supply are all associated with either a start date or a due date. All dates are represented in year-month-day format.

Date calculations must cover the complete planning horizon (up to 26 months), and must take into account the different calendars (up to 20) that can be defined by the user, the workday and holiday configuration for each individual calendar, and the lead times and lead time adjusts of the various planning parts and their associated part structures. Again, all dates are represented in year-month-day format.

The problem posed to the PL-10 team was how to access this massive calendar quickly and still keep batch run times to a minimum. PL-10's predecessor, designed to schedule only a single work area, stored the calendar in a flat file and read it into memory. The representation of the file was in year-month-day format where each digit was represented by 4 bits. Thus each calendar day was represented by 24

Fig. 7. Capacity utilization report.

bits or 3 bytes. In this configuration only workdays were kept in the file. If a calendar year had 260 workdays, and the planning horizon spanned two years, then 1560 bytes  $(260\times2\times3)$  were needed to hold the table. If the user were able to define 20 different shop floor calendars, then a total of 31,200 bytes would have been needed to hold all the calendars in memory.

In building the current version of PL-10, the memory storage requirements for 20 different calendars using the old scheme would have been impractical. Another approach was taken to represent the calendars and still keep them resident in memory. For each different shop floor calendar, a Holiday/Workday mapping is kept for each calendar day in the planning horizon. Hence, two tables are needed, one for each calendar day in the planning horizon, and one for the Holiday/Workday indicator for the various shop floor calendars. A calendar day is represented

by 16 bits instead of 24 bits. The new year-month-day format representation is: year—7 bits, month—4 bits, and day—5 bits.

With this new format, the memory requirement for 20 different shop floor calendars, each spanning 26 months, is (considering that a planning month in PL-10 can have up to six weeks or 42 days):

#### Calendar Table:

$(26 \text{ months}) \times (42 \text{ days/month}) \times (2 \text{ bytes}) = 2184 \text{ bytes}.$

#### Work Day Table:

$(20 \text{ calendars}) \times (26 \text{ months}) \times (42 \text{ days})/(8 \text{ bits}) = 2730 \text{ bytes}.$

Fig. 8. Organization of memoryresident calendar tables.

Three other tables of smaller sizes are kept in memory to provide quick date calculations for month or week planning. The month and week tables have pointers into the day table to locate the starting date of each calendar month and week. The period table summarizes the workday table—it shows the total days and work days in each planning period. All five tables and their relationships are represented in Fig. 8.

#### Acknowledgments

We would like to thank the following people whose contributions made PL-10 a reality: the MPS 1.5 group at CMIS—Kevin Cooper, Andra Marynowski, Randall Fryer, Mark Wunderman, and Preston Carter—the marketing group—Julie Schoenfeld, Tom Coughlin, Monica Randall,

and Patti Herbst—and lab members Ken Yao, Jan Grady, Scott Ingraham, and Pat Grever. Special thanks go to Mark Kinsman of the lab for his insight and help with many of the algorithms.

#### References

- W.H. Higaki, "Remote Monitoring and Control of Semiconductor Processing," Hewlett-Packard Journal, Vol. 36, no. 7, July 1985, pp. 30-34.

- R.I. White, "Automated Test Data Collection for IC Manufacturing," Hewlett-Packard Journal, Vol. 36, no. 8, August 1985, pp. 30-36.

- N.C. Federman and R.M. Steiner, "An Interactive Material Planning and Control System for Manufacturing Companies," Hewlett-Packard Journal, Vol. 32, no. 4, April 1981, pp. 3-12.

## **Authors**

**April** 1987