# JOURNAL

**JULY 1985**

# JOURNAL

July 1985 Volume 36

Number 7

### Articles

4 Protocol Analyzer for EDP Centers and Field Service, by Aileen C. Appleyard, Roger W. Ruhnow, William Grant Grovenburg, and Wayne M. Angevine It monitors serial data streams up to 256 kbps and simulates up to 72 kbps.

5 How Protocol Analysis Can Help

10 Protocol Analyzer Software Development

**12** Simple Architecture Provides High Performance for Protocol Analysis, by Stephen H. Witt and Roger W. Ruhnow A 68000 microprocessor controls the system. A trap machine provides powerful triggering capabilities.

- 14 Protocol Analyzer Power Supply Design

- 15 Protocol Analyzer Mechanical Design

- 17 Making a Protocol Analyzer Producible and Serviceable

**18** Serial Data Acquisition and Simulation for a High-Speed Protocol Analyzer, by Mark D. Keisling, Dorothy J. Yackle, David B. Karlin, and Elizabeth Gates Moore The front end is a dedicated processor that interfaces the line under test to the system processor.

24 A Low-Cost, Portable Field Service Protocol Analyzer, by Vonn L. Black, Alan Delwiche, Chris L. Odell, and Stephen B. Tursich Special features include remote operation, Autoconfigure, and bit error rate testing.

**30** Remote Monitoring and Control of Semiconductor Processing, by Wesley H. Higaki This software module provides process engineers with both a window and a handle on the fab area.

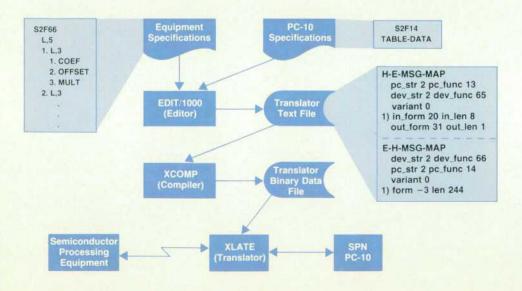

33 SECS

35 Authors

Editor, Richard P. Dolan • Associate Editor, Kenneth A. Shaw • Assistant Editor, Nancy R. Teater • Art Director, Photographer, Arvid A. Danielson • Support Supervisor, Susan E. Wright Illustrator, Nancy S. Vanderbloom • Administrative Services, Typography, Anne S. LoPresti • European Production Supervisor, Michael Zandwijken • Publisher, Russell M. H. Berg

### In this Issue

Not everything that gets transmitted over a data communication network is data. Each block of data is surrounded by synchronization characters and is usually followed by error detection bits. Between blocks of data there are overhead transmissions necessary to initiate, maintain, and terminate computer transactions. Each network uses a particular protocol, which is a definition of the synchronization and control characters and the format of data blocks and control messages. Each network also uses a particular data code. Fortunately, the number of protocols and data codes isn't as large as the number of networks. There are a handful of standard protocols and most

networks use one of them. The same holds for codes.

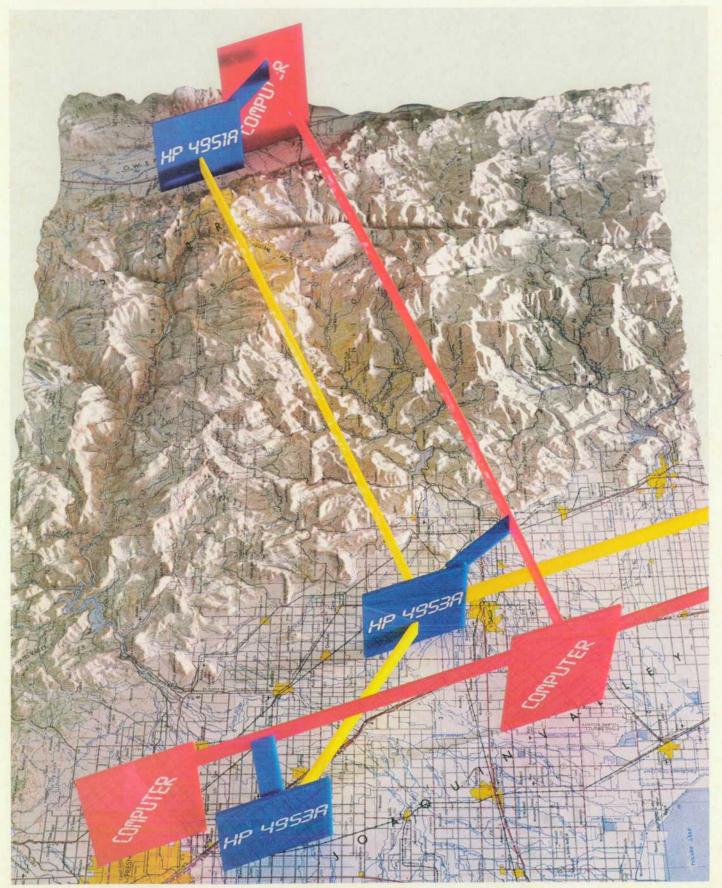

When there's trouble on the network, it isn't necessarily a hardware failure, and its effect might only be observable as a deviation, perhaps intermittent, from the required protocol. Protocol analyzers are instruments that are specially designed to monitor in-service data communication lines, trap errors, and provide enough information to isolate the source of an error to an individual component of the network. This issue gives you the design story of two Hewlett-Packard protocol analyzers. The HP 4953A, the subject of the articles on pages 4, 12, and 18, is for analyzing high-speed networks and is used mainly at computer centers, although it can also be used in the field. The HP 4951A, described in the article on page 24, is a lightweight, portable, field service analyzer for medium-speed networks. Both analyzers are capable of not only monitoring but also simulating data transmissions. This makes them useful for checking components of a network individually, or for verifying the operation of a component before it's installed in the network. Both analyzers are also capable of remote operation. One HP 4953A Protocol Analyzer can control and receive data from several HP 4953As or HP 4951As at remote sites. This means that one engineer or technician can test an entire network from a central site. Our cover illustrates this capability. Two special HP 4951A features help the field service technician: Autoconfigure determines the network's protocol and data code automatically, and bit error rate testing can eliminate the need to carry a separate instrument for this purpose.

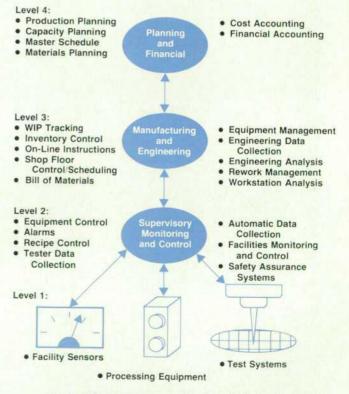

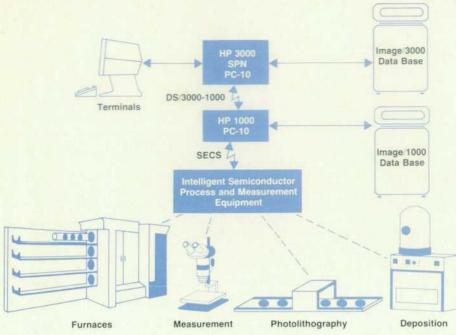

Hewlett-Packard's Semiconductor Productivity Network (SPN) is a group of integrated modules, primarily software, that are designed to automate the production of integrated circuit chips. The aim is to keep the yield of good chips high by correlating data from the entire factory to minimize yield fluctuations and discover their causes. By far the most important part of the operation is the process equipment, where temperatures and chemical concentrations are so critical that their control has always been something of an art. In the article on page 30, you'll meet the SPN module called PC-10, which is designed for direct monitoring and control of process equipment such as furnaces, ion implanters, and plasma etchers, as well as monitoring and measuring equipment. The outgrowth of work begun at HP's central research laboratories (see "A Process Control Network" in our June 1981 issue), PC-10 improves the repeatability of the production process, providing the predictability needed to get yields up and keep them there.

-R. P. Dolan

#### What's Ahead

In August, we'll have an article on the objectives and basic principles of HP's next-generation computers, which are now under development. Four articles will cover the design of the HP 3326A Two-Channel Synthesizer, a signal generator that produces either a pair of independent signals or a complex combination of two signals in the frequency range of dc to 13 megahertz. Another article will discuss TC-10, a module of HP's Semiconductor Productivity Network (like PC-10 in this issue). TC-10 takes data from various incompatible sources and makes it accessible wherever it's needed.

# A Protocol Analyzer for EDP Centers and Field Service

It's the latest member of a family that also includes a lowcost portable analyzer for field service and a high-speed BASIC-programmable analyzer for data communications research and development.

#### by Aileen C. Appleyard, Roger W. Ruhnow, William Grant Grovenburg, and Wayne M. Angevine

HE DEVELOPMENT OF COMPUTER NETWORKS has led to the need for reliable data communications, not only between elements of the network such as terminals and the CPU, but also between networks—for example, between several computer systems and a mainframe system.

Since these systems may not be at a common site, data needs to be transmitted from one site to another. This can be done using either dedicated lines or data networks. For two systems to exchange data, the data must be in a common format for both systems, and must contain overhead information—for example, the address of the unit to which the data is to be sent, what type of data is being sent, and error checking information. It is usual for the receiving system to transmit an acknowledge message in response to information received so that if some data is lost in transmission it can be retransmitted.

#### **OSI Model**

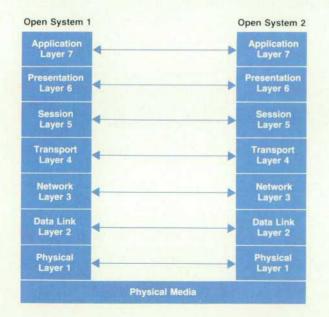

Networks are structured in levels, each level having a

Fig. 1. In the ISO Open Systems Interconnection (OSI) model, networks have seven layers. Communication takes place between like layers in different systems. specific function. One commonly used method of structuring a network is the ISO Open Systems Interconnection model, which has seven levels, as shown in Fig. 1.

The physical level transmits the digital data over the physical communications link. For example, the standard RS-232-C link uses a voltage of less than -3V for a mark (logical level one) and greater than +3V for a space (logical level zero). Other commonly used physical layer standards are RS-449 for systems operating at higher data rates, and X.21, which is commonly used in Europe on public data networks.

The function of the data link level is to ensure that errorfree data is received at the network level. This is achieved by partitioning the data into frames which are transmitted

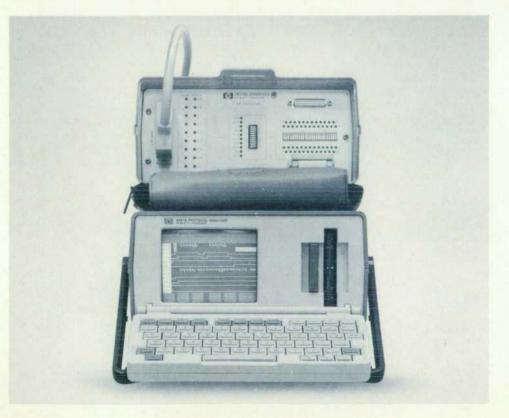

Fig. 2. The Hewlett-Packard family of protocol analyzers includes (top to bottom) the HP 4955A, a 72-kbps BASIC-programmable analyzer for datacom R&D, the HP 4951A, a 19.2kbps low-cost portable analyzer for field service, and the HP 4953A, a 72-kbps analyzer for field service and datacom center applications.

sequentially, and requiring a frame acknowledgment signal from the receiving system. If this signal is not received within a fixed time, the frame is retransmitted. This level also controls the rate of frame transfer, so that systems operating at different speeds can exchange data.

The network layer combines frames into larger groups known as packets and routes the packets to their destinations. This route would be fixed in a simple network, but in a more complex network the routing would vary according to system loading.

The transport layer accepts data from the session layer and splits it into smaller units for efficient transmission to the network layer. It also isolates the session layer from any impact of hardware changes in the system.

The session layer is the user's interface to the network. The user establishes a connection with a process on another machine in this layer, and billing information is contained in this layer.

The presentation layer performs text compression, encryption, and file conversion functions.

The application layer's function is determined by the individual user and typically is used to control the interface of two user programs on different machines.

#### **Protocol Analyzers**

The HP 4955A, HP 4953A, and HP 4951A Protocol Analyzers (Fig. 2) have been developed to aid in the design and maintenance of these networks.

The HP 4955A is primarily used in data communications research and development, where the features of highspeed operation to 72,000 bits per second and the BASIC programming language are required. The HP 4953A is used in the high-end field service area and in EDP centers, where speeds of 72,000 bits/s may be required, but in a less expensive and more portable instrument. The HP 4951A is used in field service, operates to 19,200 bits/s, and is a low-cost, easily portable instrument.

This article and the articles on pages 12 and 18 describe the capabilities and the design of the HP 4953A Protocol

Fig. 3. The HP 4953A Protocol Analyzer connects to the network under test through a network-specific interface pod. It has a menu-driven softkey user interface and a built-in cartridge tape unit for reading and storing data and applications programs.

## How Protocol Analysis Can Help

A problem situation that occurred at HP's Colorado Telecommunications Division illustrates how the HP 4953A Protocol Analyzer can be used to diagnose data communications difficulties. When a file was to be printed from an HP 3000 Computer, the response time of the printer was very slow. A line would be printed, then there would be a wait of several seconds before the next line was printed, which was unacceptable.

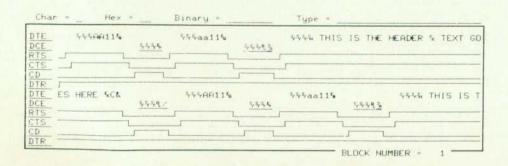

An HP 4953A was installed to monitor the activity between the HP 3000 (DCE) and the printer (DTE) during printer dump routines. It was discovered that the DTE was not returning an acknowledge character AK in response to the enquiry character EQ sent by the DCE. This was causing a timeout of the DCE of two seconds before the next block of text was sent to the DTE. This was measured using the HP 4953A's cursor timing feature.

To verify the problem, the HP 4953A was then configured to simulate the response of the DTE (Fig. 1). The printer dump routine was run with no timeouts occurring. The time from EQ to the start of the next block of text from the DCE was only four milliseconds, and the time to print a page of text was reduced by 59%.

```

Hewlett - Packard 4953A Protocol Analyzer

Device Emulating <u>DTE</u>

Transmission Mode is <u>FDX</u>

Interface Lead Control is <u>User Defined</u>

<u>plock 1:</u>

When DCE <u>5</u> then goto Block <u>2</u>

<u>Block 2:</u>

Send <u>5</u>

and then

Goto Block <u>1</u>

```

Fig. 1. Simulate menu.

Analyzer, the newest member of the family (Fig. 3). The HP 4951A is described in the article on page 24. Most operational characteristics are common to all three analyzers. For example, all three instruments use the same menudriven softkey approach in guiding the user through the selections necessary for correct operation.

A protocol analyzer has two main functions: to monitor data and to simulate data. In the monitor mode, the analyzer decodes data either from the internal buffer memory or from a line and displays it in a readily understandable format. Data in the internal buffer may have been stored there at an earlier time or transferred there from a DC100 cartridge tape. Data may be stored to tape and subsequently analyzed on any of the instruments.

The Setup menu is used to establish the characteristics of the system being used, including the protocol, the data rate, the data code, and the error checking scheme. These are all parameters that are defined by the network under test. The HP 4953A is able to operate with the SDLC, HDLC, X.25, X.75, SNA, DDCMP, Bisync, and asynchronous protocols.

The Monitor menu allows programs to be written to trigger the start and stop of the display and storage functions so that a large quantity of irrelevant data need not be scanned. For example, one of a group of terminals may not respond to data from the mainframe. This particular terminal's data flow can be examined by triggering on the address of that terminal and examining the data after this address. There are also five timers and counters, which can be used to select data to store or display—for example, by storing data to tape for a specified time after a trigger event or after a selected number of specified events (see Fig. 4).

The Simulate menu allows the user to select whether to simulate a DTE (Data Terminal Equipment)—for example, a keyboard or computer—or a DCE (Data Circuit-Terminating Equipment)—for example, a modem—and whether the transmission is to be full or half duplex. Programs are then written using the softkey-directed syntax to generate data in the format of the selected protocol and transmit it via the analyzer's interface pod to the line (Fig. 5). The leads of the interface pod can be set to simulate handshake sequences between DTE and DCE, and data strings can be specified so that a complete message can be transmitted.

The Display menu allows several different display formats to be selected depending on the protocol, so the user

Hewlett - Packard 4953A Protocol Analyzer

can easily look at the data of interest. DTE data, DCE data, or both can be shown on the display and, if required, the data can be separated into columns to decode the protocol header functions. In addition, data may be shown in conjunction with the logical state of selected interface leads.

The Run menu is used to execute the selected Monitor or Simulate menus. In the monitor mode it lets the user select the source of data, either on-line or from the internal data buffer, and in the simulate mode the analyzer is either allowed to free run or made to stop when the buffer or the tape (if selected) is full. The Execute key in this menu starts the analyzer running.

The Examine Data menu allows detailed analysis of the data that has been stored in the buffer using the selected monitor menu. In this mode it is possible to perform timing measurements between characters in the display.

The Mass Store menu allows control of the DC100 tape unit. The tape can be used to store buffer data and its associated menus, nonstandard data codes, and application programs.

The Printer menu allows the screen to be printed to an RS-232-C ASCII printer. Both menus and buffer data can be printed.

The Remote menu allows configuration of the HP 4953A as either a controller of up to 16 slave instruments or as a slave. After the configuration of the remote system, the operation to be performed remotely is selected. Functions available are uploading and downloading of data and menus and application modules. The HP 4953A may control or be controlled by an HP 4951A or an HP 4955A with certain limitations.

The Application menu is used to load and execute application programs written for the instrument. Typical programs include additional protocol decodes, tape edit programs, and high-level emulation programs that cause the instrument to simulate a network.

The Extended Tests menu is used for troubleshooting the instrument and directs the technician to a problem area.

#### Remote Operation

The features of the HP 4953A suit it to troubleshooting problems in data communications. These problems might arise from improper configuration of hardware or software, or from the failure of hardware components. The environ-

Triggers left = 51 Device Emulating DTE Transmission Mode is HDX Interface Lead Control is User Defined Block 1: DCE 1 8 88888888 88018888 88888888 88888880 then goto Block 2 Block 2: Increment Counter 1 Fig. 4. An HP 4953A program to and then use one of the five built-in counterl Beep timers to count data packets in and then Goto Block 1 DTE and DCE data.

Hewlett - Packard 4953A Protocol Analyzer

#### Device Emulating \_DTE\_

```

Transmission Mode is HDX

```

Interface Lead Control is User Defined

Block 1:

```

Increment Counter 1

and then

Send 1 <u>5</u> 10000011 EBP

and then

Send 1 <u>5</u> 00000000 THIS IS AN I FRAME EBP

```

If Counter 1 is > \_\_\_4 then goto Block \_3

```

Block 2:

```

```

Goto Block 1

```

```

Block 3:

```

Stop Tests

Hewlett - Packard 4953A Protocol Analyzer

| ADDRESS                                       | TYPE | DTE<br>N(S) |    | N(R) | INFO  | FCS         | ADDRESS TYPE    | DCE<br>N(S) P/ | F N(R) | INFO | FCS |

|-----------------------------------------------|------|-------------|----|------|-------|-------------|-----------------|----------------|--------|------|-----|

| 3                                             | SNRM |             | 0  |      |       | G           |                 |                |        |      |     |

| يق ايق ايق الحق الحق الحق الحق الحق الحق الحق | Info | 0           | 0  | 0    | THIS  | B           |                 |                |        |      |     |

| 3                                             | SNRM |             | 0  |      |       | G           |                 |                |        |      |     |

| B                                             | Info | 0           | 00 | 0    | THIS  | B           |                 |                |        |      |     |

| 3                                             | SNRM |             | 0  |      |       | G           |                 |                |        |      |     |

| 2                                             | Info | 0           | 0  | 0    | THIS  | ය සා ය සා ය |                 |                |        |      |     |

| 8                                             | SNRM |             | 0  |      |       | G           |                 |                |        |      |     |

| 3                                             | Info | 0           | 0  | 0    | THIS  | B           |                 |                |        |      |     |

| 3                                             | SNRM |             | 0  |      |       | G<br>B      |                 |                |        |      |     |

| 3                                             | Info | 0           | 0  | 0    | THIS. | B           |                 |                |        |      |     |

|                                               |      |             |    |      |       |             |                 |                |        |      |     |

|                                               |      |             |    |      |       |             | the third water |                |        |      |     |

|                                               |      |             |    |      |       |             |                 |                |        |      |     |

|                                               |      |             |    |      |       |             |                 |                |        |      |     |

| -                                             |      |             |    |      |       |             |                 | BLOCK NU       | MBER = | 1 -  | -   |

Fig. 5. An HP 4953A program (top) to transmit HDLC SNRM (set normal response mode) and the resulting display (bottom).

ment may be an existing system, an expansion of an existing system, or an installation of a new system. In most cases, the first person to troubleshoot the system will not have an extensive data communications background. Most likely, the troubleshooting procedure will be confirmation of software and hardware configurations and confirmation of hardware integrity. If these procedures are unsuccessful, then a system specialist or data communications specialist must get involved.

The specialist needs to examine the activity on the communication link. Tools available might include diagnostic trace listings provided by one of the communicating devices and/or protocol analyzers. Unfortunately, the data of interest is not immediately available. Either data must be collected at the site and delivered, or the site must be visited. Either case involves added expense and downtime for the customer. If data is delivered to the specialist, there is a danger that the data does not reveal the problem. On the other hand, site visits reduce the availability of the specialist. The remote feature set of the HP 4953A is tailored to reduce or eliminate these problems.

Using a local HP 4953A the specialist can remotely configure, execute, and obtain data from a remote HP 4953A. All that needs to be done at the remote site is to connect the appropriate pod on an HP 4953A to the link under test and attach the RS-232-C connector on the back panel to a leased or switched line via an asynchronous modem, matching the bit rate of the port to that of the modem. The specialist now has full control of the remote instrument. Any number of tests can be run and the results obtained for local analysis.

The remote feature set of the HP 4953A allows manipulation of all basic functions. From a controller, the following operations can be performed on a remote unit (slave). Upload and download are defined with respect to the controller, i.e., a menu is downloaded from the controller to the slave.

Movement of menus

Triggers left = 63

- Upload Setup, Monitor, Simulate, Run, and Display menus

- Download Setup, Monitor, Simulate, Run, and Display menus

- Manipulation of mass storage

- $\square$  Slave's mass store catalog

- Upload Mass Store menu

- Download Mass Store menu

- Execute slave's Mass Store menu

- Movement of data

- Upload timers and counters

- □ Upload captured data

#### Download captured data

- Manipulation of applications

- □ Slave's application module catalog

- □ Upload application module

- Download application module

- □ Execute slave's application module

- Delete slave's application module

- Information on slave

- □ Identify slave

- □ Slave's status

- □ Slave's memory use

- Miscellaneous control

- □ Soft reset slave

- □ Set slave's buffer size

- Lockout slave's keyboard

- □ Execute slave's Run menu.

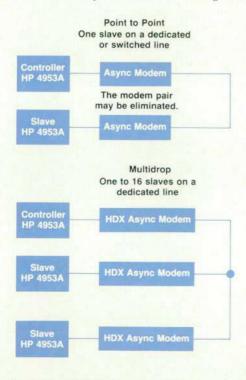

Both point-to-point and multidrop remote configurations are possible, as shown in Fig. 6. In the multidrop configuration, a controller HP 4953A can work with up to sixteen slaves. A particular slave is selected by an address field in the controller's Remote menu.

#### **Remote User Interface**

The HP 4953A's user interface is designed to be user friendly through the use of softkeys and menus. An HP 4953A is configured as a controller or a slave depending on which Remote menu (Controller menu or Slave menu) was last selected. The Controller menu allows modification of the remote link data rate, selection of the target slave, and selection of the desired slave operation. Once these selections have been made, the operation can be performed. Errors encountered by the controller during execution are

Fig. 6. Two HP 4953A remote configurations. In the multidrop configuration, a controller HP 4953A can work with up to 16 slaves.

| Header          |   |

|-----------------|---|

| Vector Routines |   |

|                 |   |

| Code            |   |

|                 |   |

|                 | - |

Fig. 7. Basic structure of an HP 4953A application module.

reported to the user as system errors. An example of a controller error might be, "The tape is out," following an operation to obtain the slave's mass store catalog.

The HP 4953A is a slave following power-up, a hard reset, or selection of the Slave menu. Once a slave, the instrument will respond to commands from a controller. The Slave menu allows modification of the remote link data rate. In addition, if a user at a slave wants to prevent a controller from modifying the state of the slave, controller operations can be disallowed via the Slave menu. The slave will then return an error for most operations received from a controller.

#### **Remote Implementation**

Remote operations use a half-duplex asynchronous protocol that guarantees data integrity across the communication link. A transaction sequence is the basic building block for remote tasks. There are four parts to the transaction sequence. First, the controller issues an operation code to the target slave. Second, the controller transfers data to the slave if required by the operation. Third, the slave returns a completion status to the controller. Fourth, the slave sends data to the controller if required by the operation. The first and third steps are required, while the second and fourth steps are optional. The following three examples illustrate these steps.

| Operation code | Data to slave | Completion status  | Data to controller |

|----------------|---------------|--------------------|--------------------|

| Reset remote   | None          | Operation accepted | None               |

| Upload menus   | None          | Operation accepted | Menus              |

| Download menus | Menus         | Operation accepted | None               |

The slave can reject an operation following the first or second step. For instance, if controller operations are disallowed by the slave and the controller initiates a download menus operation, the slave need not wait for the menus (step 2) to be received before it rejects the operation. On the other hand, the slave could accept the menus (step 2) only to find the menus are not compatible with it. If an operation is rejected, the reason is always sent to the controller in step 4. The reason is then presented to the user at the controller.

Some remote tasks, such as the examples above, require only one transaction sequence. Other tasks, such as uploading an application module, require several transaction sequences. This allows even complex tasks to be implemented using simpler operations.

#### **Applications Software**

The data communications test market is a very difficult one. The market is very fragmented, with each communications equipment vendor using a special protocol or variation of a standard protocol. To make matters worse, often a number of slightly different versions of a protocol exist because the standard changes over time. This fragmentation makes it impossible to design a completely general-purpose protocol analyzer.

The solution to this problem is applications software. An application is a program that is not built into the firmware of the instrument, but adds a function to the instrument when it is present. By the use of applications, the instrument can be customized for a specific new or different protocol without the cost and difficulty of a firmware change.

If a system is to be capable of supporting applications, some method must be devised to hook the new software modules into the system. Particularly in a softkey-driven system like the HP 4953A, new softkeys must appear when an application is present. Even more important functionally, when those new keys are pressed, the new software must be executed.

A complication peculiar to the HP 4953A is the multiprocessor architecture (see article, page 12). Applications may need to change the functionality of more than one processor. This means that there must be a way in which code brought into the unit through the system processor can be downloaded to and executed on, for instance, the front-end processor.

Fig. 7 shows the basic structure of an application module. The first block of data is a header, which contains information such as the name of the application and security flags. The header also contains four vectors, which are the offsets from the header to four functions within the application. These functions handle loading, deleting, resetting, and executing the module. The reset vector is called when a system soft reset occurs. The execute vector points to the top level of the application program if the application is executable. The load and delete vectors are discussed later.

An application may be executable or not. An executable application is one that can be run from a softkey in the applications menu. A nonexecutable application generally adds functionality to an existing menu, and therefore is not executed directly.

#### Installing an Application

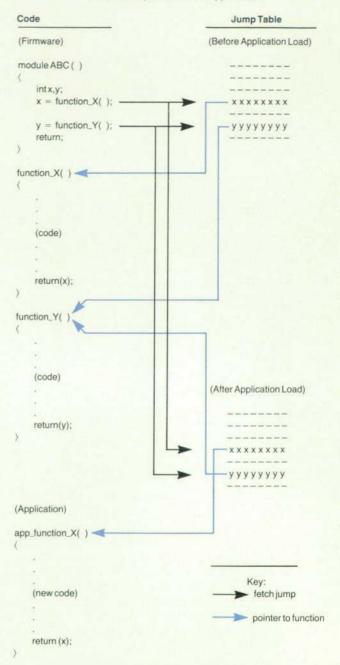

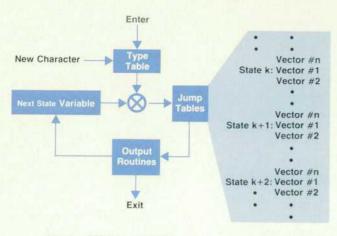

The problem of integrating applications into the resident firmware is solved through the use of jump tables (see box, page 10). The jump tables contain the addresses of every major routine in the system. The developer of an application simply chooses the functions that need to be changed to display a new softkey or call a new routine and replaces those functions with new versions by changing the entry for each routine in the jump table. Fig. 8 shows the replacement of a function.

The characteristics of system functions have a great deal

of impact on the ease of writing applications and the size of the applications produced. Good software engineering practice requires individual functions to be small and to implement a well-defined piece of the solution to some problem. These characteristics pay off handsomely when an application must modify the solution of a particular problem, because fewer and smaller functions have to be replaced.

This is where the load and delete vectors come into play. The load vector points to a routine that changes the jump table entries as needed by the application, and the delete

Function Replacement for Applications

Fig. 8. Application programs change the functions of softkeys or call new routines by changing entries in jump tables.

# **Protocol Analyzer Software Development**

Programming in the instrument environment provides opportunities that are somewhat different from programming in a mainframe environment. One of the historic constraints in a ROMbased instrument is the amount of code space available to the software designer, although this is beginning to change as the cost of memory drops. In the HP 4953A this obviously wasn't a severe problem, since we ended up with almost 350K bytes of code, but even so, we were beginning to push the limits of the available space. This space constraint caused the project team to employ slightly different methodologies from those we would have chosen given unlimited space and processor speed.

We realized that we were developing a large software system that would require several software designers. Since the user interface was organized as a set of menus, each of which was relatively decoupled from the others, each designer was given responsibility for a different menu. This resulted in the software being partitioned into a set of separately linked modules. This separate linkage of the modules in the system decoupled the designers from each other and made the possibility of undesirable interactions between modules less likely. In general, each module was in charge of modifying a set of global variables, which other modules would use as values but not modify. As an example, the Setup menu modifies the protocol specific parameters. The Display, Examine Data, and Run menus use these values but do not modify them. The modules range in size from 15K bytes to 45K bytes. As large as some of these modules are, they were much more controllable than a single module of 350K bytes would have been

At power-on the kernel module calls the performance verification module, which does a thorough test of the hardware. Assuming that the hardware is healthy, the performance verification code returns control back to the kernel which then calls the initialization routines located in each of the modules. Once the machine has been initialized, the main-level display is presented and a user response is awaited. When the user decides to enter a particular menu, control is transferred to the appropriate module. Within the menu, the user can modify the parameters as-

vector points to a routine that reverses these changes. The one major liability of this system is its inability to handle more than one application changing a given jump table entry at a time. Obviously, if application A is expecting its copy of function X to be executed, while application B, loaded later, also changes the entry for function X, application A will be gravely disappointed. The system prevents this conflict by not allowing the loading of a second application conflicting with one already present.

Applications that need to modify the way that data is brought into the analyzer must change the code on the front end, which uses a separate processor. Hooks are provided by the front-end program to allow the application code to be downloaded into the front-end processor's memory. This code is then accessed through a command table, also downloaded into the front-end processor's memory, which replaces the existing table. The command table is very similar to the jump tables on the system side. The new command table may access any functions normally resident in the front end as well as new functions defined by the application code. sociated with that menu. For example, modifying Display menu parameters changes the way the Examine Data or Run menus present the data to the user. The changes to the data base are usually under softkey control and protect the user from mistakes. A high level of help is provided through this softkey interface, since each softkey selection automatically relabels the softkeys presenting the user with the next set of selections.

Since all of the software designers had a need to access the I/O devices of the HP 4953A, such as the display and the keyboard, a standard library was implemented. All of the user interface software was implemented in the C programming language, so it made sense to provide a C standard library for the use of the software designers. Because of the position dependent nature of the user interface menus, a superset of printf and scarf was implemented that allowed cursor and attribute control of the display. Since the HP 4953A allows the user to operate in several data codes, such as ASCII and EBCDIC, scarf was modified to allow the input from the keyboard to be returned in the requested data code. The implementation of the standard library allowed the software designers to gain command of the I/O functions in the HP 4953A very quickly, since the commands closely follow the conventions established by C.

The design team acknowledged early in the project that a system of the size we were developing was highly unlikely to be error-free, so the team implemented jump tables through which all routines are accessed. These jump tables are located in an EPROM by themselves, the theory being that, if and when bugs are found, the jump vector of the errant routine can be replaced with a vector to a replacement routine located in the space left in the jump table EPROM. In this way, a field update can be effected by replacing only the existing EPROM with a new one that contains the updated jump table and the patched code.

William Grant Grovenburg Development Engineer Colorado Telecommunications Division

#### The Application Menu

The user interfaces with the applications handler of the HP 4953A in the same way as with any other function of the instrument: through a menu. The Application menu looks like Fig. 9. There is a catalog of the applications that are loaded, showing the name, size, and description of each. The user can scroll through the catalog using the cursor keys. At the bottom of the screen are memory use statistics, showing the total size of the applications loaded, the available space, the data buffer size, the largest block of contiguous space available, and the number of blocks of data present in the data buffer.

Softkeys available in the Application menu depend on the application selected by the cursor in the application catalog display. The Load application, Buffer size, and Exit keys are always present. If the selected application is storable, a Store application key appears. If the application can be deleted, a Delete application key appears. If the application is executable, an Execute application key appears. In line with the general philosophy of the instrument, invalid choices are not presented to the user.

The mass storage and remote facilities of the HP 4953A

Hewlett - Packard 4953A Protocol Analyzer

| 10. | Name   | Group | Size | Type  | Description               |

|-----|--------|-------|------|-------|---------------------------|

| 1   | APRINT |       |      | 4953A | ASCII Printer             |

| 2   | BSCX25 |       | 16   | 49538 | BSC-X.25 Decode           |

| 3   | CHAIN  |       | 40   | 49538 | Chained Menus Application |

| 4   | J15-8  |       | 40   | 4953A | Katakana Character Set    |

| 5   | SNA    |       |      | 4953A | SNA Decode                |

| 6   | TEDIT  |       | 16   | 4953A | Tape Edit Application     |

| 7   | X.21   |       | 32   | 4953A | X.21 Decode               |

|     |        |       | -    |       | and account               |

|     |        |       |      |       |                           |

Applications loaded: 152 Kbytes Data buffer size: <u>256</u> Kbytes First buffer block: 1 Available space: 40 Kbytes Largest block: 40 Kbytes Last buffer block: 1

Fig. 9. HP 4953A Application

are used for applications storage and transfer. Applications may be stored and loaded from tape and uploaded or downloaded to or from a remote unit. A simple security scheme is implemented on tape or remote transfers. An application may be storable, nonstorable, or a master application. A master application can be copied, but its copies cannot be copied. Most application programs sold for the HP 4953A are masters. This security scheme is maintained by the tape editing program that comes with each HP 4953A.

Memory to store applications is traded off with memory for the data capture buffer. In an HP 4953A with Option 01 (expanded memory) there is a total of 448K bytes to be divided. The data capture buffer must be a minimum of 16K bytes, leaving 432K bytes for applications. If the maximum data capture buffer size of 256K bytes is needed, 192K bytes is left over for applications.

#### Performance

Performance in a protocol analyzer is a function of several factors. First, there is front-end speed, or how fast the machine can receive and transmit data from the data communications line under test. The HP 4953A can communicate at data rates up to 72,000 bits per second full-duplex and up to 256,000 bits per second in a monitor-only mode with external clocking for bit-oriented protocols (BOPs). The critical section for front-end speed is the data link controller (DLC, see article, page 18). The DLC is responsible for converting the bit stream on the data communications line into the characters for character-oriented protocols (COPs) or into the frames associated with BOPs. Obviously, the front end must keep up with the bit rate of the data communications line under test, or all is lost. For the DLC to simulate or emulate, it must be able to drive the data communications line at speed. It is also desirable to be able to maintain the data rate for an indefinite period of time. The ability of the machine to drive a data communications line without pausing between chunks of data is known as utilization. In the HP 4953A there is a relatively constant time between the end of one chunk of data and the beginning of the next. This causes the utilization for small strings of data (10 characters) to vary from 95% at 1200 bps to 99.8% at 72 kbps. For large strings (100 characters), utilization varies from 99% at 1200 bps to 99.9% at 72 kbps.

Another measure of performance for a protocol analyzer is the number of simultaneous triggers that may be active at once and the complexity allowed in specifying those triggers. The HP 4953A allows up to 63 trigger characters. The 63 characters may be treated as 63 separate triggers, each of which specifies a different action when found, or may be combined to form larger complex trigger strings up to 63 characters in length. For each character in a trigger, the HP 4953 has the ability to test against the complement (NOT) of that character or mask out bits of the character. The HP 4953A can also trigger on special characters such as start and end flags, frame check sequences (FCS), and framing or parity errors.

Two decisions made early in the HP 4953A development were that it would run as close to real time as possible and that it would not allow any data to be lost. This had a very definite effect on the architecture of both the hardware and the run-time software. Often protocol analyzers collect data from the data communications line and put it into a large memory buffer where they can analyze the data at their own speed. This is called postanalysis, and it has one side effect: it allows the point of analysis to fall behind what is happening on the line. To force the HP 4953A to keep up with real time, the point of analysis has been moved out of the data buffer into the data stream between the DLC and the data buffer.

It is important that the protocol analyzer quickly respond to a trigger event, perform the actions required as a result of finding the trigger, get set up for the next trigger, and start analysis again. A small FIFO (first in, first out) buffer is inserted at the output of the DLC to allow the analyzer time to set up and get running again after it has stopped as a result of having found a trigger. This brings the difference between real time and the point of analysis in the HP 4953A to at most the size of the FIFO plus a character or two of buffering in the DLC. Staying close to real time gives the HP 4953A the ability to respond to events on the data communications line very quickly.

#### Acknowledgments

Richard Zulch was responsible for the architecture of the application programs. Betsy Perkins made a major contribution to the software quality assurance effort.

# Simple Architecture Provides High Performance for Protocol Analysis

by Stephen H. Witt and Roger W. Ruhnow

HE HP 4953A is a general-purpose high-performance protocol analyzer that is capable of monitoring serial data streams at 256 kbps and simulating serial data streams at 72 kbps. The HP 4953A is also capable of recognizing data patterns in the data stream and responding to these patterns with a variety of menu functions. A primary design consideration for the HP 4953A was to perform as a real-time monitor. This means the analyzer must process, display, and store measurement data without falling behind the activity occurring on the network under test. A second concern was cost. The instrument is intended for generalpurpose use and must be affordable. A third consideration was size and weight. The analyzer must be portable. Therefore, a simple system architecture was chosen, one that would be inexpensive and portable, and would perform well.

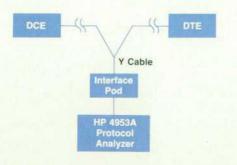

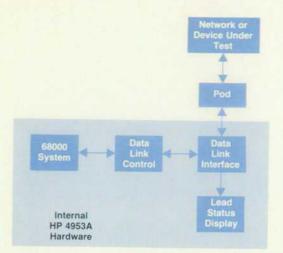

The protocol analyzer interfaces to the line under test via an interface pod. The pod provides the physical and electrical connections between the Data Terminal Equipment (DTE) or the Data Circuit-Terminating Equipment (DCE) and the HP 4953A Protocol Analyzer (see Fig. 1).

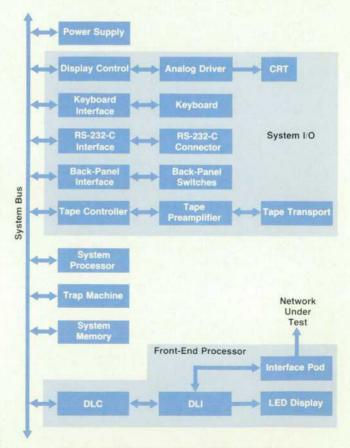

There are six major blocks in the system, as shown in the block diagram, Fig. 2:

- System processor

- System memory

- System input/output

- Trap machine

- Front-end processor

- Power supply.

The system processor, system memory, and I/O assemblies make up a special-purpose computer that interfaces to the front-end processor and the trap machine. The front-end processor provides the necessary control of the interface to the network under test. The trap machine provides data analysis (triggering capability) of the data being acquired.

Fig. 1. The protocol analyzer interfaces to the line under test by means of an interface pod.

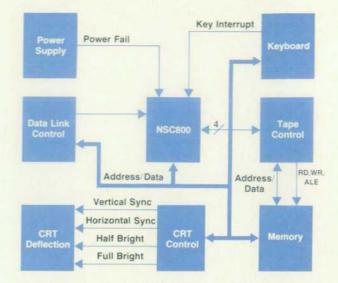

#### System Processor

The system processor provides processing and control for the HP 4953A. All other blocks in the system communicate with the system processor via memory mapped I/O (see system processor address map, Fig. 3). The system processor consists of an 8-MHz 68000 processor (CPU), program memory, address decoding, timers, DMA control, and interrupt control. Most of the system bus interface signals originate on the system processor. Board enable signals (to communicate with the other blocks via memory mapped I/O), the system reset signal, the system clock (16 MHz), the bus error signal, and the data transfer handshaking signals are generated by the system processor.

#### System Memory

The system memory consists of the ROM array (384K bytes) and the RAM array (standard 128K bytes or optional 512K bytes). Both the ROM and the RAM are 16 bits wide. This is system memory that is directly addressable by the 68000 and is not accessible to any other processor. The

Fig. 2. HP 4953A Protocol Analyzer block diagram.

ROM array contains all the system software.

- The RAM array is segmented as follows:

- System RAM: 64K bytes

- Data capture buffer: 16K to 256K bytes

- Application program space: 0 to 432K bytes

The system RAM is fixed in size. The data capture buffer and the application program space sizes are designated by the user through software control. More details of the operation of the data capture buffer and the application program space can be found in the articles on pages 18 and 4, respectively.

#### System I/O

All user interaction with the HP 4953A is accomplished via the system I/O, which consists of the keyboard and keyboard interface, the CRT display, the RS-232-C interface, and the system mass storage tape subsystem. It is only through these I/O interfaces that the user can alter the configuration of the system.

The keyboard is used to control the operation of the instrument through menu entry and interaction with data. The keyboard I/O section includes a full ASCII keyboard with eight softkeys mounted to the front of the instrument with hinges that allow for pivotal movement. It interfaces to the system processor through the keyboard interface circuitry, which interrupts the processor when a key is pressed. The system processor then reads the keyboard register to determine which key was pressed.

The RS-232-C interface exists for two purposes: to access a printer and to provide remote control. The system processor communicates with the RS-232-C interface through memory mapped I/O registers. Back-panel switches are

| Standard System RAM<br>128K Bytes                                                 |

|-----------------------------------------------------------------------------------|

| Extended System RAM (Optional)                                                    |

| 512K Bytes                                                                        |

| System ROM (System Program Memor<br>384K Bytes                                    |

| Trap Machine Registers                                                            |

| Data Link Control Registers                                                       |

| Tape Controller Registers                                                         |

| Keyboard Register                                                                 |

| RS-232-C (ACIA) Registers                                                         |

| Back-Panel Registers                                                              |

| CRT Controller Registers                                                          |

| Display RAM<br>8K Bytes                                                           |

| System Processor DMA Control                                                      |

| Registers                                                                         |

| System Processor Timer Registers                                                  |

| System Processor DMA Page Latch                                                   |

| Performance Verification Display<br>Register                                      |

| Beeper, Performance Verification<br>Switches, and Memory Size Jumper<br>Registers |

Fig. 3. HP 4953A system address map. The 68000 system processor communicates with the other blocks in the system via memory mapped I/O. used to set the address of slave units in a controller/slave remote control environment. They are also used to select a baud rate to which the instrument defaults at power-on. After power-on, the baud rate may be changed via softkey selection.

The tape section of the I/O subsystem is made up of the tape controller, the tape preamplifier, and the DC100 tape transport. The tape system provides storage of a user's menus, buffer data, run data, or application programs. Data is transferred from the tape to the system processor or vice versa using direct memory access (DMA). The 68000 deals in logical blocks of data referred to as records. It sends the tape subsystem commands to control these blocks of data.

The tape controller is made up of a system bus interface to the system processor, an 8039 processor, a state machine, a servo control loop, and the tape preamplifier. The tape preamplifier buffers the low-voltage signals between the tape transport and the tape controller. The DC100 tape transport assembly consists of the motor assembly, the read and write heads, the hole detection mechanism, the hardware for holding the tape cartridge, and the hardware for ejecting the tape cartridge.

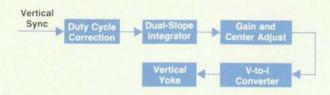

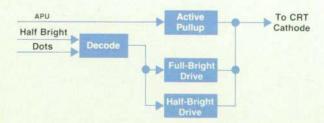

The display is made up of the digital controller assemblies, the primary display driver (high-voltage board), the secondary display driver (sweep board), and the 9-inch CRT display tube.

The CRT controller assemblies provide all of the digital mapping from the display memory in the system processor address space to the analog circuitry that controls the electron beam for energizing the CRT tube. The display memory is accessed by the system processor in a normal 68000 write mode via memory mapped I/O.

The display uses a raster-scan system and is character based. The screen can hold 25 lines of 80 characters each for a total of 2000 characters per display. The CRT controller can implement both normal and large ( $2 \times$  in each dimension) characters. The normal size characters use  $7 \times 9$ dots in a  $9 \times 15$ -dot character cell. Large characters use  $14 \times 18$  dots in an  $18 \times 30$ -dot cell.

Four character sets are available for the display: ASCII, EBCDIC, hexadecimal, and specials. The special character set provides datacom characters (e.g., start flags, stop flags, frame check sequences) and line drawing characters (for timing diagrams and display borders). The user may define a character code set that uses the ASCII character set for its printable characters. The system processor performs the character-set mapping function from a table loaded from tape or keyboard. This mapping function is transparent to the CRT assembly. If no printable character exists for a code, the hexadecimal character is displayed.

Character attributes include half bright, underline, inverse video, cursor (alternates between inverse video and normal video at 4 Hz), overline, and blinking (the cell is blanked at 2 Hz).

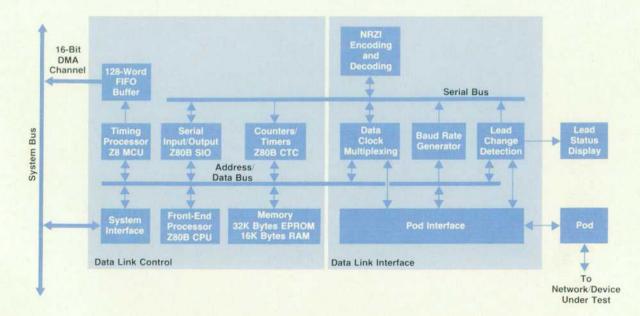

#### Front-End Processor

The front-end processor is made up of the data link interface, the data link control, the LED display, and the interface pod. These assemblies interface to the system processor as one entity through the data link control. The data link control (DLC) provides the intelligence required to (continued on page 15)

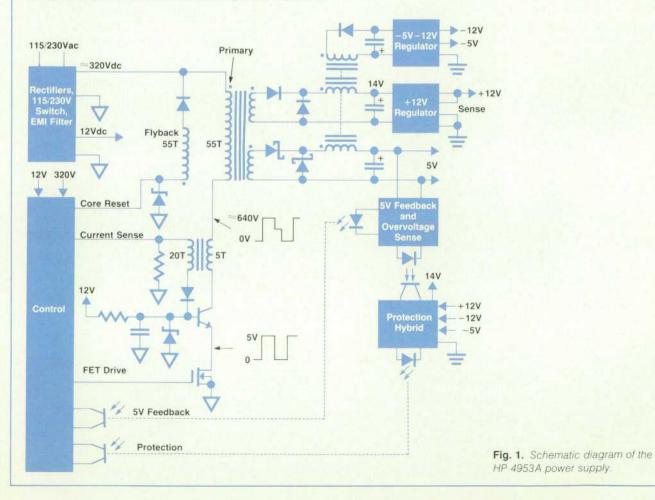

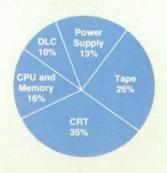

# Protocol Analyzer Power Supply Design

The internal power requirements of the HP 4953A are +5V at 10A, +12V at 4A, -5V at 0.1A, and -12V at 0.1A. The +12V output runs the display, the tape drive, and the fan. These subsystems place certain constraints on the supply. For instance, the display is sensitive to small voltage variations, while the tape motor and the fan have large current surges. The power supply also had to pass VDE level B for EMI and the design time needed to be short.

Given the above constraints, a switching type supply was designed with linear regulators on the +12V, -12V, and -5V outputs. Three-pin regulators are used on the -5V and -12V outputs. A remote-sensed regulator is used on the +12V output instead of isolating the display supply with a separate regulator. This minimizes the number of outputs that need protection. A low-dropout (1V) regulator is used to increase efficiency.

The switching circuit (Fig. 1) is a forward converter operating at 50 kHz. A forward converter transfers power to the output when the switching transistor is on. A transistor and FET combination is used for the switch: a low-voltage FET switches a highvoltage bipolar transistor in the common-base configuration. This yields lower cost and is more rugged that a single bipolar transistor or FET.

The main switching transistor is protected by a comparator that senses the instantaneous current in the transformer primary. If the current exceeds a preset value, the switching pulse is turned off early. This limits the current during an overload condition. If the overload is sustained for more than 50 ms, the supply turns off and remains off. The ac power must be turned off for at least five seconds to resume normal operations when power is reapplied. The supply will also shut down if any output is 10% over its specified voltage for more than  $10\mu$ s. The +12V, -12V, and -5V regulators have individual current limiters. However, power dissipation in the regulators is large when they are current limiting. To prevent damage, the supply shuts down if any of these outputs is 10% under specified voltage for 50 ms. These time delays ensure that turn-on and load surges will not trip the protection circuitry. The protection circuitry is fabricated on a thick-film hybrid to reduce cost and save board area.

Normally in a power supply of this type, filter networks called snubbers are used on all of the transformer windings to reduce voltage transients that could damage the semiconductors. These networks are eliminated by using bifilar windings on the transformer's primary and flyback windings, and by using the most recent technology available for the rectifiers.

> Stephen M. Ernst Development Engineer Colorado Telecommunications Division

#### (continued from page 13)

acquire data, translate data, provide timing, provide data, and perform all other tasks necessary to interface with a user's network. The data link control is made up of two microprocessors operating in parallel: a Z80 and a Z8. The Z80 has 32K bytes of EPROM program memory and 16K bytes of RAM storage. It executes the protocol code. The Z8 has 2K bytes of ROM and 256 bytes of RAM, both internal to the part. The Z8 handles the interface lead status and the timing functions, and puts the data in the capture buffer. The Z8 is called the timing processor. Details of the front-end design are in the article on page 18.

#### **Trap Machine**

The trap machine scans the DLC data from the HP 4953A front end for user-programmed character sequences, lead status changes, and errors or specials (conditions not specified by other data types) in data link protocol. The trap machine interfaces to the system bus and controls DMA transfers from the data link control to the system memory. Data patterns are scanned as they "pass by" on the system bus. On finding a trigger sequence, the trap machine reports trigger information to the system processor.

The trap machine has a mask field and an instruction

field associated with each trigger character. The mask field allows "don't care" conditions to be specified on a bit-bybit basis. The instruction field is used to specify trigger type and NOT conditions in addition to containing some reserved fields for system use. There are 64 available triggers, one of which is reserved for system use.

The trap machine keeps track of the time information and the interface lead status information put into the data capture buffer so that the condition of the interface can be reported to the system processor when a trigger is reported.

The trap machine consists of a C2000 gate array, a few TTL integrated circuits for system interfacing, and three NMOS RAMs.

In this description, several references are made to DLC data types. These formats are the same as for buffer memory and are described in the article on page 18.

#### **Trigger Definition**

A trigger is a sequence of characters or elements that the user wants to match in data received from the DLC. A user defines triggers in the Monitor and Simulate menus to direct run-time execution. Each element of a trigger consists of three bytes: a character byte, a mask byte, and an instruc-

## **Protocol Analyzer Mechanical Design**

The HP 4953A Protocol Analyzer uses standard HP cabinetry, but is the first 7-inch-high, full-width cabinet in a 10.6-inch depth used in the corporation. This nonstandard depth was chosen because the HP 4953A is frequently used as a field service instrument. As a result, low weight and a size capable of fitting under an airplane seat were important constraints.

The nine 6×9-inch digital boards load from the top of the HP 4953A into a bottom-mounted backplane and run parallel to the front of the instrument. For serviceability, the boards can sit atop an extender card and face the front for easy access to either side of the board. The two-piece connectors are staggered across the backplane so that it is physically impossible to mate a digital board into the wrong slot. The two CRT driver boards, which, with top and bottom covers removed, hinge out of the instrument for easy servicing, and the display tube consume nearly all of the remaining volume inside the box. This leaves insufficient room for the power supply. Consequently, the power supply mounts vertically inside the rear panel, which protrudes out the back of the instrument. The standard rear feet were therefore too short to allow operation of the instrument while standing on its rear feet with the necessary interface cabling connected to the rear panel. Consequently, a rear foot was tooled that is one inch longer than standard to provide the necessary additional ground clearance.

With no room on the rear panel for the necessary cooling fan, the fan was mounted on the side. It draws ambient air through the right side cover across the digital boards and power supply, and exhausts it out the left side.

On the front of the instrument is a full, nondetachable, folddown keyboard lockable at any desired angle. The front panel has a 9-inch monochrome CRT, a line switch, a DC100 tape transport, and a bank of 44 LEDs. The LEDs, 22 red and 22 green, indicate the status (on and off or mark and space) of the interface lines of the system under test. Because there exist several interface standards throughout the world, each with differing numbers of lines and differing nomenclature associated with each line, a simple means of changing the number and names of these lines' status indicators was needed. An overlay card that snaps into the front panel over the LEDs was designed for each interface. Only the correct number of LEDs can be seen through each overlay, each with its proper nomenclature.

The hinge mechanism on the fold-down keyboard extended below the plane of a standard HP bottom foot, which snap-mounts onto the bottom cover. Other feet used throughout the company were inappropriately tall for use on the bottom of the instrument. As a result, a new bottom foot, which uses a fold-down tilt stand similar to the one used with the standard bottom foot, was tooled. This new foot mounts to the front frame instead of the bottom cover.

The HP 4953A's handle is a formed, rigid metal strap with a molded hand grip. It mounts to the sides of the front frame. A side strap recessed into the side panel (typical on many HP instruments) was rejected for two reasons: first, it cut down the available path for airflow through the cabinet by nearly 50%, and second, the form factor for carrying the instrument in this orientation made it awkward and uncomfortable.

The field service environment in which the HP 4953A is frequently used demands that it be especially rugged. The instrument was tested to HP's new class B-1 standards for shock and vibration. No failures were found during either resonant vibration dwelling, or during random vibration testing. In shock tests, the instrument withstood at least 56g before experiencing unacceptable damage. Even at these shock levels, the damage was to the outer structure and did not affect the proper operation of the instrument.

> Ken Krebs Development Engineer Colorado Telecommunications Division

tion byte. The mask byte contains the bit pattern the user wishes to AND with the received DLC character before comparing it to the character byte. An example of masking would be the elimination of the ASCII parity bit. The character byte contains the byte the user wants to use as a trigger element. The instruction byte contains the trigger type, comparison criteria, and flags indicating if this element is the start of a trigger, the end of a trigger, and/or the last trigger element to be considered before obtaining a new DLC data character. The comparison criteria possible are equal and not equal.

The three NMOS RAMs hold the trigger triplets. Sixtyfour triplets are available, 63 for the user and one for the system. These can be partitioned into a number of triggers, each having a variable number of elements. If all of the user's elements are used, there can be from one trigger of 63 elements to 63 triggers of one element each. Triggers are entered into RAM from the lower addresses through the higher addresses. The trigger byte is entered into the character RAM, the mask byte is entered into the mask RAM, and the trigger type, comparison criteria, and trigger flags are entered into the instruction RAM. If the triplet is the first in a trigger, the start flag is set in the instruction RAM. If the triplet is the last in a trigger, the end flag is set in the instruction RAM. If the triplet is the last defined in RAM, the last flag is set in the instruction RAM. A trigger can be defined but rendered inactive by not setting its start flag. These RAMs are read from and written to by the system processor and are accessed by the gate array while the trap machine is running.

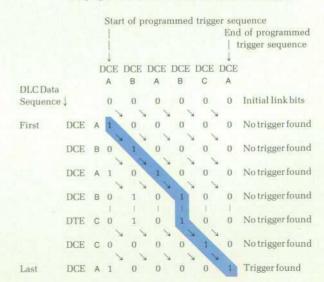

#### Search Algorithm

When searching for a programmed trigger, the trap machine uses the concept of a link bit to indicate the progression of a trigger sequence. A link bit is one bit of information associated with each trigger element. By definition, a link bit associated with a trigger element is set if and only if a sequence has been found in the DLC data that matches the trigger sequence through that trigger element. For example, if a trigger consists of trigger elements DTE A, DTE L, and DTE M, and the data received from the DLC is DTE A and DTE L, the link bit associated with the trigger element DTE L would be set. As the trap machine continues to receive DLC data that matches the trigger sequence, the link bit will move (or propagate) from trigger element to trigger element until it propagates to an element with the end flag set. In this case the trigger has been satisified.

There are several restrictions on the propagation of a link bit. If the type of the received DLC character is not the same as the trigger type, the link bits for that trigger are not modified. This property allows a trigger sequence to be unaffected by DLC data types other than its own. If the trigger type is the same as the received DLC character then the propagation of the link bit is controlled by additional considerations.

The mask byte is ANDed with the DLC character and the result is compared with the character byte. This result must match the comparison criteria specified in the trigger element's instruction byte. If these criteria are not met, the link bit is set to zero, terminating the propagation of any link bit by that element. This occurs when the DLC data sequence fails to match the trigger sequence through that element. If the comparison criteria are met, the link bit will be set if and only if the link bit of the previous trigger element was set before its last evaluation, or this element is the start of a trigger (its start flag is set).

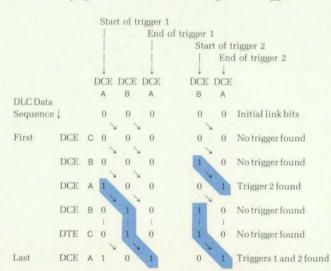

As an example of the above rules, consider Table I. The top row is a programmed trigger sequence consisting of the DCE ASCII characters A. B. A. B. C. and A in that order. The leftmost column shows the data sequence received from the DLC, consisting of the DCE ASCII characters A, B, A, and B, DTE ASCII character C, and DCE ASCII characters C and A, in that order. Since the DTE character is not the same type as the trigger elements, it is ignored and is essentially removed from the DLC data sequence. If this is done the DLC data sequence appears identical to the trigger sequence, so a trigger is present. The table is the set of link bits associated with the trigger elements. The column of ones and zeros under a trigger element shows the link bit for that element. The link bits are initialized to zero before the searching algorithm begins, as seen in the first row. While a DLC character is being compared to the trigger sequence(s), the link bits are changed to the values shown in the corresponding row of the DLC data word. When the link bit becomes set for the last element in the trigger sequence, a trigger has been found.

As mentioned, the link bits must first be set to zero to prevent false triggers, since they represent propagating trigger sequences. The first DLC data word is DCE A. This word is compared to all of the trigger elements in order from left to right. The first element is DCE A. Using the conditions for link bit propagation, it is easy to see that only the link bit associated with DCE A will become set.

The second DLC character is DCE B. As this word is sequentially compared to the elements in the trigger, it can be seen that only the first trigger element DCE B satisfies all conditions, so its link bit is set. The third received DLC data word is DCE A. As this word is sequentially compared to the elements in the trigger, two link bits are set. The second link bit becomes set because the trap machine rec-

#### Table I

#### Propagation of link bits through a trigger

# Making a Protocol Analyzer Producible and Serviceable

Producibility and serviceability are important issues in any product design. To achieve both goals, it is important to have effective performance verification software, which indicates whether the instrument is functional, and enough additional hardware and software to allow any failures in the instrument to be located quickly. It is also important that the additions to the instrument needed strictly for performance verification and troubleshooting be kept to a minimum to keep production cost as low as possible. For example, to service the HP 4953A hardware, no electronic tools or extender cables are needed. All of the boards are readily accessible and each has been designed to be easily repaired.

Test points to be used for signature analysis (SA) troubleshooting are located at the top of each board to provide for easy hookup of the signature analyzer probe when the boards are in the cardcage. The test points consist of two rows of X M-post-type connectors (where X is the number of test points), rather than the conventional single test points. Using the connectors, SA probes can be attached quickly without using the clips supplied with the SA probe. The double row of test points allows more than one connection to be made to each test node. In addition, using connectors for test points allows all of the test points to be loaded at one time, thus reducing production cost.

M-post-type connectors are also used to implement the many jumpers required to break feedback loops for SA troubleshooting. Using the connectors instead of the more common DIP jumpers conserves board space and makes it much clearer which jumper position is normal and which position is for troubleshooting.

Over seventy performance verification and troubleshooting tests were written for the HP 4953A. The same code is used for performance verification and signature analysis as much as possible. This reduces the amount of code needed and avoids the

ognizes that another trigger sequence is being received with this character as the first element. This property is desirable in the detection of overlapping triggers. Many link bits in a trigger can be set at any given time.

An interesting item is the reception of the DTE C character from the DLC. The link bits should not be changed with the reception of this character, so the trap machine simply copies the link bits, as indicated in the table. The trigger is finally found when the link bit in the last DCE A trigger element becomes set.

It is possible to be searching for more than one trigger at a time. This is accomplished by sequentially comparing the DLC character to all triggers before requesting another DLC character. When considering multiple triggers, link bits from one trigger do not affect another trigger. Table II shows an example of two triggers.

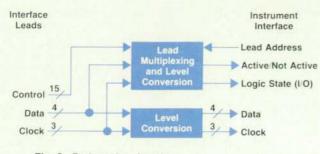

#### **Data Flow Description**

Data is provided to and acquired from the network under test by the interface pod. The network data consists of serial data, clocks, and interface control leads. The interface pod recognizes voltage levels and changes on the interface and converts these voltages into TTL levels that can be interpreted by the digital hardware in the HP 4953A. The interface pod interfaces to the data link interface (DLI). The DLI interprets the data, clocks, and leads and displays this information by writing to the LED assembly on the front problem that sometimes arises when performance verification detects a problem in a circuit, but separate SA software stimulates the circuit in a different manner, so the failure cannot be located.

The majority of the tests are executed each time the instrument is powered-on and take less than eight seconds to complete. Tests that require user interaction, such as the tape test, are accessible through a top-level softkey.

The tests are numbered in the order they are executed. Since testing begins at the heart of the instrument and works outwards, troubleshooting begins with the failing test having the lowest test number. Any test can be individually cycled for SA troubleshooting or for finding intermittent failures by setting a switch located on the CPU board to the desired test number and pressing the reset button. Switch settings are also available for cycling particular groups of tests or for cycling all of the tests and outputting the results to a printer.

Most test failures are displayed on the CRT. However, before the CRT can be used to display failure information, there must be some confidence that the CRT circuitry itself is functional. Therefore, the power-on tests are divided into two sets, the first dedicated to testing the circuitry needed to access the CRT display. If any of the tests in the first set fails, the failure is indicated by repetitively displaying the test number of the failing test on a seven-segment display located on the CPU board. Most of the remainder of the HP 4953A is tested by the second set of poweron tests. Any failures in this set of tests are displayed on the CRT.

> John R. Rader Development Engineer Colorado Telecommunications Division

panel.

The DLI detects interface lead status changes and passes this information along with the data and clocks from the interface pod to the data link control (DLC). The DLC converts the serial data into an 8-bit parallel format, keeps

Table II

Propagation of link bits through two triggers

track of 16 bits of relative time, and maintains the status of 15 interface control leads. Time stamps and information identifying the data type (see "Data Capture Buffer," page 22) are added to the 8-bit data byte, forming a 16-bit word. The DLC recognizes specific protocol events on the network under test and identifies these by generating "specials" for insertion in the buffer. The 16-bit words are passed from the DLC to the system memory via a 16-bit DMA channel that is maintained by the system processor.

The trap machine controls the flow of data from the DLC to the system memory by acknowledging the DLC's DMA requests to the system processor. The trap machine reads the data during each DMA cycle as it is transferred to the system memory. The trap machine is programmed to detect user-entered trigger sequences. When a trigger sequence is detected, the trap machine interrupts the system processor and reports the trigger. The system processor halts the trap machine, executes the appropriate menu functions, and then restarts the trap machine. During this interval the trap machine is halted and no data is transferred to the system memory. The data passes through a 128-byte-deep FIFO (first in, first out) buffer on the DLC. This FIFO allows for pauses in the data flow to the system memory.

The data is now stored in the data capture buffer in the system memory. The system processor maintains a second 16-bit DMA channel between the system memory and the tape controller. While menu programs are executing, they can control the flow of data to the tape. Run-time data may thus be stored to tape.

The system processor has access to the system memory and can read data from the data capture buffer for display on the CRT. The display RAM on the CRT is accessed through the system processor's address space. The system processor manipulates the data to provide for various display formats and sequences.

For simulation, the system processor creates data strings in parallel format and interface control lead settings from information entered by the user. This information is passed to the DLC where the data is converted from parallel to serial format for transmission on the network. Clocks are supplied and leads are set accordingly. The DLC calculates the necessary error checking sequences and appends these to the data. The DLI turns the LEDs on and off according to the information sent. The interface pod detects the data, clocks, and leads set by the instrument and reports this information via the data path discussed above for monitoring data.

#### Acknowledgments

Many people deserve recognition for their effort in the development of the hardware for the HP 4953A Protocol Analyzer. The architecture described was defined by Grant Grovenburg, Dave Karlin, and Bob Weisickle. Grant Grovenburg designed the system processor and system memory. Dave Karlin designed the system memory, data link interface, and data link control. Mark Keisling worked on the data link control, data link interface, and system integration. Sharlene Lin and Ed Moore developed the tape controller. Steve Ernst designed the power supply. Ken Krebs provided the mechanical design. John Rader was the service engineer. Jamie Hunt and Nate Sakamoto were the production engineers.

# Serial Data Acquisition and Simulation for a High-Speed Protocol Analyzer

by Mark D. Keisling, Dorothy J. Yackle, David B. Karlin, and Elizabeth Gates Moore

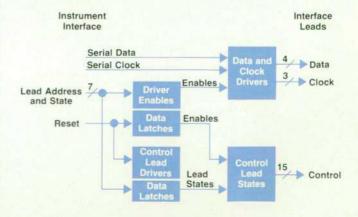

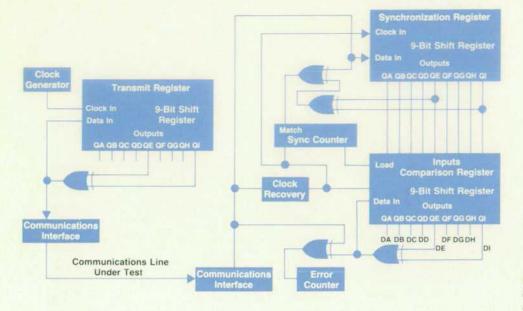

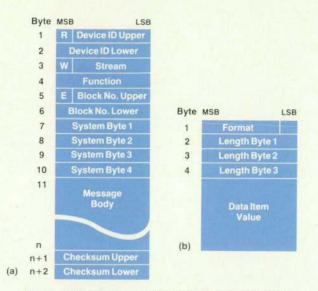

HE FRONT END of the HP 4953A Protocol Analyzer is a dedicated subsystem that provides the serial test interface for the 68000 system processor. The front end consists of four assemblies (see Fig. 1): the pod (there are several to choose from), the data link interface (DLI), the data link control (DLC), and the lead status display (LEDs). The pod, located outside the instrument, is connected to the rear panel of the HP 4953A using a two-meter 50-conductor cable. The other three assemblies (DLI, DLC, LEDs) are inside the mainframe.

Fig. 2 is a detailed block diagram of the front end. Two microprocessors in the DLC control all the functions of the front end. It is the DLC that communicates with the 68000 system processor. The DLI assembly functions as an interface between the external pod, the DLC, and the lead status display. The pod connects to the network or device being tested. The lead status display indicates the logic levels of all the interface leads on the pod.

The front end monitors the data and control leads of the device under test. This information is passed from the device through the pod to the DLI. The DLI routes the data to the proper channel of a serial input/output device (SIO) located on the DLC. Working with the front-end firmware, the SIO does some initial analysis of the incoming data and then passes the data and analysis information to the timing processor (a Z8 MCU). The timing processor formats the data into the buffer data format (see "Data Capture Buffer," page 22) and appends timing information to the data. The resulting 16-bit word goes to a 128-word first in, first out (FIFO) memory device, and then to the system

Fig. 1. HP 4953A Protocol Analyzer simplified front-end block diagram.