# JOURNAL

MAY 1984

Technical Information from the Laboratories of Hewlett-Packard Company

# MAY 1984 Volume 35 • Number 5

# **Contents:**

Putting a 32-Bit Computer System in a Desktop Workstation, by Jack L. Burkman, Robert L. Brooks, Ronald P. Dean, Paul F. Febvre, and Michael K. Bowen A modular design combines an internal printer, two mass storage units, and a 32-bit multiprocessor system in a compact package.

**Color Graphics Display for an Engineering Workstation,** by Daniel G. Schmidt This display has performance appropriate for HP's latest desktop computer, yet retains compatibility with graphics software developed on earlier computers.

BASIC Language Graphics Subsystem for a 32-Bit Workstation, by Kenneth W. Lewis, Alan D. Ward, and Xuan Bui Multiple device access, 3-D primitives, and input device tracking are some of the features.

I/O Features of Model 520 BASIC, by Gary D. Fritz and Michael L. Kolesar A transfer process for overlapped I/O and a unified I/O resource concept improve performance and simplify programming.

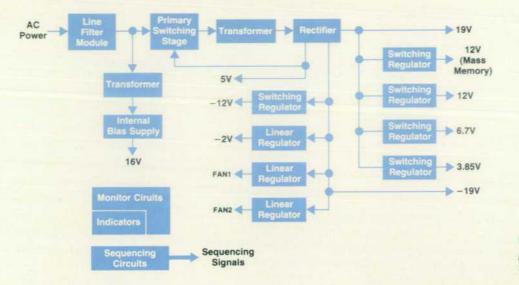

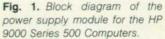

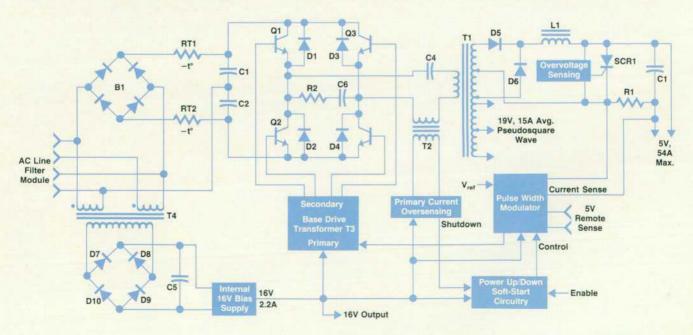

A Compact, Reliable Power Supply for an Advanced Desktop Computer, by Jack L. Burkman, Howell R. Felsenthal, Thomas O. Meyer, and Warren C. Pratt This module can deliver 550W among 12 outputs and occupies a volume less than 400 cubic inches.

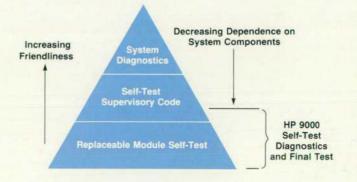

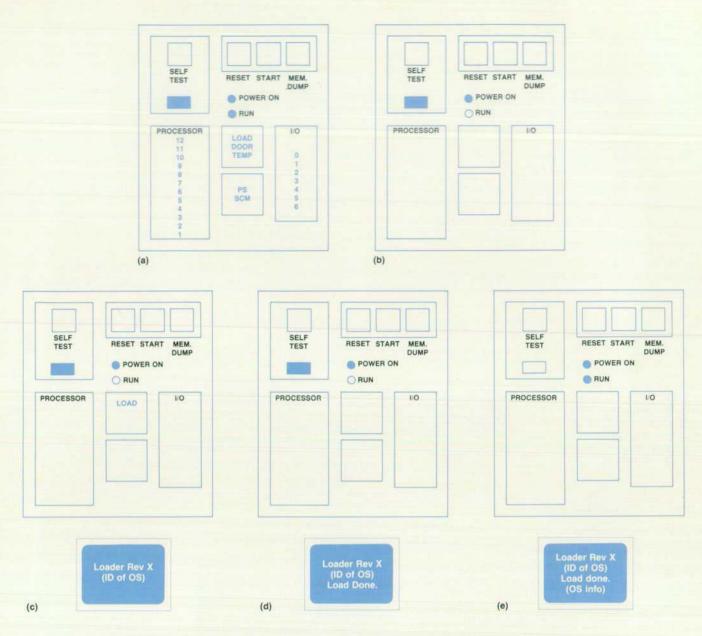

**Compact 32-Bit System Processing Units,** by Kevin W. Allen, Paul C. Christofanelli, Robert E. Kuseski, Ronald D. Larson, David Maitland, and Larry J. Thayer Two package designs, 32-bit multiprocessor architecture, and a sophisticated self-test system provide multiuser computer systems with a rugged, powerful, easy-to-service mainframe processing unit.

Authors

# In this Issue:

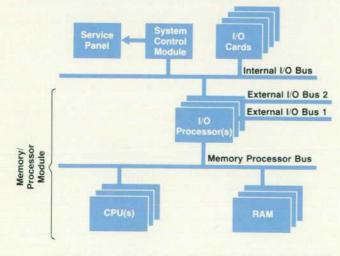

This issue wraps up the design story of the HP 9000 Series 500 Computers, Hewlett-Packard's new 32-bit machines based on the advanced technologies for integrated and printed circuit production that were featured in our August 1983 issue. The five very large-scale integration (VLSI) chips used in these computers, including the 450,000-transistor central processing unit (CPU) chip, are produced using HP's proprietary NMOS-III integrated circuit process. Mounted directly on copper-cored boards called finstrates, these chips are the basis for three kinds of functional units—CPU, input/output processor, and memory—that can be housed in various combinations in a compact Memory/Processor Module. In the HP

9000 Model 520, the desktop workstation member of this computer family, this technology can give an individual scientist or engineer exclusive use of the processing power of a large mainframe computer for such computation-intensive tasks as finite element analysis (see cover). Models 530 and 540 offer the same technology in rack-mount and cabinet versions that can be built into systems and/or shared by several users. Model 520 offers a choice of operating systems—HP BASIC or the UNIX-like HP-UX. Models 530 and 540 offer only HP-UX. Two months ago, our March issue was devoted to the operating systems and other system software for these computers. This issue focuses more closely on the three Series 500 models. The articles on pages 3 and 12 deal with the engineering that was done to incorporate the Memory/Processor Module into the Model 520 desktop workstation and give it a color graphics display. The graphics and input/output features of Model 520's BASIC language are explained by the designers in the articles on pages 16 and 21. The hardware design story of the Model 530 and 540 Computers begins on page 31, and the power supply design for all three models—unusually difficult because of the 520's compactness—is the subject of the article on page 24.

On the subject of finite element analysis, both third-party and HP software packages for this complex art will be available for the HP 9000 Model 520 in the next few months. The HP finite element package will run on HP 9000 Series 200 Computers as well, but is faster on the Model 520.

-R. P. Dolan

Editor, Richard P. Dolan

Associate Editor, Kenneth A. Shaw

Art Director, Photographer, Arvid A. Danielson

Illustrators, Nancy S. Vanderbloom, Susan E. Wright

Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright

European Production Supervisor, Henk Van Lammeren

# Putting a 32-Bit Computer System in a Desktop Workstation

A modular packaging approach provides a powerful computer workstation for computer-aided design and engineering applications.

# by Jack L. Burkman, Robert L. Brooks, Ronald P. Dean, Paul F. Febvre, and Michael K. Bowen

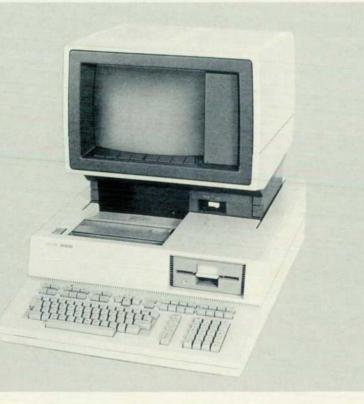

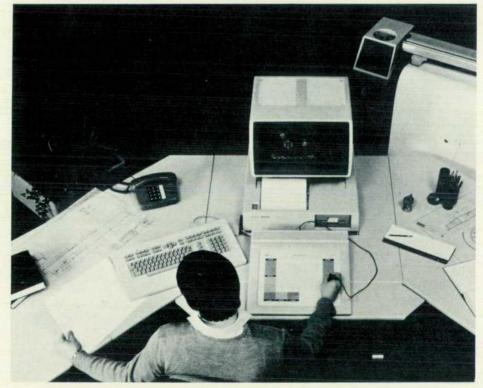

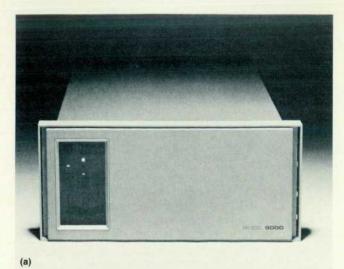

S COMPUTER TECHNOLOGY evolves, the hardware offered to users for a given cost decreases in size and/or increases in complexity. One result of this evolution is Hewlett-Packard's most powerful desktop computer system—the Model 520 of the HP 9000 Series 500 Computers (Fig. 1).

Made possible by HP's proprietary NMOS-III VLSI technology,<sup>1</sup> this workstation provides engineers and designers with a personal 32-bit computer system capable of performing many of the CAD (computer-aided design) and CAE (computer-aided engineering) applications normally requiring a large mainframe computer system. The heart of the Model 520 is the 32-bit HP 9000 Series 500 Memory/Processor Module,<sup>2</sup> a twelve-slot card cage for holding various user-selected combinations of CPU cards (up to three), I/O processor cards (up to three), and 256K-byte RAM cards. In addition, the Model 520 contains a variety of peripherals: A high-speed thermal printer

- A 10M-byte hard-disc mass memory

- A 5¼-inch flexible disc drive

- Up to five high-performance I/O channels for connecting additional peripherals

- A keyboard

- A choice of three CRT display options.

A sophisticated operating system kernel, called SUN,<sup>3</sup> coordinates the operation of this hardware and provides an interface to high-level systems such as HP-UX<sup>4</sup> (an enhanced version of UNIX<sup>m</sup>) and BASIC (see reference 5 and articles on pages 16 and 21).

Each part of the Model 520 conducts its own self-test when the machine is turned on. Any failures are indicated by appropriately lighted LEDs (light-emitting diodes) on each module and the operating system logs the failures, displays them on the CRT, and configures the Model 520 to operate around them, if possible. If the display fails, the

UNIX is a U.S. trademark of Bell Laboratories

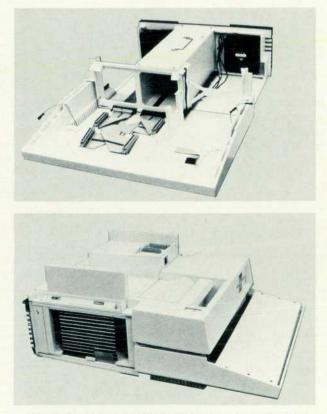

Fig. 1. The HP 9000 Model 520 Computer is a 32-bit computer system based on HP's NMOS-III VLSI and finstrate technologies.It provides professional personnel with a desktop workstation having mainframe computer capabilities. The Model 520 contains its own printer, hard and flexible disc memory devices, I/O processor, and keyboard. Several CRT display options are available. The Model 520 can have up to three CPUs for increased performance in computation-intensive applications or up to 2.5 megabytes of RAM for data-intensive work. For I/O-intensive work, up to three I/O processors can be installed.

printer is used to report the failures. If the Model 520 is connected in a multiuser HP-UX system, the failures are also reported on the system console.

If any portions of the memory cards are bad, the failed portions are blocked out and the amount of memory loss is reported to the display. In addition, during normal system operation, the operating system continually tests the memory for soft errors at a rate of 12 megabytes/day as a background function. Single-bit errors are corrected; double-bit errors are detected and reported.

Careful design and a special power supply (see article on page 24) were necessary to fit this computer system into an enclosure small enough to sit on a desktop. This package had to satisfy the basic ergonomic requirements of the operator and provide adequate cooling for all the electronic components, while remaining manufacturable and serviceable. To understand the product design challenge, consider some of the Model 520's characteristics. The total amount of power dissipated inside the enclosure approaches one kilowatt, a fully loaded machine weighs over 70 kilograms, and the ac line filter volume required measures over 820 cubic centimeters.

# Modular Design and Assembly

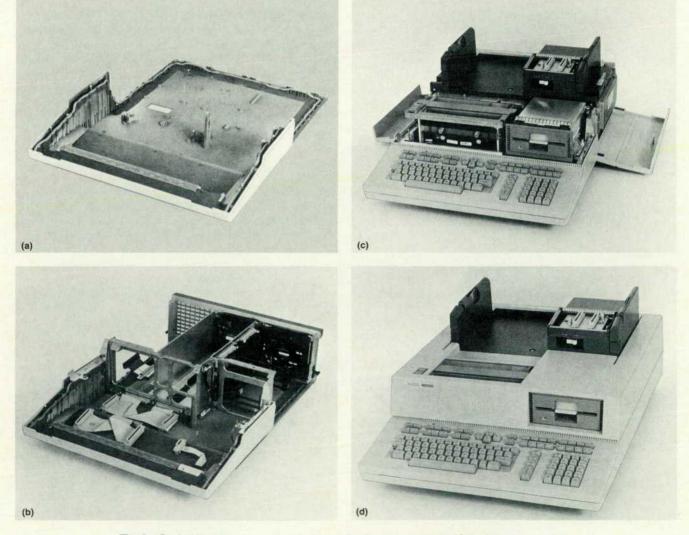

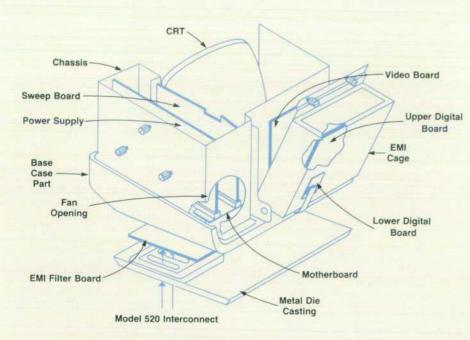

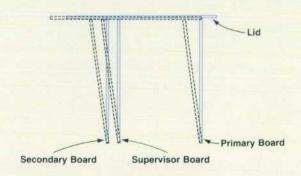

The design of the Model 520 is founded on the concept of independent modules linked together to form a highly compact package (Fig. 2). This approach allows each module to be tested fully by itself before assembly. A structural foam base (Fig. 2a) reinforced with two aluminum die castings and a central sheet-metal "bucket" forms the structure for mounting the modules. A multilayer printed circuit board, two ribbon cables with connectors, and a fan wiring harness are added to this basic structure to connect the modules electrically (Fig. 2b).

The Memory/Processor Module containing the CPUs, I/O processors, and RAM has its own cooling fan and is sealed to prevent electromagnetic interference (EMI). This module is inserted into the left rear chamber of the base assembly, and requires only the installation of the fan cable, internal I/O (input/output) cable, and eight screws. The I/O back-

Fig. 2. Packaging of the Model 520 Computer begins with a structural foam base (a) to which is added a sheet-metal "bucket," two aluminum die castings, a printed circuit board, and wiring harnesses (b). The various modules are then inserted (c) and the covers are put on (d).

plane board and two card guides are attached to the inside of the right rear chamber, and with the ac line filter module and a metal door, form the I/O and mass memory controller card cage. The line filter module houses the circuit breaker and ac line filter. It is placed on the top of the right rear chamber and installed with four screws. The power supply module is inserted into the center rear chamber. The ac line from the line filter module is coupled to the power supply and four captive fasteners are tightened to secure the assembly. The printer module is installed into the space directly in front of the processor and power supply modules and is secured with two captive fasteners. The mass memory modules are located directly in front of the I/O card cage. These devices require the attachment of dedicated cables to their controller boards and the tightening of three captive fasteners. The last module installed (Fig. 2c) is the keyboard, which uses four captive fasteners. Each module can be removed independently. Each module is also fully guided during installation to ensure proper connector alignment.

The covers (Fig. 2d) provide more than a clean appearance and EMI suppression. The rear cover provides access to the ac line circuit breaker from the front of the machine and houses the printer paper tray and the tilt mechanism supporting the CRT display. The front cover allows access to the power supply module's diagnostic LEDs (light emitting diodes) without turning the machine off. It also allows the mass memory devices and printer to be accessed without removing the CRT display. All screws used to attach both of these covers are captive. These features greatly reduce the time needed to access the interior modules for service.

The side access doors, base reinforcement strips, and keyboard cover are installed last. The keyboard cover snaps into position over the keyboard. The base reinforcement strips snap onto the left and right rear sides of the base and two screws on each strip are tightened to provide the required structural strength. These strips allow easy access to the bottom of the processor module and the I/O card module when removed. The side access doors, which also snap into position, provide access to the processor, I/O, and mass memory diagnostic LEDs without turning the machine off. They also provide easy access to the processor module cards and the I/O cards.

An external interface module was designed to allow the use of earlier HP 9845 Computer CRT displays for the Model 520. This interface is attached to the CRT display assembly and the assembly is placed on the two pedestals on top of the rear cover. Installation of the display also completes the electrical connection to the Model 520's base automatically.

# System Cooling

The high level of integration and performance in the Model 520 presented the packaging challenge of dissipating a heat load of approximately 900 watts. High reliability is achieved by maintaining device junction temperatures at levels significantly less than the maximum value specified by the device manufacturer. Under worst-case conditions, the temperatures inside the Model 520 do not exceed 80% of the maximum junction temperature specification. These worst-case conditions occur when the machine is fully loaded and operated in a 40°C ambient temperature at 4570 m elevation. The 40°C temperature limit is imposed by the mass storage media. The other modules are designed for reliable operation up to 55°C. The I/O cards are inside the machine, where forced-air cooling allows these high-performance cards to maintain reliable operation even at 55°C. In a typical environment of 25°C at sea level, component temperatures are maintained at approximately 50% of the maximum junction temperature.

The results of early tests dictated the creation of a large inlet plenum and three air flow chambers for the Model 520. This arrangement equalizes the air volume flowing through the processor, power supply, I/O, and mass memory modules. Two broad inlets reduce the pressure drop through the inlet screen and provide cooling along the entire length of the keyboard. The printer heat load is distributed equally between the air supplies for the power supply and the processor modules. An aluminum die-cast

(continued on page 7)

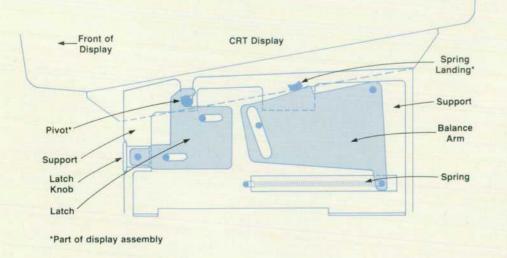

Fig. 3. CRT display tilt mechanism located inside each of the two pedestals on top of the rear cover of the Model 520 (see Fig. 2d). This design adapts to different CRT display option weights by simply changing the position of the spring-landing part fastened to the display.

# Low-Tech Modeling for Better Design

Design is an iterative process. Mother Nature, the grand designer of all time, is still trying out new models and variations on basic designs that have been in production for thousands and millions of years. Each new version is submitted to rigorous testing. The ones that pass are approved for further production, the failures fade away.

It isn't really that much different when humans design, except that they generally operate on a different time scale, which at HP is called a schedule. In the case of a product like the HP 9000 Model 520 Computer, the time scale was measured in months. About 60% of those months were spent deciding what the product was going to be: what its component parts would be, how big it should be, what it should look like, etc. Then there was an intense period of several months in which the actual design of the product package was accomplished.

The major objective of this period was to convert the images of various parts in various designers' minds into actual hardware that could be manufactured, assembled, tested, sold, and serviced. Making more than one of something invariably leads to mass-production techniques such as tooling. This presents a severe schedule and cost constraint all by itself, for the tool for a part like the structural foam base of the Model 520 took weeks to design and build, and was expensive. The Model 520 has five major structural foam parts, four die castings and a couple of dozen miscellaneous tooled plastic parts. All of the tools for these parts took time to produce and cost money, which meant that we really wanted to do it right the first time. So there was our fundamental challenge: achieving sufficient iterations of the design early enough to have high confidence that the first tooled parts would be correct.

A few words about the design process—a product designer at HP is responsible for conceiving and defining the physical parts used in the product. Many are standard parts that we purchase from vendors or are used in other HP products screws, connectors, cables, electronic parts, etc. But others we design specifically for one product, and in the case of an integrated desktop computer like the Model 520, this included the case parts plus most of the structural parts inside. Conceiving each part is one phase—deciding what it must do and how best to accomplish the task, and considering the many alternatives at each step. Documenting the solution is another phase, and the basic 3-view mechanical drawing is still the primary document that directs other people in producing the part.

The Model 520 is not a simple product, and the odds were extremely slight that each member of the design team would be able to sit at the drawing board and create drawings of parts, and that all of these parts would fit together properly. It is a big enough challenge to visualize and draw one part, let alone hundreds of interconnected ones. So we were after a way to let the design team visualize, make mistakes, and improve the designs until we got what we wanted, and then to make the tools with some confidence that they would be right the first time.

The technique we used was modeling, which is common enough. The different twist was that we did not go high-tech with expensive, complex, computer-aided three-dimensional drafting, but went low-tech with foam-core board (a styrofoam and paper form of cardboard), sharp knives, and hot-melt glue. Despite this unsophisticated approach, the increase in our productivity was on the order of 20 to 40 times in the crucial early design phase where iteration is so important. That sounds like an unbelievable increase, but it is easy to demonstrate. Usually a designer first makes mechanical drawings of a new part. Then to verify the design, the designer sends the drawings to a model shop to have one or two parts made. If this traditional approach had been used for the Model 520 design, the time involved for a typical part might have been a couple of days on the drawing and then several days in the model shop.

However, a serviceable foam-core mockup (a 3-D sketch) could be made in an hour or two, fitted to other parts, and modified in minutes if necessary. The feedback was almost immediate, and the effort required to change things was so slight that the process almost encouraged us to build the part again. So we could have two iterations in 2 to 4 hours, while the model shop approach might take 40 to 80 hours. For the more complex parts, creating the mockup first was the quickest way for the designer to visualize the part before doing the initial drawing, saving days or weeks of drawing time.

The first drawings were only rudimentary layouts, trying to obtain the best machine configuration in terms of cooling airflow, ergonomics, accessibility, serviceability, etc. Many of the component modules were already well-defined in terms of size and shape—the Memory/Processor Module, the thermal printer, and the two 5<sup>1</sup>/<sub>4</sub>-inch flexible and hard disc drives. These were rep-

Fig. 1. Foam-core board model of an early prototype of the package design for the HP 9000 Model 520 Computer at two assembly steps.

resented by simple foam-core boxes while the nondefined parts took shape in models and drawings. We eventually constructed an entire machine out of these low-tech models (Fig. 1). In fact at a quarterly review, we presented a 35-mm slide show in which we sequentially showed each module or part, first by itself and then in place in the product, progressing just as production would assemble the product until we had built a finished Model 520. This gave us a high level of confidence that we understood what the various parts were, how they related and interconnected to one another, what fit, access, and airflow problems there were, etc. The only drawback was nervousness on the part of lab management because we had the design so far along, but in the wrong material—cardboard.

The foam-core board's strength as a modeling tool came from its ease of fabrication. It seems obvious that a cardboard mockup of a die casting can share little more of the physical characteristics of the real part than its shape. But it was surprising how much we could tell from the model parts—where they were weak, the real parts were weak. So they did serve to warn us of fundamental flaws in our structural design approach.

We did not go directly from foam-core board to the final tooling. Instead we took an intermediate step and created temporary tooling for most of the major parts—rubber molds and urethane parts for the structural foam components, and sand castings instead of die castings. The reasons were time and money. These temporary tools were much less expensive and the parts they made allowed us to get more quickly into the design evaluation phase because of their better structural characteristics. And when we found the need for changes, they were easy to accomplish, meaning quick and inexpensive.

Only after building several production prototypes did we start cutting hard tools. One measure of success of the design effort is the cost of the changes that had to be made to the final tooling. On at least one previous product in our division's past, we spent the tooling budget about three times. First we bought the tools. but because of the schedule pressure, the parts design had not been adequately verified and many changes were required. The total bill for tool modifications to make the changes nearly equalled the original investment. Then we started running production guantities and it became apparent that the tools were so patched up from the corrections that we needed to start from scratch and buy new tools, spending the tooling budget a third time. For the Model 520, our model-oriented design approach encouraged lots of iterations early and the use of temporary tooling to prove the design reduced the total tool bill. Of this, about 6% was spent on temporary development tools and parts. and about 9% was spent on changes to the final tools. So we didn't spend the tooling budget three times, but only 1.15 times.

So low-tech modeling paid off on both ends—early in the design phase where it enabled us to look at many alternatives and evolve the best ones quickly, and later at the end of the development cycle when design changes are so costly. All in all, our investment in modeling tools was less than \$1000 (foam-core board, knives, glue guns, and glue sticks), but our savings were in the hundreds of thousands of dollars, making a nice return on our rather modest investment.

> Steven R. Anderson Industrial Designer Fort Collins Systems Division

rear grill with aerodynamically streamlined ribs is used to eliminate high outlet pressure drop while providing structural strength and operator protection. Supplemental air inlets are provided in the sides of the base and around the top mass memory faceplate bezel to provide additional air to the processor module and the mass memory controller cards. They also compensate for any I/O chamber inlet blockage caused by the two mass memory devices.

The fans are mounted on the rear of the machine. Instead of the more common ac fans, dc fans are used. A dc fan provides more consistent air output since its supply voltage is usually regulated, while an ac fan's air output varies with a change in the ac line voltage and/or frequency. The dc fan speed in the Model 520 is increased in three discrete steps according to system load, ambient temperature, and altitude. This provides reliable system operation over a wide range of operating conditions while reducing audible noise.

# Interconnect

Ideally the electrical connections to other modules and components should be completed or broken automatically when a module is inserted or removed. In the Model 520, most of the modules are designed so that this occurs. This aids in testing, and makes the final assembly of the mainframe much faster—just drop in the modules and close up the machine. But, if the automatic interconnect method is not reliable, it is not worth doing. The key problem to overcome is the alignment of the connectors. A small misalignment between two mating connectors places a lot of stress on the contacts. This usually leads to intermittent and/or hard failures. In the Model 520, alignment pins are used to locate each module accurately. These pins in the base of the machine engage receptacles in the modules to align the connectors.

Another objective was to eliminate any differential motion between mated connectors. This differential motion causes fretting corrosion on the connector contacts which could lead to connector failure. In vibration, a module can easily move slightly relative to a mating connector. Even a small movement can be detrimental. The Model 520's design uses a floating connector scheme to solve this problem. The connectors are mounted using shoulder screws so that they can move 0.5 mm in all directions. This requires a connector that can align itself with its mate without damaging any contacts even if the two connectors are initially misaligned by as much as one millimeter. Since the connector is no longer rigidly attached to the structure, it can move to eliminate all relative motion.

All this leads up to an even bigger problem—how to connect the CRT display electrically to the base. Here the problem is that the display must be able to be tilted and the connectors must locate themselves to the bottom of the display when it is set at different angles. The solution adds another level of floating alignment. The base connectors are mounted with shoulder screws to a connector plate that has two large locator pins with over 5 mm of lead-in taper per side. The plate is spring-loaded against the bottom of the CRT display to follow it through its range of motion. The connectors are as close as possible to the center of rotation to minimize their motion relative to the mainframe. When the display is installed, the locator pins find their holes in the casting on the bottom of the display and move the connector plate to the proper position and angle. After installation, the spring-loaded connector plate follows the display as it is tilted, guaranteeing a reliable electrical connection.

# **CRT Display Tilt Mounting**

The tilt mechanism (Fig. 3) inside each of the two pedestals supporting the CRT display performs three basic functions. It provides a spring force to counterbalance the weight of the CRT display, it has a latch to secure the display to the mainframe, and it provides adequate friction force to maintain the display in a selected position. Within the mechanical stops, the tilt is infinitely adjustable. The operator simply tilts the CRT to the position desired, and it stays where the operator leaves it. The same mechanism works for both the HP 98760A color CRT display option, which weighs over 32 kg, and the standard HP 98780A monochromatic display option, which weighs only 16 kg.

The tilt mechanism consists of five major parts: support, spring, balance arm, spring landing, and pivot. The support is the frame that holds the parts together. The spring provides the force to counteract the weight of the display. The balance arm transfers the force to the spring landing, which is mounted on the casting on the bottom of the display assembly so that it holds the balance arm at the right position to balance the display properly. The position of the spring landing is different for the two CRT display options. The pivot is also mounted to the CRT display and simply acts as a pivot point for tilting the display.

Each pedestal on the rear cover of the Model 520's base assembly provides a notch for the pivot to settle into, and then the latch simply grabs it like a finger. The display rests entirely on the pivot and spring landing as shown. The different position of the spring landing on the two different display options allows the same mechanism to counterbalance them both. No adjustments need to be made to the tilt mechanism to switch displays.

Friction is added to the system for two reasons. The counterbalance force is not exact, but an approximation. Also friction is needed to compensate for variations in spring forces, weight, center of gravity, and mechanical dimensions.

The pivot and spring landing are part of the interface module mounted on the bottom of the display. This module houses one printed circuit board and allows the color and monochromatic displays for the HP 9845 Computer to be used also on the Model 520. For future displays, the same design can be used by simply locating the spring landing in the right place.

# Mechanical Design

Access to the Memory/Processor Module on one side of the Model 520 and to the I/O and mass memory card cage on the other does not allow a sidewall on the structural foam base. The resulting flat shape at the rear of the base does not have good bend resistance. Another decision caused additional concern about this inherent weakness. In the design of the keyboard area, a number of air intake openings are incorporated under a cantilevered extension of the base. This extension forms a nest for the keyboard module and provides a cable route for the electrical connections to the main printed circuit board. The air openings further weaken the base to bending. Also, the extension is subject to extra bending forces, because it is likely to be leaned upon and because it presents a convenient handle for a user wanting to move the computer.

A number of enhancements were made to the base design to provide the needed strength. The cooling air openings are reinforced by adding triangular gussets at the edge of each opening on the inside and outside of the part. The gussets also enhance the flow of plastic in the mold to fill the forward portion of the base. A reinforcement resembling an I beam turned over on its side is incorporated into each base sidewall. The most important structural addition is attached to the planar rear part of the base: another I-beam structure was added lying down and fastened to the base (Fig. 2b). A die-cast aluminum rear panel forms the top of the I and another die casting forms the bottom of the I. A folded aluminum sheet-metal part with a U-shaped cross section joins the two castings. The module adapter plates or covers tie the forward and rear castings together for added strength. An extruded aluminum strip is screwed to the front and rear castings on each side to further support the base. This extrusion can be removed to service the CPU and mass memory boards. Two rubber rollers are installed at the rear of the base to aid in moving the Model 520, because the combined weight of the color CRT display option and the mainframe can be as much as 73 kg. The computer can be raised by using the cantilevered keyboard as a handle to clear the front footpads from the resting surface and then it can be wheeled to a new position.

Fig. 4. The conductive rope gasket used to seal the Model 520's enclosure against EMI is located between the case halves and retained in place by ultrasonically deforming two parallel rows of oval bosses as shown. The triangular ramps ensure conductive contact between the case halves.

8 HEWLETT-PACKARD JOURNAL MAY 1984

The design was modeled using 6-mm thick plywood for the base and folded 2.5-mm thick aluminum for the castings. A goal of less than 3 mm of deflection at the joint between the mainframe and the keyboard was set so that there would be a safety factor to prevent excessive flexural relative movement between electrical connector pairs. Such movement can cause disengagement or fretting of the metal contact surfaces of the connectors and lead to failure. The initial model demonstrated a deflection in excess of 3 mm between the base sidewall and the front casting. The joint is made acceptable by adding a 2-mm thick piece of aluminum bent into an L shape in two directions to provide stiffness. This piece is screwed to the sidewall and bolted to the casting. The folded sheet-metal model simulated the casting successfully. Sheet metal could have been used in production in place of the castings for structural reasons, but die casting offers versatility for fastening modules, making contact with conductive EMI gaskets, and mounting fans, and it provides adequate strength with less material and fewer process steps. The plywood model was duplicated several times and used to support the monochromatic or color CRT displays and the prototype keyboard assembly. These units were used for hardware and software testing of breadboard electronics and the prototype stage of the Model 520.

# **Electromagnetic Compatibility**

Suppression of electromagnetic interference to meet regulatory agency limits is accomplished by spraying the interior of the structural foam plastic parts with a conductive nickel-base paint. A cylindrical woven wire mesh with a compressible foam-rubber core rope is attached to the interior of the housing parts. This material compresses against the metal-encased modules at their outside interface with the base and covers, forming a seal around the periphery of the mainframe to prevent electromagnetic waves from getting in or out. Tradeoffs between EMI sealing and cooling air flow requirements are made at air inlet and outlet areas. Wire screen is placed over the air inlet openings in contact with the conductive coating on the inside of the base and an open grid pattern is cast into the rearpanel air outlets to satisfy both requirements.

The optimum compressive force for the selected gasket material is 0.67 kg/cm. Since the periphery of the mainframe is approximately 2540 cm, we faced another distortion problem when the covers were attached. The covers were pushed away from the mainframe in areas away from the captive fastener locations. The problem is overcome by incorporating a channel to retain the gasket rope and provide intermittent contact. The channel is established by a double row of oval bosses raised off the interior of the structural foam part (Fig. 4). The intermittent contact is provided by placing a triangular ramp midway between each pair of oval bosses. A 30-mm interval between ramps provides enough contact pressure to suppress emission of EMI from the housings and to reduce the compressive forces between covers and modules by 75%. The gasket rope is retained in the channel by an ultrasonic staking process on selected boss pairs. The cut ends of the rope are potted with a silicone rubber and terminated within the structural foam housing in holes molded into bosses at the ends of the channel.

# Fasteners

The quantity of screw fasteners can become large in a computer of this size. Different lengths and sizes compound the problem of putting the correct screw in the correct place. A goal to minimize the number of different kinds and sizes was set. There are five types: captive screws for the housing covers, captive screws of another type for the modules, self-tapping (into plastic) screws, and two machine screws (metric 3 and metric 3.5). The total quantity of fasteners is minimized by using as large a screw as possible for each application. The larger screws meet strength requirements with fewer numbers. The decrease in assembly time by having fewer fasteners is enhanced by the use of air-powered, adjustable-torque drivers on the assembly line.

The captive screw assembly in the covers is based on a regular M4 pan-head machine screw. A flat washer and an external-tooth locking washer are installed under the screw head and the screw is then installed into a metal insert that is ultrasonically pressed into the cover. The screw is retained in place by pushing a neoprene rubber O ring over the screw threads. The holes in the cover for the captive screws are oversized to provide for alignment tolerances. In the original design of the cover this left too small an area in contact between the washer and the hole. Hence, the screw tightening torque of 1.4 N-m caused compressive failure of the plastic. The metal insert mentioned above is required to overcome the compressive load of the screw head.

The captive screw used for the modules is a swaged-on spring-loaded commercial assembly. The spring loading is necessary to keep the threads from interfering when seating the module on its connector. The swaged-on design and the addition of a washer allow movement of the assembly to align the screw to its mating threaded socket in the base assembly.

The self-tapping screws used to fasten structural components to the plastic base have a special head. The tolerance analysis for fastening showed that a washer would be required to transfer the tightening torque safely. The hole size for the fastener determined by the analysis does not leave enough bearing area between the part to be fastened and a common screw head without the addition of a washer. A standard hex-washer screw head style has sufficient area, but requires a different drive. A common drive is desirable on an assembly line using air-powered drivers. By combining the common drive recess with the hex-washer head style, it was possible to retain a common drive and eliminate the separate washer necessary for use of other head styles.

# Acknowledgments

Many thanks to everyone who became involved in the plastic processing department. Special thanks to Walt Heron for his ultrasonic staking idea, to Bill Toben for his work on the conductive paint, to Sandy Degi for her help with all the plastic parts, and to the molding department for their efforts in tool tryouts. Linda Johnson, Bev Hemstreet, and Gretchen Honick spent many hours helping (continued on page 11)

# The Toleranced Design of the Model 520 Computer

Some attention to the effects of dimensional variations in component parts is a normal part of the design of any assembled product. In the case of a product as densely packed as the HP 9000 Model 520 Computer, this attention is particularly critical, requiring a painstaking consideration of the accumulated effects of individual tolerances to ensure easy assembly of the product and easy replacement of any failed modules later in the field.

To review some basic principles, a tolerance is the allowable range of variation in the dimensions of a part. These tolerances may be unilateral or bilateral. A unilateral tolerance is taken to one side of a dimension (e.g., a hole diameter of 3.0 + 0.13 mm). A bilateral tolerance occurs on both sides of a dimension (e.g., a hole position of  $10.0 \pm 0.13$  mm).

Tolerances have a variety of origins. As the equipment for forming sheet-metal parts wears, lead-screw backlashes increase, as do punch-to-die clearances. These effects produce variations in hole placement and diameter. When a plastic part is molded, it is subject to inconsistent shrink rates and constituent material variations. The final part produced has dimensional changes as a result. In any kind of molding or casting operation the cooling of the molten material to the solid phase results in internal stresses, thus warping the parts produced.

If tolerances are not accounted for in the design of mechanical parts, several problems arise. The predominant problem is difficult or impossible fits during assembly. As these fit problems are discovered on the production line, redesign for tolerances must occur to correct them. These corrections take place through part specification revisions, obsoleting parts in stock, documentation updates, etc. In some instances, it may not be possible to solve a tolerance problem, forcing production problems to continue for the entire product life cycle. Some tolerance problems result in long-term intermittent electrical connections, requiring repetitive servicing of equipment that only works after merely taking it apart and putting it back together again.

The benefits of a toleranced mechanical design are many: easier production line assembly, minimal production changes, increased electrical interconnect reliability, and generally, a better product. The ability to use parts manufactured with tolerance errors is increased. This allows the production line to continue manufacturing where otherwise it would be halted.

A worst-case tolerance T<sub>i</sub> is typically assumed to be three times the standard deviation in the Gaussian distribution of the errors in the actual length of a dimension. If a dimension is specified as  $1 \pm 0.1$ , this means that its mean value is 1 with a standard deviation of 0.1 divided by 3, or 0.033. Thus, a dimension greater than 1.1 or less than 0.9 will occur at a frequency of 0.27%.

The overall standard deviation is the square root of the sum of the squares of the individual standard deviations, or

$$\sigma_{\Sigma} = \sqrt{\Sigma \sigma_{\perp}^2} \tag{1}$$

Since the typical bilateral tolerance is three times the standard deviation for a dimension, this equation may be restated as

$$T_{\Sigma} = \sqrt{\Sigma}T_{i}^{2}$$

(2)

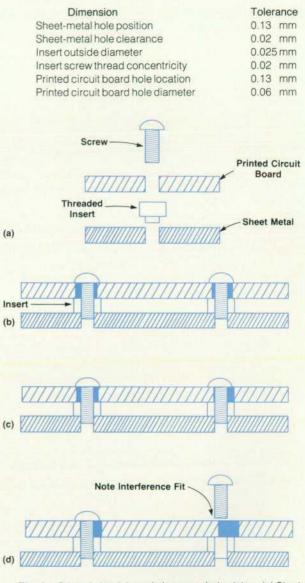

This equation can be used for the sizing of a screw clearance hole. For example, assume that a printed circuit board and a sheet-metal plate are in perfect relative position, with zero location error between them (Fig. 1a). These two parts need to have a screw attaching them. The screw protrudes through the printed circuit board and attaches to a hardware insert pressed into the sheet-metal plate. To analyze what the screw hole clearance must be, the following tolerances must be known:

Fig. 1. Printed circuit board clearance hole sizing. (a) Single mounting screw to attach board to sheet-metal plate. The size of the hole in the board for the screw must be large enough to accommodate some misalignment and variation in part dimensions. (b) Printed circuit board in perfect position relative to the sheet-metal plate. Note the misaligned holes in the board for the two mounting screws. (c) Board skewed relative to plate, but the hole dimensions still allow the mounting screws to fit. (d) The mounting screw on the right does not fit because the screw on the left was tightened prematurely with the board extremely skewed relative to the plate.

To determine the screw clearance hole dimension, the overall tolerance is determined from equation (2):

| Tolerance<br>0.13 |      | Square of<br>Tolerance<br>0.0169 |  |

|-------------------|------|----------------------------------|--|

| 0.02              |      | 0.0004                           |  |

| 0.025             |      | 0.000625                         |  |

| 0.02              |      | 0.0004                           |  |

| 0.13              |      | 0.0169                           |  |

| 0.06              |      | 0.0036                           |  |

| sum: 0.385*       | sum: | 0.038825                         |  |

Square root of sum of squared tolerances: 0.197\*

The result is the bilateral tolerance that should be allowed for the radius of the clearance hole.

When the printed circuit board and the sheet-metal plate are in perfect relative position, the above clearance hole will work with a 0.27% rejection level. To ensure perfect relative position, all of the screws fastening the board to the plate must have been started, but not tightened, as indicated in Fig. 1b. This guarantees that the two parts are either in perfect relative position, or at least close enough to be functional as an assembly as depicted in Fig. 1c. If one screw is tightened before the other screws are started and the board is skewed too much relative to the plate, the other screws will be impossible to fasten as shown in Fig. 1d. In this case, the tightened screw(s) can be loosened to allow the relative position to shift for successful assembly.

This screw attachment example illustrates an extremely common and simple problem. It also demonstrates how to use the statistical tolerance method. While this example may not seem very important, some worst-case clearances in practical product design situations can exceed the screw head diameter, requiring a washer to allow proper tightening of the screw. The very same situation, when analyzed statistically to select the correct dimensions, may not require any special treatment.

On the Model 520, our final design resulted in a three-level approach. The three levels are attached to each other at controlled interfaces, enabling the control of tolerance accumulations. These three levels of attachment take place at roughly the front-to-back and side-to-side midlines of the Model 520's base. This allows tolerance accumulations to be more evenly distributed about the instrument from a location near its central vertical axis.

The base is the first level and provides locating features for the structural casting assembly, which is the second level. The keyboard electronics, keyboard bezel, disc drives, and front

\*Note that the worst-case tolerance is 95% worse than the statistical tolerance (0.385 compared to 0.197).

us make the Model 520 manufacturable.

Brad Clements was a remarkably dynamic and effective materials engineer. Thanks also to Cliff DeLude who did the original conceptual design and to Priscilla Berwick for her help with drafting.

# References

1. J.M. Mikkelson, et al, "NMOS-III Process Technology," Hewlett-Packard Journal, Vol. 34, no. 8, August 1983.

2. J.W. Beyers, E.R. Zeller, and S.D. Seccombe, "VLSI Technology Packs 32-Bit Computer System into a Small Package," *ibid*.

3. D.D. Georg, B.D. Osecky, and S.D. Scheid, "A General-Purpose Operating System Kernel for a 32-Bit Computer System," Hewlettcover are directly located by the base. This ensures close positioning to the base, and using only one major interface allows few tolerance accumulations.

The structural casting assembly is the second level of the toleranced design. It is composed of a front casting, a right-front casting, a power supply housing, and a rear casting. The casting assembly is located relative to the base by means of a locating pin pressed into the base and projecting through a tight clearance hole in the front of the casting assembly. To locate the casting assembly along the centerline of the base, two tapered indentations in the bottom of the rear casting fit over two pedestals with tapered sides cast in the rear of the base (see Fig. 2b on page 4). The tapered fit of the base relative to the rear casting allows for a considerable variation in differential lengths from front to back, while providing negligible variation in lateral positioning.

The positioning of the I/O backplane against the power supply housing locates the mainframe motherboard. As the casting assembly is installed in the base, the motherboard/backplane assembly is formed. The final attachment of the casting assembly to the base then sandwiches the motherboard into its permanent location. Thus, no fasteners are required to hold the motherboard in place. After the motherboard is installed, the power supply and Memory/Processor Module can be installed.

The mounting plate of the processor module is located by a closely positioned hole-insert pair at the top center of the front casting. Rotational alignment is accomplished by tapered pedestals in the rear casting in the same manner that the structural casting assembly is located with respect to the base. The I/O area is similarly attached to the top of the right-front casting. The processor mounting lid floats relative to the processor module, allowing simultaneous stress-free electrical interconnect of the processor module and accurate positioning of the mounting lid.

Both the processor mounting lid and the I/O lid planes have inserts projecting vertically to align the position of the rear cover. The positioning method used is similar to that used in the base-tocasting assembly: one point locates the cover in two dimensions, another references the angle.

The integral printer is hung from the front casting, with its position set by base aligning pins.

It was determined that the most critical part in the overall toleranced design is the structural casting assembly. In this assembly, the power supply module housing was found to be the most critical part, and was tooled as a class-A stamped and formed part. In addition, the holes in the casting are drilled using drill jigs with tight tolerances.

> Joseph R. Milner Product Designer Fort Collins Systems Division

Packard Journal, Vol. 35, no. 3, March 1984.

4. S.W.Y. Wang and J.B. Lindberg, "HP-UX: Implementation of UNIX on the HP 9000 Series 500 Computer System," *ibid.*5. D.M. Landers, et al, "An Interactive Run-Time Compiler for Enhanced BASIC Language Performance," *ibid.*

# Color Graphics Display for an Engineering Workstation

# by Daniel G. Schmidt

ANY PEOPLE THROUGHOUT HISTORY have emphasized the importance of visual images in human communication. The computer, being nonhuman, prefers numeric or, at best, alphanumeric communications. This conflict is the father of the color graphics subsystems for computers. With such a subsystem, a computer can deliver information to users in a much more efficient way. The proper use of color graphics can aid in simplifying the interpretation of large amounts of complex data.

Cost is a major concern when considering the addition of color graphics to a computer system. The cost of an item must be weighed against its perceived value before a decision can be made as to whether the item is worth the price. If color graphics can be supplied at a lower cost, then its advantages can be made available to more users.

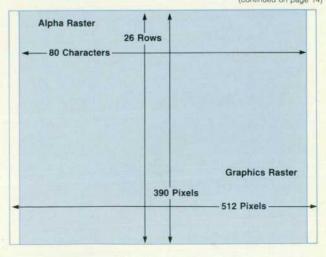

The HP 98760A Monitor Assembly is a color graphics display subsystem designed for the HP 9000 Model 520 Computer with these goals in mind. The 98760A can display both alphanumeric (alpha) and graphics information on its 13-inch-diagonal color CRT using a raster-scan format. The alpha and graphics rasters are separate and can be displayed individually or together. The system software supports new features such as color map graphics and raster size, and emulates displays of earlier systems such as the HP 9845C Computer.<sup>1</sup>

# **Graphics Attributes**

The graphics raster fills the entire screen and is 512 pixels wide by 390 pixels high. The horizontal size of a graphics pixel is 1.5 times that of an alpha pixel. Hence, the alpha raster is narrower than the graphics raster by 32 graphics pixels and is centered within the graphics raster (Fig. 1).

Four memory planes are available for the graphics raster with each pixel individually addressable. (The alpha display is not color mapped; alpha colors are handled differently as will be explained later.) The graphics memory planes address a color map that can generate up to 16 colors per frame. That is, the video circuitry is capable of displaying any choice of 4096 colors by altering the voltage on each of the three CRT guns (16 levels per gun), and the color map can contain references for 16 choices. This allows the user to display single pixels of any of the selected 16 colors at the same time at different locations on the screen. The system software also uses the pixel dither patterns<sup>2</sup> used in earlier HP eight-color displays to provide a variety of eye-averaged colors that can be used at the same time as the color map to provide area fill and shading. This allows display of up to 4913 eye-averaged colors using only 8 of the 16 color map locations. This is simply emulating HP's earlier eight-color displays by devoting half of the color map to the basic eight colors. This gives the 98760A

a great degree of flexibility and backward compatibility with earlier HP color displays.

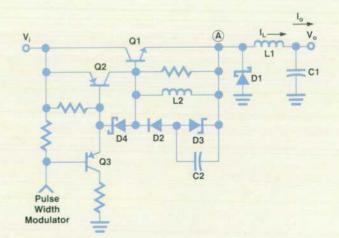

The graphics circuitry uses a UPD7220 graphics display controller IC, which is an intelligent graphics peripheral controller. This controller has at its disposal 64K×16 bits of dynamic graphics RAM. This RAM contains color map information for each of the graphics pixels on the screen, and can be accessed by the Model 520 via the graphics controller. Using a graphics controller simplifies the circuitry and reduces the cost of the display without a great loss in performance. This graphics controller generates vectors for the 98760A at a speed greater than 28,000 pixels per second.

# **Alpha Attributes**

The alpha raster is 720 dots wide by 390 dots high. Alphanumeric characters are 9 dots wide by 15 dots high and the alpha raster can display 26 lines of 80 characters each. The character set includes the 128 ASCII characters, a semigraphic line drawing set, and either the HP European extension or the Japanese Katakana characters. The local language extensions are detailed and are comparable to those used in other HP products.

The alpha display and many of the sync signals used by the analog circuitry are controlled by an MC6845 CRT controller IC located on the circuit board in the casting underneath the CRT. The MC6845 requires system software initialization to provide the proper sync signals for either 60-Hz or 50-Hz operation.

The attributes for the alpha characters are contained in six signals: UL (underline), IV (inverse video), BL (blinking), (continued on page 14)

Fig. 1. The graphics raster for the HP 98760A Color Display fills the entire screen. The alpha raster is slightly smaller horizontally and is centered on the graphics raster as shown.

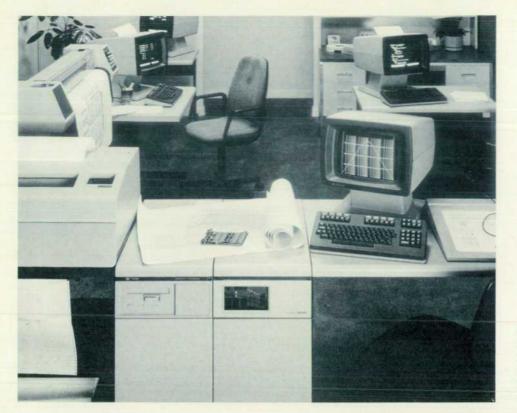

# Detached Keyboard Option for the Model 520 Computer

Late in the design phase of the HP 9000 Model 520 Computer, after most of the parts were already tooled, the German ergonomic standards ZH1/618 were first proposed.<sup>1</sup> The Model 520 was designed as an integrated workstation and like other HP desktop computers has many features packaged togethertwo mass memory devices, a printer, a power supply, a Memory/ Processor Module, a CRT display, an I/O card cage, and a keyboard. When the initial product design was compared to the proposed ergonomic standards, some discrepancies were noted. Some were easily brought into compliance, such as going from dark keycaps to lightly colored, textured keycaps. To achieve proper working heights for the keyboard and CRT, a special table was designed and is available through HP's Computer Supplies Operation. The biggest noncompliance with the ergonomic standards was that the Model 520's keyboard was fixed with respect to the display. The only adjustment available between the keyboard and display was a self-holding tilt feature for the CRT. Detaching the keyboard from the display was not possible. A follow-on design project was initiated to correct that deficiency

There are a few different ways to detach the keyboard from the display. One obvious method is to package the keyboard separately and mold a new base for the rest of the machine. Similarly, detaching the CRT from the base would be a way to meet the standard. These two solutions were undesirable because of high tooling costs and difficult cabling. Also, neither solution is easily interchangeable with the existing design. For manufacturing simplicity and possible modification by customers, the use of parts already used in the standard machine is best. The detached keyboard was also needed quickly since the proposed ergonomic standards were scheduled to become mandatory in Germany. The best solution would be quick, use most of the same parts, and minimize tooling and development costs.

The Model 520 keyboard consists of a purchased keyboard assembly and an HP-built scanner board. The scanner board interfaces with the rest of the machine through the I/O processor bus and receives and distributes the power for the keyboard. The keyswitch assembly and the scanner board are electrically connected with a 20-line flat cable. The major challenge of the detached keyboard design for the Model 520 was determining what to do with the scanner board. If placed outside the machine, up to 100 signals would have to go with it. The cable would be very large and require very good EMI shielding. If it stayed in a shortened base, the only volume available for the board was either across the front of the machine, which would block cooling airflow, or standing next to the printer as a two-board package. A two-board package would have required much more development time and a new place to mount the Model 520's beeper. The easiest solution was to leave the base and scanner board assembly intact and just bring out the 20 signals between the scanner board and the keyswitch assembly. That was the method chosen. The result is shown in Fig. 1.

Leaving the scanner board in the base required covering the board and providing for its mechanical mounting. In addition, the cover and mount must make all of the necessary conductive connections to the RFI gaskets, and provide a place to mount an interconnect/buffer printed circuit board. Those functions are carried out by a welded sheet-metal assembly. A molded cover snaps onto this piece and provides a surface for the keyswitch assembly to rest on. A removable extension is provided to give more surface for the keyboard. The extension can be stored under the molded cover along with flexible discs, tapes, and other thin items.

Fig. 1. The detached keyboard (Option G02) of the HP 9000 Model 520 Computer is available in Europe and complies with German ergonomic requirements specified by the ZH1/618 standard. The keyswitch assembly is packaged between a sheet-metal base and a structural foam molded bezel. The cable connection to the mainframe is made at the keyboard and is fully hidden under the rear overhang of the bezel. The rear overhang also provides a recess for the cable. When the keyboard is placed on a table, it can be tilted to a 10-degree angle using its built-in folding legs.

The keyboard cable is 90 cm long, providing enough cable to place the keyboard to the right or left of the base, or on the operator's lap. The cable tucks into the recess in the back of the keyboard and drops into a hole at the back of the base cover. The final solution meets the German ergonomic requirements, ZH1/618. The option is easy to add at any time and requires less than 20 special parts. The major drawbacks of this solution are that the keycaps are higher than those of the fixed keyboard when the detached keyboard is sitting on the scanner board cover and that the front end of the computer sometimes gets in

R (red), G (green), and B (blue). Each  $9 \times 15$  character cell can be individually addressed with respect to each of these attributes. This allows each character in any combination of characters to be one of eight different colors: red, green, blue, yellow, cyan, magenta, white, and black. And, each character in any combination of characters can be underlined and/or blinking and/or inverse video. These attributes are the same in the 98770A High-Performance Color Display so that user programs will run on both displays.

Alpha pixels are dominant over graphics pixels. Whenever an alpha pixel is present, it is displayed undisturbed, while a graphics pixel at the same location on the screen is not visible. Because aesthetic concerns required the widening of just the inverse characters to make them more visible, a circuit to stretch the rising edge of each inverted alpha pixel by one half is included in the 98760A. If the character is not inverted, the stretch circuit is turned off.

# Hardware Design

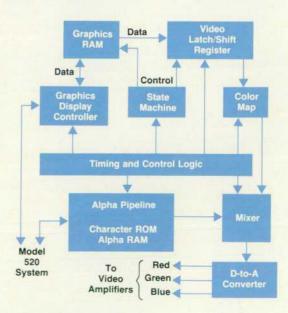

A block diagram of the color graphics circuitry is shown in Fig. 2. The video shift registers consist of three 16-bit latches and four 16-bit shift registers. To reduce the cost, these shift registers are incorporated into an output gate array. The gate array receives data bits in parallel from the graphics memory for display refresh and shifts these bits out, four at a time, at the graphics video rate.

The gate array design lowered the cost and raised the reliability of the system by eliminating many TTL packages. The estimated failure rate of the one chip compared to its TTL equivalent shows a marked improvement in reliability. The cost savings came mostly in the board space saved. Without the gate array, the digital board could not have contained all of the necessary TTL logic. Since the board size was fixed by its location in the mechanical layout, a design to accommodate a larger board would have been much more expensive.

The outputs of the color map RAM define the colors seen on the face of the screen. The color map RAM consists of three high-speed  $16 \times 4$ -bit static RAMs which map a fourbit address into 12 bits of color information. The graphics RAM contains an address to the color map for each graphics the way. To solve these problems, another work table was designed that has a recessed area for the main computer and a movable work surface that can cover the front of the machine. The work table also makes it possible to place a graphics tablet directly in front of the CRT display with the keyboard located to either side.

The detached keyboard version, Option G02, of the Model 520 and its companion work table are available only in Europe at this time.

# Reference

P. Arnold, "Ergonomics with bite: New video display standards," *Electronic Business*, Vol. 10, no. 2, February 1984, pp. 222-223.

Michael K. Bowen Product Designer Fort Collins Systems Division

pixel. Each four-bit field from the color map is used to drive a different gun in the CRT to one of 16 levels of intensity. The addresses applied to the RAM come from a multiplexer, which can select either the four video lines from the graphics shift registers (output gate array) for display refresh or the DB12 to DB15 data lines from the Model 520's I/O processor bus to allow the Model 520's CPU to access the RAMs.

The video mixing circuitry mixes the alpha video with the graphics video, making alpha dominant over graphics. Advanced Schottky TTL circuits are used for the digital-toanalog (D-to-A) drivers to obtain fast rise and fall times, and to reduce skew between the red, green, and blue color channels and the high-to-low and low-to-high transitions. The graphics lines are fed into five NAND gates in each channel with the combined blanking signal able to gate the graphics off. A sixth NAND gate in each channel is devoted to alpha and is driven only when the graphics display is forced off by the alpha pipeline. The single alpha driver is

Fig. 2. Block diagram of color graphics circuitry for the 98760A.

made equivalent in CRT brightness to all five graphics drivers combined by using a smaller D-to-A resistor value.

The D-to-A and bias voltage circuits provide the interface between the digital video signals and the analog drive requirements of the video amplifier input stage. The interface signal yields increasing display brightness with increasing sink current. The beam-off level corresponds to black on the display. Because of the variations and drift of the cutoff voltages for each gun in the tube, it is necessary to make the change in sink current between black and the first visible shade larger than the step size between adjacent visible shades. The threshold of visibility is set approximately halfway between black and the first visible shade. This guarantees that the black level will always yield black on the display and that the lowest shade will be visible. The remaining steps between shades are equal in size.

The D-to-A circuit was chosen for its cost/performance ratio. The D-to-A circuit is fast and is coupled directly to the video amplifier, which has a 12-ns rise time. Current is sunk through the resistors in an 8-4-2-1 weighted resistor network. A fifth resistor receives an offset signal, which is present whenever a nonblack graphics dot is being displayed. This causes the larger sink current step between the black level and other brightness shades.

All components and component values in the 98760A are critical for proper operation and suppression of EMI (electromagnetic interference). Changing the individual boards in the system could result in poor picture quality because of variations in the exact values of the components on the boards. To reduce repair costs and avoid the need to readjust the CRT when a board must be replaced, a means was devised to add a special resistor on each board at the factory that compensates for measured differences in the component values.

The 98760A Color Display meets the requirements for EMI suppression, level B. This was difficult to achieve because of the fast (51-MHz) video circuitry, but it qualifies the device for unlicensed residential use.

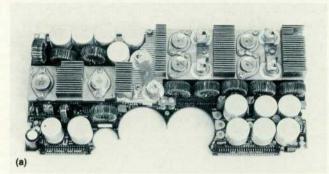

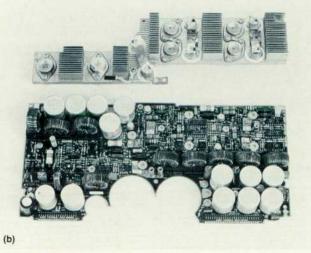

# Cost

The 98760A has a low price for four main reasons. The output gate array and the discrete D-to-A converters have already been mentioned. Another reason was the leveraging of the printed circuit and tube assemblies used for the color display of the earlier HP 9000 Model 236 Computer (formerly designated as the HP 9836C). The video board, sweep board, power supply, and CRT tube are used in both the Model 236's color display and the 98760A (Fig. 3). This reduced the R&D investment and lowers the production costs of both systems.

The fourth reason for lower cost is the use of an in-line CRT tube. Although the color purity is not as good as that attainable with a delta-gun configuration, it is acceptable and using in-line tubes lowers the cost considerably. The CRT's yoke is matched to the tube, which eliminates both drift and the need for user convergence. Built-in convergence and purity simplifies the vertical and horizontal sweep circuits so much that while providing adequate performance in noncritical applications, it also produces a more efficient and reliable product at a greatly reduced cost.

# Acknowledgments

Recognition should be given to the entire design team headed by Bill Hale. Darel Emmot and Roger Swanson worked on the gate array and Dave Lungren and Joe Milner did the mechanical design. Bob Fredrickson worked on the graphics processor and system testing as well as the gate array. Kathy Osborne, Mary Sue Rowan, and Mitch Stein wrote the software handlers for the product. Tom Bartz worked on product definition and Leonard Lindstone worked closely with us on the EMI testing and qualification. Also special thanks to the Model 236 Computer's color display design team for their support of the assemblies that are shared by the 98760A and the Model 236.

# References

Hewlett-Packard Journal, Vol. 31, no. 12, December 1980.

H.L. Baeverstad, Jr. and C.C. Bruderer, "Display System Designed for Color Graphics," *ibid*, p. 29-31.

Fig. 3. By using the same assemblies for portions of different HP display options, the manufacturing cost can be reduced considerably. The assemblies indicated are used by the color display options for both the Model 236 and the Model 520 Computers.

# BASIC Language Graphics Subsystem for a 32-Bit Workstation

# by Kenneth W. Lewis, Alan D. Ward, and Xuan Bui

HE GRAPHICS LANGUAGE SUBSYSTEM for the HP 9000 Model 520 Computer provides high-performance, device-independent, interactive graphics via BASIC language keywords. The rich set of features and the friendly BASIC environment facilitate construction of such applications as data display, graphical monitoring of realtime events, two- and three-dimensional drafting systems, and CAD modeling systems.

Two major objectives guided the definition of the graphics subsystem-increase the performance and extend the power and functionality of the graphics language used in the earlier HP 9845C Computer.<sup>1,2</sup> The graphics language extensions were influenced by the ACM SIGGRAPH CORE standard. The interest in this standard was caused by a growing number of implementations and users in the industry. The AGP graphics package for the HP 1000 Computer and the Series 500 HP-UX operating system is based on this standard as a precedent. Therefore, the graphics extensions made for the Model 520 are functionally similar to those defined by CORE. Transportability of existing HP 9845C programs is an important consideration for current customers upgrading to the Model 520 Computer. This provided the objective to generate a product that is a superset of the language used in the HP 9845C.

# **Graphics Features**

Multiple Device Access. The HP 9845C introduced the concept of multiple plotting devices. This concept was extended to include the logical view surface concept defined by the CORE standard. Also, multiple active input devices are now available with this new system. The selection of graphics devices is done dynamically during the execution of a BASIC program.

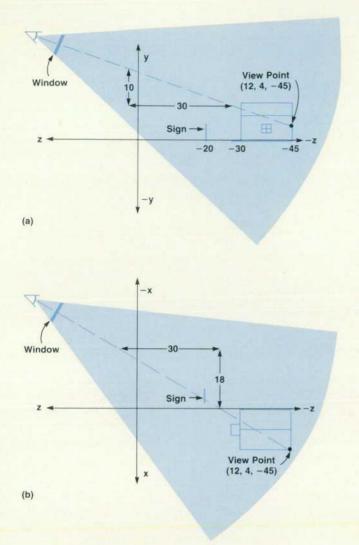

**2-D** and **3-D** Plotting. Both two-dimensional and three-dimensional line and surface primitives are provided. Lines can be specified by individual BASIC statements, or an array of lines can be constructed and plotted with one statement. Regular and irregular polygons can be generated and filled with the desired color. Two-dimensional and three-dimensional modeling and viewing transformations are provided for generating an image from these primitives (Figs. 1, 2, and 3). The specification of these transformations uses the same model as the AGP graphics package, facilitating a common understanding of both packages and transportation of programs. The transformations can be used for generating instances of objects and nesting of sub-objects, as well as for positioning a view of these objects.

Three-dimensional viewing transformations are highly intensive in floating-point operations. The Series 500 CPU

> Fig. 1. Three-dimensional view generated by the Model 520 BASIC graphics subsystem. A portion of the program for this view is given in Fig. 2. Note that text can be treated as a graphics object (For Sale sign).

FOR

W

```

10 GINIT3D

! INITIALIZE GRAPHICS SYSTEM TO 3D

I SETS THE POINT YOU ARE LOOKING AT

20 VIEW POINT 12.4. - 45

30 VIEW NORMAL 18, -10, -30

! SETS THE DIRECTION YOU ARE LOOKING

I SETS WINDOW TO BE CENTERED ABOUT VIEWPOINT

40 WINDOW - 1,1, - 1,1

! SETS DISTANCE FROM VIEWPOINT TO WINDOW

50 VIEW DISTANCE 70

60 PROJECT PERSPECTIVE 0,0, -2 | ESTABLISHES A PERSPECTIVE VIEW: I.E.

I DEFINES A VIEWING PYRAMID ALONG WITH WINDOW

70

1 INITIALIZE PLOTTER

80 PLOTTER IS "INTERNAL"

I TURN GRAPHICS RASTER ON

90 GRAPHICS ON

CALL Draw_sign

100

110

CALL Draw_house

120

CALL Draw_grass

130 END

140 !

160 SUB Draw_sign

170 | This subroutine draws a For Sale sign

PEN 1

180

MOVE 8.1,3.5, -15

190

GTEXT ORIENT - 1,0,0,0,1,0 ! SETS GRAPHICAL TEXT ORIENTATION

200

! SETS SIZE OF GRAPHICAL TEXT

210

GTEXT SIZE 1.1.1.0

220

GTEXTJUST .5..5

! CENTER-JUSTIFIES THE GRAPHICAL TEXT

GTEXT "FOR SALE"

230

MOVE - 4,0, - 20

! THE FOLLOWING SEQUENCE DRAWS THE

240

DRAW - 4,2, - 20

SIGN AROUND THE TEXT

250

1

260

MOVE -4.2.0, -20

.

330 SUBEND

340 1

350 SUB Draw_house

360 ! This subroutine draws a house

370

MOVE 0,0, -30

380

DRAW 0,0,-45

.

600 SUBEND

610 SUB Draw_grass

```

Fig. 2. Partial listing of graphics program for view shown in Fig. 1. See Fig. 3 for a depiction of the viewing parameters specified in lines 20 to 60.

provides high-performance floating-point operations for these transformations.<sup>3</sup> The hardware is an excellent match for the 3-D features.

**Graphical Text.** The AGP and CORE definitions provide mechanisms for including text as part of objects within a picture. The text can be positioned, scaled, and rotated to be part of a 2-D or 3-D object. For example, a viewed scene might include a sign with text on it (Fig. 1). The text and the other primitives composing the object are displayed as specified by the current viewing transformation. By comparison, graphics labels in the HP 9845C are not part of the object, but are used to annotate a plot. Changing the view of the object changes the position of a label, but not its appearance. These labels act as if they were overlays on the view surface. Thus, the label remains legible independently of the view of the object selected.

Both of these types of graphical text are useful depending on the job to be done. Model 520 BASIC provides statements to generate both types. In addition, the fonts used for generation of the characters can be defined by the user. Thus, Gothic or Roman characters can be viewed as part of an object or used to annotate a plot.

Input Device Tracking. Interactive graphics systems use input device tracking to provide operator feedback. The position of a locator graphics input device is echoed on a plotting device. For example, the position of the stylus on an HP 9111A Graphics Tablet is mimicked on the integral display of the Model 520 by using the graphics cursor of the display. The Model 520 BASIC graphics system allows this tracking to be done concurrently with the execution of the user's program. This is implemented via a tracking process that executes asynchronously with the process executing the program. Thirty times a second the tracking process wakes up, reads the locator device position, updates the plotter echo position, and goes back to sleep. This provides a smooth, continuous updating of the echo position, facilitating operator interaction with the program. In turn, the program does not need to be concerned with continually providing the operator with this feedback. Tracking can, of course, be terminated, or it can be established

**Fig. 3.** Viewing pyramid (shaded area) specified by program given in Fig. 2 as seen (a) looking along Y axis from +y to -y, and (b) looking along X axis from +x to -x. The coordinates of the reference point in the scene to be viewed are specified in line 20. The direction of the normal from the viewing window (display screen) to this reference point is specified in line 30. The position of the window about the normal is specified by line 40 and the distance of the window from the reference point is specified in line 50. Line 60 specifies the location of the observer's eye with respect to the window.

between multiple pairs of input and plotting devices. The performance of the program suffers only a 7% degradation because of this tracking.

# **Asynchronous Graphics Input**

Interactive graphics often uses graphics input device events to trigger an action. A Model 520 BASIC program can handle input from several graphics input devices. The operator can press the stylus or select a menu item on a digitizing tablet. These events are captured very quickly under interrupt and placed in an event queue that can be sampled later by the program. In addition, the program can specify, using an ON branch, that a particular routine is to be invoked when the event occurs. This frees the program from constantly checking the event queue for events and provides for true event-driven program design.

# Extensibility

The Model 520 BASIC graphics system software is designed to separate device-independent processing from device-dependent processing. The device-independent portions of the pipeline transform output primitives to virtual device coordinates. Device-dependent drivers are concerned with the peculiarities and coordinate systems of individual peripheral devices. These drivers map the virtual coordinates into the hardware device coordinates and perform any required formatting and I/O.

This structure allows the easy addition of new device drivers. Thus, this graphics subsystem can be easily extended to take advantage of new peripherals. The recent release of the HP 97062A Color Video Interface and the HP 97060A Graphics Processor illustrates this extensibility and demonstrates the ability to support future peripherals.

# **High Performance**

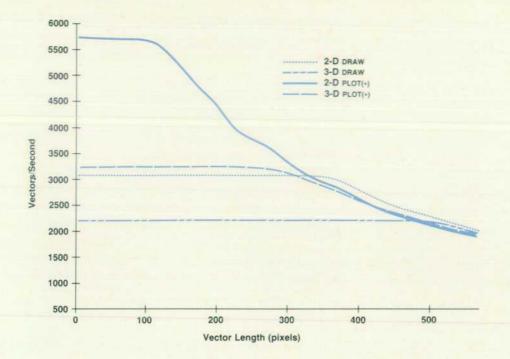

A major goal was to provide high-performance graphics. The original goal was to generate vectors ten times faster than the rate for the HP 9845C Computer of 250 vectors per second. The Model 520 Computer far exceeds this goal. Two-dimensional vectors can be generated in buffered mode at 5500 vectors/s (see Fig. 4).

Many components contribute to this performance. The Series 500 32-bit processor's speed and the vector generation rates of the HP 98770A Display for the Model 520 are essential. In addition, the performance reflects a planned tuning phase in the implementation process.

The tuning tools available to the design team included a debugger that allowed execution tracing and a software scope that provided execution time profiling. These tools were the key to minimum effort in performance tuning. They allowed detailed analysis of software performance and bottlenecks. This enabled selective tuning and recoding efforts to be concentrated on the areas that could provide the largest dividends.

The code modularity was also a contributing factor to the performance. The implementation is based on a modular design with ease of system construction, ease of maintenance, and reliability as primary goals. This same modularity permitted independent tuning of bottlenecks and experimentation with alternative algorithms and code sequences. Entire modules were rewritten without impact on the overall system. The result of this tuning effort was a sixfold performance improvement over that for the untuned code.

The generation of the viewing transformation matrix was a performance bottleneck until the tuning efforts improved the performance. Each vector endpoint is multiplied by this matrix to transform the point into virtual device coordinates. The matrix is logically constructed when the viewing operation changes by multiplying the matrices defining the component transformations to generate the transformation matrix. To reduce the time to compose this matrix, a

Fig. 4. The graphics system for the desktop Series 500 Computer, the HP 9000 Model 520, provides a vector generation rate more than 20 times faster than that provided by the earlier HP 9845C Computer (250 vectors/s).

program was written to multiply matrices defined in terms of symbolic equations. This yields a transformation matrix with individual elements expressed as equations. The values for the transformation matrix can be generated at run time by evaluation of these equations using current variable values rather than the standard matrix multiplications. These equations are simpler than the original matrix multiplication, because many terms cancel or combine. Hence, the number of required operations at run time is greatly reduced.

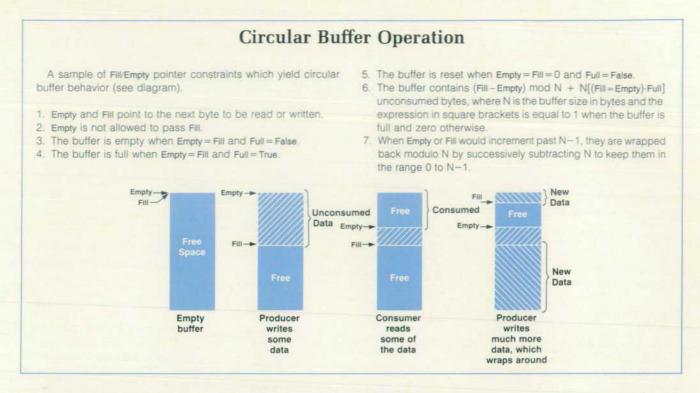

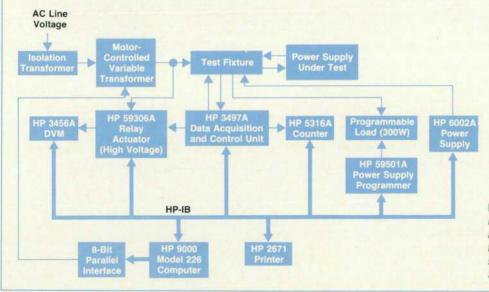

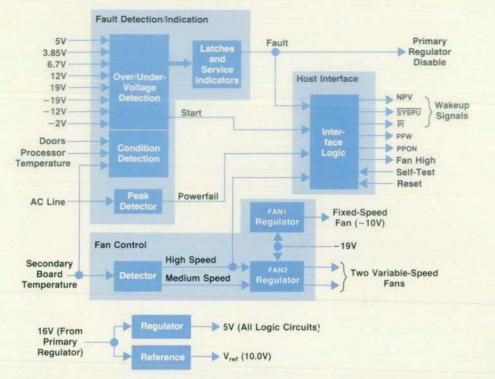

# Reliability