# THE COMPUTER APPLICATIONS **JOURNAL**

SIGNAL **PROCESSING**

SPECIAL SECTION: **Embedded** Interfacing

RISC vs. DSP The Photonic Transistor Instant PC Boards

August/September, 1992 — Issue #28

# EDITOR'S INK

**Process This**

hile the term "signal processing" can cover a full range of topics, we've decided to concentrate on digital signal processing in this issue's theme articles. DSP continues to he a hot topic, with more and more

consumer and industrial devices showing up on the market sporting features and capabilities previously found only on very expensive equipment or not found anywhere at all.

Does digital signal processing necessarily mean the use of a dedicated digital signal processor chip, though? In our first article, we take a look at instances where some of today's fast RISC processors actually look pretty good next to dedicated **DSPs** in traditional DSP applications.

Our next two articles move away from benchmarks and theory and into the practical uses of DSP chips. Audio spectrum analyzers have traditionally been built using rows of analog filters tuned for specific frequencies. Using DSP, though, our first project fits in the palm of your hand while analyzing the frequency content of a voice input and displaying the results on an oscilloscope screen. Our second project demonstrates the dynamic nature of filters implemented using DSP as the DSP2000 Audio Waveform Shaper works to extract voice from a signal full of static.

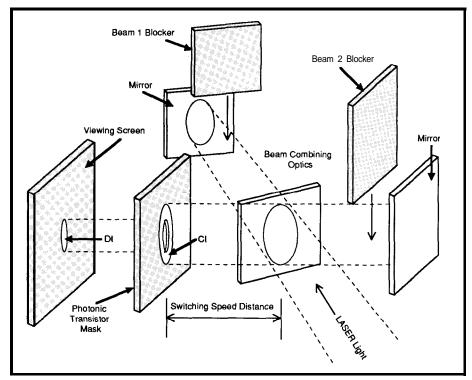

I'm particularly excited about the last article in the feature section this issue. The single most important invention in the development of today's high-speed electronic computer was unquestionably the silicon transistor. However, electron-based computers are quickly approaching theoretical limits when it comes to speed and size. Light is certainly going to play a large role in future computers. We are thrilled to be the first publication to run an article detailing a new invention that could be as important to the computer industry as the silicon transistor: the photonic transistor. Using light and holograms, future computers many orders of magnitude faster than today's best desktop machines will be the norm, all based on the very simple photonic transistor. Be sure to check it out.

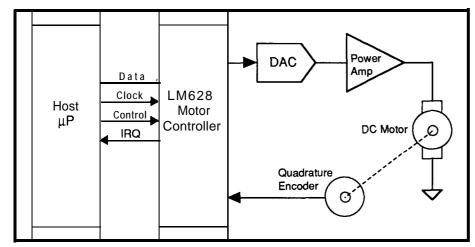

In our special section, we take a look at how to replace the popular stepper motor with a closed-loop DC motor control system that offers additional benefits over steppers. In the second article, we discuss a topic many readers have written to us about: designing with programmable logic devices. There are some pitfalls you have to avoid if you want a solid design.

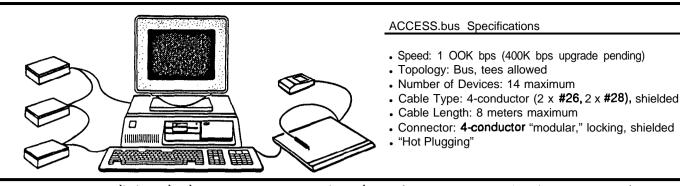

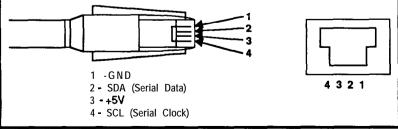

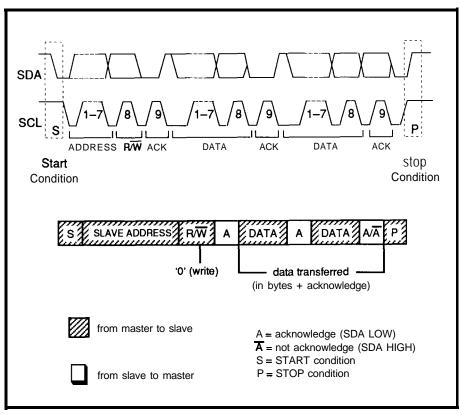

Rounding out our issue are our regular columns. Ed wraps up his series describing the various HCS II modules by presenting some tricks he used in the DIO- and ADIO-Link modules. He also lets us in on a very useful debugging session that took place in the Circuit Cellar. Jeff shares the results of his experiments using the latest in instant PC board etching systems. Tom reviews a new standard designed to eliminate much of the cable clutter found behind a typical PC. Finally, John explores some options for reducing power consumption in battery-powered embedded systems without the need for complicated power monitoring hardware.

In our next issue, we'll have articles dealing with Measurement 8 Control and Embedded Graphics & Video, so watch for it in the mail.

CIRCUIT CELLAR I N K

### THE COMPUTER **APPLICATIONS JOURNAL**

FOUNDER/EDITORIAL DIRECTOR

Steve Ciarcia

**PUBLISHER** Daniel Rodrigues

MANAGING EDITOR

Ken Davidson

PUBLISHER'S ASSISTANT Susan McGill

ASSOCIATE **EDITOR** Lisa Nadile

**CIRCULATION** COORDINATOR Rose Mansella

**ENGINEERING STAFF** Jeff Bachiochi 8 Ed Nisley

**CIRCULATION ASSISTANT** Barbara Maleski

CONTRIBUTING EDITORS

CIRCULATION CONSULTANT Gregory Spitzfaden

Tom Cantrell & John Dybowski **NEW PRODUCTS EDITOR**

BUSINESS MANAGER Jeannette Walters

ART DIRECTOR Lisa Ferry

**Harv** Weiner

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK (ISSN 0896-8985) is

STAFF RESEARCHERS:

Northeast John Dybowski Midwest

Jon Elson & Tim McDonough

West Coast Frank Kuechmann

published bimonthly by Circuit Cellar Incorporated. 4 Park Street, Suite 20. Vernon, CT 06066 (203) 8752751. Second-class postage paid at Vernon, C T and additional offices. One-year (6 issues) subscription rate U.S.A. and possessions \$1795. Canada/Mexico \$21.95, dloUwcanries S32.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders to Circuit Cellar INK, Subscriptions, P.O. Box 3050-C, South-

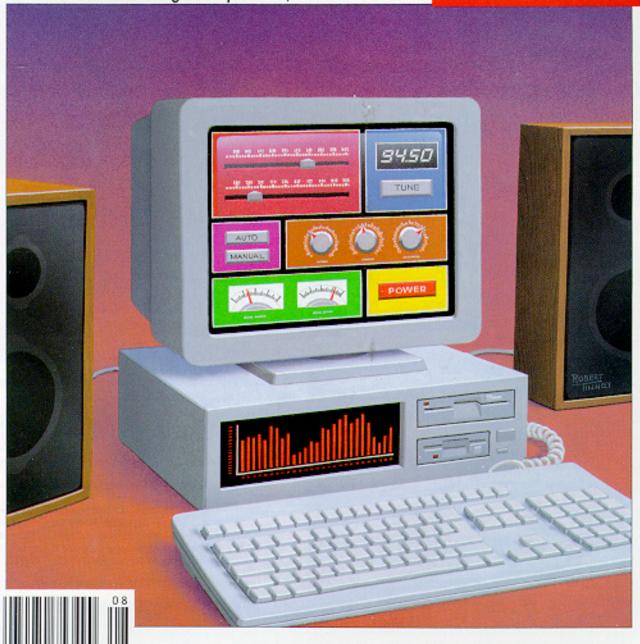

Cover Illustration by Robert Tinney

POSTMASTER: Please send address changes to Circuit Cellar INK. Circulation Dept., P.O. Box 3050-C. Southeastern, PA 19398.

eastern. PA 19398 or call (215) 630-1914.

### **HAJAR** ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST Debra Andersen (617) 769-8950 Fax: (617) 769-8982

SOUTHEAST Christa Collins (305) 9668989 Fax: (305) 9858457 WEST COAST Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

MID-ATLANTIC

Barbara Best (908) 741-7744 Fax: (908) 7416823 **MIDWEST** Nanette Traetow (708) 789-3080 Fax: (708) 789-3082

Circuit Cellar BBS---24 Hrs. 300/1200/2400 bps, 8 bits, no parity, 1 stop bit, (203) 871-1988; 9600 bps Courier HST, (203) 871-0549

All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK.

Entire contents copyright @1992 by Circuit Cellar Incorporated. All rights reserved. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# INSIDE ISSUE 28

- 26 Analyze Voice in the Palm of Your Hand by Gerald McGuire

- 34 Shaping the World of Sound by Steven Avritch

- The Dawning of the Light Transistor/

An Optical Computer Method Using Interference Fringe Component Regions by John N. Hait

## SPECIAL SECTION Embedded Interfacing

50

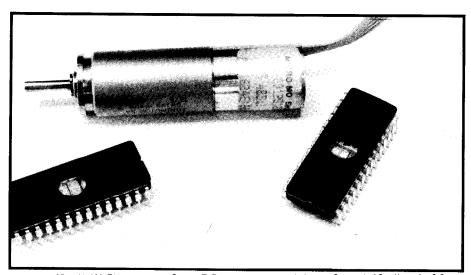

Closing the Loop on DC Motor Control by Tom Dahlin & Don Krantz

58

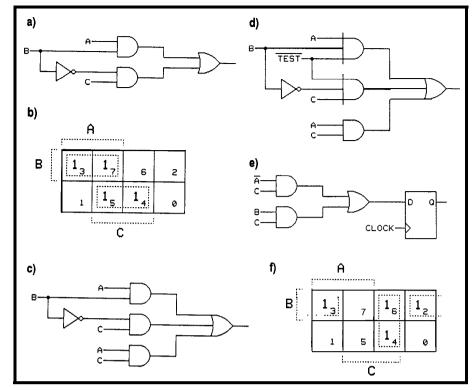

**Designing with Programmable Logic** by Charles R. Conkling, Jr.

- Editor's **INK/Ken** Davidson **Process This**

- Reader's INK-Letters to the Editor

- New Product News edited by Harv Weiner

80

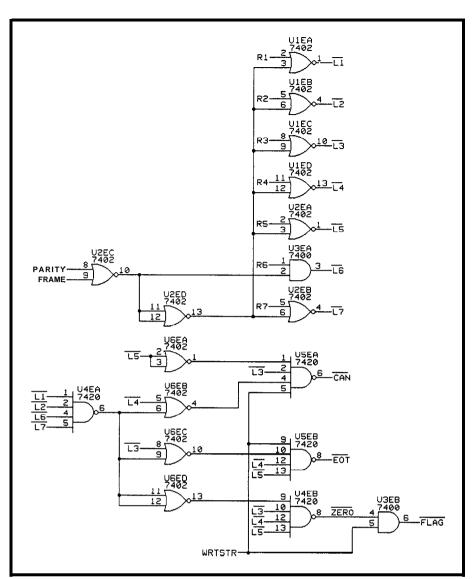

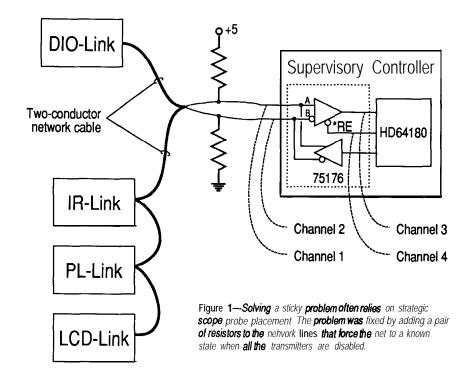

- Firmware Furnace/Ed Nisley

HCS Ii War Stories and I/O Links

- From the Bench/Jeff Bachiochi Approaching PCB Nirvana

- Silicon Update/Tom Cantrell

The Ultimate Desk ACCESSory?

- Practical Algorithms/John Dybowski

Power Code

- **ConnecTime**—Excerpts from the Circuit Cellar BBS conducted by Ken Davidson

- Steve's Own INK/Steve Ciarcia

Cost is in the Eye of the Beholder

- 97 Advertiser's Index

# READER'S INK

### **DS5000** Ideosyncrasy

Having just received issue #27, I was pleased to see another article ("The Elements of a Data Logger" by John Dybowski) that made use of the Dallas DS5000 microcontroller. I have been using this module for a while now, and feel that its advantages in board area, easy downloading, and nonvolatility outweigh its high cost. My only gripe with it is that the versions with more than 32K of memory do not come in the 40-pin DIP form factor.

However, John made a comment in his article that may mislead future users of the device regarding a problem that stumped me for a while. He says, "Also, note that all the pins of port 2 are available for use as general I/O because the RTC is referenced using  $\boldsymbol{M\!V} \boldsymbol{X}$   $\boldsymbol{A}$ , BRO-type instructions that have no effect on the high-order address bus."

What he says is true, and it is also true that explicit references to the embedded RAM of the DS5000 (using MDVX A ,@RO-type instructions] are performed on a separate internal bus that avoids disturbing P2. However, during the MDVX A, @RO-type instructions, certain values that may happen to be on P2 can cause implicit references to the embedded RAM, using a feature known as "page-mode addressing." When this happens, the external memory cycle will not occur, and the embedded RAM will be accessed instead, causing mysterious behavior in the best case, and embedded RAM corruption in the worst.

What this means is that P2 is not completely available for general I/O when you also want to use PO as a multiplexed bus. In my case, I simply avoided using P2.7 and left it set to a "1." This forced all page-mode accesses into the high half of the address space, which is never used for embedded RAM accesses in either the 8K or 32K versions of the DS5000.

The *Computer Applications Journal* is one magazine I really look forward to receiving-I read it cover to cover as soon as it arrives. Thank for doing such a great job.

Dave Tweed, Littleton, MA

### Get the Noise Out

(The following exchange took place on the Circuit Cellar BBS:]

In your February/March 1992 issue (#25), Mark Nurczyk went a long way to preprocess the input of an A/D converter, and although he goes through a number of valid points (like Spice modeling and some other production concerns) in his article, he seems to miss the whole point altogether.

Such preprocessing would be fine if the reason were noise or the like, but as the problem is DC offset and input scaling, there are easier ways to accomplish it. If the ADC is some standard part like the ADC0808 or ADC0809 or almost any other ADC, you can modify the reference inputs to suit your needs.

In Mark's example, by using 2.25 V and 3.9 V in the REF- and REF+ inputs (it can be done with a simple three-resistor divider in the relation 1.3:2:2.7), the thermometer would use 84% of the full range, so the precision goes to  $1.2^{\circ}F$  per bit.

Another useful alternative would be adding a small noise source ( $\pm 1$  bit) to the reference inputs (this could be done with the same microcontroller and some passive filter components). This dither noise can be filtered out with a promediation routine in the processor, so you could accomplish any needed precision (with ADC linearity and, maybe, measurement time the only limiting factors).

Edgar Brown, Universidad Simon Bolivar, Caracas, Venezuela

### Ed Nisley replies:

Welcome aboard!

I'd like to see a good presentation of using the dithering trick on analog inputs. I've read a little about it, but could use a practical tutorial. Are you up to a brain dump on the subject (if it's too expensive from Caracas, don't do it just for me!).

### Edgar Brown replies:

Well, I don't know if I could do a tutorial on this, but here is my best attempt [I've only had 4 hours of sleep in the last 2 days! ):

Dithering is based on promediation of added noise to a signal. Let's say you have a signal that you have to measure. There is too much noise added to it and you know the noise has no DC (i.e., its mean is zero). You could get a good guess by sampling the signal several times and the getting the mean of the samples. E(S+noise) = E(S) + E(noise), where E() is expected value or mean. It works real well in the analog domain.

In the digital world, you could use the same principle by considering the quantization of a signal as noise added to it. However, the problem is the noise is corre-

lated to the signal. If there is no noise in the original signal, finding the mean of a lot of samples would do no good.

However, if you add some noise to the signal (with zero mean), and this noise is of little amplitude (it makes no sense to hide a good signal with the noise we are adding), you can decorrelate the quantization noise from the signal and make it look like real added noise. Now by finding the mean of the samples, you can filter out the noise.

For this to work, the noise must be at least the size of the quantization noise (i.e., 1/2 an LSB of the quantizer). However, if you wish to account for problems like nonlinearities in the ADC, you can make the noise a little bigger so it spans several bits.

Hope this helps.

### Ed Nisley replies:

OK, so there are three principles: the noise must be added in the analog front end, it's got to be relatively small, and you have to know what the characteristics are so you can filter it out digitally once it's been quantized.

I'll add that to my list of Things to Read More About...thanks for the update!

### And We Have a Winner

Congratulations to **Curtis Goodson** of Austin Texas. Curtis is the winner of our latest Tech Deck contest sponsored by Contact East and the **Computer Applications** Journal. He will be receiving a Fluke 87 Digital Multimeter.

Be sure to watch your mail for future Tech Decks and more contests!

### We Want to Hear from You -

Our readers are encouraged to write letters of praise, condemnation, or suggestion to the editors of The Computer Applications Journal. Send them to:

The Computer **Applications** Journal letters to the Editor 4 Park Street Vernon, CT 06066

# OUERFOLD

# 320C25 DSP ASAP \$1,995

Drive your embedded 320C25 design to market as fast as possible with our 320C25 in-circuit emulator. The MACROCHIP 'C25 emulator features real time emulation to 50 MHz with no wait states, 64K words of program overlay memory, simple software breakpoint, single step trace, disassembler, and RS-232

communications for fast downloading of programs from your PC COM port.

Call, write or fax for literature:

1301 N. **Denton** Drive Carrollton, TX 75006

Tel I-800-783-9546 Fax 214-245-1005

102

# INSTANT 320C25 MONITOR \$295

Ever wondered what it would be like if you could communicate with your 'C25 application using your PC COM port? Well, we have. Now we are offering you a C25 chip already programmed with a 4K-word monitor in internal program

memory. All you have to do is insert the chip into your target socket and hook up the BIO and XF pins to a MAX 232. With the instant 'C25 monitor, you will be able to download/upload TI-tagged or Intel hex files directly into your target application at speeds to 9600 baud, examine/ edit internal/external memory and I/O. We'll give you entry points so you'll be able to call the GET-CHAR, GET\_LINE, COUT, PARSE, ASC\_TO\_HEX, etc. routines already in ROM.

For only \$295 more, we'll even sell you a symbolic debugger you can upload to your target application.

Call, write or fax for literature:

1301 N. Denton Drive Carrollton, TX 75006 Tel I-800-783-9546 Fax 214-245-1005

Edited by Hary Weiner

## MC68332 **SINGLE-**BOARD COMPUTER

A low-cost, high-speed, low-power single-board computer based on the Motorola MC68332 32-bit microcontroller has been announced by Vesta Technology. The Vesta SBC332 has features that make it ideal for embedded systems control and development.

Based on the powerful MC68020, the MC68332 has a 32-bit internal data path and 32-bit internal address bus. Externally, it has a 16-bit data bus and a 24bit address bus. This feature, coupled with a 16.78-MHz clock, makes the SBC332 a potent embedded system "engine." The 68332 microcontroller features on-chip RAM, a Queued Serial Module (QSMJ, and an intelligent 16-bit Timed Processor Unit (TPU). These integrated peripherals allow a variety of complex operations with minimal CPU intervention. Lowpower operation is fully supported with minimal power consumption during normal operation (110 mA), the capability to reduce clock speed as the application permits, and a standby mode.

The Vesta SBC332 is Motorola Business Card Computer (BCC) compatible so allows the direct use of software systems designed around Motorola's popular

evaluation platform. The Vesta SBC332 features socketed 28- and 32-pin DIP external memory, which includes two 8-bit EPROMs with a capacity up to 1 MB and two 8-bit SRAMs with a capacity up to 1 MB. An external watchdog and supercap-backed standby SRAM are also provided. The SBC332 measures 2.3" x 6.25" and maintains compatibility with the BCC P1 and P2 connectors.

Two peripheral cards, designed to facilitate prototyping, are also available. The **MFP332** Multifunction Peripheral adds A/D and D/A conversion to the SBC332. The ADC subsystem will acquire 12 bits of analog

data from any of eight channels at over 80 kHz. Four independent 12-bit DACs provide a O-IO-volt output range. Both ADC and DAC are connected to the 16-bit-wide bus. Two additional RS-232 serial channels, one of which may be configured for RS-485 operation, are also provided.

The LBK332 LCD, keypad, and beeper peripheral is the operator interface to the SBC332 in embedded applications. It supports alphanumeric displays from 1 x 8 to 4 x 40, providing negative Vss when required. A self-scanning keypad circuit supports up to 8 x 8 keys and will generate an interrupt upon keypress. A multitone audio annuncia-

tor is intended to assist during data entry via keypad.

The Vesta Technology SBC332 single-board computer sells for \$249 and the MFP332 Multifunction Peripheral sells for \$229, both in quantities of 25. The LBK332 is priced at \$79 in single quantities.

Vesta Technology, Inc. 7100 W. 44th Ave., Ste. #101 Wheat Ridge, CO 80033 (303) 422-8088 Fax: (303) 422-9800

### MINIATURE XT-BASED COMPUTER

**Dover Electronics** has announced an innovative miniature computer, the E.S.P 8680. Based on the Chips and Technologies 8680 single-chip computer, the module measures 1.7" x 5.2" and provides full computing functionality. It has a fully integrated 8086XT with a nonvolatile memory card socket (PCMCIA), CGA graphics, up to 1 MB of RAM, a keyboard interface, one serial port, and expansion connectors.

The E.S.P. 8680 was designed to permit expansion and upgrades. The double-sided surfacemount technology produces a very small, dense module that fits into a OS-inch-on-center backplane in 3-D fashion. In addition to core

processing, add-on E.S.P. modules provide functions such as PCMCIA, modem, fax, packet radio, network interface, SCSI, ADCs and DACs, static memory, and bar-code scanning, all in the same form factor.

Other features internal to the C&T 8680 chip include an intelligent sleep mode for reduced power consumption, a SuperState R mode for a separate operating environment and the enabling of full I/O and

interrupt monitoring without BIOS modification, and a four-stage pipeline and 14-MHz speed for performance comparable to a '286based system. A 26-bit address bus enables a 64 MB-memory map and directly supports a PCMCIA memory card. A virtual interrupt feature allows interrupts to be monitored. redirected, or both, before any operating system, application program, or TSR sees them.

A development kit with the E.S.P. 8680 is available for \$995.

Dover Electronics 1198BostonAve. Longmont, CO 80502 (303) 772-5933 Fax: (303) 776-1883

#501

### 64-MHZ ADC BOARD FEATURES 16-MB BUFFER AND DSP LINK

Sonix Inc. has announced the STR'864, a 64-MHz Transient Digitizer board featuring simultaneous sampling at 64 MHz on two channels, a high-speed DSP link, and a flexible memory buffer scheme providing up to 8 MB of memory per channel or 16 MB on one channel. It provides freedom from the static architecture of a stand-alone digital oscilloscope and from the slow data transfer rates between a stand-alone instrument and the computer.

The STR\*864's high-speed data acquisition memory is mapped directly into PC memory space. Once the waveform has been captured, the PC can transfer data off the board at l-MHz (8 bits) or 3-MHz (16 bits).

The STR\*864 will not slow down PC operations due to its 25-ns RAM and fast bus interface logic. As the processing speed and power of the PC's microprocessor increases, the STR\*864 will continue to provide bus and memory access speed compatibility. A special high-speed data transfer link has been included because the STR\*864 is expected to be used with DSP boards.

All board functions are under software control including input impedance selection, AC/DC coupling, input voltage range, sampling rates, ADC output coding, trigger selection, clock control, threshold phase and level, board selection, and interrupt enabling.

The STR\*864 is well suited for two-channel, phase coherent acquisitions as in radar applications. Other applications include digitizing waveforms, processing real-time signals, spectrum analysis, capturing transient data, implementing ultrasonic inspection systems, and analyzing optical and laser signals. More than one board may be installed for multichannel applications. Pricing was not available at press time.

Sonix, Inc. . 8700 Mbrrissette Dr. . Springfield, VA 22152 . (703) 440-0222 . Fax: (703) 440-9512

### HIGH-LEVEL/LOW-LEVEL DEBUGGER FOR 8051

A high-level debugger for 8051 C compilers that is **keypress** compatible with Borland's Turbo Debugger has been announced by **ChipTools.ChipView-51** is available in two versions: a high-performance simulator/debugger or a front end for the Nohau **EMUL5** l-PC emulator.

With ChipView- 1, the Turbo C programmer can instantly begin debugging code in the embedded-systems environment. ChipView- 1 presents over 14 different views of your program, including all of Turbo Debugger's views. Screen layout is fully user configurable with movable, resizable, and zoomable windows for 25-, 43-, and 50-line EGA/VGA modes. Features include data browsing of C structures and linked lists using point and click, and over 100K of context-sensitive hypertext help. ChipView- can display a C-level call stack, which displays nested function calls along with their arguments-a powerful view absent from other 805 1 debuggers.

The emulator/debugger version for Nohau's **EMUL51-PC** is tailored to fully support its emulator and trace boards. Emulation and trace collection can continue to run while you analyze a trace history.

The high-speed simulator version running on a 33-MHz '486 PC achieves the real-time speed of a 12-MHz 805 1. This level of performance makes it ideal for testing entire programs in a safe environment, even before the application hardware is designed. In addition, chip I/O can be simulated for both polled and interrupt-driven systems. Like the emulator version, the simulator can not only collect a trace history for execution analysis, but also reverse-execute, or "undo," back to a previous state whenever a bug is detected, backing into and out of interrupt code if required.

ChipView- 1 is the only 805 1 debugger to support all popular 8051 C compilers at a high level, and features total compatibility with all object formats. Unlike debuggers that support only simple data types, ChipView- 1 lets you browse through C structures, unions, enumerations, bit-fields, pointers, and arrays.

The simulator version of ChipView- sells for \$795, the emulator version for \$595, and a combo package for \$995. System requirements include an IBM XT or compatible with 640K RAM and a hard disk. Additional system RAM as EMS or XMS is recommended for programs with sizable debugging information.

### ChipTools

1232 Stavebank Rd. • Mississauga, Ontario • Canada **L5G2V2** (416) **274-6244** • Fax: (416) **891-**2715

#503

## PC SERIAL PORT TO DATA ACQUISITION CONTROL MODULE

**B&B** Electronics is offering a general-purpose control module that is connected to your **com**puter's RS-232 serial port. The **Model SPIO** can be configured and manipulated using a PC or compatible and an easy-to-use **com**mand set. The SPIO comes with an instruction manual and a diskette that includes configuration, **demonstra**tion, and upgrade programs.

The SPIO has eight programmable I/O lines, eight 8-bit ADC inputs, and two 8-bit DAC outputs. Digital output lines may be used as normal outputs or delayed on/off. One digital output is available as a programmable pulse-width output. The digital input lines may be used as normal inputs or latches, and two digital inputs are available as event counters. I/O lines are available through a female DB-25 connector.

Two compatible interfaces are available for

the SPIO. The SDIOB8 connects to the SPIO and offers a watchdog circuit for its eight programmable I/O lines. Each I/O line has an LED status indicator and can be used to control voltages as high as 50 VDC. The DAPBl connects to the SPIO to provide terminal block access to available I/O lines. The DAPBl has a prototype area available for custom signal conditioning circuitry.

The SPIO sells for \$119.95. The SDIOB8 interface module sells for \$69.95 and the DAPBI for \$49.95. A separate power supply (232PS3) is available for \$14.95.

B&B Electronics P.O. Box #1040 Ottawa, IL 61350 (815) 434-0846 Fax: (815) 434-7094

### **HIGH-PERFORMANCE** SINGLE-BOARD COMPUTER

Innovative Integration is now shipping the SBC25 high-performance single-board computer.

The SBC25 couples the Texas Instruments TMS320C25 microcontroller and C or FORTH programming language to provide a complete, integrated solution to the

development and implementation of real-time applications. The TMS320C25 architecture is optimized for

> ates at a sustained 12-MIPS throughput. The processor provides one 16-bit counter/timer, three prioritized interrupts, on-chip RAM/ ROM, and a 16-bit single-cycle multiplier/ accumulator. Additionally, the 160-mm x 100mm SBC25 features an on-board real-time clock, an eight-channel prioritized interrupt control-

ler, a 2-Mbps DUART,

computationally intensive

DSP algorithms and oper-

three **8-bit** digital I/O ports, three 16-bit counter/timers, a watchdog timer, a multiplexed 12-bit 330kHz ADC with a programmable gain amp, and four 12-bit 100-kHz DACs. Up to 16 MB of battery-backed RAM/ ROM is supported.

The SBC is priced from \$499 in single quantities. Complete development packages start at \$2995.

Innovative Integration 4086 Little Hollow Pl. Moorpark, CA 93021 (805) 529-7570

#505

# ROMboy

### Low Cost, Reliable, High Quality **ROM** Emulation from the Creators of PROMICE

- Emulation of up to 1 Mbit ROMs (4 Mbit-soon)

- Supports any ROM type (DIP or PLCC)

- · Supports high speed ROMs

- Supports any word size up to 2048 bits wide

- Host software for DOS, Unix, Mac, VMS

- Battery backed memory

- Intelligent micro-controller based unit

- SMT CMOS layout for robustness

- Tiny size: 2.5" x 3.8" x 0.9"

- · Unbelievably low price!

### ROMboy...

from the authority in firmware development tools

Orders: (614) 899-7878 West: (415) 750-0219 (614) 899-7888 FAX:

#105

# lake It

Take it easy on your cargo with a custom Cabbage Case built to the exact dimensions of pour equipment.

Take it easy on your back with our extension handle and tilt wheels options.

Take it easy on your wallet. Let Cabbage Cases show you how easy it is to

save money on quality, custom-built road cases that make shipping and traveling with your valuable cargo safer and easier. Prices quoted over the phone.

Call 800-888-2495 today.

1166-C Steelwood Rd. Columbus, OH 43212

800/888-2495 614/486-2495 FAX /486-2788

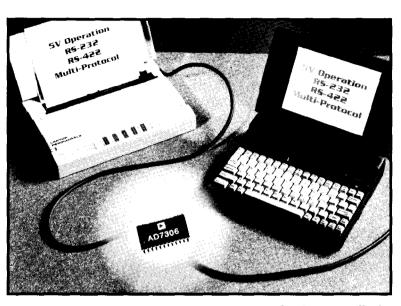

## SINGLE-SUPPLY MULTIPROTOCOL TRANSCEIVER

Systems that must operate from a single 5volt supply and communicate with other equipment using industry-standard RS-232 and RS-422 protocols can benefit from a chip announced by Analog Devices. The AD7306 is a multiprotocol driver/ receiver chip that offers two RS-232 drivers, one RS-422 driver, one RS-232 receiver, and a configurable RS-232/RS-422 receiver in a 24-pin SOIC package.

The single-supply AD7306 generates ±10 volts internally using a charge pump voltage converter. The charge pump allows RS-232 output levels to be developed without the addition of complex

external bipolar power supplies. Unlike designs that require expensive, bulky capacitors of up to 10 µF for operation, the AD7306 charge pump is efficient enough to operate using nonpolarized, miniature 0.1-µF capacitors, considerably

saving circuit board space. Additionally, some of the charge pump output is available to power external circuitry requiring dual supplies.

The AD7306 transceiver provides an interface between TTL/CMOS signal levels and dual standard EIA RS-232/RS-422 signal levels.

The RS-232 channels communicate at rates up to 100 kHz, and the RS-422 channels are suitable for high-speed communications up to 5 MHz. Timing skew (T,,) for RS-422 communication is typically only 2 ns. No-load power consumption is typically 50 mW with 100 mW maximum.

The AD7306 sells for \$3.75 in quantities of 1000.

Analog Devices

181 Ballardvale St.

Wilmington, MA01887

(508) 658-9400

#506

### DIGITAL SIGNAL PROCESSING BOARD

A digital signal processing board with analog and digital I/O has been announced by Dalanco Spry. The Model 500 is designed for the PC/AT- and ISA (Industry Standard Architecture)-compatible microcomputers. Applications include data acquisition, instrumentation and control, speech and audio, as well as general-purpose DSP software development.

The Model 500 is based around the Texas Instruments TMS320C5120-MIPS DSP. The unit provides data acquisition for eight channels at 12-bit resolution and a maximum 225-kHz sampling rate. Two 12-bit analog output channels are also provided, along with a buffered digital I/O connector for user expansion and the two serial interfaces of the TI DSP.

The board is populated with 64K words of program RAM and 128K words of dual-ported data RAM. The dual-ported architecture enables the creation of applications requiring simultaneous mathematical calculations coupled with concurrent analog and disk I/O.

The Model 500 features high throughput to the host PC's memory (up to 3 MB per second) and disk. Multiple boards may be used within a single system. Depending on the host system, data may be written to or read from disk at the maximum sampling rate of 225 kHz.

Software included with the Model 500 consists of a TMS320C5 1 assembler and debugger, FFT software, real-time signal and spectrum display, concurrent record and playback to or from disk, digital filter examples and FIR filter code generator, and a waveform editor.

The Model 500 with TMS320C51 sells for \$1600.

Dalanco **Spry 89** Westland **Ave.** Rochester, NY 14618 (716) 473-3610 Fax: (716) 473-3610

### **FEAT**'URES

14

To DSP or Not to DSP

26

Analyze Voice in the Palm of Your Hand

34

Shaping the World of Sound

40

The Dawning of the Light Transistor

# To DSP or Not to DSP

# Will a RISC chip do it better?

Everyone usually assumes that to do true digital signal processing, a dedicated DSP chip is necessary.

Depending on the application, today's high-speed RISC processors may do just as good a job.

# FEATURE ARTICLE

M. R. Smith

ne of the few advantages a university professor has is combining re-

search and teaching. I am able to expand my own knowledge in my chosen field as well as impart my experience to others with similar interests. The work I share with you here is a rewarding combination of results from both these vocations.

As a research project, my students and I designed a number of high-speed coprocessors for use in modeling to improve the quality of magnetic resonance images and for other digital signal processing (DSP) algorithms. The fastest system we developed was based around an Advanced Micro Devices microprogrammable DSP byte-slice chip family, which is now obsolete. Their disappearance is no tragedy, because although the project was successful, the custom microprogrammed system's high pin count made it unreliable. Recently, we focused toward implementing our algorithms on the new single-chip DSPs coming on the market.

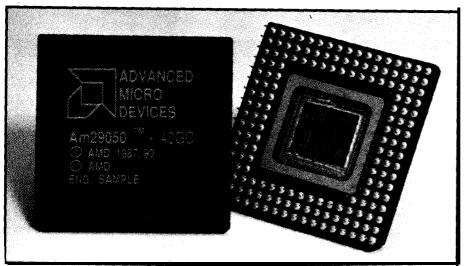

Teaching classes in computer architecture that involve the comparative analysis of high-speed processors has allowed me, with my students, to compare the architectural features of the Motorola DSP56001, DSP56200, and DSP96002, NECµPD77230, and Texas Instruments TMS320 family DSP products. More recently, we have examined the Advanced Micro Devices Am29050, Intel i860, Motorola MC88100, and the SPARC family of RISC chips.

We became curious about just how well the non-DSP, but high-speed,

RISC chips would stack up against the more dedicated DSP chips and where the design limitations existed. The RISC instructions expose much of the processor's internal architecture, which allows tailoring of the timing of an algorithm's operation to optimize the use of the highly pipelined RISC resources. The dedicated DSP chips are more like complex instruction (CISC) processors where timing optimization is not as available. However, the DSP's specialized hardware makes each instruction very efficient.

The RISC chips are good general-purpose processors with many practical applications. Two high-speed RISC chips proved very amenable for DSP applications, but for very different architectural reasons. The Am29050 has a large register window and additional high-speed registers, all with direct access to a fast arithmetic processor unit (APU). By contrast, the i860 gets its DSP capability through the use of a wide (64-bit) instruction cache and an extremely wide (128-bit) data cache.

In this application tutorial, I discuss the implementation of a Finite Impulse Response (FIR) digital filter using these processors. Although aimed specifically at the Am29050 and i860 processors, many of the techniques I describe can be used to your advantage in other RISC applications. I will show you how to overcome the problems experienced because of memory access difficulties and the typically long RISC floating-point unit

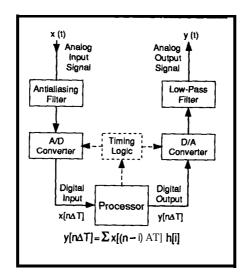

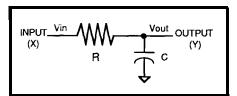

Figure 1-A *FIR* digital *filter* can be *constructed with* a processor and memory-mapped ADC and DAC devices. Conventional *filters* are used to *band limit the input* and *output*.

(FPU) pipeline. I'll discuss the limitations of the Am29050 and i860 as generalized DSP chips, and I'll suggest possible architectural modifications.

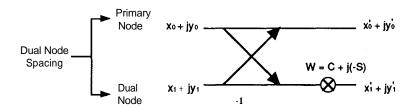

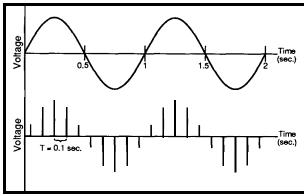

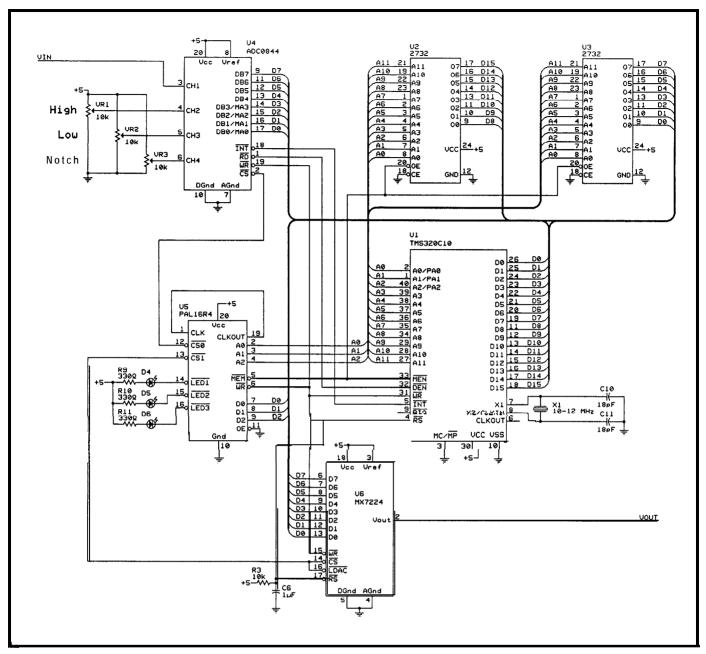

### FIR FILTER THEORY

Figure 1 shows the typical schematic for a dedicated real-time FIR digital filter system. The ADC, used to sample the input signal x(t), and the DAC, used to produce the filtered output signal y(t), are assumed to be memory mapped into the data memory space of the processor. This location means that simple reads and writes can be used to access their values.

The pseudocode for the FIR filter program is shown in Listing 1 using a C-like syntax. The analog input signal is first filtered to reduce the signal and noise bandwidth below the Nyquist rate to avoid signal contamination (aliasing). The digitizing occurs at intervals of AT seconds under the control of the timing logic. The new sampled input value,  $x[n\Delta T]$ , and the old digitized values,  $x[(n-1)\Delta T]$ ,  $x[(n-2)\Delta T]$ ,..., are stored in a buffer. The digitized filter output of a linear phase FIR filter with **LENGTH** taps,  $y[n\Delta T]$ , is determined from the simple summation equation

$$y[n\Delta T] = \sum_{i=0}^{\mathbf{UNGTH}-1} \mathbf{x}[(n-i)\Delta T] \times h[i]$$

where the digital filter coefficients, h[i], are designed to meet the required filtering response. For example, the output of a simple linear phase S-tap FIR filter is calculated from

$$y[n AT] = \{x[n AT] + x[(n-4) AT]\}h[0]$$

+  $\{x[(n-1) AT] + xi(n-3) AT]\}h[1]$

+  $x[(n-2) AT]h[2]$

The final analog signal is obtained by low-pass filtering the DAC output to remove the high-frequency components introduced during conversion. Before starting the next filtering stage, the circular buffer used to store the earlier input values must be updated. For the 5-tap filter above, the output is the same as

$$x[(n-4+i)AT] = x[(n-3+i)AT]; 0 \le i < 4$$

For long-length filters, this update would require considerable, time-consuming data movement or pointer manipulation.

## IMPLEMENTATION OF A FIR FILTER-ATTEMPT I

Implementing a FIR filter on a processor does have its difficulties. Filter coefficients must be expressed with sufficient accuracy to model the required filter response. You must also ensure there are sufficient bits in the APU to prevent either underflow or overflow during the summation,  $y[n \Delta T]$ . Although the number of bits required for this accuracy depends on the actual filter, a reasonable number of guard bits for the sum would be about 12 at either end of the digitized

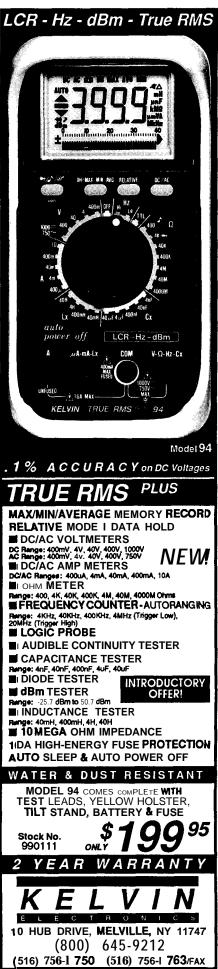

Photo I-The Am29050 RISC chip has a lot in its favor incertain DSP-oriented applications

input signal. For a 12- to 16-bit input signal, an APU with a width of 36 or more bits is required. For example, the Motorola DSP56001 chip maintains a 56-bit accumulator accuracy-much higher than the input signal's 24-bit width.

The FIR filter pseudocode (refer to Listing 1) indicates that considerable overhead will occur at each step of the filter to make sure the program does not write outside the circular buffer required to store the previous input values, x[n AT]. To cut this overhead, maintain the buffer using the specialized hardware you find in dedicated DSP chips (e.g., TMS320 and DSP56001).

Many DSP algorithms involve extensive loops. In a processor with a long instruction pipeline, these loops can cause time loss by stalling after a branch as new instructions are fetched. Some DSP chips get around this problem by allowing the repeat of a given instruction many times in a single instruction loop. Finally, sufficient additional registers for pointers and temporary variables are needed.

RISC chips often have a register window with a format very similar to a circular buffer. However, unless this window has easy access (no penalty) to a hardware multiplier, the implementation of the FIR equation will be greatly slowed. The scalar Am29050 has a large (128) register window with direct access to the high-speed FPU. The SPARC chip has a register window, but it does not have this direct access. The superscalar i860 does not have the register window; instead, it uses a dual-instruction capability to refill its smaller register bank in parallel with floating-point operations.

The filter coefficients also need to be stored where they can be accessed without penalty. In addition to the register window on the Am29050, there is a large additional register bank also with direct access to the FPU. Again, the dual instruction of the i860 can be used to create a similar capability. Some other RISC chips are not as fortunate, so their speed is considerably slower.

Listing 1-A direct implementation of a FIR digital filter can be described in C-like pseudocode.

```

/*Requires software implementation of a circular buffer

*/

int ReadA2D(void):

void SetUpCoeffs(float *.int);

void WriteD2A(int);

#define LENGTH

#define NUMCOEFFS 48

main0 {

/* data and filter coeffs buffers */

float x[LENGTH], coeffs[NUMCOEFFS];

/* control of the buffers */

float *buffstart, *buffend, *nextempty;

float *xrecent, *xancient, *coeffcurrent;

float sum

/* filter sum */

/* ADC and DAC integer values */

int xn. yn:

int count;

SetUpCoeffs(coeffs, NUMCOEFFS):

/* start up */

buffend = nextempty = x + LENGTH 1:

buffstart = x;

for (;;){

/* main loop */

/* get new value */

xn = ReadA2D();

/\star convert and store \star/

*nextempty = (float) xn:

/* adjust pointers to buffer */

xrecent = nextempty;

coeffcurrent = coeffs:

/* since circular */

xancient = xrecent + 1:

if (xancient>buffend) xancient = buffstart: /* wrapped? */

/* perform convolution, check buffer */

sum = 0.0:

for (count = 0: count < NUMCOEFFS 1: count++) {

sum +≈ *xrecent * *coeffcurrent;

if (--xrecent < buffstart) xrecent = buffend;</pre>

sum += *xancient * *coeffcurrent:

if (++xancient > buffend) xancient = buffstart:

coeffcurrent++;

sum += *xancient * *coeffcurrent;

/* center tap */

yn = (int) sum

/* convert and write out */

WriteD2A(yn);

/* update start of future circular buffer */

if (++nextempty > buffend) nextempty = buffstart:

```

The i860 and Am29050 meet the accuracy requirement because they can maintain a 64-bit internal representation in the FPU accumulators without any time penalties.

The branching in a heavily pipelined RISC has to be handled carefully. You can avoid stalls in the instruction pipeline by having an onboard cache to hold the most recently used branch instructions. Stalls in the ALU pipeline have to be handled in a different way, as I demonstrate later.

A number of RISC chips (including the Am29050 and the i860) have the ability to perform a simultaneous floating-point multiply-and-accumulate operation (FMC) without the necessity of fetching and initiating individual multiply and add instructions-a great timesaver. Most of the newer RISC chips have a floating-point capability that can simplify the design of DSP algorithms.

With these resources, I will show that implementing a 95-tap linear

phase FIR digital filter with a AT ≈ 3.0 μs sample time using the Am29050 and i860 RISC processors is possible.

The architectural features of the RISC chips play an important role in DSP applications. Of the two chips, the Am29050 has the simpler [more intuitively obvious) assembler instruction set, so the FIR filter will be discussed in terms of this chip.

Listing 2 shows the start-up Am29050 assembler code for the filter. Various mnemonics are established for the Am29050's 64 general-purpose registers (g r), used for the filter coefficients  $(H_n)$ , and the 128 local window registers (1 r), used as a circular buffer for the data  $(X_n)$ . Constants (such as addresses) needed inside the loop are placed in additional general registers for faster operation.

The first attempt at an actual 95tap FIR filter code is shown in Listing 3 and is an almost direct implementation of the pseudocode from Listing 1. The integer input value from the ADC is converted to a floating-point number before being stored in local register X 0. This step avoids the overhead of continually reconverting the previous digitized and stored values into floats during the time-sensitive filter loop. The FMC instruction is used to maximize the speed of the FIR equation. After the filter loop, the sum is converted back to an integer before being sent to the DAC. Finally, the circular buffer is updated by adjusting the register window using the register stack pointer (g r 1). In a single cycle, this instruction obtains what would otherwise require 94 register moves.

Generally, this code implies that an N-tap linear phase FIR filter can be implemented in N + 8 instructions. At first glance, this assumption would indicate that a 95-tap filter with 192 floating-point operations can be performed in 103 cycles (2.56 µs at 40 MHz). However, this result is not the case because it takes 4N + 18 cycles  $(9.95 \mu s)$  when run. The problem is the code does not take into account the RISC FPU's highly pipelined architecture used for the **FMC** instruction.

The other RISC chips fair even worse, with the i860 and MC88 100 requiring a time in the order of 6N-9N

cycles (≈15–23 µs). Not only is there the deep FPU pipeline, but these chips only have 32 registers attached to the FPU. These registers must be continually reloaded with data and coefficient values from the memory. In addition, the circular buffer operation must be handled in software, whereas on the Am29050 it was handled at low cost via the register window. Some current SPARC chips also have a problem because these data fetches must compete with instruction fetches on a single input bus. (Not all SPARC chips have exactly the same architecture; e.g., instruction caches.)

Details of the problems from the long FPU pipeline found in RISC chips are explained in terms of the Am29050 pipeline. Table 1 shows the effect of the pipeline operation for the consecutive **FMC** instructions needed to implement the start-up of the FIR operation

```

X0 = (float) X_n; CONVERT

sum = 0; FMAC

sum = XOxHO+sum; FMAC

sum = X1xH1+sum; FMAC

sum = X2 \times H2 + sum; FMAC

```

where X0, X1, and X2 are the respective current, last, and next-to-last inputs, and HO, H1, and H2, the corresponding filter coefficients. The pipeline stalls after the first **FMC** instruction as the processor waits for the conversion of  $X_n$  to complete. A second stall immediately occurs because the deep pipelined **FMC** instruction means that sum is not available for use by the second **FMC** instruction until six cycles later.

The most obvious result of these pipeline problems is the occurrence of three **STALLs** as each **FMC** instruction waits for the last to complete. Also, a sequence of eleven **STALLs** occurs after the last **FMC** instruction as the pipeline flushes. These stalls are completely transparent to the programmer, but they do not make the algorithm go any faster. Therefore, you must make use of the possible parallel operations on the Am29050 to fill in these transparent stall cycles.

On the other RISC chips, the FPU instructions must also be properly

Listing 2—The common start-up code for the direct (slow) and custom (fast) implementation of an Am29050-based floating-point FIR digital filter.

```

.cputype 29050

AB_PLUS_0, 4

.equ

; for FMAC

AB_PLUS_ACC, 0 ; for FMAC

. equ

. equ

SUM 0

: fp accumulator 0

FORMAT and ROUNDING control

.equ

SING_FP, 1

; is single precision fp

.equ

DOUBLE FP. 2

; is double precision fp

.equ

INT. 0

; is integer

NEAREST. 0

.eau

; round to nearest. integer

.equ

SIGNED_INT. 0; is signed integer

GENERAL REGISTER ALLOCATION

.set

A2D, gr127

; store ADC address location

. set

D2A, gr126

store DAC address location

ZERO, gr125

; store ZERO constant

. set

set.

Yn. gr124

: final value

; temporary storage of ADC input

Xn. 1r94

set

FIR coefficients

HO. gr64

; also H94

.set

.set

Hl, gr65

: also H93

.set

H2. gr66

; also H92

H3, gr67

; also H91

. set.

. . . . .

H45, gr110

.set

; also H49

; also H48

H46. grlll

.set

.set

H47. gr112

: center tan

X94, 1r0

.set

; input delayed by 94 sample periods

. set

X93. 1rl

; stored in CIRCULAR buffer

. set

X92. 1r2

; local registers

X91. lr3

.set

.set

X48, 1r46

X47, lr47

.set

X46. 1r48

. set

. . . . .

X3. 1r91

. set

; input delayed by 3 sample periods

. set

X2. 1r92

; input. delayed by 2 sample periods

X1, 1r93

; input delayed by 1 sample periods

set

.set

X0. 1r94

; current input.

ADC and DAC locations and fp filter coefficients locations

AtoDaddress, 0x80000000

.equ

DtoAaddress, 0x80000004

.equ

0x80000100

.equ

FILTERCOEFF.

text

.global

start

start:

: Set. FP Acc do d.p. mode for 64-bit accumulators

; Ignore all FP Exceptions

fpe. 0x43F

: FP environment

ntsrim

gr127. FILTERCOEFF

; read in filter coefficients

const

consth

gr127. FILTERCOEFF

; store as floats

ntsri m

cr. 47

; bring in 48 coefficients

0. 0, HO. gr127

loadm

A2D, AtoDaddress

: establish constants

const

A2D, AtoDaddress

consth

const

D2A, DtoAaddress

D2A, DtoAaddress

consth

const.

ZERO, $float(0.0)

ZERO, $float(0.0)

consth

```

```

Listing 3-The FIR pseudocode from Listing 1 can be implemented directly in Am29050 assembler code.

. eau

LENGTH 95

SYMMETRICPART. (LENGTH >> 1)

. equ

LOOP:

load

0. 0. Xn. A2D

; read ADC and convert

CONVERT

XO, Xn. SIGNED INT, NEAREST, SING FP, INT

AB_PLUS_0, SUM ZERO, ZERO; sum = 0:

FMAC

; calculate sum

FMAC

AB_PLUS_ACC, SUM XO, HO

; sum += x0 * h0

FMAC

AB_PLUS_ACC, SUM,

X94. HO

; sum += x94 * h0

; sum += xl * hl

FMAC

AB_PLUS_ACC, SUM X1, H1

FMAC

AB_PLUS_ACC, SUM, X93, H1

; sum += x93 * hl

N. 1

. set

COEFF. 64

.equ

. equ

DATA. &XO

(SYMMETRICPART - 2)

. rep

N. N + 1

.set

; sum += xn * hn

FMAC

AB_PLUS_ACC, SUM %%(DATA-N), %%(COEFF+N)

sum += x(LENGTH n 1) * hn

AB_PLUS_ACC, SUM, %%(DATA-LENGTH+N+1), %%(COEFF+N)

FMAC

.endr

FMAC

AB_PLUS_ACC, SUM, X47, H47; center tap

Yn. SING_FP, SUM; yn = (int) sum

MEACC

CONVERT

Yn. Yn. SIGNED_INT, NEAREST, INT, SING FP

0, 0, Yn. D2A

store

; store at DAC

add

grl, grl, 4

; adjust circular buffer

LOOP

j np

NOP

```

ordered to keep the pipeline full. In addition, the memory accesses for data and filter coefficients and circular buffer operations must be more efficiently manipulated for a better performance.

## IMPLEMENTATION OF A FIR FILTER-ATTEMPT II

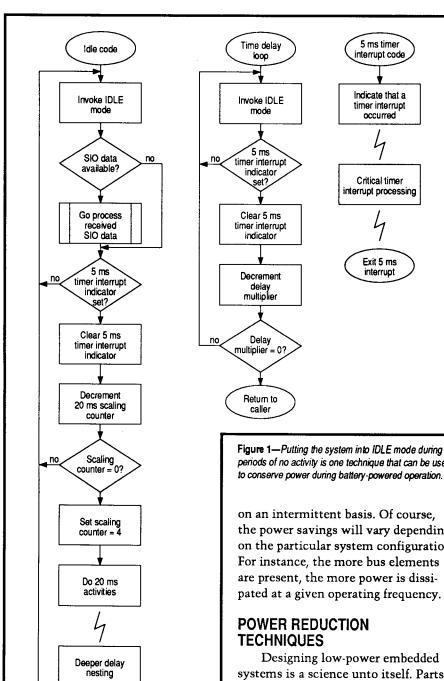

The major problem with the direct implementation of the FIR filter is the code did not take into account the internal construction of the pipelined FPU. The code must be adjusted to keep this pipeline full. This change is made by rewriting the algorithm into a form that allows consecutive FMAC instructions on the same floating-point accumulator every nth cycle, atwhich time the values will be available. (This adjustment requires four and three partial sums for the Am29050 and the i860, respectively.) The pseudocode for the new loop part of the high-speed FIR filter implementation is shown in

Listing 4. In this version, the calculation of the filter output,  $y[n \ AT]$ , is performed using four partial sums added together to get the final result. This approach (schematically shown in Table 2) allows the floating-point pipeline to be kept full.

The actual Am29050 code requires (N+20) instructions with only ten cycles remaining where you must wait for an operation to complete or to flush the pipeline. Thus, the 95-tap filter completes in 125 cycles (3.125  $\mu s$  at 40 MHz)-a 350% time improvement over the direct implementation. Because this system is dedicated, you can further customize the code through some minor reordering, and fill in the transparent **STALL cycles** with useful operations by overlapping two filter cycles.

In Listing 5, the code moved into the STALL cycles is indicated by stars  $(* \bullet)$  in the comment field. Moving instructions for maximum speed is not

|                       | Bu  | ses_           | Mul   | tiplier      |              | <u>Adder</u> |        |        | Regi | sters . |

|-----------------------|-----|----------------|-------|--------------|--------------|--------------|--------|--------|------|---------|

| <u>instr.</u><br>CONV | Δ   | <u>В</u><br>Хп | MT    | <u>PS</u>    | DN           | AD           | RN     | RU     | ACC0 | LR94    |

| FMAC                  | 0   | 0              |       |              | Xn           |              |        |        |      |         |

| FMAC                  | -S- | -s-            | 0 x 0 |              |              | Xn           |        |        |      |         |

| -S-                   | -S- | -S-            | -S-   | 0 x 0        |              |              | Xn     |        |      |         |

| -s-                   | HO  | X0             | -s-   | -S-          | 0 x 0        |              |        | Xn     |      |         |

| FMAC                  | HO  | x94            | HOXO  | -s-          | -S-          | 0 x 0        |        |        |      | X0      |

| FMAC                  | H1  | ΧI             | HOX94 | HOXO         | -s-          | -S-          | 0 x 0  |        |      |         |

| -s-                   | -s- | -S-            | -S-   | -s-          | <b>-</b> S-  | -s-          | -S-    | 0 x 0  |      |         |

| FMAC                  | H1  | x93            | H1X1  | H0X94        | HOXO+S       | -S-          | -S-    | -S-    | S    |         |

| -S-                   | -S- | -S-            | -S-   | - <b>S</b> - | - <b>S</b> - | HOXO+S       | -S-    | -S-    |      |         |

| -S-                   | -S- | -S-            | -S-   | - <b>S</b> - | - <b>S</b> - | - <b>S</b> - | HOXO+S | -S-    |      |         |

| -s-                   | -S- | -S-            | -S-   | -s-          | -s-          | - 8-         | - 8-   | HOXO+S |      |         |

| FMAC                  | H2  | x 2            | H1X93 | H1X1         | H1X1+S1      | -S-          | - S-   | - 8-   | S1   |         |

| -S-                   | -S- | -S-            | -S-   | -\$-         | <b>-</b> \$- | H1X1+S1      | -S-    | - 8-   |      |         |

Table I--The FPU's pipeline blocks (-s-) during consecutive FMAC operations using a single FPU accumulator.

straightforward because of the difficulty when six-deep pipeline FMAC instructions are mixed with three- or four-deep pipeline instructions (DADD, CONVERT), so the instructions may block each other. Memory is accessed when using the LOAD and STORE instructions to read and load the ADC and the DAC. If the external memory is slow, these instructions may need to be moved elsewhere in the loop so memory values are available at the right moment.

The importance of an intelligent DSP compiler becomes obvious. Combining the accumulator clearing with the first four multiplicative operations further reduces the number of cycles, but you must reorder the first eight multiplicative operations. This step ensures the CONVERT operation on the ADC input value does not stall the pipeline due to a result being unavailable for the *X0* x *HO* operation. In order to keep up the

accuracy of the summation, the new program brings out the FPU accumulators into twin global registers and uses DADD to add up the partial sums. This move does not cause any time penalties when doing a single-precision add because of the Am29050 FPU has **64**-bit buses to and from the main register bank.

The code in Listing 5 was finalized in conjunction with an Am29050 simulator and actually operates in N+13 instructions with only three STALL cycles remaining. For filters with a slow digitization rate, the processor would be put into a tight infinite loop at the start of the FIR calculation. An interrupt signal from the timing logic would then initiate another calculation cycle. In this situation, the remaining STALLs are unimportant.

The 95-tap Am29050 FIR digital filter implementation completes 192 floating-point operations in 111 cycles (2.78  $\mu s$  at 40 MHz, or nearly 68

megaFLOPS)-not bad for a nonspecialized chip.

Fixing the FPU pipeline on the MC88100 and the i860 greatly speeds them. However, they remain 2.5 times slower than the Am29050 because they have only a small 32-floating-point register bank attached to the FPU compared to the 192 registers of the Am29050. The MC88100 and i860 registers must be continually reloaded, taking additional cycles for every FPU operation.

However, the i860 RISC has a couple of aces up its DSP sleeve. The on-board instruction cache can be switched to a dual-instruction capability that allows the registers to be sent to the FPU while simultaneously permitting other registers to be reloaded from the data cache. This feature would improve things, but it still would not allow the superscalar i860 to be as fast as the scalar Am29050. The circular buffer over-

|                | Bus | ies_           | Multip | <u>ier</u>   |          | <u>Adder</u> |          |           |            |      | Registers |      |      |

|----------------|-----|----------------|--------|--------------|----------|--------------|----------|-----------|------------|------|-----------|------|------|

| Instr.<br>CONV | A   | <u>B</u><br>Xn | MI     | <u>PS</u>    | DN       | <u>AD</u>    | BN       | <u>RU</u> | ACC0       | ACC1 | ACC2      | ACC3 | LR94 |

| FMAC           | 0   | 0              |        |              | Xn       |              |          |           |            |      |           |      |      |

| FMAC           | 0   | 0              | 0 x 0  |              |          | Xn           |          |           |            |      |           |      |      |

| FMAC           | 0   | 0              | 0 x 0  | 0 x 0        |          |              | Xn       |           |            |      |           |      |      |

| FMAC           | 0   | 0              | 0 x 0  | 0 x 0        | 0x0      |              |          | Xn        |            |      |           |      |      |

| FMAC           | Ю   | X0             | 0 x 0  | 0 x 0        | 0x0      | 0x0          |          |           |            |      |           |      | X0   |

| FMAC           | Ю   | X94            | HOXO   | 0x0          | 0x0      | 0x0          | 0x0      |           |            |      |           |      |      |

| FMAC           | H1  | X1             | H0X94  | HOXO         | 0x0      | 0x0          | 0x0      | 0 x 0     |            |      |           |      |      |

| FMAC           | H1  | X93            |        | <b>HOX94</b> | HOXOtS   | 0x0          | 0x0      | 0 x 0     | S          |      |           |      |      |

| FMAC           | H2  | <b>X2</b>      | H1X93  | H1X1         | H0X94+T  |              | 0x0      | 0 x 0     |            | T    |           |      |      |

| FMAC           | H2  | X92            | H2X2   | H1X93        |          | H0X94+T      | HOXOtS   | 0 x 0     |            |      | U         |      |      |

| FMAC           | НЗ  | <b>X3</b>      | H2X92  | H2X2         | H1X93+V  |              | H0X94+T  | HOXOtS    |            |      |           | V    |      |

| FMAC           | В   | X91            | H3X3   | H2X92        | H2X2+S1  | H1X93+V      | H1 X1 tU | H0X94+T   | <b>S</b> 1 |      |           |      |      |

| FMAC           | 114 | <b>X4</b>      | H3X91  | НЗХЗ         | H2X92+T1 | H2X2+S1      | H1X93+V  | HIXItU    |            | T1   |           |      |      |

Table 2—The Am29050 FPU pipeline can be keptfull by splitting the FIR calculation into four partial sums.

```

Listing 4-The pseudocode for an FIR implementation using partial sums to overcome the FPU stalls.

/* Assume automatic circular buffer wrap-around handling */

float sum[4];

/* filter partial sums */

int count. whichsum

New loop to perform the convolution using partial sums */

for (count = 0; count \langle 4; count++)

sum[count] = 0.0:

(count = 0. which sum = 0: count < NUMCOEFFS 1; count++) {

sum[(whichsum++) % 4] += *xrecent-- * *coeffcurrent;

sum[(whichsum++) % 4] += *xancient++ * *coeffcurrent++:

sum[0] += *xancient++ * *coeffcurrent++:

/* center tap */

/* Convert and write out */

vm = (int) (sum[0] + sum[1] + sum[2] + sum[3]);

```

head still has to be handled, and too many registers need to be reloaded in the cycles available. Therefore, the i860 changes gear and switches into a 128-bit quadruple fetch mode from the data cache to allow the loading of four registers simultaneously. A couple of cycles of the dual-instruction i860 FIR code is shown in Listing 6 for an example. Because of the structure of the i860 FPU pipeline and assembler code, the filter sum is implicitly broken up into three sections rather than explicitly into four as in the Am29050 implementation.

Note that, unlike the scalar Am29050, the superscalar i860 has some fancy addressing modes more reminiscent of a CISC rather than a RISC chip. The data (X 1-X 8) and coefficients (H 1-HB) are fetched into the FPU registers using pointers (X p and **H** p , with the circular data buffer starting at memory location Xba se.

Note also that the  $\mathbf{d}$  .  $\mathbf{f}$  nop stalls the FPU once every eight cycles in order to steal the time to update the circular buffer using the integer APU. (The second circular buffer update is performed in parallel with an existing FPU operation and causes no overhead.) Although not obvious in this code, the i860 **FMC** instruction, ml 2 a pm. sd, takes three operands, exposing the architecture of the FPU in an unusual way. In any one cycle, these operands correspond to those two just about to enter the FPU pipeline and the value being stored

from the FMC instruction that started six cycles back.

The structure of the six-deep i860 FPU pipeline means that filling and flushing the pipeline at the start and end of each summation requires a total of six [nonproductive) cycles. This requirement is not important for the long 95-tap FIR filter, but would be significant for shorter DSP loops. Like the Am29050, the i860 will also stall when adding together partial sums. The conversion of the integer ADC value into floats, and vice-versa for the DAC value, also causes some additional overhead because of the difficulty of overlapping these operations with other FPU operations. (The i860 does not have an explicit CONVERT instruction.) These factors mean that an N-tap FIR digital filter will take  $\sim 1.13N + 24$  cycles.

The 95-tap i860 FIR digital filter implementation completes 192 floating-point operations in 132 cycles (3.3 µs at 40 MHz, or 58 mega-FLOPS)- also no slouch as a DSP processor.

As I mentioned earlier, I teach comparative computer architecture. Under the AMD University Support Program, I was able to obtain some Am29000 evaluation boards, which I later upgraded with the pin-compatible Am29050 chips. I have yet to approach Intel to see if they would also provide me with a classroom full of i860 boards to allow a similar extensive DSP experimentation. Therefore, I am

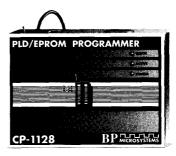

CP-1128 Combination Programmer \$1295.00

Supports AMD's MACH110/210/120/130/ 230 EPLDs, Altera's 900. 1800-series ond MAX EPLDs Cypress' CY7C36 1, Lattice's isp LSI1032 & pLSI1032, National Semiconductor's -5D & -7D devices and MAPL devices.

✓ Qualified and recommended by AMD, Lattice, National Semiconductor, Signetics and others. Utilizes only manufacturer approved programming algo✓ Supports upto 28-pinE/ EPROMs and bipolar PROMsincluding the microwire12C device ✓ Supports Dallas Semiconductor NVRAMs and TI DSP320, Microchip PIC microcontrollers ✓ Lifetime FRFF software

updates available via BBS

and US Mail ✓ Call for a DEMO disk and literature pack. ✓ Made in the USA

EP-1140 E/EPROM & µcontroller Programmer \$895.00

✓ The EP-I 140 supports NEC's 27C8001, B-Mbit EPROM, all 27C2404-Mbit 16 bit EPROMs, FLASH EPROMs, NVRAMs and all microwire EPROMs.

✓ All Intel, AMD, and Signetics 40-pin Ucontrollers su\_orted directly.

✓ Qualified and recommended by Intel. Signetics. Notional Semiconductor, and

✓ Lifetime FREE software up dates available via BBS and US Mail

✓ Risk-free thirty-day moneybock quarantee ✓ Made in the USA

With lifetime FREE software updates, you can't go wrong and BP Microsystems offers a thirtyday money-back guarantee to ensure product satisfaction. Remember, BP Microsystems is...

. . . . . . . . . . . . . . . . . .

The Engineer's Programmer<sup>TM</sup>

10681 Haddington • Houston, TX 77043-3239 (713) 461.9430 • FAX (713) 461-7413

© 1991 BP Microsystems, Inc

not as familiar with the i860 as with the Am29050 chips, so a more experienced programmer might tighten the i860 code by a few cycles.

### EVALUATION OF RISC CHIPS FOR DSP PURPOSES

As I have shown, some RISC chips have many of the features useful for DSP applications. Most importantly. they are fast (30-50 MHz). An on-board register stack or a quadruple-ported data cache can store data and coefficients without having to access slow external memory. Some RISC chips have a separate instruction bus to keep data and instruction fetches from competing for resources. Another advantage the RISC chips have over dedicated DSP chips is an internal architecture more exposed to the programmer/compiler, giving full control of the FPU pipeline to maximize the filter throughput.

The Motorola DSP56200 is an interesting DSP chip to compare to the RISC FIR performance. The DSP56200 was designed for FIR operations and has some fancy features. It has a 16-bit input with a 40-bit integer data path for the accumulator operation compared to the 64-bit floating-point path on the Am29050. What is neat about the DSP56200, in a comparative architectural sense, is it was specifically designed (c. 1985) with simple interchip serial connections to allow multiple DSP56200s to operate in parallel if a single chip does not perform quickly enough. I adapted the timings shown in Table 3 from data sheet results for DSP and RISC chips.

For nonspecialized DSP chips, RISCs do not perform too badly. The Am29050 and i860 RISC outperform the other RISCs because of their register- and memory-handling capabilities. For other DSP operations that make less use of a large number of registers, the timings are closer (e.g., for the shorter-length Infinite Impulse Response [IIR] digital filter). The availability of an FMC instruction is also very significant in this DSP application.

The Am29050 and i860 RISCs seem to be handling themselves as reasonable (if not perfect) general-

Listing 5—Two overlapped filter cycles are used for maximum efficiency in he final partial sum version of the FIR filter code. Instructions for he second filter cycle are moved into the stall positions (\*\*) of he initial filter cycle.

```

changes to general register definitions

; external copies of FP ACCUMILATORS

. set

TEMPO, gr122

. set

TEMP1, gr120

; using twin registers for double

TEMP2, gr118

. set

; precision storage

.set

TEMP3. gr116

.set

Yn. TEMPO

changes

to FP accumulator names

.equ

SUMD. 0

. equ

SUM1, 1

.equ

SUM2. 2

SUMB. 3

. equ

0. 0. Xn, A2D , x0 = (float) ReadA2D()

load

CONVERT XO, Xn. SIGNED_INT, NEAREST. SING_FP, INT

FMAC

AB_PLUS_0, SUMD. X1, H1

** sum[0] = x1 * h1

AB_PLUS_0, SUM1, X93. H1

**sum[1] = x93 * hl

FMAC

FMAC

;** sum[2] = x3 * h3

AB_PLUS_0, SUMP. X3. H3

** sum[3] = x91 * h3

FMAC

AB_PLUS_0, SUMB. X91. H3

FMAC

AB_PLUS_ACC, SUMD. X2. H2

;** sum[0] += x2 * h2

FMAC

AB_PLUS_ACC, SUM1, X92, H2

;** sum[1] += x92 * h2

LOOP:

FMAC

AB PLUS ACC. SUMP. X94, HO

;** sum[2] += x94 * h0

FMAC

AB_PLUS_ACC, SUMB, XO, HO

:** sum[3] += x0 * h0

.eau

LENGTH, 95

.equ

SYMMETRICPART. (LENGTH >> 2)

.set

DATA. &XO

COEFF. 64

.set

.set

(SYMMETRICPART - 2)

. rep

. set

N, N + 2

FMAC

AB PLUS ACC, SUMD. %%(DATA-N), %%(COEFF+N)

AB_PLUS_ACC, SUM1, %%(DATA-LENGTH+N+1), %%(COEFF+N)

FMAC

FMAC

AB_PLUS_ACC, SUM2, %%(DATA-N-1), %%(COEFF N+1)

FMAC

AB_PLUS_ACC, SUMB. %%(DATA-LENGTH+N+2), %%(COEFF+N+1)

. endr

FMAC

AB_PLUS_ACC, SUMD, X48. H46; finish off summation

FMAC

AB_PLUS_ACC, SUM1, X46. H46

FMAC

AB_PLUS_ACC, SUMP. X47, H47; center tap

grl. grl. 4 ;** Adjust circular buffer

add

0,0, Yn. D2A ;** WriteD2A(yn) for previous cycle

store

MFACC

TEMP2. DOUBLE FP. SUMB

; temp2 = sum8

MFACC

TEMP3. DOUBLE_FP.

MFACC

TEMPO. DOUBLE_FP. SUM1

MFACC

TEMP1. DOUBLE FP. SUMP

FMAC

AB_PLUS_0, SUMP. X3. HB

DADD

TEMP2. TEMP2. TEMP3

: temp2 += temp3

AB_PLUS_0, SUMB. X90, HB

FMAC

DADD

TEMPO, TEMPO, TEMP1

: temp0 += templ

FMAC

AB_PLUS_0, SUMD. X2. H2

FMAC

AB_PLUS_0, SUM1, X91. H2

DADD

TEMPO. TEMPO, TEMP2

; temp0 = temp0 + temp2

AB_PLUS_ACC, SUMD. XI. H1 ; ** sum[0] += xl AB_PLUS_ACC, SUM1, X92, H1; ** sum[1] += x92

FMAC

: ** sum[0] += xl * hl

FMAC

load

0, 0. Xn. A2D

CONVERT XO, Xn, SIGNED_INT, NEAREST, SING_FP, INT

j mp

ym = (int) temp0

CONVERT Yn, TEMPO, SIGNED_INT, NEAREST, INT, DOUBLE_FP

```

| DSP chips            |               |                |

|----------------------|---------------|----------------|

| single DSP56200      | 10 MHz        | 10.4 <b>μs</b> |

| dual DSP56200        | 10 MHz        | 3.25 <b>μs</b> |

| quadruple DSP 56200  | <b>10</b> MHz | 2.71 <b>µs</b> |

| single DSP56001      | 33 MHz        | 5.64 <b>μs</b> |

| single DSP96002 (fp) | 40 MHz        | 4.96 <b>μs</b> |

| single TMS32025      | 50 MHz        | 7.84 <b>µs</b> |

| single TMS32030 (fp) | 33 MHz        | 4.75 <b>μs</b> |

| RISC chips           |               |                |

| single Am29050 (fp)  | 40 MHz        | 2.78 <b>µs</b> |

| single i860 (fp)     | 40 MHz        | 3.3 <b>µs</b>  |

| single MC881 00 (fp) | 33 MHz        | 9.75 <b>μs</b> |

| single SPARC (fp)    | 33 MHz        | >9.75 µs       |

|                      |               | •              |

Table 3—In the case oia 95-tap F/R filter, some processors do better than others due to differences in architectures. The Am29050, in fact, beats almost all of the DSP chips in an application traditionally reserved strict/y for such chips.

purpose DSP-capable chips. What is missing?

•The Am29050 could do with a floating-point accumulator-toaccumulator add operation similar to that found on the Am29027 coprocessor used in conjunction with the Am29000 integer RISC chip. Examining the code for the final FIR filter indicates the FPU accumulators are transferred to local registers simply to bring them back into the FPU so an accumulator-to-accumulator add can occur. This time does not incur a substantial overhead for a long (95-tap) FIR filter because you can fill the **STALL** cycles associated with pipeline filling and flushing with useful instructions. However, it could be critical for the shorter loops often present in other DSP applications.

\*A problem with the i860 is also associated with the way its FPU pipeline is filled and flushed. Compared to the Am29050, the i860 has an additional 6-cycle overhead, critical for shorter DSP loops. It also suffers from STA L L problems when adding together partial sums even with the capability of the direct floating-point accumulator-to-accumulator add lacking in the Am29050.

\*For applications requiring a very large number of continual memory accesses [e.g., a 150-tap FIR filter), what would be useful is if the Am29050 had the superscalar i860 capability of being able to reload one bank of floating-point registers while using another bank. The scalar

Am29050 already has a load multiple instruction, LOADM and appears to have sufficient internal buses to allow this operation to occur in conjunction with FPU operations. However, because of the complex data dependencies that might occur, this parallelism is currently blocked by the Am29050 internal logic. However, I would not want to go to the other extreme with no checks on conflicts, which makes programming difficult. With the large number of available registers on the Am29050,

handling the logic associated with reloading one "bank" (say a group of 8 or 16) while using another should be possible.

### CONCLUSION

In this application, I started off with an academic exercise to evaluate the RISC chips in a simple DSP application-a FIR digital filter. I ended up with some interesting conclusions about the similarity between the RISC and specialized DSP chips. In particular, the Advanced Micro Devices Am29050 and the Intel i860 RISC chips were shown to have many DSP capabilities.

\*These chips are fast (40 MHz); have a fast, high-precision, on-board FPU; and are capable of performing many simultaneous floating-point and integer operations simultaneously.

\*The RISC instruction set exposes the chip's internal operation to the programmer/compiler, permitting maximum pipeline efficiency at all points in a DSP algorithm.

\*Although the data coming into the FPU is 32 bits wide, the internal representation of the FPU accumulators allows 64-bit double-precision floating-point storage of intermediate results with no time penalty. This feature means that sufficient guard bits are available to ensure against underflow and overflow of DSP algorithms involving extensive summation or recursive operations.

\*Typical DSP applications involve extensive looping [branching). For a

See us at the Embedded Systems Conference—Booth#305

Listing 6—The i860 FPU pipeline has a dual-instruction mode that can be used in FIR calculations. The filter sum is implicitly broken up into three sections rather than explicitly into four as in the Am29050.

| d.m12apm.sd<br>d.m12apm.sd | <b>X5. H5.</b> T1 fld. <b>X6. H6.</b> T1 add. | •                      | ; sum1 += X5 * H5, fetch 4 coefficents<br>; sum2 += X6 * H6. update data pointer                             |

|----------------------------|-----------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------|

| d. fnop                    | and                                           | #\$1FF, Xp. Xp         | ; FPU stall while adjust circular buffer                                                                     |

| d.m12apm.sd                | <b>X7. H7,</b> T1 add.                        | s 32. <b>Hp. Hp</b>    | ; sumB += X7 * H7. update coeff pointer                                                                      |

| d.m12apm.sd                | <b>X8. HB.</b> T1 fld.                        | q 16(Bp), <b>135</b>   | ; suml += X8 * H8, fetch 4 coefficients                                                                      |

| d.m12apm.sd                | Xl. H1,T1 fld.                                | q Xp(Xbase), <b>X5</b> | ; sum2 += $Xl * H1$ , fetch 4 data values                                                                    |

| d.m12apm.sd                | <b>X2. H2.</b> T1 add.                        | s 16. <b>Xp. Xp</b>    | ; sum1 += X5 * H6, now complete<br>; sum8 += X2 * H2. update data pointer<br>; sum2 += X6 * H6, now complete |

| d.m12apm.sd                | <b>X3. H3.</b> 11 and                         | #\$1FF, <b>xp. xp</b>  | ; suml += X3 * HB. adjust buffer<br>; sumB += X7 * H7, now complete                                          |

| d.ml2apm.sd                | <b>X4. H4.</b> T1 fld.                        |                        | ; sum2 += X4 * H4. fetch 4 data values                                                                       |

heavily pipelined system, this aspect could involve frequent inefficient pipeline stalls (flushes] while the new instructions are being fetched. The use of the *delayed jump* instruction overcomes much of this problem. The availability of an on-board Branch Target Cache (Am29050) or an instruction cache (i860) overcomes problems

with slow external instruction memory.

- •A register window connected to the FPU or the ability to reload a small floating-point register bank in parallel with floating-point operations is essential for high-speed DSP operation.

- •A useful DSP feature apparently missing from the Am29050 is a floating-point accumulator-to-accumulator add implemented directly in the FPU. However, the presence of this instruction on the i860 did not provide additional speed because of the structure of its FPU pipeline. This feature can currently be implemented on the Am-29050 using two existing

instructions that expose the accumulator-to-accumulator add pipeline to the programmer. Such an approach may actually better control keeping the FPU pipeline full. Whether the lack of this instruction is a bug or a feature in DSP applications is a question answered only by further evaluation.

\*Data access can compete for resources with the instruction fetches

in DSP loops. The **i860** and the Am29050 avoid this problem by having separate instruction and data buses and an instruction cache, features not available on all RISC chips. However, it would be useful if the current Am29050 instruction prefetch buffer was actually a cache for DSP applications. As shown on the

Photo 2-The TMS320 is a popular **dedicated** DSP chip that, in some applications, may be passed over for capable RISC chips.

i860, the ability to access twin instructions and quadruple data fetches in a single cycle from a reconfigured cache considerably improves speed.

- •Clumsy FPU pipeline filling and flushing can produce heavy overhead on short DSP loops.

- •A DSP-intelligent compiler is needed to make sure the optimization

of the tight DSP loops is done efficiently on RISC machines.

\*By examining a real-time FIR digital filter application, I have hinted at possible RISC DSP applications in the telecommunications area. Economy of scale would bring the RISC prices down. Low-power standby modes and other useful DSP features

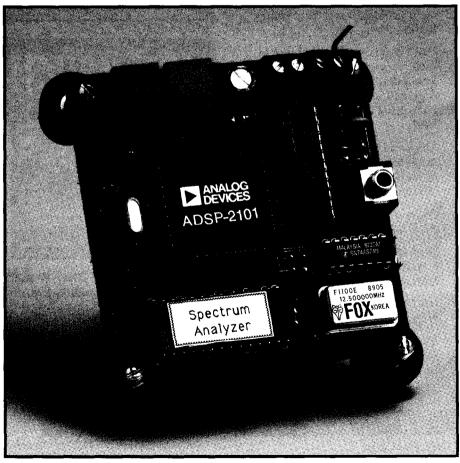

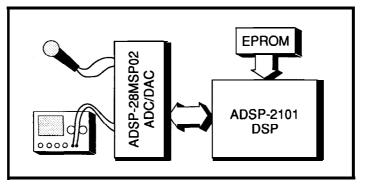

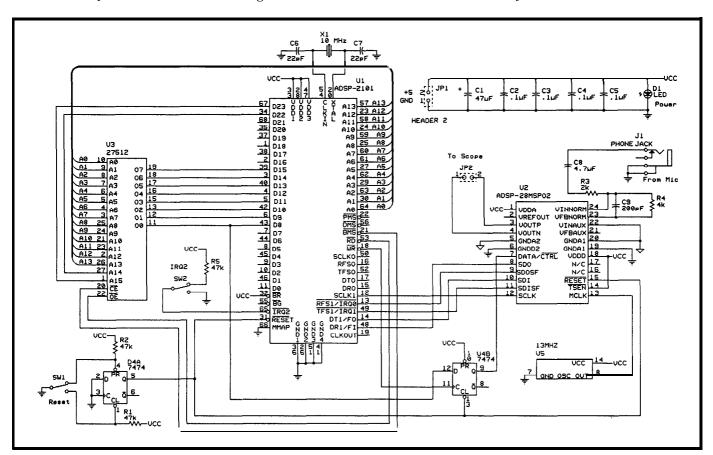

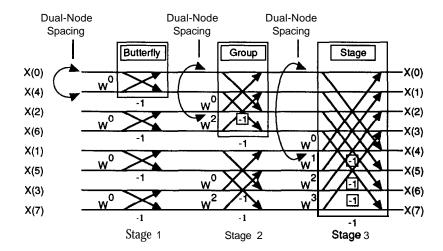

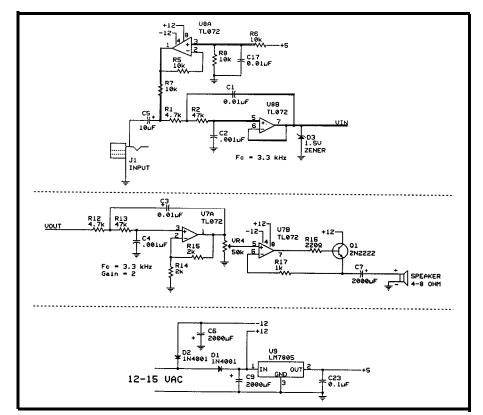

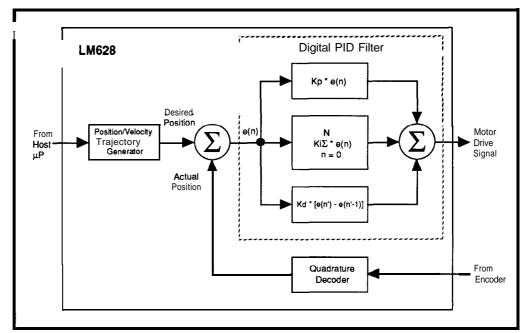

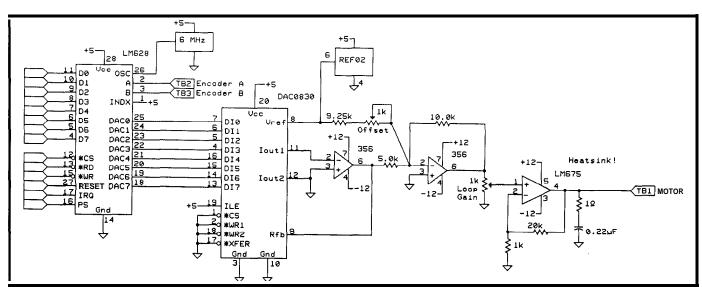

could easily be added to RISC chips if market forces come to bear.