# CIRCUIT CILLARINK®

THE COMPUTER APPLICATIONS JOURNAL

# EDITOR'S |

# The Whole Story

oftware is one of the major issues we wrestle with here at Circuit Cellar INK. On the one hand, our readers look to us for practical hardware solutions and innovative control techniques. There are several other high-quality magazines where readers can turn if their interests center on code rather than solder. Given that we have to be

discriminating in our selection of articles, why not focus solely on hardware?

On the other hand, our subtitle reads *The Computer Applications Journal*, not *The Computer and Controller Hardware Journal*. We have promised practical, complete solutions, not black-box instructions. Since our readers are interested in functional applications, shouldn't we provide them with all the pieces required to build those applications?

When you look at our table of contents for this issue, you'll see articles on software. Yes, hardware is what makes us unique, but it's not enough. Programmable microcontrollers and complex designs have become so common that

even the most diehard hardware engineers must recognize the importance of software.

It's become fashionable to talk about how huge the programs running on embedded controllers and other applications have become. This is used as a way of saying that software is the sole force driving the development of computer applications. I'm not sure that I believe all the numbers being thrown about, but I do see signs of a growing partnership between "engineers" and "programmers." Until recently, it was fashionable for hardware designers to disparage the work of programmers, and vice versa. Now, cooperation is common. What's more, hardware and software engineers are learning one another's disciplines, and finding that it makes their own work more creative and

Circuit Cellar INK is dedicated to helping you become a better computer applications designer, engineer, or programmer. If we can teach you more about the discipline you know least, we're well on our way.

Speaking of Trends...

When you get as many pressreleasesas we do hereat Circuit Cellar INK, you can, if you squint just right, see trends start to develop. One of the trends that seems to be picking up steam is the use of microprocessors rather than microcontrollers in embedded and control applications. Members of the 8088 and 68000 families are showing up in places that, until recently, were reserved for 8052s and 6809s. What's up?

For starters, it's easy to see that hardware engineers aren't the ones driving this trend. After all, who wants to have to work extra glue, memory, and I/O circuitry into a design if you don't have to? It's not as though controllers aren't powerful enough. Controllers like the Intel 80960 are, arguably, more potent than anything the company offers on the microprocessor side. That argument aside, most control and embedded applications just don't need the wide data

path, huge address space, and 25+ MHz clock speed of the latest microprocessors.

No, the driving reason for this trend can be found back about four paragraphs. Programmers and engineers who have to write the software for applications are getting more vocal about the need for better programming tools. In general, if you have an IBM PC on your desk, you have the basis for a high-powered 8088 software development system. If you have a 68000-based desktop machine, you're only so far from developing software for a 68000 control project. The fact is, software development time is now more valuable than mere hardware. This explains the appearance of PC-clones on just about every bus; a 4" x 6" card with 80386, 1 meg of memory, and VGA built-in; and 68000 UNIX single-board computers. I don't expect to see microcontrollers and their development tools disappear any time soon. Indications are that 8-bit microcontrollers will be the major portion of the market for years to come. But where microcontrollers were the only solutions available, now you can pick from a wide variety of platforms based on the many criteria (including financial and time) of a given project.

### Time Marches On

Those with eagle eyes might have noticed than we jumped from the January/February date of Issue #7 to the April/Maydateof this issue. Is this a sign of corporate memory loss, or a personal vendetta against March? It's neither. It is, instead, the easiest way we could find of making the monthson the cover and the real schedule match. You should notice no change in the way you've been getting Circuit Cellar INK.

> Curtis Franklin, Jr. Editor-in-Chief

FOUNDER/ EDITORIAL DIRECTOR Steve Ciarcia

PUBLISHER

Daniel Rodrigues

EDITOR-in-CHIEF Curtis Franklin, Jr.

ASSOCIATE PUBLISHER John Hayes

ENGINEERING STAFF Ken Davidson Jeff Bachiochi Edward Nisle y

CONTRIBUTING EDITOR Thomas Cantrell

CONSULTING EDITORS Mark Dahmke Larry Loeb

CIRCULATION COORDINATOR Rose Mansella

CIRCULATION CONSULTANT Gregory Spitzfaden

PRODUCTION MANAGER Tricia Dziedzinski

BUSINESS MANAGER Jeannetfe Walters

### STAFF RESEARCHERS

Northeast

Eric Albert

William Curie w

Richard Sawyer

Robert Stek

Midwest

Jon Elson

Tim McDonough

West Coast Frank Kuechmann Mark Voorhees

Cover Illustration by Robert Tinney

# CIRCUIT CT N K R

### **FEATURES**

22

**Switching Power Supplies**

Efficient *Power for* Embedded *Control* Systems by Steve Ciarcia

When you downsize the controller, the power supply has to shrink, too. Steve looks at the "black art' of designing efficient, clean power supplies in compact form factors.

### Product Reviews—

The Next Generation

Circuit Cellar INK sells out and enjoys if!

Supercharged Worry Munchers

Circuit Cellar INK looks at four diverse applications solutions

Writing A Real-Time Operating System-Part 2

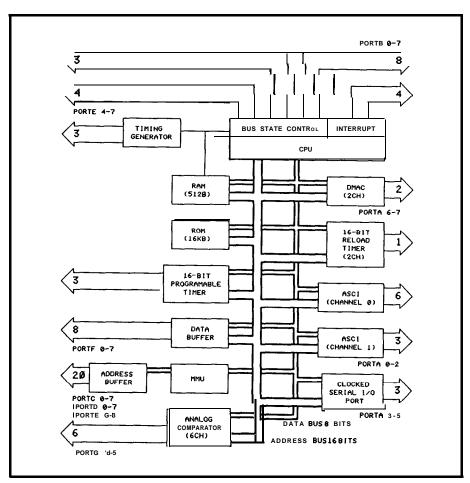

Memory Management and Applications for the HD64180

by Jack Ganssle

Jack Ganssle discusses working with the HD64180's internal MMU and tips on writing applications in the conclusion of this two-part article.

### **DEPARTMENTS**

The Whole Story by Curtis Franklin, Jr.

Reader's INK—Letters to the Editor

5

Visible INK—Letters to the INK Research Staff

Creating a Network-based Embedded Controller 46

by Jeff Bachiochi

### THE COMPUTER APPLICATIONS JOURNAL

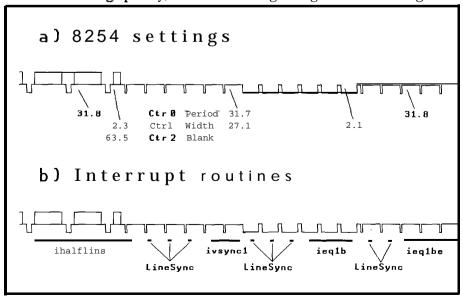

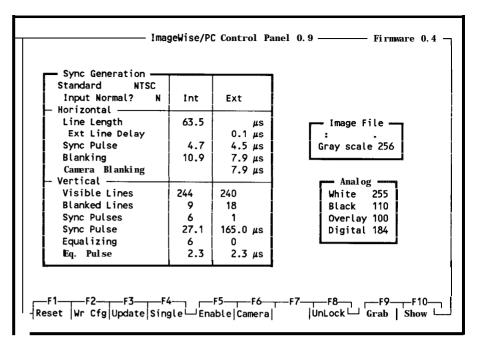

### [34] ImageWise/PC-The Digitizing Continues-Part 3

Topping it off with Software by Ed Nisley

Although solder is the favorite programming tool of many engineers, software is the glue that holds ImageWise/PC together, as this three-part series concludes, Ed Nisley describes the software that makes this PC-BUS digitizer possilbe.

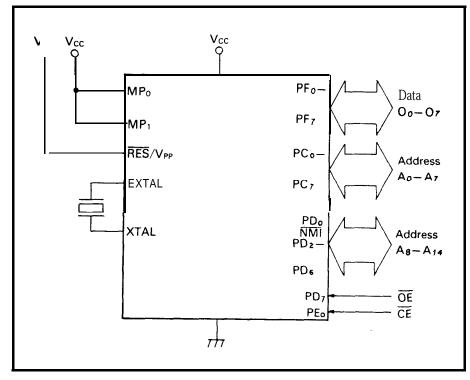

### 52 HD647180X-A New 8-Bit Microcontroller

Embedded Controllers Get Respect by Tom Cantrell

While the state-of-the-art marches toward 32 bits, 8-bit microcontrollers keep gelling more powerful. The HD647180X is the latest integrated controller built on the foundation of the proven Z80.

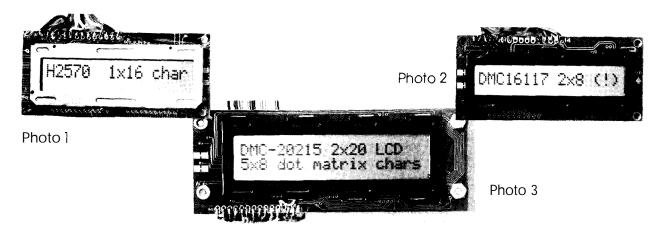

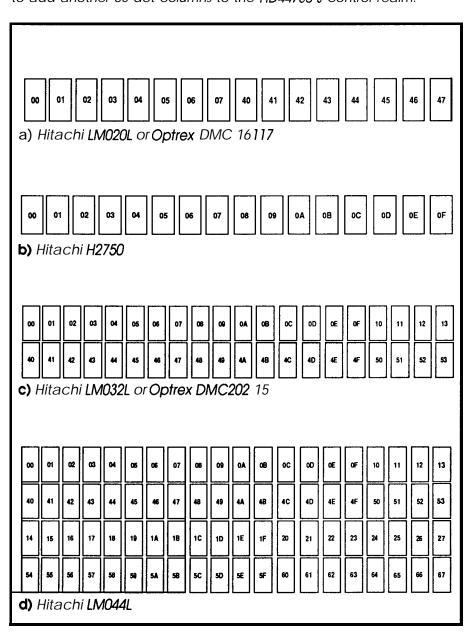

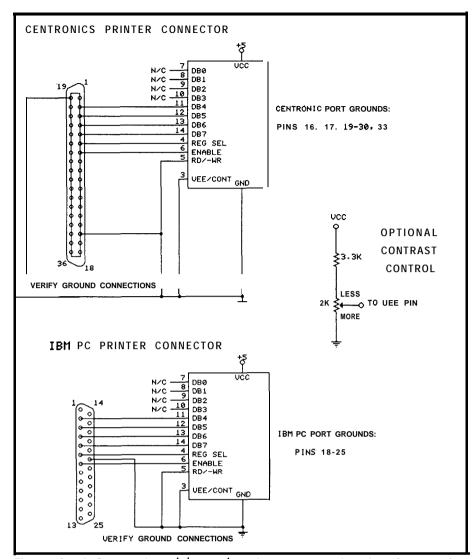

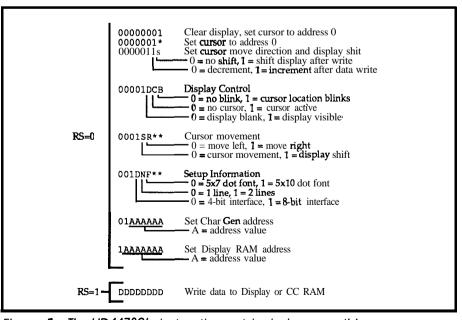

Firmware Furnace The True Secrets of Working with LCDs — by Ed Nisley Advertiser's Index — Connectime - Excerpts from the Circuit Cellar BBS -----Conducted by Ken Davidson Steve's Own INK Smile When You Call Me That by Steve Ciarcia

Circuit Cellar BBS-24 Hrs. 300/1200/2400 bps, 8bits, no parity. 1 stop bit, (203) 871-1988.

The schematics provided in Circuit Cellar INK are drawn using Schema from Omotion Inc. All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure that their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscrib-

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of the possible variation in the quality and condition of materials and workmanship of readerassembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK.

CIRCUIT CELLAR INK (ISSN 0896-8985) is published bimonthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203) 875-2751. Second-class postage paid at Vernon, CT and additional offices. Oneyear (6 issues) subscription rate U.S.A. and posse&ions \$14.95, Canada \$17.95, all other dountries \$26.95.. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders to Circuit Cellar INK, Subscriptions, P.O. Box 2099, Mahopac, NY 10541 or call (203) 875-2 199.

POSTMASTER: Please send address changes to Circuit Cellar INK. Circulation Dept., P.O. Box 2099, Mahopac, NY 10541.

Entire contents copyright 1988 by Circuit Cellar Incorporated. All rights reserved. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# READER'S INK

### Letters to the Editor

I had a few comments on the article on multitasking ("Writing a Real-Time Operating System") and the discussion on control networks ("ConnecTime") which appeared in issue #7 of Circuit Cellar INK. As part of my own multitasking system (wearing many hats in a small company), I do hardware and software design, write our manuals, and do a monthly article for Radio World Newspaper (a technical newspaper for radio broadcast stations).

### Multitasking

The multitasking system discussed in the article looks quite complete, and complicated. We've been using a simpler system on 6802-based systems. Hardware interrupts are used just for I/O buffering (rather than task switching). The interrupt-driven I/O buffering (using circular buffers) allows us to send or receive blocks of I/O from different devices or users. The system uses roundrobin task switching with no priorities. Every task waits its turn. A task switch is initiated whenever the current task runs out of work. This is generally I/Orelated. Either the task is waiting for input and the input buffer is empty, or it has output and the output buffer is full. On exit, each task resets its "program counter" to the point where the decision was made that caused the exit. If there is a particularly processor-intensive task that we do not want to hog the system, it can be broken into parts. On exit, the task program counter is set to where the task is to continue. In 6800 assembly, the task manager looks like this:

```

TASKLOOP: JSR TASK0 ;Go do task 0

JSR TASK1 ;Go do task 1

JSR TASK2 ;Go do task 2

JSR TASK3 ;Go do task 3

BRA TASKLOOP ;Go do it all again

```

We set up an area of RAM to hold the "program counters":

```

TASKOPC: DS 2 , -Set aside 2 bytes of TASK1PC: DS 2 ;RAM for task 0 PC TASK2PC: DS 2 TASK3PC: DS 2

```

Task entry looks like this:

```

TASKO: LDX TASKOPC; Get our program counter JMP 0,X ; and go to it

```

Task exit looks like this:

```

TASKOF:

LDAB #0

,-Specify buffer 0

JSR BUFFULL: Go see if it's full

BEQ TASKOG ; Cont routine if not full

LDX #TASKOF; Point where come back

STX TASKOPC; Store as PC for this task

RTS

; and exit

;Buffer not full, so output

TASKOG:

LDAB #0

;Specify buffer 0

LDAA #7

;Get a bell

JSR PUTBUF; and put it in buffer 0

```

On entry to task 0, we pick up the program counter for this task, then start executing at that point (in the example, TASKOF). We redo the test that caused the task exit (checking to see if buffer 0 is full). If it's still full, we set up our task program counter for next time. If it's not full, we continue with the task (here outputting a bell character).

The key to this approach is that whenever a task needs to wait, it goes on to another task. When each other task is carried as far as it can go (without waiting), we come back around to see if this task is ready for action.

This approach uses only the standard hardware stack. There are not separate stacks for each task. Note, however, that this complicates the use of local variables. Since many high-level languages keep the local variables on the stack (throwing them out on procedure exit), the stack would quickly get confused. The simplest approach to this problem is to just use global variables that are always allocated. Each task needs its own set of variables. If each task is running the same program (thus having the same variable requirements), each variable could become an array that specifies which task the variable is used by. To save memory, an array called stack (Task) could be set up. Temporary variables could be stored on this "high-levellanguage" stack that is dedicated to this task. Since they are no longer needed, the stack pointer would be moved to delete them. This "high-level-language" stack allows reuse of memory for temporary variables.

Of course, one purpose of the hardware stack is keeping track of subroutine return addresses. If a task gets

three subroutine calls deep and then exits, all those return addresses are still on the stack. The stack will very quickly become confused again. For simplicity, all task exits would have to be from the "main-line" code. This can be accomplished by either checking for an exit-causing condition prior to calling the procedures (see if the buffer is full prior to calling Buf Put) or having a flag (ProcFail) that is set if the procedure failed and needs to be run again (and cleared if the procedure did not fail). When we get back to the main-line code, we continue if ProcFail is false. If ProcFail is true, we set up our task program counter to repeat the procedure next time, then exit this task.

### Networking

In ConnecTime, there was quite a discussion of network protocols. I had a few comments (again, based on systems we manufacture).

Mark Lampkin gave a suggested data packet format. His simple format did not contain a return address or error checking (he's gotten no errors). His packet consisted of:

### STX, Address, Command, Packet Length, data bytes, ETX

I'd suggest the following format:

### Hex AA, Hex 55, ToAddress, FromAddress, PacketLength, data bytes, CheckSum

The AA55 hex is a beginning-of-message flag. We need to have a flag that will never occur in our data. Synchronous protocols do this by sending more than the maximum number of allowed 1 bits in a row in a character. To prevent a data byte from having too many 1s in a row, they use "bit stuffing" to stuff a 0 in the character after the maximum number of 1s. On the receiving end, after the maximum allowed number of 1s is received, the following "stuffed" 0 is removed, restoring the data to original.

In asynchronous communications, we cannot stuff more bits in a character (although some protocols send a break as a begin-of-message flag, which is detected at the receiver as a framing error). What we've done is "byte stuffing," quite similar to bit stuffing. If the data contains an AA hex, we stuff a 00 after it on transmission and remove it on reception. This guarantees that the flag (AA55 hex) will never occur in the data string. By the way, AA55 hex is used since it is an alternating pattern of **0s** and 1s, then the reverse pattern. Both Mark Lampkin's protocol and mine include the ToAddress. I've included a From Address to allow the other device to respond (whether with an acknowledgement or with requested data). Mark included a "command byte." I believe this does not belong in the header, but should instead be in the data bytes area of the message. This allows for multibyte commands and makes even "noncommand" data packets the same. If needed, the first byte of the data bytes section could be a "packet type" byte, which determines how the remainder of the packet is to be interpreted. As Mark, I then left room for the data. I followed this with a checksum byte, which is the sum of all bytes in the message (excluding the AA55 hex flag, but including the addresses, byte count, and data). Another approach is to use the 2's complement of the sum as the checksum. The receiver then adds up all the bytes in the message, including the checksum. If the result is 0, the message is good.

Mark had an ETX byte to mark the end of the message. Since the message already includes a packet length byte, we already know where the end of the message is, making ETX unnecessary.

### Contention Avoidance

Mark's system used a fiber-optic ring, where it is not possible to get contention (multiple devices transmitting on the same medium simultaneously). Each fiber link has only one transmitter and one receiver, so a "token passing" protocol does not appear necessary. Any device wanting to send a message may transmit it at any time. The next device in the ring receives that message. If its address matches the **ToAddress** of the message, it acts on the message. If the address does not match, it passes the complete message on to the next device in the ring. Eventually, the message should find a home.

Note that this ring could be expanded to a **multibranched** tree or matrix where each device has several links to several other devices. Received messages that are not for this device are passed on to other devices through any one of several output ports. The decision as to which port to use **canbe** based on a table held in that device. The routing information could also be included in the message header. The device originating the message would include several bytes of **ToAddress**. For the destination site to answer, it is necessary to include several bytes for the **FromAddress**.

If there really were a possibility of contention (a bus topology where more than one device can transmit on the same medium simultaneously), a contention-avoidance system is desirable (though not required). If each device transmits at random times and the system loading is low, there is a good possibility the message would get through.

The next approach to contention avoidance would be to "look before you leap." Listen for someone else transmitting before you bring up your carrier. This eliminates some contention, but there is a possibility of several sites holding off until a carrier drops, then having them all come up at once. To avoid this problem, a delay can be introduced after detecting carrier drop and before bringing up carrier. If this delay is fixed (and different1 for each site, a priority system is established. The site with the shortest delay gets in first. If a random delay is used, all sites have equal access.

### Token Passing

In token passing, a "permission-to-transmit" token is passed from device to device in the system. When a device receives the token, it transmits any messages it is holding,

then transmits the token to the next device in the system. There is danger, however, of the token getting lost, due to a transmission error. When this occurs, the system must detect it and generate a new token.

### Absence-of-Data Token Passing

In one of our systems, we've used "absence-of-data token passing." Each device in the system includes a timer that is set to a "sitedelay" on reception of a valid data byte. If the timer reaches 0 before a valid byte is received, a "site counter" is incremented and the site delay timer is set back to the initial site delay. This continues until the highest site number in the system is reached. After that, the site counter is reset. When the site counter is incremented, each device in the system checks to see if the site counter now matches its site number ("it's now my turn to talk"). If so, carrier is brought up and FE hex characters are sent for site delay and act as a 'leader."

Once the "leader" is complete, we transmit all the data packets that are held in the transmit buffer (with no more leader). When the transmit buffer is empty, we leave the carrier idle for a couple character times to allow the last byte to get through, then drop the carrier. A SiteDelay after the last valid byte, all sites increment their SiteCounters, enabling the next site in the system. If any site does not haveanydata to send, it leaves its carrier off, automatically passing the "permission-to-transmit" token to the

next site in the system. In addition, each time a site receives a valid message, it sets its site counter to match the FromAddress of the received packet. This **resynchronizes** all sites in the system. This "absence-of-data" token-passing system is really just like a standard token-passing system except for the form of the token. Further, no site must regenerate a lost token, since the token is the lack of data rather than the presence of a certain data sequence. It's hard to lose something that was never there!

#### Conclusions

There are lots of different ways of handling networks. Right now, I like the absence-of-data token passing for bus systems and the routed matrix for nonbus systems. The routed matrix has some additional delay due to message retransmission, but this retransmission removes noise and timing inaccuracies from messages, resulting in better system performance. The routed matrix also has a higher throughput since the medium connecting two devices or sites is only carrying traffic that needs to go between those sites. In a bus system, all media in the system carries all the traffic. The routed matrix can be carrying several messages simultaneously over various portions of the medium. The bus can only carry one message at a time.

> **VOICE MASTER KEY** \* VOICE RECOGNITION SYSTEM FOR PC/COMPATIBLES & TANDY 1000 SERIES A FULL FEATURED VOICE I/O SYSTEM

(GIVE A NEW DIMENSION TO PERSONAL COMPUTING The amazing Voice Master Key System)

SPEECH RECORDING SOFTWARE Digitally record your own speech. sound. or music to put into your own software programs. Software provides sampling rate variations, graphics-based editing, and

EVERYTHING INCLUDED. . Voice Mas-ter Key Systemconsists of a plug-m card, durable lightweight microphone headset. software, and manual Card fits any available slotExternal

ports consist of mic inputs and volume controlled output sockets Highquality throughout. easy and

ORDER HOTLINE: (503)342-1271Monday-Friday, 8AM to 5 PM Pacific Time

Visa/MasterCard, company checks. money orders, CODs (with prior approval) accepted Personal

tion tool-box utilities are included A genuine productivity enhancer!

adds recognition to just about any program or application. Voice command up to 2% keyboard macros from within CAD. desktop publishing, word processing, spread sheet, or game programs. Fully TSR and occupies less than 64K. Instant response time and highrecognition accuracy Voice recogni-

Harold Hallikainen San Luis Obispo, CA

lata compression utilities. Create soft-

ware sound files you can add to macros

for voice recognition verification re-

sponse. a complete, superior speech and

growing list of third party talking software titles using synthesized phonetics (text - to - speech) or digitized PCM,

ADPCM, and CVSDM encoded sound

files. Voice Master Key system does it

ONLY \$149.95

**COMPLETE**

and development tool. SOFTWARE CONVERSION CODES. The Voice Master Key System operates a

un to use

ONLY \$89.95 FOR TANDY 1000 \$L/TL MOOELS

SOFTWARE ONLY—REQUIRES TANDY BRAND ELECTRET MICROPHONE.

# **Switching Power Supplies**

Efficient Power for Embedded Control Systems

by Steve Ciarcia

ith all the emphasis on embedded controllers and process control in the pages of Circuit Cellar INK, it was only a matter of time before I felt obligated to address the power requirements of such systems. After all, it hardly makes sense to build the world's most efficient micro-miniature controller only to have it powered by the world's most inefficient, grossly oversized, Neanderthal-technology power supply. At least, that's the way my logic went. Little did I realize what masochism I was inviting.

The Circuit Cellar has a variety of control systems. There is such a maze, in fact, that I'm even beginning to need a road map to figure out where everything is going. To alleviate some of the confusion and provide a substantial development base for future expansion, I will be converting much of my system to an RS-485 net with many locally intelligent data acquisition and control nodes. Rather than stringing a wire 200 feet out to the garage to monitor a switch closure, I will simply connect it to the garage controller node with the dozen or so other I/O contacts and its status will be transmitted with everything else. (This whole system will be described in Circuit Cellar INK in the coming months.)

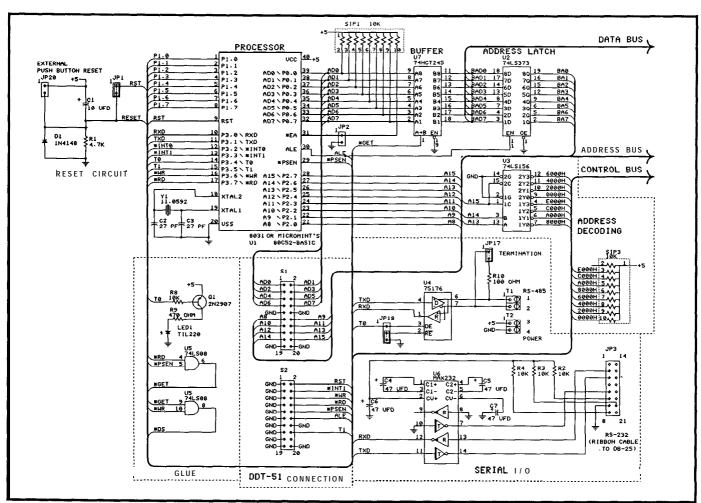

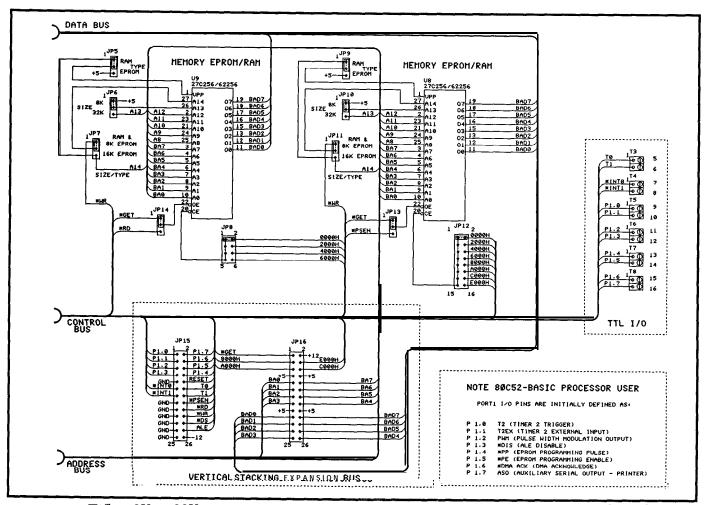

Not only does this cut down on wiring (you wouldn'f believe how much wire there is around this place already!) but it allows control changes to be done in a more orderly fashion. At the very least I'll have less aggravation tracing shorter wires. Most of the new system will consist of 8031- and 8052-

based dedicated controllers. [Editor's Note: For details on the RTC31 and RTC52 controllers, see "From the Bench" beginning on page 46.] So what's masochistic about this? Everything.

At the same time I decided to revamp the control system I thought I would take a more comprehensive approach toward power control and distribution. My present system has separate AC power supplies in each of its control areas. While I do have costly AC UPS power-backup units oncritical computercontrolelements, the system is still susceptible to control errors when individual locally powered sensors lose power (usually false negative because they are no longer operable). Of course, there are various methods of redundancy and monitoring that I could incorporate to correct these problems, but it seemed like too much bother considering the frequency of such events. Nevertheless, I determined I'd fix this condition if I ever redesigned the system.

Instead of 115VAC power for the new controllers, I intend to run everything on +12 volts. Like commercial alarm systems that run battery power even to the remote sensors, my new system could be entirely battery operated in the event of an AC power failure. One AC-line 12-volt power supply with a constantly charged 12volt gel-cell (or car battery for that matter) could serve as an uninterruptable power source for the entire system. The same power supply design could also be applied to a single embedded control system to provide UPS operation.

Running things from 12 volts is

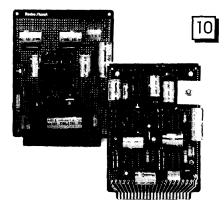

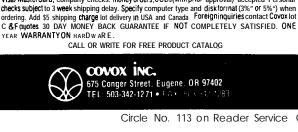

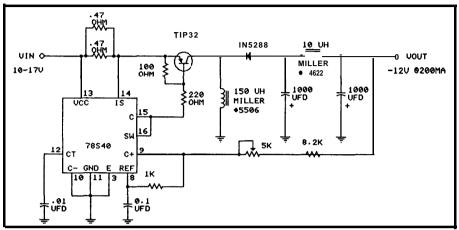

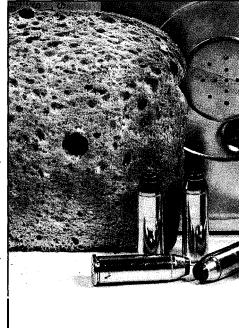

Photo 1—78S40-based design using traditional techniques.

nothing new. This application, however, presents some very special design considerations. Individual net controllers will have a variety of tasks. Some will be simple contact closure or temperature monitors. Others will have more elaborate configurations with event printers, modems, and displays. Even some form of data logging (hard disk) couldbeincluded.

From the outset I had to be aware of both power conversion efficiency

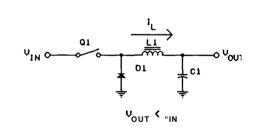

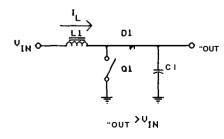

a) "Buck" Step-down Converter

**b)** "Boost" Step-up Converter

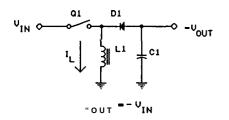

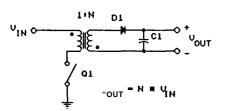

Figure 1 -Traditional *DC-to-DC* converter designs.

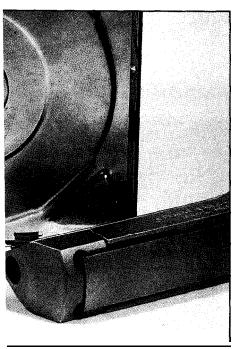

Photo **2**— LT 1070-based flyback converter.

and power consumption. Rather than tailor a custom supply for each node, I decided to build a general-purpose converter with three output voltages (+5V,+12V, and -12V) that could supply high currents where needed yet still have a low quiescent current when less consumption was required.

Unfortunately, getting from here to there is more easy to understand as a task than an accomplishment. Since I have built many low-current (less

**c)** "Buck/Boost' Polarity-Inverting Converter

**d)** 'Flyback' Transformer-Coupled Converter

than 100 **mA)** converters in previous projects, I perceived this as a weekend project where I merely extrapolated and expanded on basic design theory. Now, after successfully doing it, I can tell you that while the theory indeed holds true, the proof is more elusive.

### General-Purpose Design Objective

My design objective was to build a DC-to-DC converter that could be used as a general-purpose 12V-powered UPS for embedded systems. Its modest specification would be: +5V at 1.5 amps, +12V at 0.5 amp, and -12V at 0.25 amp. Its efficiency should let the battery last a reasonable time. More importantly, it should be efficient enough so that the current requirements of the 12V common supply are not excessive when powering multiple converters.

This article documents the progression of events leading to a final power supply configuration. At the same time it answers basic questions on switching regulator-based DC-to-DC converter design. For the record, I don't claim to be an authority **on** this subject. This project is presented as a collection of tested circuits with useful observations because, in my experience, successful high-current DC-to-DC converter designs have more to do with layout technique and analog black magic than anything as tangible as component specifications or sche-While my final converter matics. exceeds the design objectives and is relatively easy to build, successful duplication of it will have a lot to do with your ability to hold the magic wand properly.

Since we have to start someplace, understandingthedifferencebetween plain-vanilla series-pass regulators and switching regulators provides a good introduction. I'm sure someone has already asked why we don't just regulate the 12V common down to 5V through a three-terminal regulator.

### Series Pass vs. Switching Regulators

Since the advent of the three-terminal voltage regulator, it seems that

everyone has become a power supply expert. No longer are ten pages of calculations required to produce a design for even a modest power supply.

Three-terminal regulators like the LM317 are so easy to use that few experimenters stop to consider how inefficient they are. Consider for example, using an LM317 to power one of the controller nodes above. Given the maximum level of the common input voltage (Vin) for a 5-volt 1.5-amp output, 11 volts would be dropped across the regulator (in actuality, Vin will vary between 10V and 17V depending upon whether it is operating only from the battery or from an ACpowered charger and power supply). Power is dissipated by the regulator in an amount equivalent to the differencebetween theregulator's input and output voltages multiplied by the current through it.

The LM317 and similar linear regulatorssuchas the 7805 and LM340 are all called series dissipative regulators. They function in a linear mode, simulating a variable resistance between the input voltage source and the load. The regulator maintains a constant output voltage by dissipating the excess power as heat. Unfortunately, as we see in this example, it consumes 16.5 watts producing the desired 7.5-watt output (31% efficiency).

In most applications the ease of use and relative low cost of linear series regulators far outweigh the inherent lack of efficiency. The linear series regulator is well-suited for **medium**-current applications or applications with a small input/output voltage differential. When electricity isn't supplied by a battery and costs only ten cents per kilowatt-hour, it's hard to get concerned about losing 16.5 watts.

### Why Use a Switching Regulator?

Power supply efficiency usually isn't important unless size, heat dissipation, or total powerconsumption is limited. Since the common power source for our network controllers is a battery (when the AC power fails), we have to be more careful about how

much energy is converted for useful work and how much is thrown away as heat.

Efficiency is really the name of the game. In a series dissipative regulator, conversion efficiency is directly related to the input/output voltage differential. As the difference between the two voltages increases, efficiency decreases.

It would be far better if the regulator consumed no power and if all the power were channeled to the load. Of course, perfect conversion efficiency is impossible, but the inherent fault in using series dissipative regulators is the linear operating mode of the series-pass transistor. If the transistor is used as a switch (in saturated operation) rather than as a variable resistor (in linear model the pass transistor consumes very little power. (This is not a new discovery.)

A regulator constructed to operate in this manner is called a series switching regulator. The same seriespass transistor switches between cutoff and saturation at a high frequency, producing asquare wave of amplitude Vin. This waveform is then filtered through a low-pass LC (inductance/capacitance) filter, producing an average DC output voltage (Vout) proportional to the pulse width and frequency. The efficiency of such a regulator is generally independent of the input/output voltage differential and can approach 95% in good designs.

Switching regulators come in various circuit configurations, a few of which are the flyback, buck, boost, and buck-boost types. Also, unlike the typical three-terminal dissipative regulator, the switching regulator can be directly configured to operate in any of three modes: step down, step up, or polarity inverting.

### Switching-Regulator Basics

Figures la through 1d outline the three common modes of switching-regulator operation. Basically, the switchingregulatorconsistsofapower source which supplies a voltage *Vin*, a "switch" Q1, and an LC filter. The way the components are connected determines the output mode.

**Fi**gure Z-The 78S40 is a popular variable-trequency-type switching regulator.

**Buck Regulator**

In the step-down buck regulator in Figure 1a, the basic circuit operation is to close transistor switch Q1 for a time Ton, and then open it for time Toff. The total, Ton + Toff, is called the switching period 7'. Neglecting the saturation voltage of Q1(Vsat) and the diode(Vdiode), the voltage at the input to the inductor is +Vin during the time Ton and zero during Toff. (These other voltage drops would be included in calculations that choose actual components.)

When Q1 is closed, a step increase in voltage is applied to the inductor coil, which has the value L. However, current flowing through an inductor cannot change instantaneously; instead it increases linearly according to the factor L(di/dt), building amagnetic field. This reduces any instantaneous current changeseenby theload. When Q1 opens, the magnetic field in the inductor decays linearly, supplying power to the load. The current path is completed through the forward-biased flyback diode D1. As you can see mathematically, the output voltage of a buck converter is always less that its input:

Duty Cycle (

$$DC$$

) =  $Ton$

$Ton+Toff$

$Vout = Vin \times DC$

In this type of switching regulator, the inductor and capacitor form a low-pass filter. High-frequency pulses are applied to the input, and an averaged DC level comes out. The **peak**-to-peak ripple voltage is a function of the switching period T and the values of the inductance L and capacitance C. As the frequency of operation is increased, the voltage ripple is reduced, but the supply becomes less efficient.

### **Boost Regulator**

Figure 1billustrates the circuit configuration of the basic step-up boost regulator. In this type of regulator, closing Q1 during *Ton* charges the

### CO OR **IM GEWI** E

ZIP Software now allows both the original serial DTO1 and ImageWise/ PC to digitize and display full-colorpictures on an IBM PC with VGA.

See page 44for more details,

inductor. When Q1 is opened, the inductor discharges through D1 into the load. The output voltage is:

$$Vout = \frac{Vin}{1-DC}$$

Current drawn from the input is delivered in pulses to the output load at significantly higher currents than the average load current. Both Q1 and D1 must be sized to handle these increased currents. You'll also note from the equation that in all cases, *Vout* is greater than *Vin*.

### **Buck-Boost Regulator**

Figure 1c shows a polarity-invert-

given by:

$$Vout = -Vin \times (DC / l-DC)$$

Note that the magnitude of *Vout* can be either greater or less than *Vin*.

### Flyback Regulator

A final configuration worthy of interest is theflybackconverter, shown in Figure Id. Flyback regulators use a transformer, as opposed to a simple choke, to convert *Vin* to *Vout*. During Ton, energy builds up in the core due to increasing current in the primary winding. At this time diode D1 is reversebiased. WhenQ1 opensduring *Toff*, the total stored energy is trans-

Figure 3-A 1.5-amp, 5-volt buck regulator using the 78\$40.

ing buck-boost switching regulator. As in the other cases, closing Q1 charges the inductor during Ton. When Q1 is opened during *Toff*, there is a "kickback" voltage produced by the inductor as it discharges. This effectoccurselsewhere, too. **For** years, many of you have probably been putting reverse-biased diodes across relay coils, perhaps without thinking about it. The purpose of the diode is to dampen the high-voltage spike produced after a pulse is applied to the inductive relay coil. In a switching power supply, rather than short out the voltage, diode D1 directs this opposite-polarity voltage to the load. Buck-boost regulators have an output ferred to the secondary winding and current is delivered to the load. The primary-to-secondary turns ratio (*N*) affects *Vout* and should be set for optimum power transfer:

$$Vout = Vin \times N \times (DC/l-DC)$$

The greatest advantage of flyback regulators is that they can have an output voltage that is higher or lower than theinputvoltageandcaninclude multiple windings on the transformer secondary to create other isolated voltages. Unfortunately, all this does not come without a price. Flyback converters have higher ripple currents due to the high energies which must

be stored in the form of DC current in the windings compared to using pure AC waveforms.

Variable- vs. Fixed-Frequency Regulation

Generally speaking, in all four cases, the output voltage *Vout* is regulated by controlling the ratio of Ton/T, which can be altered in a number of ways depending upon the control method. Two of the more common approaches are variable pulse width (pulse-width modulation) and variable frequency. In a pulse-width-modulated switching regulator, the switching period T is fixed and the "on" time Ton varied. Conversely, in a variable-frequency regulator, Ton is fixed and the "off" time *Toff* is varied.

Thevariable-frequency switching regulator is generally easier to design and build since the magnetic flux developed in the inductor coil during the fixed on-time determines the amount of power deliverable to the load. This eases the design of the inductor because the inductor's operating region within its characteristic curve is precisely defined. Operating frequency, which increases proportionally with the load, is mostly a function of the inductance L, capacitance C, and voltages Vin and Vout.

The fixed-frequency pulse-width-modulated switching regulator varies the duty cycle to change the average power delivered to the load. This method is particularly advantageous for systems employing transformer-coupled output stages and is often used in commercial switching supplies with multiple outputs. It is more complex and uses more components than variable-frequency supplies, but theadvantagesoutweightheextracost in high-current applications.

Typical operating frequencies of switching regulators range from 10 to 50 kHz. However, there are some tradeoffs. High frequencies reduce the ripple voltage at a price of decreased efficiency and increased radiated electrical noise. If the frequency is lowered, greater efficiency and less electrical noise will result, but larger coils and capacitors are needed. Also,

a switching power supply operating at 10 kHz can become quite annoying to listen to after a while.

The most effective frequency range for optimizing efficiency and size with the components presently available is around 20–50 kHz. This is out of the range of human hearing yet low enough to be within the switching speeds of most inexpensive transistors and diodes. As switching speeds of newly developed high-current semiconductors increase and new ferrite components are introduced, practical operating frequencies will rise. There are discussions now about switching regulators that will operate at 1 MHz or more.

### Putting Theory to the Test

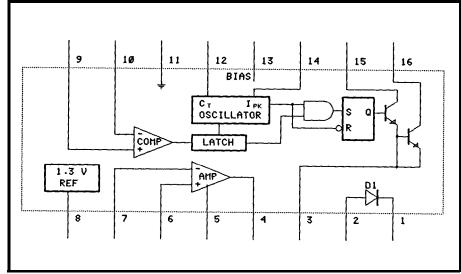

My first approach to building the new switching supply was to use the 78S40 switching regulator which is readily available and inexpensive (a block diagram is show in Figure 2). The 78S40 is a variable-frequency-type regulator which contains a current-controlled oscillator, current-limit

| Characteristic                      | Buck                                                                        | Boost                                                                                                      |                                                                                                                         | <del>,                                     </del> |

|-------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                     |                                                                             |                                                                                                            | Buck-Boost                                                                                                              | Units                                             |

| <sup>l</sup> pk                     | <sup>2I</sup> OUT(Max)                                                      | $2I_{OUT(Max)} \cdot \frac{V_{OUT} + V_D - V_S}{V_{IN} - V_S}$                                             | $2^{I}_{OUT(Max)} \cdot \frac{V_{IN} +  V_{OUT}  + V_{D} \cdot V_{S}}{V_{IN} \cdot V_{S}}$                              | A                                                 |

| P <sub>SC</sub>                     | 0.33/I pk                                                                   | 0.33 l <sub>pk</sub>                                                                                       | 0.33 l <sub>pk</sub>                                                                                                    | Ω                                                 |

| <sup>t</sup> on                     | V <sub>OUT</sub> + V <sub>D</sub>                                           | V <sub>OUT</sub> + V <sub>D</sub> - V <sub>IN</sub>                                                        | IV <sub>OUT</sub> I+V <sub>D</sub>                                                                                      |                                                   |

| <sup>t</sup> off                    | VIN-VS - VOUT                                                               | V <sub>IN</sub> - V <sub>S</sub>                                                                           | $\frac{ V_{OUT}  + V_D}{V_{IN} \cdot V_S}$                                                                              |                                                   |

| L                                   | VOUT + VD · t off                                                           | $\frac{V_{OUT} + V_D - V_{IN}}{I_{pk}} \cdot t_{off}$                                                      | V <sub>OUT</sub>   + V <sub>D</sub>                                                                                     | μН                                                |

| <sup>t</sup> off                    | V <sub>OUT</sub> + V <sub>D</sub>                                           | I <sub>pk</sub> • L<br>V <sub>OUT</sub> + V <sub>D</sub> - V <sub>IN</sub>                                 | I <sub>pk</sub> • L<br>IV <sub>OUT</sub> I + V <sub>D</sub>                                                             | με                                                |

| C <sub>T</sub> (µF)                 | 45 x 10 <sup>-5</sup> t <sub>off</sub> (μs)                                 | 45 x 10 <sup>-5</sup> t <sub>off</sub> (μs)                                                                | 45 x 10 <sup>-5</sup> t <sub>off</sub> (μs)                                                                             | μF                                                |

| co                                  | BV <sub>ripple</sub>                                                        | (l <sub>pk</sub> - I <sub>OUT</sub> ) <sup>2</sup> • t <sub>off</sub>                                      | (lpk - lOUT) <sup>2</sup> • toff<br>2lpk • Vripple                                                                      | μF                                                |

| Efficiency                          | $\frac{v_{IN}\cdotv_{S^+}v_{D}}{v_{IN}}\cdot\frac{v_{OUT}}{v_{OUT^+}v_{D}}$ | V <sub>IN</sub> • V <sub>OUT</sub> • V <sub>OUT</sub> • V <sub>OUT</sub> • V <sub>D</sub> • V <sub>S</sub> | $\frac{v_{\text{IN}} \cdot v_{\text{S}}}{v_{\text{IN}}} \cdot \frac{v_{\text{OUT}}}{v_{\text{OUT}} \cdot v_{\text{D}}}$ |                                                   |

| IN (Avg)<br>(Max load<br>Condition) | $\frac{I_{pk}}{2} \cdot \frac{V_{OUT} + V_{D}}{V_{IN} - V_{S} + V_{D}}$     | 1 <u>pk</u> 2                                                                                              | $\frac{I_{pk}}{2} \cdot \frac{I_{OUT}I + V_{D}}{V_{IN} + I_{OUT}I + V_{D} - V_{S}}$                                     | A                                                 |

**Figure 4—** Numerous formulas are used in the design of buck, boost, and buck-boost converters.

sensor, voltage reference, high-gain comparator, high-current op-amp, transistor switch, and power-switching diode. A single capacitor sets the frequency range (adjustable between

100 Hz and 100 kHz, but normally used at 20 to 30 kHz), and one external resistor provides current-limit sensing. Other than a few discrete resistors to set the output voltage, only an

# Science, Engineering & Graphics Tools for Microsoft C, Turbo C and Turbo Pascal

Science and Engineering Tools are a collection of general purpose procedures and functions which solve the most common data analysis and graphics problems encountered in science and engineering applications. All procedures and functions are supplied on disk in the source code of the target language. The procedures and functions are compatible so the graphics functions can directly display the output of a regression, curvefit, etc. All of the routines can be used royalty free in compiled form. A 150 page manual describes the form, function, and parameters of each procedure and function. The Science and Engineering Tools are available for Turbo Pascal 4.0, 5.0, Turbo C 1.5, 2.0 and Microsoft C 5.x for IBM compatibles.

Ordering Information

Model#

Version

Price

IPC-TP-016

IBM Turbo Pascal

\$ 79.95

IPC-TC-006

IBM Turbo C

\$ 79.95

IPC-MC-006

IBM Microsoft C

\$ 79.95

Price includes shipping within North America. Elsewhere add \$18.00 for shipping. Mastercard, Visa, Company PO's, and personal checks accepted. MASS. residents add 5% sales tax.

### **FEATURES**

100% Royalty Free

Turbo Pascal 4.0, 5.0 Turbo C Rev. 1.5, 2.0 or Microsoft C Rev. 5.x compilers

CRT Graphics Adapter Support - the graphics libraries use the graphics routines supplied with the respective compiler. (CGA, EGA, Hercules, VGA)

Hardcopy support - Epson MX, FX and LQ printers, HP plotters, HP Laserjet and Thinkjet printers, Toshiba 24 pin printers and other devices

Science/Engineering charting routines - Linear, semi-log, and log graphs. Auto-scaling of axes, line, scatter, pie, and bar charts. Charting Graphics Now Includes Contour Plotting.

**3-D plotting** - translation, scaling, rotation, and perspective routines

**Statistics** - mean, mode, standard deviation, standard error, etc.

Multiple Regression - With summary statistics Curve Fitting - Polynomial and cubic splines Simultaneous Equations - real and complex Fourier Analysis - Forward and inverse FFT, Rectangular, Parzen, Hanning, Welch, Hamming,

and Power Spectrum

Matrix Math - Real and complex Complex Number Arithmetic Eigen values and vectors Integration - Simpson's method

Differential Equation - Runge-Kutta-Fehlberg Linear Programming - Simplex method Root Solving - Bisection, Newton and Brent methods

Files Transfers - Lotus 1-2-3

Data Smoothing

Special Functions - Gamma, Beta, Bessel, error, hyperbolic trig, orthagonal polynomials

RS-232 Support - the Turbo Pascal version includes an interrupt driven RS-232 driver

1191 Chestnut St., Unit 2-5, Newton, MA 02164 USA Tel. (617)965-5660 FAX (617)965-7117 inductor and capacitor are required to make a highly efficient switching power supply. (The internal **Darling**-ton-configured transistor switch and diode of the **78S40** are capable of handling 1.5 amps at 40 volts, but an external transistor and diode are

connected to a fixed 1.3V reference voltage. If the output voltage exceeds the reference, the regulator will begin to skip Ton cycles until the voltage lowers. Changing the output voltage setpoint in a buck converter is simply a matter of changing

Figure 5-A buck-boost design using the **78\$40** generates **-** 72V from a IO- 7 7V input.

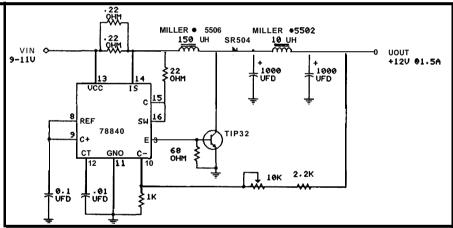

Figure 6-Again using a 78\$40, a boostdesign is used to generate + 72V from a 9-77 V input.

needed here because of the increased currents involved in this design.)

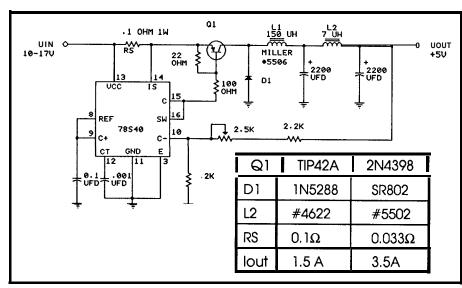

### 5-Volt Buck Regulator

Figure 3 outlines a **1.5-amp**, 5-volt buck regulator using the **78S40**. Operating frequency is set by the capacitor at pin 12 (usually between 0.01 and 0.001  $\mu$ F). *Vin* is connected through the current-sensing resistor to the transistor switch, and at Ton it charges the inductor. During *Toff*, the diode conducts and the energy in the inductor is transferred to the load. The voltage at the load is fed back to a comparator. The other side of the comparator is

the resistor divider between this comparator and the output.

The current-sensing resistors are intended to protect the switching transistor and diode rather than the load. The 78S40 will stop functioning when the voltage between sense points (pins 13 and 14) exceeds 0.33 volts. For a 1.5-amp buck regulator, the peak current is typically 3 amps and a O.l-ohm resistor (or two 0.22-ohm resistors in parallel) is used.

As you might have guessed, the most important elements in switching regulators are the transistor and the diode. For the same inductor value, this regulator configuration can have higher or lower output current depending upon the speed and current ratings of these devices. Switching regulators use special Schottky Barrier Rectifiers specifically for their low forward-voltage drop (0.3-0.6 volts typically) and high speed. Using a TIP42A (6-amp) transistor and 1N5822 (3-amp) Schottky diode, I was able to obtain a 1.5-amp output current for a Vin range of 9-17 volts. By changing the transistor to a 2N4398 (30-amp) and the diode to an SB840 or SR802 (8amp), the output current could be increased to 3.5 amps (the current-sensing resistance was lowered to 0.033 ohms to handle the higher currents).

Figure 4 outlines the mathematics involved in making buck, boost, and buck-boost converters with the 78S40 switching **regulator**. For the most part I used these calculations to form the fundamental basis of the end result with a certain sprinkling of empirical modification. Because the input voltage (Vin ranges from 10 to 17 volts) is not a constant, there is actually a range of component values which are all optimum at a specific combination of Vin and load current. The final component values are compromise selections derived by building the circuit and testing it.

An important fact about the buck converter also pertains to boost, **buck**-boost, and other configurations. Traditional switching regulators are electrically very noisy. Switching transients can be coupled throughout a power supply either inductively between adjacent components **or** directly through inadequate or misrouted grounding. **Grounding** in a switching power supply, like EM1 reduction, is one of those black magic areas.

Much of the noise generated consists of 100–200-ns spikes which occur when transistor Q1 is either turned on or off. It is not unusual to see 3-volt spikes (at about 30 kHz) on a 5-volt output line if you aren't careful! Eventually, you will discover that if you remove the 12" ground extension jumper from the scope probe and use just the short pigtail ground across the load that the noise is actually less than a volt. That's better, but not great.

In most cases, switching regula-

tor designs are greatly improved by post-regulator filtering. Capacitors alone, regardless of their size, usually don't eliminate these high-frequency spikes. Instead, an LC filter consisting of a 7-10-uH choke and a 1000-4700μF capaci tor works well in most cases. Be advised that these aren't just any old inductors. Typical low-cost molded inductors are only rated at a few hundred milliamps. Since we are talking amperes here, make sure that the filter components will handle the current. The 9-amp Miller chokes that I used reduced the electrical noise to about 200 mV peak-to-peak.

Negative 12-Volt Buck-Boost Regulator

Creating -12 volts using the 78S40 switching regulator is described schematically in Figure 5. The major difference between it and the straight buck regulator is that the inductor and diode are now in the reverse positions. The inductor is charged during Ton again, but this time during Toff the negative-polarity EMF gener-

Figure 7-The LT7070 integrated switching regulator is often used in flyback converter designs

ated by the collapsing magnetic field in the inductor is directed through the Schottky diode to the output capacitor and load. Regulation set-point feedback, current limiting, and LC output filtering are handled much as before except this circuit is designed to supply only about 200 mA.

### MODEL PCSS-81 OCTAL SERIAL COMMUNICATION CO-PR-R

- 8 Co-processor driven RS232 channels/card.

- BIOS Enhancement Software included.

- · Eliminates host processor overhead.

- 32-2048KByte buffer memory.

- May be used standalone in custom appl.

### ► **HIGH** PERFORMANCE

#### MODEL 9000 (E)(E)PROM MPU PROGRAMMER

- Fastest programmer on the market.

- Quick&Intelligent programming atgorithms.

- Supports megabit eproms.

- Programs largest variety of chips.

### ► **TIME** SAVING

### MODEL ROMX-2XL **EPROM EMULATOR**

- Emulates 2716-27010 eproms. · 256K to 1024K memory available.

- Battery backed up, auto emulate on power-up.

- Low-cost, pays for itself on first project.

- Free 19.2K Serial Communications Software

VERSATILITY

#### MODEL PCSS-8X MULTD'ORT **SERIAL ROARD**

- 8 RS232 ports par card (opt. 4 port).

All 8 ports 100% DOS compatible,

- 32 ports may be added to a PG.

- Optional RS422 to 4000 ft.

- Interrupt driven BIOS Enhancement Software included,

If Intelligence, Versatility, High Performance and Time Saving products are what you're looking for, make that move today and let GTEK® put one, two, three or all four of these products to work for you! Remember, other development products are available, -CALL!

> DEVELOPMENT HARDWARE &SOFTWARE P.O. Box 2310; Bay St. Louis, MS 39521-2310 U.S.A.

>

> ORDER TOLL FREE 1-800-255-GTEK (4835) FAX: 1-801-467-0935 MS & Technical Support 1-601-467-8048

> > Circle No. 12 ] on Reader Service Card

### **12-Volt Regulator**: Boost or Buck?

When I got to the 12-volt section of the power supply, the configuration was not as straightforward as theother sections. In fact, it was almost easier to contemplate going back to a low-dropout S-terminal series-pass regulator than to build what seemed to be required here. The trouble with producing 12 volts from a 10V-17V source is that it can't easily be done with a single-stage design. Let me explain.

Using a buck-converter design we can produce 12 volts from an applied voltage of approximately 13V to 45V (theupper limit of the **78S40**). **Similarily, using a** boost-converter design we can produce 12 volts from an applied voltage of approximately 5V to 12V (a **typical 12-volt output boost-converter** circuit is illustrated in Figure 6). Unfortunately, since our input supply voltage can range from **10V** to **17V**, no one circuit adequately fits the bill.

Just for the sake of experimentation, I did build a buck-buck-boost compound regulator just to see if the results were worth the effort. Using a circuit similar to Figure 3, I made a 3.5-amp, S-volt output buck regulator. Then, with a circuit similar to Figure 5, I configured an 8-volt—to—12-volt boost regulator. Surprisingly, the compound configuration worked, but it seemedlessefficient than 1 would have liked and it produced more electrical noise than theothercircuits; undoubtedly because of greater PC board real estate and radiating components.

The results of my empirical cutting-and-pasting are in Photo 1.

### A Flyback Regulator to the Rescue

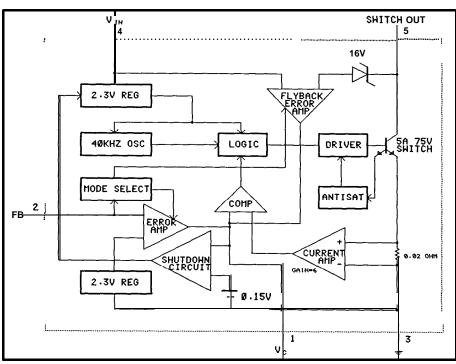

As the others around the office here can verify, I had considered forgetting this whole project **idea** because I hadn't arrived at a "neat," **cost-effectivesolution** to the problem. **The Photo** 1 prototype, while workable, was hardly some thing I cared to make more than one of. It was at that point that I came across the Linear Technology Corporation LT1070 integrated switching regulator and its suggested use in **flyback** converter designs.

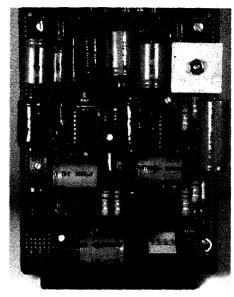

The LT1070, block diagrammed in Figure 7, is a fixed-frequency current-mode switching regulator. It operates from 3V to 60V and can be used to produce the same buck, boost. and buck-boost circuits previously described as well as a flyback converter. The major advantage of the LT1070, unlike the 78S40 used at this current, is that both a 5-amp transistor switch and a 0.02-ohm current-sensing resistor are internal to the LT1070 chip. This not only reduces heatsink and board space requirements but also eliminates the radiated noise from con**nections** between these components. The shorter the wires in a switching regulator design the less electrical noise.

The flyback converter circuit is very straightforward: The LT1070 closes the switch on the primary winding causing the transformer core to

store energy in its magnetic field. A resistor-capacitor-diode "snubber" network isinserted across the primary to reduce switching transients. No current flows in the secondary windings because the diodes are reversebiased at this time. When the switch is turned off, the magnetic field collapses and induces a voltage into the secondary windings. Given the reversepolarity of the collapsing field, the diodes become forward-biased and the energy is transferred to the outputs. (Note: It is important not to confuse this flyback pulse transformer with a sinusoidal AC transformer half-wave converter design. In all cases the secondary windings use Schottky diodes and the energy is transferred in squarewave pulses, much the same way as the previously described buck converters. Use of "standard" silicon rectifiers will cause excessive power dissipation and low output voltage.)

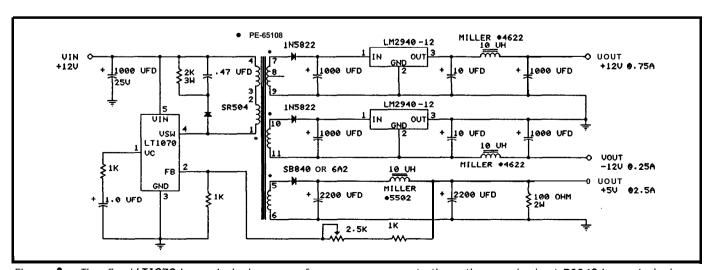

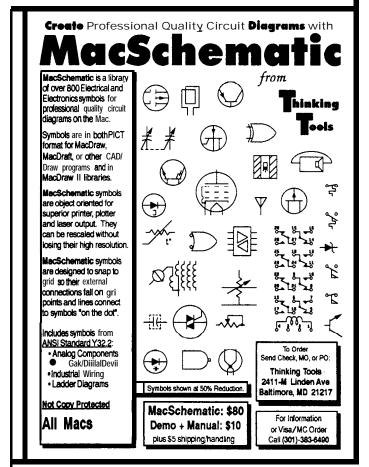

The PE-65108 pulse transformer has two primary and three secondary windings. Given the turns ratio, this circuit can work at either 6 volts with a parallel-wired primary, or at 12 volts withaseries-wiredprimaryasshown. There are three secondary windings. Two can be used for 12-volt outputs while the third is designed for 5 volts.

The system regulation is controlled by feedback from the 5-volt supply section. The 5-volt secondary output **uses a** resistor divider network to compare the 5-volt output to a **1.24-**volt reference in the **LT1070**. If the output voltagestarts **todrop**, **the pulse-**

Figure 8— The final LT1070-based design uses fewer components than the equivalent 78S40-based design.

# FREE CATALOG

### RS-232C INTERFACE AND MONITORING EQUIPMENT CATALOG

Order direct from manufacturer TODAY and SAVE

### WRITE or CALL for YOUR FREE B&B ELECTRONICS CATALOG TODAY!

Pages and pages of photographs and illustrated, descriptive text for **B&B's** complete line of RS-232 converters, RS-422 converters, current loop converters, adapters, break-out boxes, data switches, data splitters, short haul modems, surge protectors, and much, much more. Most products meet **FCC15J.**

Your RS-232 needs for quality, service and competitive prices will be more than met by **B&B** ELEC TRONICS. Manufacturer to you; no middleman!

Money-back guarantee! Same-day shipment! Oneyear warranty on products! Technical support is readily available.

Terms: Visa, MC, cash orderspostpaid, P.O.'s from qualified  $\Gamma ated$  firms accepted. IL residents add 6 1/4% sales tax.

| RUSH    | MY | NEW | FREE | CATALOG |

|---------|----|-----|------|---------|

| Name    |    |     |      |         |

| Company |    |     |      |         |

| 2       |    |     |      |         |

### B&B electronics

State

**4032C** Baker **Road** • P.O. 1040 Ottawa, IL **61350**

Phone: 81 S-434-0846 Sircle No. 105 on Readers Service Carc width-modulated switching regulator just lengthens Ton a bit for each cycle to compensate and vice versa.

With the 5-volt secondary regulating properly (and not overloaded) approximately 14V-16V is induced in each 12-volt secondary winding. A pair of special low-dropout-voltage three-terminal linear regulators are used to create a regulated 12-volt output. LM2940-12 l-amp, low-drop out regulators require only 0.6 volts across them (Vout-Vin) instead of the 3 volts typical of **7805-type** devices. The LM2940-12 is only available as a positive voltage regulator, but with isolated windings, each secondary can be configured as an isolated 12-volt output. One is simply inverted to appear as a negative 12-volt output.

### The Proof is in the Pudding

One final concemisradiated EMI. To minimize this electrical noise and inductive pickup, the divider resistors and the components between pin 1 and pin 3 should be mounted very close to the LT1070. A single-point grounding system should be employed with the wires routed for least radiation (black magic again). All three secondary outputs have post-regulator LC filters to eliminate spikes. You'll note that the divider feedback network is connected on the "quiet" side of the LC filter so that output noise does not unduly influence regulator stability.

This flyback regulator seemed to work quite well and noise was generally less that 200 mV peak-to-peak on any output on my prototype. I would expect it to improve on a production PC board. With a 12-volt input I was able to obtain 2.5 amps at +5 volts, 0.75 amp at +12 volts, and about 0.25 amp at -12 volts. If I raised the input voltage to 17 volts, more output current was available from all three outputs proportionally. Conversely, at a given input voltage, the 5-volt output current could be raised if the 12-volt output currents were lowered and vice versa. There seemed to be a minimum 5-volt current necessary for regulation, however, and a 100-ohm resistor was added to make sure it was always

there (and should be removed in a fixed-use application).

As the input voltage was lowered to 10 volts, the available output current wasalsoreduced. Conservatively, it was still 1.5 amps at +5V and a 100 mA at ±12V. I tested this to the extreme and found that the board still regulated down to about a 6.5-volt input (of course if I ever had to depend on that, I'd probably have worse problems elsewhere). If you use this design for currents lower that I specified, then you may want to use an alternative regulator. Both the LT1071 and LT1072 have lower current ratings and costs.

The completed power supply circuit, shown in Figure 8 and Photo 2, used considerably fewer components and less board space than the previous three designs to produce the same relative power output.

### **Sources**

J.W. Miller

Division Bell Industries

19070 Reyes Ave.

Rancho Dominguez, CA 90224

(2 13) 537-5200

linear Technology 1630 McCarthy Blvd. Milpitas. CA 95035 (408) 432-I 900

Pulse Engineering, Inc. P.O. Box 12235 7250 Convoy Court San Diego, CA 92112 (619) 268-2400

IRS =

201 Very Useful 202 Moderately Useful 203 Not Useful

### Circuit Cellar Books

Circuit Cellar INK writers often refer to previous Ciarcia's Circuit Cellar articles. These past articles are available in book form from Circuit Cellar Inc., 4 Park St., Suite 12, Vernon, CT**06066**.

Ciarcia's Circuit Cellar Volume I covers **articles** in **BYTE** from September **1977through** November 1978. Volume II covers December 1978 through June 1980. Volume III covers **July** 1980 through December **1981**. Volume IV covers January 1982 through June 1983. Volume V covers July 1983 through December 1984. Volume VI covers January 1985 through June 1986.

Ctrl

# VISI BLE I N K

# Letters to the INK Research Staff Answers;Clear and Simple

Tell me Why

I want to thank you again for the fine work you are doing to disseminate electronic leading-edge technology and encouraging us to look deeply into this field and its mushrooming future.

I have a few questions for you:

- 1. Concerning HAL-4, why are the signals to IC8 (74HC373) scrambled on input and then descrambled on output?

- 2. The original schematics show the IC4 (8255) CS hooked over into IC7 (74LS138), which supposedly is not there until the full system is defined. The same situation exists for IC5. Why is this? How should it be hooked up?

- 3. At a previous job, I worked on a parallel processing system which had three **CPUs** running in parallel, and used a memory scheme which included "shared" RAM, which could be accessed as read/write by any or all of the **CPUs**, as well as "private" RAM which could only be accessed by its associated CPU. I was wondering how one would go about setting up a circuit layout so as to be able to do this with microprocessors.

- 4. I am having a bit of difficulty finding information as to what to do to establish a **CMOS/TTL** interface. Can you give me some hints here?

- 5. Where can one get information as to what sort of current demands different devices will incur, so as to be able to total up a system's power usage?

- 6. What is a good way of interrogating a battery-supplied power setup so as to detect a "battery low" condition?

**Allan** R. Summers Pasadena, TX

Dear Allan,

Thanks for the kind words on OUT projects! We **t** y to strike a balance between "leading edge" and "practical" projects; letters like yours tell us that we are on the right track.

The scrambled lines on Hal's IC8 make sense if you look at the printed circuit board. Assigning the bits in that order made the traces fit on a double-sided board! Since this depends on fhe particular board, you'll find different layouts on all the projects; ve y often we leave the choice of bits up to the guy who does the PC board layout.

That schematic showing the combinations of 8031 systems was essentially correct, but you have to take the colored backgrounds with a grain of salt. Basically, some of the gates needed for various "subsysfems" wound up in the wrong colors simply because gerrymandering in all the peninsulas and tributaries would have complicated things a little too much. What it boils down fo is that, if a circuit looks like it needs a connection, if does!

There were a feW minor errors in the schematics; if you're particularly interested in the details you should sign onto the Circuit Cellar BBS and get fhe latest information.

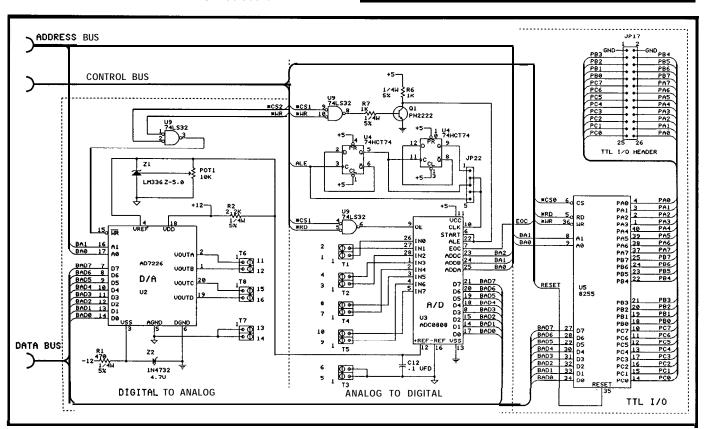

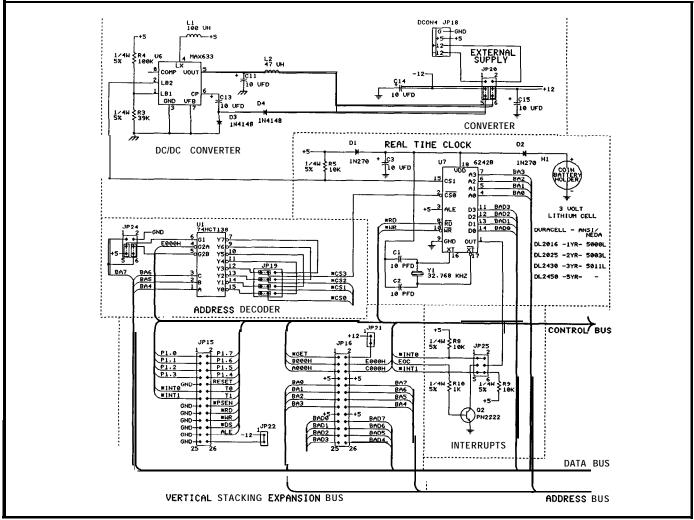

The trick to having both local and shared memory is that you must have buffers and gates to provide separate dafa paths for each CPU, with separate address logic on both sides. If you take alookaf the ImageWise schematics, you'll see how fhevideodafa bus (going to the ADC and DAC chips) is separated from the 8031 data bus (going to the EPROM and address latch). Trace down the addresses though the multiplexers to see how the 8031 can be doing something while the RAMs are handling video data.

There are several ways to convert from CMOS to TTL, rangingfrom ICs dedicated to the job all fhe way down to baling-wire circuits you build on the fly. It depends on how many lines you need to convert and how many units you're building; a one-off project can use circuitry that makes no sense in a real production unit.

Rather than give you the answer, we'll describe the process. There are two conditions you have to cover: a CMOS low level must draw enough current from the TTL gate to ensure that it "sees" a zero, while a CMOS high level must supply enough current for the TTL back leakage to shut off the gate. Therequisite currents and voltages differ for the various flavors of TTL and CMOS logic, as well as for individual gates within each family, so there are no hard-and-fast rules.

One rule of thumb is that you should not have a singlegate driving both CMOS and TTL loads; stick with one or the other. This simplifies building the converters because you don't have fo worry about the effects of drawing nonstandard currents from thegafe on the rest of the system.

The data books that give you enough information to build level converters also tell you about the maximum and average current requirements for the complete chip. Mail order parts sources usually advertise the National and TZ data books; take a look at the Digi-Key and Jameco catalogs for the specifics. Make sure you get the Application Nofes books, too, because they have lofs of recommendations and hints for handy circuits.

As you might expect, defecting a low-battery condition requires an analog-to-digital converter. Fortunately, you only need one bit, so it isn't too hard to build, sincesomething like an

LM311 comparator that compares a referenceagainst the battery voltage fills the bill. When the battery falls below the reference voltage, the LM311 output changes state (either high to low or low to high, depending on your circuit ry) and your CPU starts saving things.

The trick is that you'vegof to be able to correlate the battery voltage with remaining charge. Thevolfagevaries with ambient temperature, as does the available charge, so this isn't quite as simple as if sounds. We don't recall fheparf number offhand, but we think National Semiconductor makes a battery-voltage monitor IC that handles some of the grisly details. Once you get fhedafa books you can take a walkthrough the "building blocks" section and find something useful.

You cangef rapid answers to questions like these by signing onto the Circuit Cellar BBS. There are a bunch of really competent folks hanging out there who can probably answer any question you can dream up. Best Of all, the whole group can suggest approaches you haven't thought of and describe all the details based on real experience.

#### A Problem of Power

I have a car restoration shop. My problem is that my CAD system (AT clone running at 10 MHz) sends out beeps and stops when we use our plasma cutter, which has no HF to start its arc.

Our telephone system, a genuine Bell setup, lights up all six buttons and won't ring when our HF piggyback arc stabilizer runs when we're using the heliarc welder.

Is the fix as simple as **adding ground** wires? Or should I build a screen room around the welder/cutter?

How about this as a project for your magazine—"Clean Power in an Ugly World"?

Robert J. Schumann Kansas City, MO

Dear Robert.

**Every** now and again wegef a letter that reminds us of just how odd things get out in the real world...

The hash in your AT and phone system is probably coming through the power lines. If could be radiated (we bet you don't have any background music playing while you're welding, do you?), but we think the place to start is with the line cords.

Any electric arc will generate energy across the entire electromagnetic spectrum, quite literally from DC to daylight in fhecaseofa welder. Naturally enough, the more power in the arc, the more power shows up as interference. What you need is a filter foremovefheobjecfionablefrequencies whileleffingfhearc burn normally. From our experience with EMI (electromagnetic interference) generated by computer systems, a ferrite filter is the way to go.

Ferrite filters are made up of a finely divided iron compound with a high resistance to electrical current. A current-carrying wire passing through a ferrite slug induces a current in the ferrite, but theferrite's resistancedissipates fheenergyveywell. The resistance increases withfrequency, so fheslugforms a quite effective low-pass filter.

One catch is that the ferrite slug must be able to handle the induced current without saturating. In the case of your welders and cutters, that's going to fake a pretty big chunk! Rather than paying real money for this project, fake a trip to the local junk yard and scavenge the yokes from a couple of TV sets—the older, the better. If you've never rummaged around in a TV before, what you're looking for is the deflection hardware around the neck of the picture tube. Along with all the coils is a big hunk of blackferrite, which is just what you want. You may have to break the tube fogef the yoke off, but that's why you do this trick in the junk yard instead of Sears.

Do be careful, though, because the implosion resultingfrom shattering thepicture tube can blow glass all over the neighborhood. Wear a face shield and gloves. The safest method is to put the neck of the tube in a plastic bag and rap if with a screwdriver. This presumes, of course, that the junk yard has no further interest in the tube!

With a few yokes in hand, simply string the power lines through them. If the power lines go directly to a junction box on the wall, run the cables on the secondary side through the yokes. The key point is that the ferrite slug should form a continuous path around the current carrying wire, with one wire per yoke. Don't bother wrapping the wire around the yoke, because one "turn" is enough; more turns simply builds a step-down transformer with a single-turn shorted secondary.

You should see an immediate improvement, but if not, fy moving **the** yokes closer to the workpiece. Because fhearcs are the source of the hash, the less wire carrying the current, the less interference will be induced elsewhere in your building.

As an alternative, fy puffing a yoke or two on the power lines leading to the AT and phone system. After all, if doesn't matter where you filter the hash out as long as if doesn't get to thecircuit y. You will have fofilferall of fhepower lines leading to the AT; don't forget the printer and modem!

We've been thinking of doing an article on RFI control and your letter has pushed us over **the** edge. It'll probably show up around the end of 1989, simply because we'vegof so much other stuff to do between now and then.

IRS

204 Very Useful205 Moderately Useful206 Not Useful

In Visible INK, the Circuit Cellar Research Staff answers **micro**computing questions from the readership. The representative questions are published each month as space permits. Send your inquiries to:

> INK Research Staff c/o Circuit Cellar INK B o x 7 7 2 Vernon, CT 06066

All letters and photos become the property of **CCINK** and cannot be returned.

### **PRODUCT REVIEWS:**

# The Next Generation Circuit Cellar INK sells out and enjoys it!

It'snot often that **one** is witness to a major event in human history, but if you're reading this, you're not only a witness, but an eyewitness! Yes, you see before you an occurrence of epoch-changing proportions. Mere human inventions pale in significance before this. Polio vaccines, atomic energy production, and those little plastic things that slowly slither down your walls all fade away when compared to what you hold before you.

What am I talking about? Why the Circuit Cellar INK Benchmarking, Product Evaluation, and Junk-Food Consumption Testing Facility.

Now, I know we said that you wouldn't see any "metoo" reviews or evaluations in Circuit Cellar INK, but hey, times change. First, we saw what was being passed off as product reviews by other magazines and realized that no publication in this end of the universe was better qualified to write technical, hard-hitting reviews than were we. Second, we were getting miffed that companies weren't sending neat toys (free of charge) to our offices. Third, it seemed like a good way to get paid for breaking stuff.

#### No Dweebs Here

At Circuit Cellar INK, when we decide to do something, we don't go in for half-measures. Before we opened the CCINK BPE&JFCTF, we performed an exhaustive study of what "the other guys" were doing. What did we find? Wimpy softwarebenchmarks and effete instrumentation, that's what! Where were the calisthenics for individual instructions, the particle accelerators, the blast craters? They were not to be found, at least not until now.