#

THE COMPUTER APPLICATIONS JOURNAL

\$3.9

**PUBLISHER** Daniel Rodrigues

> **EDITORIAL** DIRFCTOR Steve Ciarcia

EDITOR-in-CHIEF Curtis Franklin, Jr.

> **TECHNICAL EDITORS** Ken Davidson Jeff Bachiochi

CONTRIBUTING **EDITORS** Thomas Cantrell Edward Nisley

**CONSULTING EDITOR** Harv Weiner

**CIRCULATION** DIRECTOR Jeannette Dojan

CIRCULATION **CONSULTANT** Gregory Spitzfaden

**PRODUCTION MANAGER** Tricia Dziedzinski

> **BUSINESS MANAGER** John Hayes

**STAFF** RESEARCHERS

Northeast Eric Albert William Curlew Richard Sawver Robert Stek Midwest John Elson Tim McDonough West Coast Frank Kuechmann Mark Voorhees

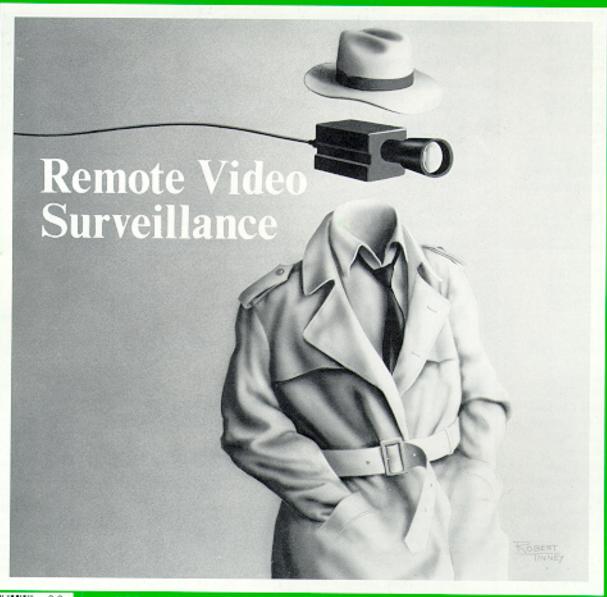

Cover Illustration by Robert Tinney

## Circuit Ciri

THE COMPUTER APPLICATIONS JOURNAL

#### **FEATURES**

- **ROVER** Remotely Operated Video-based Electronic Reconnaissance by Steve Ciarcia & Ken Davidson

- The Satellite Home Weather Center -- Part 5 Focus on the MC68000 Peripheral Controller by Mark Voorhees

- 10-MHz/8-bit Digitizing Board for the IBM PC An Affordable Digital Oscilloscope on a Plug-in by Russell Lindgren

#### DEPARTMENTS

Conducted by Ken Davidson

| Editor's Ink                                                                                                    |           |

|-----------------------------------------------------------------------------------------------------------------|-----------|

| Not the Same Old Song by Curtis Franklin, Jr.                                                                   | 1         |

| Reader's Ink - Letters to the Editor                                                                            | 2         |

| Visible Ink - Letters to the CCINK Research Staff                                                               | 14        |

| From the Bench RS-232 Economic Tradeoffs Conducted by Jeff Bachiochi                                            | 24        |

| Update: Additional information to previous articles                                                             |           |

| The X-10 TW523 Two-Way Power Line Interface A step toward closed-loop power line control by Ken Davidson        | 34        |

| The DDT-51 Lives - Fixes, Updates, and Future Pl for the Low-Cost 8051 Development System by Ink Research Staff | ans<br>38 |

| ConnecTime - Excerpts from the Circuit Cellar BBS Conducted by Ken Davidson                                     | 40        |

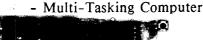

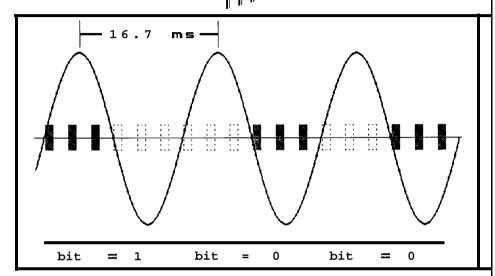

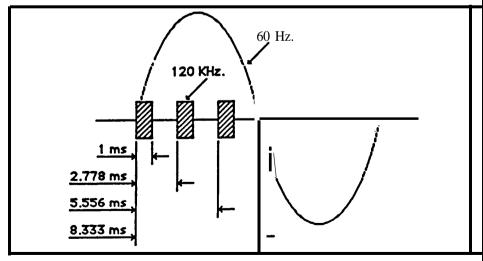

Firmware Furnace Precision Pulses - Carrier-Current Transmission Timing by Ed Nisley

Steve's Own Ink Back Here by Steve Ciarcia 52

Circuit Cellar BBS - 24 Hrs. 300/1200/2400 bps, 8 bits, no parity, 1 stop bit,

The schematics provided in Circuit Cellar INK are drawn using Schema from Omation Inc. All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure that their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of the possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK.

Entire contents copyright 1988 by Circuit Cellar Incorporated. All rights reserved. Reproductions of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

page 4

page 17

CIRCUIT CELLAR INK (ISSN 0896-8985) is published bimonthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203-875-2751). Second-class postage paid at Vernon, CT and additional control of the control ditional offices. One year (6 issues) charter subscription rate U.S.A. and possessions \$14.95, Canada \$17.95, all other countries \$26.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders to Circuit Cellar INK, Subscriptions, 12 Depot Sq., Peterborough, NH 03458-9909 or call (203) 875-2199 POSTMASTER: Please send

address changes to Circuit Cellar INK, Circulation Dept., 12 Depot Square, Peterborough, NH 03458-9909.

# EDIORSI N K

# Not the Same Old Song

hen you design and create for a living -- whether it's process control applications, scientific applications software, commercial products, or magazines -- there is always the great temptation to fall back on tried and true formulas rather than look for truly innovative solutions. Deadline and budget pressures build up, creative frustration mounts, and before you know it you're singing "Why reinvent the wheel" instead of "I did it my way."

Now, don't get me wrong. There are many times when a proven solution is just the ticket for a particular problem. It's just sad to see people move from creative problem solving to rote formula recitation. We're not going to let that happen here at Circuit Cellar INK, and we're going to do our best not to let it happen to you.

This month, you'll notice that some of our articles (check out "ROVER") look a little different. We think that the new captions and layouts will help you get into the article a little more easily. In coming issues, you'll see some other differences, all of them aimed at making Circuit Cellar INK not only useful, but enjoyable.

You'll also notice the ads for our two new services. Many of you have told us that you would like to get the software mentioned in Circuit Cellar INK articles, but you can't log onto the Circuit Cellar BBS. Now, you can order all of the software for a particular issue on the Software Disk for the issue. Speaking of the BBS, if you can't log on, but you still want to get the solid information that's posted every day, now you can order the Circuit Cellar BBS On Disk, two months' worth of BBS messages on IBM PC disks. Both of these new services will get more information into your hands faster than ever before.

We're going to keep you on track by giving you articles that have solid, practical design information wrapped in a package that will let you look at problems from a fresh perspective. As an example, Steve's at his best with his latest project, beginning on page 4. Sure, other magazines could tell you how to build the hardware, but how many others can give you the itch to go out and do something creative *right now?*

It all boils down to just how good you want to be. Using the proven solution is fine now and then, but relying on the old and true too often leads to a complacent slide into mediocrity. If you want to be the best, then, it calls for striking out into new ways of thinking about problems, designs, and solutions. That's where you want to be, and you can count on us to be there with you, educating, stimulating, and entertaining.

Curtis Franklin, Jr. *Editor-in-Chief*

## I N K

#### Letters to the Editor

While looking forward to an article on the subject of autonomy and power supplies, I am dropping you word of what one user is getting by with and adding a word of thanks for your articles.

I live in an area which is sparsely populated, hilly, and subject to thunderstorms, the consequence being that long stretches of main distribution lines are exposed to every passing lightning flash. The protection system (for the electricity corporation's property) is very good, and it cuts out quickly and often. Some form of autonomous supply was necessary, especially after one motherboard received something up its parity chips, this from an unlucky lightning strike which arrived without any warning whatsoever.

Not being attracted to the idea of buying a machine to convert the main down to 12 volts, store it, and then convert it back up again, I decided to run my PC and an earlier TRS-80 directly off car batteries. The PC, of course, draws too much current for unassisted car batteries, so I ended up running off of battery chargers with large capacitances (in the form of batteries) attached.

Though I was hesitant at first, the system works well; I can leave it on all day without problems, which suggests that the power coming out is reasonably clean. Of course this system gives me no protection from either internal or external faults, but the savings are sufficient, compared to the price of a new motherboard, to get away without this protection. The actual cost of the system was little more than the PC power supply I didn't buy. With an AT or larger machine, this will no longer be true. I presume, though, that a wellprotected and -regulated battery supply is a costly item. I am resigned to stopping work and disconnecting the mains when there is lightning in the offing. Having seen the state of the pair of MOVs which took the brunt of another stroke of lightning, I need some convincing that there is a really effective, sure obstacle that will bar lightning from reaching into those flimsy chips. I have wired in a pair of devices I found at Radio Shack

labeled "field effect overvoltage protectors, DSAR 1 701 MA, part no. 270-9811, reaction time 1 microsecond" but I have no idea what they are worth.

I have wired in an automatic voltage-sensing relay which cuts off the chargers when the main battery reaches full voltage an hour or two after turning the system off.

This is not a letter that requires a reply, it just thanks you for your inexhaustible supply of good ideas and practical, viable projects. I just regret that I cannot build more of them and that I do not live within reasonable reach of the Circuit Cellar BBS.

John Negus--Bessas, France

Lightning and power outages are subjects near and dear to our hearts here at CCINK, and we're looking at some future projects that might be effective weapons in the war against blown-up equipment. We'd like to hear from any of our readers who have come up with creative solutions to power outages, line garbage, and lightning strikes.

--Editor

Sure, I'd like to subscribe to Circuit Cellar INK! I have one request to make, though: Could you occasionally expand your magazine by a page or two to discuss a uniquely neat piece of hardware you've included in a project but haven't discussed in the article?

A specific example might be the Shugart SA-300 single-sided **3.5-inch** disk drive installed in the SB180 "computer in a lunchbox" article in the October 1985 issue of BYTE. I think that this would be a great drive for the experimenter to start out with. Unfortunately,

Shugart is no longer in business and, while **Con**-sumertronics' Disk Drive Tutorials give some clues for adjusting drives, they don't mention anything about the shorting pins used to configure them.

Maybe you (or your readers) can help.

Les Wenninger--Hubbards, Nova Scotia

We have a couple of ways to tell readers about "neat hardware" used in a project but not fully described in the article: Updates, such as the bottle rocket launcher in the July/August issue and, beginning in this issue, "From the Bench," conducted by Jeff Bachiochi. Jeff will be presenting practical advice on device selection and a number of interesting "small" circuits in the coming months. He'd like to hear from readers about what they want to see him cover. Technical questions should be addressed to Visible INK. We've turned your question on the Shugart drive over to the Circuit Cellar INK Research Staff.

--Editor

Republic Committee of the Committee of t

First, I'm writing to congratulate you on a fine magazine. The diversity and quality of articles is first-rate. I'm glad that you have included articles about trends in technology as well as projects and tutorials. I especially enjoyed the article on RISC vs CISC. It was the first article I had read that said something other than RISC is be-all and end-all of the future in computer design. I also really enjoy your editorials which have put into print feelings that I have had for a long time. Keep up the good work!

Second, I would like to reply to Mr. Dodge who wrote about displaying weather facsimile data by shortwave radio. Amateur radio operators have been doing this for some time. There are several products on the market which will receive FAX and RTTY and send the data to a computer via RS-232. These are listed below. All will receive both FAX and RTTY as well as packet radio. The MFJ interface will translate FAX data into an Epson-compatible graphics file that can be dumped to any Epson-compatible printer. Any good terminal program for the Amiga, such as Online!, VT100, or Comml.4 can be used to control the interface. I do not know of any commercial software that would convert these files to display on the Amiga

screen, however the American Radio Relay League (ARRL) maintains a program exchange which may have some programs that can help. The format of Epson graphics files should not be hard to obtain, and using the capabilities of Amiga BASIC it should not be difficult to write a program to translate that file into something that can be displayed on the screen.

I hope this gives him something to start with. Once again, thanks for a great magazine.

Roy G. Clay III--New Orleans, LA

P.S. This letter is being prepared on an Amiga 2000. Hope to have some projects for the Amiga soon.

Thanks for the information on weather FAX. We share your hopes for some Amiga projects soon, and are also working on having Macintosh (including Mac II), Atari ST, and S-100 projects, as well as a continuing stream of projects that are built around stand-alone processors. Circuit Cellar INK is not biased for or against any computer system or processor, but we can't run articles we can't find. If anyone has put together applications for a system that they haven't yet seen in the pages of INK, they should call or write Curtis Franklin.

--Editor

#### Weather FAX Interfaces:

MFJ-1278 MFJ Enterprises, Inc. P.O. Box 494 Miss. State, MS 39762 (601) 323-5869

PK-232 Advanced Electronic Applications P.O. Box C- 1260 Lynnwood, WA 98036 (206) 775-7373

HK-232 Heath Company P.O. Box 1288 Benton Harbor, MI 49022

## **ROVER**

## Remotely Operated Video-based Electronic Reconnaissance

by Steve Ciarcia & Ken Davidson

looked around the corner and peered through the doorway of the official-looking office. The walls were decorated haphazardly with town maps and site plans, some of which I recognized as years old. It was as if new layers of paper, like new generations of people, simply built upon the remnants of the past.

I always thought that death and taxes were the only undesirable things in life that were inevitable, but I've found a third -- local government bureaucracy. Unfortunately, it's practically impossible to live your entire life and not interact with government officials. Believe me, I tried! I use the mail for practically everything: dog licenses, permits, requests, and payments. Never before had I darkened the doorway of city hall, and never had I felt I was missing anything.

There were two desks in the room but only one was occupied. The unoccupied desk was piled high with a mountain of rolled and folded building plans. Considering the frictional variabilities, interlocking all this tubular and flat surface material into a semistable configuration was a stupendous engineering feat. The desk abutted the age-stained wall, and the pile sloped down in a straight line from a precarious height to the outer edge. It appeared that just one more site plan would bring the entire town architectural history down in a tremendous avalanche. I looked at the tightly rolled site plan in my hand and wondered, small towns being what there were, if I'd be remembered as "the one who upset the pile."

I'll never know why New England towns can't have air conditioned city halls. I'm sure that since most claimed to have been built around the time of the Mayflower, adding such amenities would deface the cultural significance of the structure. The people who worked in these buildings, as a result, were hardened pros. Like heat treating metal where you cycle the temperature often and to extreme limits, these New England city hall employees were a hard bunch. Hard to like, hard to take, and hard to satisfy.

In any case, here I was in a hallway that was about 98 degrees, standing in line waiting to get a building permit. The only consolation I had was that I was next in line and there were at least fifteen uncomfortable people behind me.

It was interesting to note a certain synchronization in mass body language. As if on cue, one group, which had been leaning against the wall on one leg, would shift to the other leg. At the same time, another group would cough, shuffle, or wipe their brows. For over an hour I observed this almost programmed pattern of shuffle, shuffle, lean right, lean left, sneeze and wipe. The only break in the pattern was when the line moved forward and two half-step shuffles were added.

It seemed like the previous person to enter the building inspector's office was taking an inordinately

long time. To alleviate the tension of waiting I swopped a few jokes with some of the others in line and nervously added, "What's the guy in front of us trying to do, build a hundredunit condo?" A few of the more conservative town residents in the line immediately jumped to attention at hearing the word "condo" but I quickly waved my hand, "No! No! Just kidding, guys! No condos, here. Just joking." Still smarting a bit from coming so close to being lynched, I whispered to the person behind me, "What is this guy doing that takes so long? Here I am next in line and he's been in there almost an hour already."

The lady turned around, smiled like she knew she was dealing with a tenderfoot, and chuckled, "Oh nothing special. I think he just wants to put up a garage." Suddenly I had a very hollow sensation and I could feel a cold sweat coming on. She chuckled and continued, "Do you remember going to the DMV to get a car registered? Well, this place is like that. It takes about six trips just to figure out what paperwork is required. Unfortunately," she smiled, "it's a little hard to drag in a parcel of land or a building when there's some question about the way it looks!"

sweaty palms were undoubtedly

smearing all the carefully inked details of my new garage on the plot plan that I clenched tightly. I leaned back against the wall and closed my eyes. What had I gotten myself into? I was shocked back to reality with the loud call, "Next! Anyone out there? Next!" The woman behind me pushed me toward a Dutch door. As I opened the bottom half to enter the building inspector's office, the resident who had been in there for the past hour brushed past me, muttering loudly to himself, "Can't build a damned doghouse in this town without everybody's fingers in it!"

These were hardly words to inspire confidence but I entered the office, carefully avoided disturbing "Mount Paper Pile," and sat down in the chair next to the inspector's desk. I passed him the crumpled paperwork which detailed my project.

The inspector was about 45 years old with slightly graying hair and medium build; average in every way. He was dressed in a white shirt and brown trousers. both with areas shiny from extended contact with a desk chair. Scanning down from a tie that contained most of a week's menu, I noticed his heavily soiled shoes. Obviously this man did field work as well. I was beginning to hypothesize about his health and family situation when he looked up from studying the site plan and interrupted me. "Mr. Ciarcia. should I presume from this that you are building another house next to the present one? You know we can't let you do that!"

"No, no, Mr. Wright. That is the plan for a four-car garage. It just happens to be as big as a house."

It was sacrilege giving this job to anyone with a name sounding like "right." Admittedly I was better at drawing electronic sche-

Introducing ZIP, software for **ImageWise** control, image processing, and outstanding display of video images on EGA/VGA

KINGTUT displayed at 640 x 460 on EEGA

Superior EGA/VGA displays 3 levels of zoom Color/gray level displays 64 level ordered dithers Minimum error techniques Halftones and duotones

Process single + multiple images Math and logic functions Matrix convolution Histo equalization/linearization Square aspect ratio Pixellation, and more

Supports ImageWise digitizer Transmitter and receiver Use 1 or 2 serial ports Process 3 images at a time Combine images

Saves Images for desktop publishing Saves in PCX and MAC file formats

ZIP price: \$79 plus \$2 s/h Missouriresidents add 5.6%. check/VISA/MC

470 BELLEVIEW ST LOUIS MO 63119

\* call for information • \*

matics than detailing the location and dimensions of a garage on a realestate site plan. In the same breath I continued, "I've had about 40 truckloads of fill brought in, the hole for the foundation is dug, and the lumber has been delivered. All I need now, according to my carpenter, is for you to sign off on this building permit so that we can lay the forms and start building! We could start this afternoon!"

He looked up at me. I caught a glint in his eye as he ignored what I had said. Instead, in an expression of power which he obviously relished, he extended his forefinger and sharply jabbed at the drawing. "If you meet all the requirements I'll grant you a permit, but not until. The regulations are very straightforward but you'd be surprised how many people come in here and try to put one over on me. What's this?"

I answered automatically, "That's an existing two-car garage."

It was like a bell went off. He sat up quickly and questioned in an official-like manner, "Six cars?"

I'm sure he felt he had to protect the community from people who start automobile junkyards in the neighborhood but this was hardly the case. The Circuit Cellar was getting pretty full and I needed some place to put a real workshop and transfer some of the junk. As I prepared to defend my actions, I suddenly thought better of it. If this guy was upset about six cars, what's he going to do when he found out we're really talking about eight? He hadn't discovered the **two**car garage in the house yet and I was sure not going to tell him ...

Fortunately he didn't wait for that answer. Instead he continued, "You have to be 25 feet from the property line. This looks much too close on your site plan. And what's down here in this area?"

I leaned forward to see where he was pointing and replied, "Oh, it's at least 25 feet. Take my word for it. Besides," I chuckled, "I own the land

on the other side of that property line too." I smiled while thinking "gotcha."

"Makes no difference how much land you own, Mr. Ciarcia. Since that other piece of land is legally separate, if you are closer than 25 feet you'll have to go before the zoning board and petition for a variance. The next available slot in their agenda is in about three months, I think ... or, was it four? Before we worry any more about that, however, what's over here?" He pointed to the same area he previously designated.

I chuckled nervously, hoping that we could forget about zoning board meetings. "It's a swamp or something like that ... but, don't worry. I won't try to build a garage on it."

"Darn tootin' you won't!" he voiced authoritatively. "That would be wetlands and you can't build closer than 100 feet from wetlands without going before the wetlands commission and then the zoning board of appeals. The dimensions indicated in your site plan aren't clear and unless I have concrete evidence that you comply with zoning regulations I will have to deny your permit!\*'

My world came crashing down. The simple task of building a little garage was taking on monstrous proportions. "But ... but ... that swamp is at least 200 feet away and, while it isn't indicated on the plan, it's another 100 feet down a hill as well as 200 feet away!" I implored vigorously. "Trust me! It's far away!"

"I think the solution is for you to have a professional survey done of the property that clearly marks the location of the new building. I appreciate that you have already dug for the foundation, but unless I have personal knowledge that your building location is proper or you have an official survey map which indicates same, I have to

deny your permit."

He was about to yell "Next!" when I feverishly said, "All you have to do is come out and see the garage site! You'll see that all my dimensions are in order and that any wetlands are way off." That seemed reasonable to me, and the least a public servant could do.

"Sorry, but unless you have a

building permit, I am not authorized to visit the building site," he stated matter-of-factly. I was depressed. If he saw that everything was copacetic, I could get a permit. But without a permit he couldn't go see it, right?

Suddenly, I jumped up and yelled, "Wait, Mr. Wright, I've got the perfect answer! ROVER is in my car!" I

bolted for the door before he could answer. I knew if I waited for his reply it would have been "Next!" and I'd be at the end of the line. I heard him yell, "What the hell has a dog got to do with ..."

I didn't hear the rest as I rushed past the line of people and dashed for my car. Fortunately, New England town halls are small and the car was parked only a few hundred feet from the building inspector's office. Before he could challenge this obvious miscarriage of protocol, I was back in his office panting from exhaustion.

In my hand was a box that looked like a portable computer. The inspector seemed surprised, but not shocked. Apparently, modern technology was within his scope of understanding and I wouldn't have to be concerned about being

burned as a witch for what I was about to demonstrate. I plopped the box on top of a pile of site plans on the corner of his desk, disconnected the phone line from his telephone and plugged it into the unit. He was used to people piling paper in his office, but not messing with his desk or phone. He jumped up and remarked loudly, "I really don't have time for

Walking down the driveway to my house was an alien!

this right now! What is this thing anyway? Is it dangerous?"

As I flipped on the power and pressed "CALL A," I answered, "This is ROVER! ... Remotely Operated Video-based Electronic Reconnaissance! Think of ROVER as a spy in the sky that's dedicated to my house." I had his attention but immediately knew from his expression that "spy" was not a word I should have used.

"ROVER is an electronic device that communicates with a video camera at my house. Using ROVER I can show you on a video screen exactly where the new garage will go and where the boundaries in question are. You won't have to visit my house, I'll bring it to you live and in black and white." (I wish I could have said "live and in color." I was really on a roll).

I continued describing ROVER, explaining how it used the telephone line to transmit digitized video and that the pictures we were viewing were snapshots of the real-time activity at my house. I pointed the camera at the house

and oriented him to the location on the site plan. Eventually I panned the camera to a position where he could see both the foundation hole that had been dug and the stone boundary wall which marked the property line. To my amazement, he agreed that the new garage did indeed "appear" to be considerably more that 25 feet

from the wall. As skeptical as Mr. Wright had initially appeared, he recognized that ROVER was indeed filling in some blanks in my permit application. I won't say that he wanted one installed in city hall, but his was obviously a case where once he got over using a laser transit he wasn't surprised to see anything.

I was patting myself on the back for this coup over the bureaucracy as town employees from the fire department, EPA, and department of public works entered the building inspector's office to see why their shared partyline phone suddenly sounded like a lot of static. Soon, even these three were mesmerized by ROVER, The concept of viewing a physical work site without having to leave their desk appealed to them.

1

After a while I didn't even have operate ROVER as one of the faster learners among them took over the controls continued panning, tilting, zooming and around my property. I smiled as I watched the four men leaning over and intently watching the video display. Suddenly one of them yelled, "Hey, what was that!? Something

The suited figure on my deck was bending forward and holding something that looked like a gun.

moved! Pan back over there."

I peered over the top of the huddled group to see what had attracted their attention. ROVER was still painting a high-resolution picture on the display so I offered a plausible explanation. "Gentlemen, ROVER was designed for security applications and I am trying to get a building put up. With your help of course.\* I motioned toward the building inspector. "Perhaps one of the carpenters has arrived."

ROVER had finished sending the image, and walking down my driveway toward the house was an alien! Or should I say a humanoid that looked like an alien! Well, something in a space suit anyway. They looked at me; I looked at them; and we all looked back at ROVER which was now painting another closer image. I, too, was curious and joined the crush to view the latest picture.

In full view was a person who looked like he was wearing a white space suit! I mean, it had a helmet, air hoses, and all the stuff that made it look like something from NASA. I said, almost jokingly, "A guy in a space suit at my house?"

"Turn the camera and follow

that guy some more!" the EPA official ordered in unison with the fire department guy. "That's no space suit! That's an environmental hazard suit! We use those when we inspect hazardous waste dumps!"

The next picture showed the suited form on my deck bending forward and holding something that look like a gun. The EPA guy continued in an agitated voice, "Those are spraying tanks he's wearing. Whatever he's spraying that requires that kind of suit is bad news. I presume you have a permit for whatever this is, Mr. Ciarcia?"

"Really, sir. I haven't the slightest idea what is going on! I don't know what that person is doing! No, I haven't got a permit!"

"No permit to spray toxic compounds? Do you realize what kind of trouble you're in if any of that is found to be polluting the neighborhood, Mr. Ciarcia!?"

Truly I didn't know what was going on. I just sat there dumbfounded and emotionally ex-

hausted as the next picture was painted on ROVER's screen.

This time the suited man was standing next to a truck that I instantly recognized. Suddenly everything clicked into place. I exclaimed, "That's Bob Borg! He's a friend of mine!"

"This is all a joke! I know what he's doing now! Oh boy, Bob, you really had me

going for a while there." I nervously voiced the latter at ROVER's screen as if to talk directly to the suited man. The four town officials looked at me strangely.

One of them said, "I thought you didn't know who that was using toxic chemicals on your property?"

"It's Bob Borg! He's playing a joke!"

"It looks like he's spraying toxic chemicals, Mr. Ciarcia. There's nothing here to joke about that I can see," was the sarcastic reply.

"No, no. He's not spraying anything! He's just posing for my alarm system!" You couldn't believe how ridiculous such a statement sounded, but I was frantically trying to explain my way out of a predicament.

Continuing, "Bob knows I have a security system with video cameras and a VCR. The last time he was at my house killing some ants when I was away, I sent him a picture showing him that I 'caught' him creeping around my house. He laughed and said that one day he'd visit my house again and really shake things up."

"So you admit, Mr. Ciarcia, that this man is here spreading toxic chemicals with your complete knowledge and authority!? And further, vou're obviously doing this in violation of the law?"

These guys weren't listening and I wasn't making any headway. Again I implored, "It's a joke. Bob is a friend who's just playing a joke on me. It was all a dare!" Without voicing it, I thought to myself that Bob was a friend all right, but I'd strangle the SOB later for his poor choice of timing.

"Get a load of this!" The EPA guy called the others to look at ROVER which was in the process of displaying the contents of Bob's truck. "Whoever this guy is he ain't carrying cord wood back there."

"I told you his name is Bob." I was interrupted abruptly by the fire official who was communicating with someone outside the office via a walkie-talkie attached to his belt.

The fireman interjected loudly. "I ran a make on the truck license plate through the state police. His

name is Bob Borg. He's some kind of special exterminator that they call for the really 'bad bugs'! Sounds like we're dealing with character who has access to all kinds of nasty stuff. However, if we're dealing with only a single truckload of chemicals that aren't too toxic, perhaps the pollution threat

won't have to involve the state boys."

"I wouldn't count on that if I were you. Every time we nail one of these waste dumpers, it turns out they've just buried about 50 drums of chemicals under a pile of landfill, or they try to build a building or a garage over it," the EPA official added.

They talked among themselves as if I weren't there and continued to study the pictures from ROVER until the EPA person again said, "Oh, oh. Get a load of this. There's a big gas bottle on the back of the truck with a poison label. The only gas bottle I know of that warrants such a bold notice is Trichloro-Dimethyl-Benzimidanide or Tetrachlorosobromide. Both are so toxic that we're probably going to have to dip into the Superfund to clean up this mess."

"OK, guys. It's my opinion that we declare a class-one alert and get our people over there right now! Obviously Mr. Ciarcia and his friend Borg have been disposing of chemicals for some time now and we were fortunate enough to uncover their activities."

"But, but, I tell you it's a joke."

telephone.

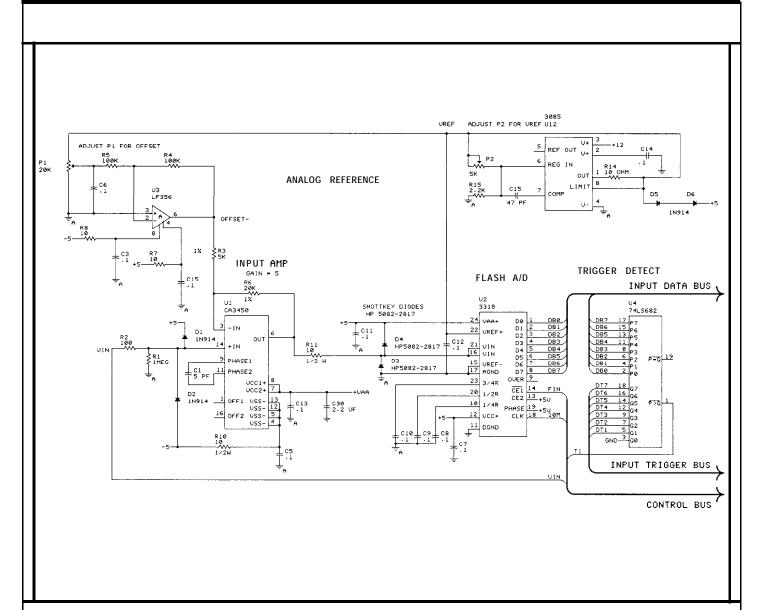

via modem to a receiver. ROVER is more than a straight video link, however. The transmitter portion of ROVER is a complete microcomputer-based data acquisition and control system. Rather than simple fixed-focus camera, video is provided by a lowlight-level autoiris CCD camera with motorized pan, tilt, zoom, and focus. Camera position. zoom, and so

by discrete contact closure outputs which are controlled from the re-

'Whoever this guy is, he ain't carrying cordwood bock there."

I cried out as two constables entered the room and asked that I go with them. "I just wanted to build a garage ..."

As ROVER and I were being led away past the intensely curious crowd, the building inspector stuck his head out the door and yelled, "Permit denied! Try and put one over on me will ya!"

ROVER stands for Remotely Operated Video-based Electronic Reconnaissance (we would have called it "BIG BROTHER" but we couldn't think of an appropriate expansion of the acronym). ROVER is an electronic surveillance system which allows digitized video pictures and pertinent status information to be transmitted and viewed anywhere in the world via

Similar in concept to a video telephone which has a separate video transmitter and display receiver, ROVER has a video camera which transmits a digitized picture

on, are controlled

ceiving end. Similarly, ROVER passes discrete input data from various contact closures and switches to the receiver.

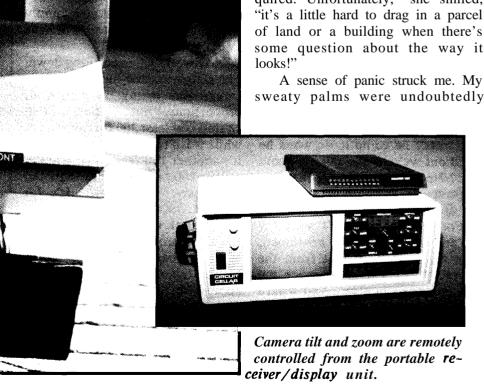

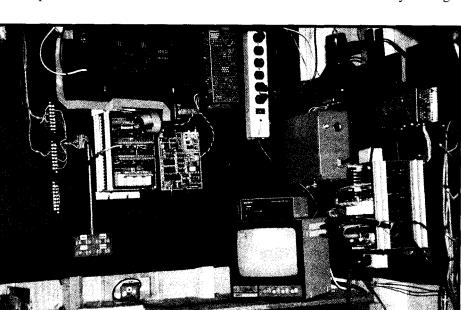

The ROVER receiver/display unit looks like a small suitcase computer and is designed to be portable. The receiver contains a 9600-bps modem and a digitized video display board connected to a controlling single-board computer.

An array of switches initiates the telephone call to the transmitter, controls the various camera attributes, and sets the receiver's display resolution.

When I want to check the house for any reason, I merely plug ROVER into the phone line and turn it on. After initialization, I press "Call A" and the ROVER

receiver (on my

desk) autodials the ROVER video transmitter (on the garage roof at my house) and starts painting a picture of what it "sees" on the screen. The camera position is changed by pressing the various pan, tilt, and zoom buttons. Pictures are displayed every 5 to 50 seconds (at 9600 bps) depending upon the resolution selected.

Since my house is a local telephone call from my office at CC INK, I often leave ROVER on all day, providing a real-time view of events in my driveway. I have watched the UPS truck back over the shrubbery and salesmen looking in the windows trying to find the "lady of the house" (they really do a double-take when they notice the camera "following\*' them).

Regardless of my humorous use, ROVER is real and it is off-the-shelf. The basic ingredients of ROVER are the ImageWise serial grayscale video digitizer/display system and the HD64180-based BCCi80 control computer. Both of these units were presented as Ciarcia's Circuit Cellar projects (see source box at conclusion) and are fully documented designs which can

users. ROVER, at that point, just involved plugging in a couple of new ROMs, slapping on a camera, a few switches, and specialized software. Of course, getting from here (with off-the-shelf hardware) to there (configuring it into ROVER) is what this article is all about.

Regional State of the State of

Building a portable ROVER receiver consisted of putting a BCC180 and an ImageWise receiver/display into a surplus transportable computer case and gluing a USRobotics Courier HST modem to the outside.

be easily built from the article descriptions and reader-support software on the Circuit Cellar BBS (they are also available as kits or assembled units).

I refer you to these original articles for video basics and the hardware architecture of ImageWise and the BCC180. To build ROVER, Ken and I approached it as if we simply took a pair of ImageWise DT01/DR01 boards and a couple BCC180s and did a project as end

The Image-Wise system consists of two parts: the digitizer/ transmitter (DT01) and the receiver/display (DR01). The digitizer portion accepts a standard NTSC video input, digitizes a picture in 1/60th of a second at a resolution of 256x244 pixels with 64 levels of gray, and sends out the digitized picture serially

over a standard RS-232 connection. The display board has an RS-232 serial input through which digitized picture information enters the board. The board then stores that picture information in its on-board memory and recreates a standard NTSC video output signal at the same resolution of 256x244 pixels and 64 levels of gray.

The **ImageWise** boards are designed to work together with no outside help. The display board sends a picture request to the digitizer and the digitizer obliges with a picture. Switch settings on the display board allow the operator to select one of three different resolutions (256x244, 128x 122, and 64x61) and the time between pictures (continuous, 4 seconds, 8 **sec**-

onds, or on the push of a button).

The ImageWise system was designed with remote surveillance in mind. The serial ports on both the digitizer/transmitter and receiver/display are set up in a DTE configuration so each can be plugged directly into a modem. While neither end has the necessary software support to dial a modem, neither end needs a host computer to

be used in a standalone, free-running fashion.

The beauty of the system, however, stems from the serial interface used by both boards. Rather than connect the boards directly together, it's very easy to connect them to a host computer. The host computer can then request a picture from the digitizer and save it in main memory or a file. The picture

can be manipulated, modified, and saved on the host computer. When the operator wants to see the picture at some later time, he can send it out through the host computer's serial port to the display board and get an exact duplicate of the original.

As mentioned before, it's a relatively straightforward task to connect the **ImageWise** boards to modems and communicate pictures between the two boards without outside help. Such help is only needed when dialing the originating modem (most Hayes-type modems will automatically answer the phone on the answer side of the connection). However, when laying out the specifications and features of ROVER, we wanted to be able to do more than just make a

connection by hand and see **fixed**-resolution pictures from a stationary camera. We wanted to be able to move the camera around, zoom in and out, turn a targeting laser on and off (just wait for that article!), and receive status information back from my existing home control alarm system. In addition, we wanted a choice of resolutions so we could trade off transmission time with resolution **de**-

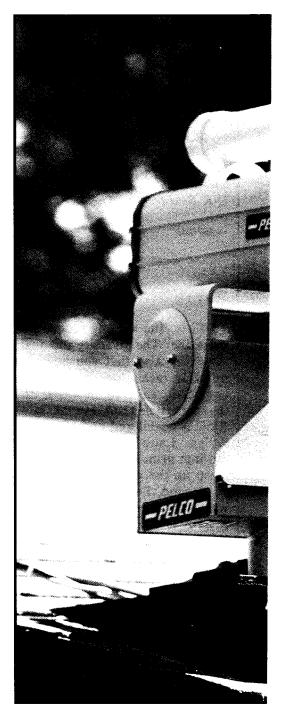

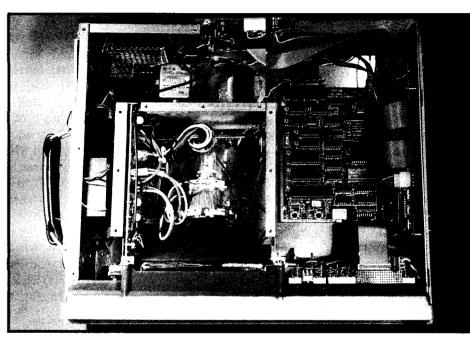

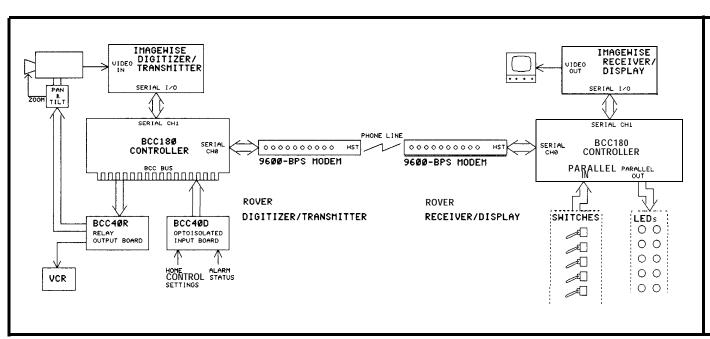

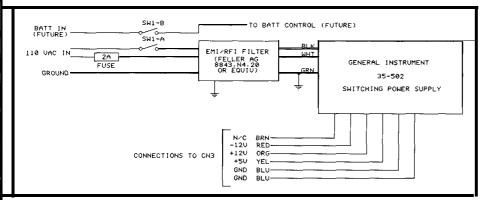

The ROVER transmitter consists of a camera (see opening photograph), USRobotics Courier HST, ImageWise digitizer, and BCC180 computer with relay output and optoisolated I/O expansion boards.

pending on the situation.

The BCC180 turned out to be ideally suited to the task. (While the BCC52 is relatively inexpensive and has enough speed to handle the role of "picture traffic cop," it lacks a second full-duplex serial port and requires an expansion board to get more than 48K of memory.) The BCC180 has two full-duplex serial ports, 128K of EPROM or static RAM for

program storage, plus 256K of dynamic RAM for picture storage and manipulation. In addition, it has six 8-bit parallel ports for use as switch and contact-closure inputs or indicator and relay outputs. Finally, it can be plugged into a backplane so expansion boards containing relays and optoisolators can be easily added.

As you might already know, I

have had more equipment blown up by lightning than you can shake a lightning rod at. If you saw my article in issue #1 of INK ("Motion-Triggered Video Camera Multiplexer"), you know to what lengths I'll go to isolate discrete inputs and outputs so transients caused by lightning only affect isolated

portions of the system. On the digitizer end of ROVER, I wanted to have various inputs to the system that indicated when the house alarm was on, the HCS was active, plus the states of various contact closures. For outputs, I needed to be able to control the power to the pan, tilt, and zoom motors and be able to turn the laser and VCR on and off.

I could very easily have connected all these inputs and outputs directly to the BCC 180's parallel ports (drive transistors for the outputs and clamping diodes for the inputs), but that wouldn't have provided sufficient protection as far as I'm concerned. Instead, we designed ROVER more along the lines of an industrial control system.

"igure 1 - ROVER is a system that allows digitized video and status information to be transmitted anywhere in the world via telephone.

1001 美祖4、198

Figure 1 is a detailed block diaram of the ROVER system. The igitizer/transmitter portion of **COVER** is mounted on the wall in he garage directly under the pan/ ilt camera unit pictured in the pening photograph, and the reeiver/display unit is a portable nit resembling a Compaq comuter.

The ROVER transmitter con-Courier HST modem, ImageWise iigitizer, and BCC180 control omputer with relay output and ptoisolated I/O expansion boards. As I previously mentioned, no toiris motorized zoom lens. omputer or expansion boards are equired for a ROVER transmitter onfigured for auto answer/fixedamera operation). The BCC40R elay output board controls the 24-**IAC** power to the motorized pan nd tilt and +5V/-5V to the camera ocus and zoom.

The Pelco PT 175-24P allveather pan and tilt uses separate

connections for each control input: pan left, pan right, tilt up, and tilt down. To pan or tilt the camera, we momentarily close the appropriate relay (for the amount of time the switch is pressed on ROVER's receiver) which applies 24 VAC to the winding. By making these connections through DPDT relays that "break before make," we can also physically guarantee that the computer can't accidentally energize opposing directions at the same time. ists of a camera, USRobotics Compound motion such as down and right or up and left are possible, however.

> The camera I used is a Sony SSC-D5 with a Cosmicar SCL 0813 AI authough the camera is CCD and not susceptible to image burn-in if accidently focused on bright lights, an iris is necessary to optimize the exposure for a given lighting condition. The iris fuction is automatic while the 12.5mm-to-75mm zoom lens and focus controls are "manual." the home control system, AC Unlike the pan/tilt, however, this unit relies on changing polarity on a

single control line rather than providing pairs of separate function lines. Applying +5V to each control line zooms or focuses "out" and -**5V** zooms or focuses "in." In addition to the camera controls, relay outputs are provided to turn on a video tape recorder (recording everything from the camera rather than just the digitized snapshots) and a laser. While I haven't quite decided what to do with the laser, it's there. It is the thing that looks like a sighting scope mounted to the top of the camera housing.

Much of the added complexity of my ROVER configuration is due to its full-duplex data transfer. In addition to the relay board for the camera controls, ROVER utilizes a **BCC40D** optoisolated I/O board to monitor various 12-VDC and 115-VAC signal inputs and light the corresponding indicators on ROVER's receiver. Presently these signals consist of status bits from power, and house alarm systems. Because of the line lengths and

voltages involved, optoisolated inputs were mandatory.

The ROVER receiver/display is a transportable unit with built-in video monitor. The case, without CPU board but with a nice 6" 12-VDC composite video monitor and power supply, was purchased (dirt cheap) at the Trenton Computer Festival. It was originally intended for a portable Apple clone from Franklin Computer which was never marketed in volume. Perhaps one reason is the overly expensive but ultimately beneficial construction. To meet FCC emission rules, there is a metal "Faraday cage" shell inside the attractive plastic enclosure. All the electronics built inside this shell are protected from causing as well as receiving electrical interference from other equipment. My "prototype" ROVER probably has better EM1 characteristics than many commerical computers as a result.

Building a portable ROVER receiver into this case merely consisted of jamming in a BCC180 board and an ImageWise receiver/display. To make room for all this odd-shaped hardware, I eliminated some of the existing partitions and substituted a smaller power supply. The Courier HST modem was "velcroed" to the top cover.

The only laborious task was constructing the front panel and indicator lights. All these switch inputs and LED outputs were connected to the BCC180's six onboard parallel I/O ports (the LEDs were externally buffered). To add a high-tech look to ROVER, I mounted the switches to a translucent plastic panel and back-lit the nomenclature with red LED indicators. Similarly, the lower status panel uses rear-projecting indicator lights. The bar-style LEDs are imprinted directly with the various status symbols and mounted behind the plastic panel. The symbols are

only seen through the plastic when they are lit.

No. 2 . 21

My part of building ROVER was easy: a couple off-the-shelf boards, a couple of trips up the roof, and some monotonous wiring. The real task of making ROVER into the video reconnaissance unit we imagined was left to Ken. Next issue we'll explain the fancy footwork behind ROVER's software.

The authors would like to thank Bob Borg for allowing us to take his photograph, use his name, and destroy his professional image.

The complete source code for ROVER is available on disk (see page 44) or can be downloaded from the Circuit Cellar BBS. For a reprint of the ImageWise Serial Video Digitizer articles presented by Steve Ciarcia in May-June '87 BYTE, order DT/DR Reprint. Send \$3 postage and handling.

Add \$10 for the two **ImageWise** assembly and user's manuals.

For a reprint of the BCC180 Multitasking Computer/Controller articles presented by Steve Ciarcia in Jan.-Mar. '88 BYTE, order **BCC180** Reprint. Send \$4 postage and handling.

Add \$6 for the **BCC180** assembly and user's manual.

Send all manual and reprint requests (mail order only, please) to:

Circuit Cellar INK Reprints P.O. Box 772 Vernon, CT 06066

#

Ideal for Plug-h AT CPU **Boards:**MICROMINT CCAT (OEM-286)

board (see BYTE "Circuit Cellar"

Sept '87)

and others

- \* Five **8/1 6** bit full-length expansion **sio** ts

- Three 1/2 height drive slots w/drive mounting rails

- 100 watt power supply wlhigh surge capacity & fan

Keyboard connector, keylock & speaker

- \* Four seriallparallel connector punchouts

- Dimensions: 6.25" **H** x 11.75" **W**x 15.25" **D**

Microcomputers & Peripherals

DISKS PLUS, INC. 356 Lexington Drive Buffalo Grove, IL 60089

Technical and more info: (312) 637-7888

Fax: (312) 537-6331 Quantity pricing available

Trademarks: IBM PC-AT, International Business Machines Corp.; CCAT and OEM-286, The Micromint, Inc.; CPU 386, Sigma Designs, inc.

## SEL INK

### Answers; Clear and Simple

## Letters to the INK Research Staff

My name is M. Tarvirdi Zadeh. I am an Industrial Engineer and am interested in computing and electronics. I have some experience in computer interfacing. I designed and made a general-purpose interface for **ZX81, ZXspectrum**, and C-64. I am working with Amstrad PC1512 (XT Clone 8086 8 MHz) now. I want to do the same (design and make a general-purpose I/O board for control) for my XT clone. Because of the many regulations and limitations, I do not have any special documents to help me. I borrowed an IBM XT hardware technical reference from my friend. After much searching, I haven't been able to find any free addresses for the expansion board. I decided to use the I/O address 300-31F hex which are used for prototype cards.

- I have three questions that I hope you can help me with.

- **1.** Which I/O addresses are free to use for expansion boards?

- 2. Can my CPU (8086 8 MHz) or IBM XT CPU (8088 4.77 MHz) support I/O addresses higher than 64K. And which segment I should use for my addresses (300-31F hex)?

- 3. How can I flag my CPU that there is an active board plugged in and how is it recognized?

- I hope that you can answer me personally. I am looking forward to hearing from you as soon as possible.

Thanking you in advance for your cooperation and best wishes for you.

M. Tarvirdi Zadeh Tehran, Iran

Apparently your past experience with computer interfacing has been limited to memory-mapped I/O. The 8088/8086 processors use I/O ports to communicate with the outside world, which requires a little different approach to interfacing. The IBM PC expan-

sion bus (called I/O channel by IBM) is also a little different than buses you may be more familiar with.

The 8088 can address up to 65536 I/O ports, but IBM implemented I/O channel addressing for only 512 ports, starting at address 200h, and ending at 3FFh. Ports used by IBM are listed in chapter I of your XT Hardware Technical Reference (probably on page I-10). There are several blocks of unused addresses in the range from 200h to 3FFh, mostly reserved by IBM for future use. You can use these for your own projects, but there may sometimes be conflicts with new equipment you might install later. Using 300h to 31Fh should be safe.

Since I/O addresses are not mapped into memory address space you don't use a segment address, and no memory addresses are used up. The processor addresses memory through MOV instructions which transfer data from memory to registers, registers to memory, and so on, where addresses are always in a segment + offset form. I/O ports are accessed by means of INP or OUTP instructions which transfer data between registers and ports directly, and require no segment address.

It is not necessary to tell the processor that there is an active board plugged into an expansion slot. All slots on PCs and all except the short slot on XTs are the same. No special addressing is required, and all memory and I/O ports in the range given above are accessible to boards installed in the expansion slots. You simply write your software to use the features of your board and plug it into any slot.

-- INK Research Staff

We need to obtain a mathematics library for use with the AMD 95 11 /Intel 823 1 A 8-bit coprocessor. We want it to be a **linkable** replacement or substitute for the FORTRAN library supplied with the old Microsoft

FORTRAN-80 compiler for the **8080/Z80** processors running under CP/M-80. Is such a library available anywhere?

We have a number of **8-bit CP/M** computers in current use, each dedicated to a single laboratory instrument. Installation of the coprocessor hardware would be no problem, but our programs need to be able to access it. We need to do fast Fourier transforms in fractions of a second rather than a few seconds.

C. Sherman **Gromme**Menlo Park. CA

In reference to your letter asking about a mathematics library for the 8080/Z80 processor under CP/M: I dug through my files and I am afraid I did not come up with much. I found an old address of a company which may or may not still be around or still have these routines available. They advertised complete 951 I driver software including reentrant conversion routines but it was from a very old advertisement.

Their address is:

Sorensen Software Raiffeisenstr.1, 6104 Seeheim I, West Germany Tel. 06257/83707

Another suggestion would be to contact suppliers of CP/M public domain software. The following listings I found in a recent issue of the Computer Shopper.

Public Domain Users Group Box 1442-C2 Orangepark, FL 32067 (send SASE and computer type for info)

CP/M User Group Library -- 100 disks \$150 S. Mills, 4615 Orleans Blvd. Jefferson, LA 70121 (504) 733-9611

Another suggestion would be to place an advertisement in the Computer Shopper or perhaps some other publication.

-- INK Research Staff

I am building a speech synthesizer for my Atari 800XL. I have two Radio Shack chips, CTS256A-AL2 and SP0256-AL2. I see on the enclosed panel that upon power-up or use of the hardware reset, the system

speaks "OK." It doesn't. I hear two "buzzings" but they are not the same.

Please, Steve, how do I connect this to the Atari and what must I do on the keyboard to enter the data? It is not possible for me to obtain a **3.12-MHz** crystal. I am using 3.2768 MHz. What about that replacement? All my thanks in advance.

#### **Hubert Lemort** Belgium

The Atari 800XL is an interesting computer with some severe limitations as far as interfacing to the outside world. The port provided is designed for synchronous serial I/O only. The speech chip set will accept asynchronous serial input, or parallel format with strobed handshaking. The best approach is an adapter of some sort such as an RS-232C or Centronics attachment. One source that is advertising an extensive number of Atari 8-bit accessories is: Electronic Dimensions, P.O. Box 1846, San Luis Obispo, CA 93406 USA. Using either an RS-232C serial or a Centronics parallel port, a properly wired synthesizer assembly can be addressed and treated as if it were a printer or other output-only peripheral.

Your use of the 3.2768-MHz crystal instead of the specified 3.12 MHz is unlikely to be a source of the problem you are experiencing on start-up. In this country it is not uncommon to find a 3.58-MHz color burst crystal used instead of the much rarer 3.12-MHz crystal specified.

You should double check all wiring, solder joints, and layout. Check power supply voltages at each IC and observe proper polarity on all polarized capacitors. Be sure your speaker is functioning properly: if it isn't, replace it. Trouble-shooting circuits is seldom fun, but is a necessary part of design and construction.

In order to send text to the synthesizer, it must be directed to the output port. Access instructions should be supplied by the maker of the interface converter for RS-232C or parallel. The October 1987 issue of Modern Electronics contains an article on the Tandy speech synthesizer set, with information that may prove useful to you. The letters columns in the January and April 1988 issues have corrections for errors in the original article.

#### -- INK Research Staff

In Visible Ink, the Circuit Cellar Research Staff answers microcomputing questions from the readership. The representative questions are published each month as space permits. Send your inquiries to: INK Research Staff, c/o Circuit Cellar INK, Box 772, Vernon, CT 06066. All letters and photos become the property of CCINK and cannot be returned.

September/October 1988

## The Home Satellite **Weather Center**

by Mark Voorhees

## Part 5

## Focus on the MC68000 Peripheral Controller

Editor Note: This is Part 5 of a 12-part series on The Home Weather series. Mark frequently refers to circuitry described in previous installments. For information on ordering back issues, see page 39.

s I'm writing this portion of our series on weather information tools, I'm sitting in my room at the San Diego Princess Resort, overlooking an overcast Mission Bay, and wishing that I had paid more attention to the data and maps I'd looked at prior to the trip. They foretold the presence of the fronts producing the low temperatures (highs of 65-75 degrees, much better than the 108 at my home in Phoenix yesterday) and the cloudy skies (I would appreciate a little sunlight!) likely for the duration of my stay -- looks like the data was right on target. Oh well, it's a nice area to visit. Hawaii is a little too expensive to visit this year (although it's climatologically superior!), and, after all, this is a working vacation.

There is a point to all this (in case you were beginning to wonder). The conditions here could put quite a damper on a vacation trip with the wife and kids unless you had the information warning you to expect it. That's one of the ways our system will help: providing you with the tools to gather data about the weather phenomena occurring around you.

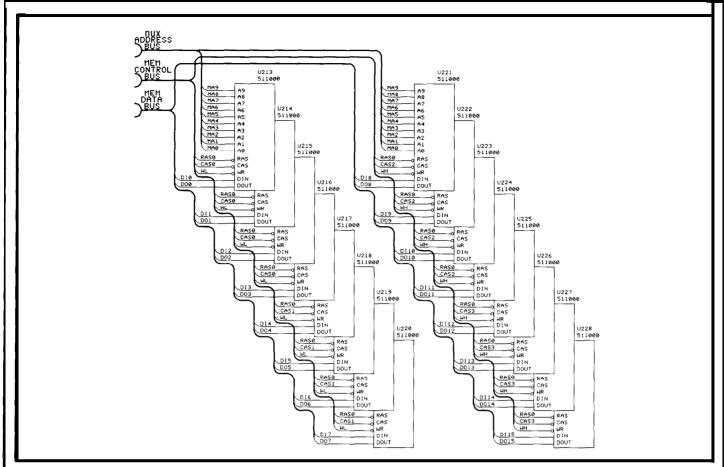

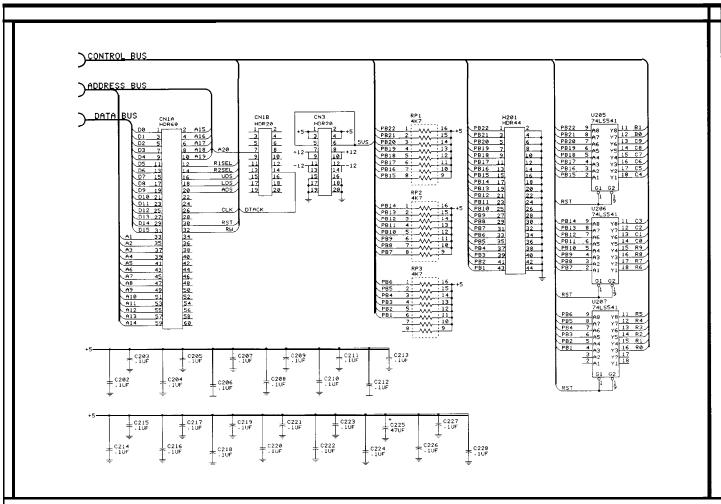

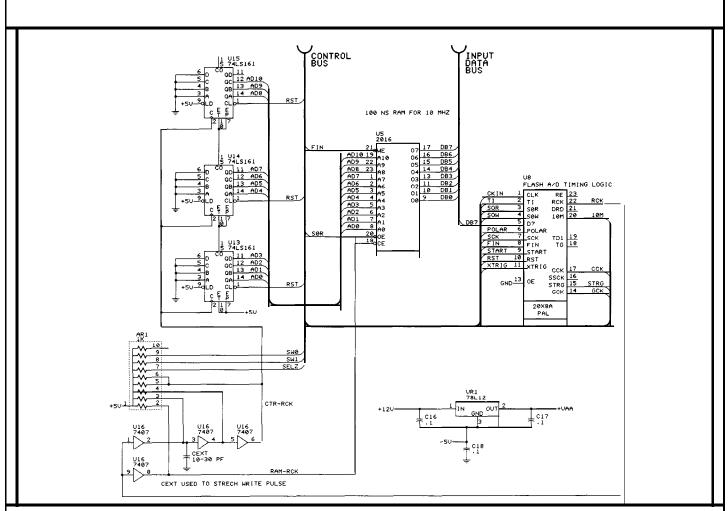

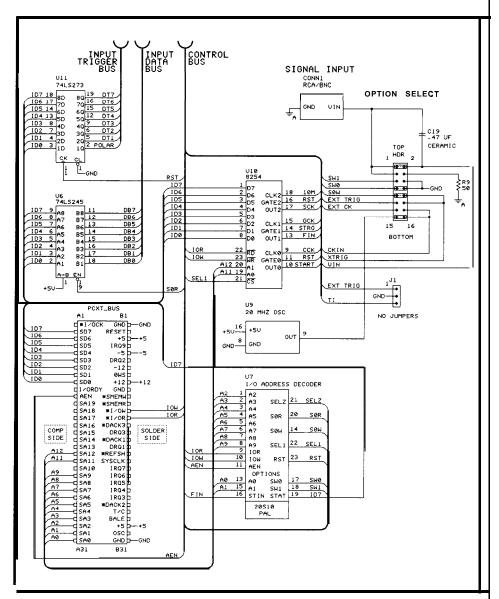

Enough of our little vacation, and back to focusing on the construction of the Home Weather Center 68000based Peripheral Processor. In this installment, we'll talk a little more about the main processor circuitry, as well as describe the mass-memory circuit and a front-panel circuit, and I'll give recommendations on a power supply and case for the finished system.

When I discussed the main processor in the last issue, I covered the operation of the circuit in only general terms. The precise usage of the hardware will, of course, be guided RAM, which we'll use for by the firmware (a subject of the next installment). The circuit itself is actually a very generic 68000 application, and (experimenters take note) could probably be used for many other purposes.

Also, in the last issue I neglected to mention the purpose for connector CN4. It is the power connection for the RGB/NTSC encoder board described in the first two issues of Circuit Cellar INK. Sufficient room exists in the recommended enclosure to mount this unit, if desired.

Let's take a closer look at some of the circuit elements as they will be used in our project:

a PAL for Memory Selection

Editor's Note: containing U102, U105, U106, and U112-U114 was presented in the battery backup for the entire proj-July/August issue of INK. Logic for the PAL is available on the Circuit Cellar BBS or the INK Software Disk

for this issue. For downloading and ordering information, see page 44.

Programmable This Array Logic (PAL) device has high-order address lines (A16-A19), data strobes (UDS, LDS), and the address strobe (AS) from the 68000 available to it, as well as system clock and an on-board memory select (OBMSEL) logic from U114.

The device serves the processor by handling the selection of chips within the 32K x 16 EPROM area, or the 32K x 16 on-board static scratchpad memory as well as stack and configuration storage areas. U112 also generates a delayed data acknowledge (DTACK) signal to allow for EPROM and SRAM setup times. The address area for EPROM is OOOOOOH to 01 FFFFH. and for on-board RAM is 020000H to 03FFFFH. We won't be using all of these areas at the moment, but the remainders are available for future use if needed.

Battery-Backed SR iii

**SRAMs** themselves are really rather self-explanatory, but I do want to mention something that is not on the schematic: the battery backup method used to protect **The schematic** these chips from memory loss.

My system design allows for As with any battery-type device, however, there are limitations. I wanted to provide the stack

Bi-directional **DataMigration** Facility for IBM **PS/2**, AT, PC, PORTABLE and **Compatibles**

Parallel port to parallel port. Economical method of file transfer. Bi-Directional file transfer easily achieved.

achieved.

Supports all PS/2 systems

(Models 30, 60, 60, and 80).

Supports IBM PC, XT, AT, Portable and 100% compatibles.

Supports 3 1/2 inch and 5 1/4 inch disk transfers.

Supports hard disk transfers. Supports RAMdisk file transfers. The SMT 3 Year Warranty.

The pointing device of the future is here!

Two and three axis pointing capability. High resolution trackball for X and Y axis input. High resolution fingerwheel for Z axis input.

Use with IBM®PC's, XT's, AT's and compatibles.

'Three input buttons.

Full hardware emulation of Microsoft ® Mouse.

Standard RS-232 serial interface. Includes graphics drivers and menu generator.

Easy installation. 1 year warranty. Made in U.S.A.

167 North Limestone Street Lexington, Kentucky 40507 Tel: (606) 233-4156

Orders (800) 872-7279

Data (606)252-8968[3/12/2400 8-N-11

VISA, Mastercard, Discover Card,

FeleCheck

and configuration storage with separate protection. I chose to install a special type of socket under the memories. The unit is called a "SmartSocket," and is made by Dallas Semiconductor (part no. DS1213C). The unit is basically a standard-configuration 28-pin DIP socket with a built-in CMOS controller and lithium battery source.

The **SmartSocket** is totally transparent until the embedded controller sees a Vcc out-of-tolerance condition. It then write-protects the SRAM and powers it with its own energy source until normal Vcc is restored.

While this addition is not required, it is recommended, especially to those who may not feel that a full battery-backup scheme is necessary for their application.

This PAL device uses A6-A8 as well as the data strobes (UDS, LDS) from the 68000, and logic from U114 indicating that the memory-mapped address area is selected (IOSEL). U113 allows for 7 active devices, each with up to 32 assigned addresses (used for register access, etc.)

The memory-mapped device area is designated to start at 300000H.

This PAL device provides for the mapped select lines, and uses A20-A23, the address strobe (AS), and the function code information (FC0-FC2) from the 68000 to create its outputs. It also provides the decoded interrupt acknowledge signal (IACK) from the 68000 when the three function code lines are high. R1SEL and R2SEL are provided as bank selects for the mass DRAM memory.

Along with providing the UART and programmable baud-rate gen-

eration for communication with the control terminal (your PC), this device provides interrupt prioritizing logic and two utility timers (which we'll make use of later on in the series).

Before we leave the main board, I want to mention something of interest to those of you who like to take a project and improve or customize it to meet vour special needs: occasionally I'll provide an idea, suggestion, or circuit of a possible change in the design that could lead to enhancements to our overall system. These ideas are presented "on paper" only, and are not required for operation of the system as designed. The front panel circuitry is an example of this concept.

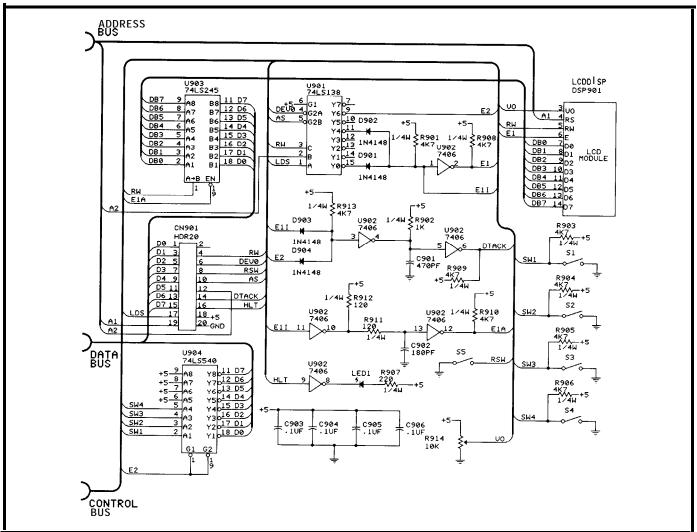

Figure 1 shows the schematic of the standard front-panel circuit. This display will give us basic prompts on the Peripheral Processor's "health," including status items such as "No Config," "Memory Full" (for the DRAM memory), and so on. The circuit also supports four switches for software sensing (clearing WEFAX images without downloading them is a typical application), and a "warm boot" reset switch (resetting the 68000 to "boot" state without destroying the scratchpad-held configurations).

I've also made allowance for a "processor running" indication, LED1 is driven by the processor "HALT" line, and is normally illuminated. It will extinguish if the processor halts for any reason. This is a dual-purpose indicator, in that it will only stay out if, for some reason, the "watchdog" reset circuit fails to restart the processor.

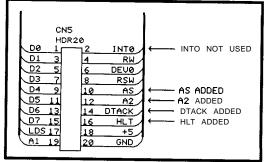

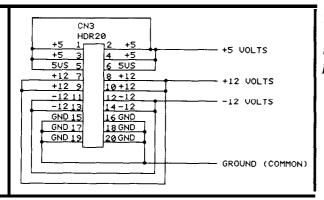

I've designated **CN5** to serve as interconnect to the front panel. Figure 2 shows added connections to implement the basic design.

Figure 1 - The standard front-panel circuit, showing LCD display, switches for software sensing, and a warm boot reset switch.

These are not critical parts omited from the original. Rather, hese pins might be needed for ther signals if you decide to ustomize your front panel. The nain buses (CN1A and possibly N1B) could be brought to the ront-panel circuit if you needed ophisticated access to the 68000.

As to the standard design, the ircuit of Figure 1 handles the iterfacing of the software-insed switches via U904 (you ould add up to four more witches to this design, connecting them to U904-6, U904-7, I904-8, and U904-9), and also

Figure 2 - CN5 serves as an interconnect to the front panel to implement the basic design.

provides for the connections to the LCD module, a Philips (Amperex)

LTN2 11 R- 10 or equivalent unit This module provides for **display** of two lines of 16 characters, **with** necessary cursor and display **con**trols built in.

Final address decoding is done by U901, which provide! signals to enable the LCD module as well as U904 and U903.

The LCD module used here is described in Philips Technical Publication 238. It is quite self-sufficient, but lacks the logic to create high-Z bus conditions or to generate a data acknowledge (DTACK) to the 68000 board. Much of the remaining circuitry

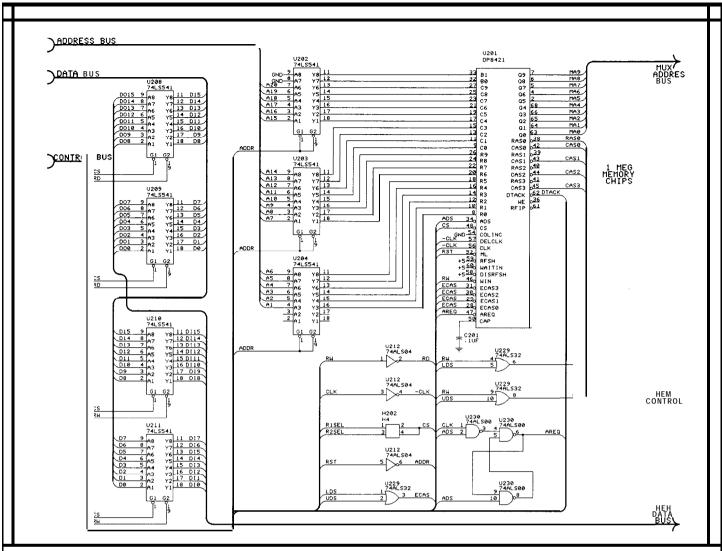

Figure 3a - Controller circuitry for DRAM board. The National Semiconductor DP8421 is simple to design around and requires minimal support from the hard-working MC68000.

(U903, TC511000P 1 Meg x 1 page-mode U902) provide, t  $\mathbf{D}$  eR nAe (100-ns essary logic to accomplish these 120-ns

$\begin{array}{c} \text{(NEC's}\\ \text{uPD411000} \text{ would be an acceptable}\\ \text{substitute)}. \end{array}$

front- The DRAM controller is the Na-

the DRAM can be expanded based on space and power availability. In the standard design, two boards is a practical limit.

Before continuing, a short explanation is necessary. As we all

mal support requirements from the 68000 (which will have enough to do!). The controller receives configuration information at boot time and then operates virtually unat-

The design is based on the premise that the system will be using the mass memory for data storage (a "RAM disk" of sorts), and therefore

end in sight. I planned this circuit

nat- current price vs performance comparisons lean to using l-Meg deemsigns. However, hedging a bit on my "cloudy crystal ball" predicted (a tions, I'm providing on 256K DRAMs

&gures 3a layout of the 1M

a

Figure 3b - Pin assignments for the I-Mbyte DRAMs used on the memory board.

You can get the schematic for the 256K DRAM version of the board by sending a SASE to: Circuit Cellar INK, P.O. Box 772, Vernon, CT 06066.

If you have a massive supply of 256K DRAMs or find them availdesign is for you, with the following warnings: first, you will need to increase the size of your cabinet to allow for the additional board space and ventilation due to the addition of 48 ICs, and second, you will have to increase power supply to support the extra chips. In this case, I think that I would provide a separate supply for the memory board(s), as the power supply I will mention later will likely not handle the extra load (based on entire system requirements).

I must confess that I loathe the idea of coming up with power supplies for projects. "Brute force" designs are the least costly for experimenters, and parts are readily available, but they are inherently heatproducing and tend to take up too able at a super price, then this much space in an otherwise neatly designed enclosure. They are, in many ways, inefficient.

Switching supplies, on the other hand, are efficient, but difficult to available product, I'm told, so construct for an experimenter. Purchasing a ready-built supply is the alternative, but often is too costly.

I toiled over many power supply designs for this project, finding them inadequate in one way or another. We need +5 volts at a minimum of 5 amps for the system, as well as about 350 way of external support, as is mA at +12 volts and 200 mA at - 12 volts. And all this in a minimum of

space.

One of my suppliers surprised me with a product from General The Model 35-502 Instrument. switching supply slightly exceeds our power requirements, is reasonably priced, and the size and style of its enclosure lends itself to mounting on the rear of the system cabinet, thus keeping supply noise and heat as far away from the circuitry as possible.

This power supply is a widely finding it should not be a problem. My supplier has a limited number of these units in stock as of this writing, and 1'11 gladly provide information and pricing. See the ordering **sidebar** for details.

The supply requires little in the shown in Figure 5. The power switch on the rear will remove AC

Figure 4 - The 68000 peripheral controller provides ample interaction with the outside world through the slots shown above.

power from the supply, but not the battery system (to be described in a future installment, which will also cover the interconnections to the power bus; for now, the temporary connections of Figure 6 can be used for testing).

I have searched for an adequate enclosure for our project, which needs about 10" by 5" by 11" of interior space, and I've located a PacTec enclosure that meets the requirements. The model CL-525 case has front and back panels that are 5.3 12" x 12", allowing for space to install our power supply and connectors on the back, and our front-panel display with switches on the front. You can get the name

of your nearest distributor by contacting PacTec directly:

PacTec Enterprise and Executive Aves. Philadelphia, PA 19 153

I have a limited number of these enclosures available at special pricing. See the ordering **sidebar** for information. I will also provide cutting and drilling templates for the standard configuration by mail (since space is limited here, and I'll be providing a full-scale drawing).

This is, by no means, the only answer to the need for a cabinet. Any case meeting the requirements above will house the standard system. If you plan to customize, or build the memory configuration which uses the 256K DRAMs, be sure to take the

extra space needs into consideration. If you plan on using your system in a den or similar room (and you're familiar with fine woodworking techniques), you might want to construct your cabinet of furniture-grade hardwoods to make it a showpiece!

In our next episode, I'll be describing the firmware which runs the system, as well as describing the methods we'll use to port the data into and out of the Peripheral Processor. (You can see Figure 4 for a headstart on I/O.) We'll also venture a bit ahead to describe the WEFAX antenna and RF modules which you'll need to provide the WEFAX signal to our Peripheral Processor (these pieces of RF equipment are fairly critical, so I don't recommend building them

÷

Figure 5 - The circuit for the power supply will allow you to cut AC power while retaining the battery back-up.

Figure 6 Temporary connections for testing the power supply\_

yourself; I've found units that are reasonably priced and perform well).

Before I wrap up for this issue, I want to cover some questions I've received on using the RGB/NTSC Encoder board which was presented in issues 1 and 2 of Circuit Cellar INK.

- Q. Can the Encoder be used on PAL (European) TV systems?

- A. The MCI377 IC contains the circuitry to allow for this change. It will be necessary to make the following changes in constructing the circuit:

- I. The EPROM will have to be programmed with the proper pattern for PAL sync.

- 2. Pin 20 of the MC1377 will have to be pulled high (or left open).

- 3. The TTL oscillator module will need to be changed to 17.72 MHz to handle the different sub-

carrier frequency generation and provide proper timing for the EPROM.

Most of the setup procedures should yield results similar to the NTSC setup, but if you build a unit for PAL use, I recommend that a PAL-qualified serviceman or TV engineer make the adjustments for you.

- Q. Can the encoder work with a monochrome signal?

- A. It's possible, but not recommended, since the signal specs for mono TTL video are much looser than for color. You could feed the mono signal simultaneously to the R, G, and B inputs, feed the intensity signal to the I input, and feed H and V sync to their appropriate inputs, and see if the output of your graphics card will agree with the timing capabilities of your encoder.

The main problem stems from the fact that the NTSC color signal specifies a horizontal rate of 15.734

kHz and a vertical rate of 59.94 Hz. These numbers didn't come out of thin air; they relate directly to the 3.579545-MHz color subcarrier frequency and, therefore, have a relationship to our encoder's 14.31818-MHz clock and EPROM.

The mono signal, however, sets H rate at 15.75 kHz and V rate at 60 Hz, which could cause noise or waves in the picture due to the timing relationships.

- Q. Can analog RGB signals be fed to the encoder?

- A. Yes, within the limitations of standard horizontal and vertical sync frequencies (the same limitations as with TTL, i.e., no doublerate horizontal frequencies as in EGA). This is the reason that CN2 is jumpered at the MC1377 (I likely will make use of that header in the future also, as part of the Home Weather Center). The headers on pins 3, 4, and 5 will accept capacitivelycoupled (nominal 15 uF) R, G, and B inputs of l-volt peak-topeak level noncomposite video (no sync). The horizontal and vertical syncs are usually 4 volts peak-topeak and can be handled through the normal sync path. Remember to leave the jumpers on pins 1 and 2 of the MC1377 in place. Setup should be virtually the same as with TTL inputs.

(As space permits, I'll be handling questions relating to our project in these articles. If you have ideas or questions to share, please forward them to the address in the ordering **sidebar** on page 45.)

I think it's time to end this month's installment on an optimistic note: by next summer, we should all be better equipped to handle the planning of our summer vacations, weather-wise. As for me, I vow to take advantage of a better climate next year (maybe if I start saving for Hawaii now. ..).

## FROM THE BENCH

Conducted by Jeff Bachiochi

## **RS-232 Economic Tradeoffs:**

Board Space vs. Parts Count vs. Parts Co\$t

ost "system" designs include at least one serial I/O channel for communications with the outside world (modem, printer, terminal, etc.). A minimum serial I/O channel will consist of at least three connections: transmit, receive, and a common ground. Additional lines can be used for optional control functions such as request to send, clear to send, data set ready, data terminal ready, and carrier detect.

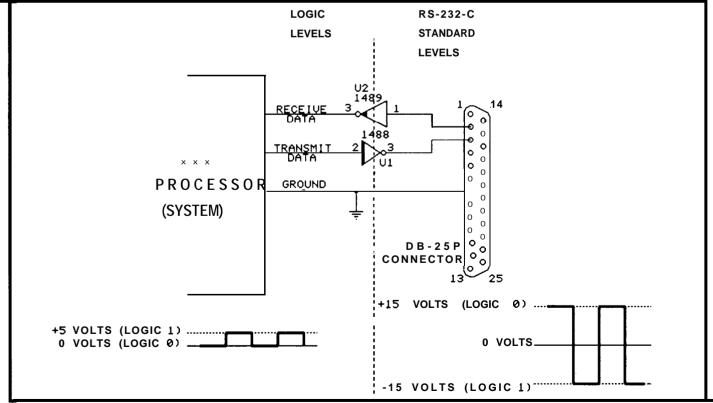

RS-232-C, the standard for serial interface between Data Terminal Equipment (DTE) and Data Communication Equipment (DCE), requires a positive level of +5 to +15 volts to indicate a "0" (SPACE or ON) and a negative level of -5 to -15 volts to indicate a "1" (MARK or OFF). These levels are not compatible with the "system" TTL levels of "ground" (0 volts) and "+5"

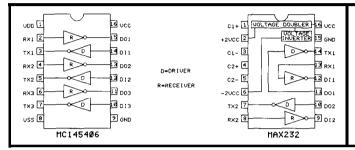

(volts). The TTL levels must be changed to and from RS-232-C levels. This change is accomplished through the use of two kinds of level converters: a line driver (the transmitter), which converts a O-volt TTL level to a positive 5-15-volt level and a +5-volt TTL level to a negative 5-15-volt level (depending on the supply voltage); and a line receiver, which converts a positive 5-15-volt level back to a O-volt TTL logic level and a negative 5-15-volt level back to a +5-volt TTL logic level. (See Figure 1).

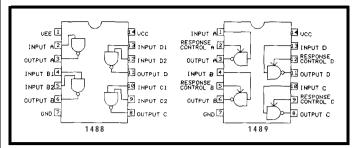

For years the "standard" parts used for this level conversion were the 1488 (TTL-to-RS-232 transmitter) and the 1489 (RS-232-to-TTL receiver). These two 14-pin IC packages, shown in Figure 2, each contain four transmitters or receivers.

Figure 1 - A line driver and line receiver are required to convert TTL signal levels to RS-232 and back.

Figure 2 - The 1488 and 1489 are standard components for TTL to RS-232 conversion.

With the onset of CMOS devices, direct replacements for the 1488 and 1489 have arrived. The 14C88 and 14C89 take advantage of CMOS technology to provide very low power consumption.

| DEVICE | BOARD AREA      | A POWER                          |

|--------|-----------------|----------------------------------|

| 1488   | 1/2 square inch | <b>±10-15</b> volts @ 20 mA each |