## Troubleshooting and Repairing Your COMMODORE 128

# Troubleshooting and Repairing Your COMMODORE 128

ART MARGOLIS

#### FIRST EDITION FIRST PRINTING

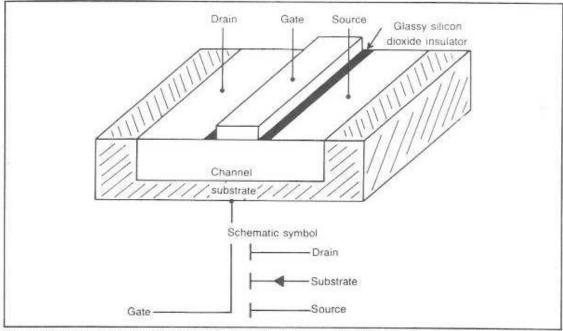

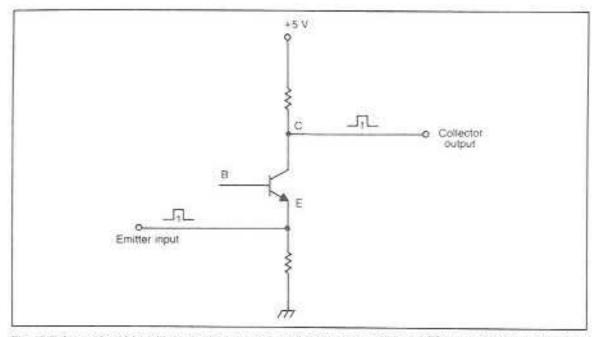

Copyright © 1989 by TAB BOOKS Inc. Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

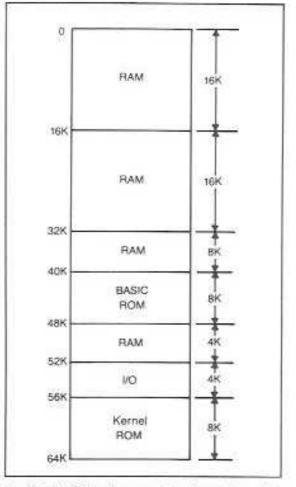

Library of Congress Cataloging in Publication Data

Margolis, Art.

Troubleshooting and Repairing Your Commodore 128 / by Art Margolis.

p. cm. Includes index.

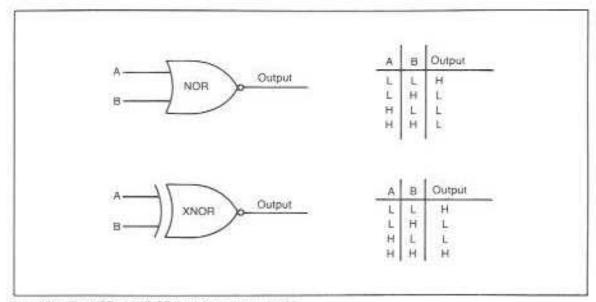

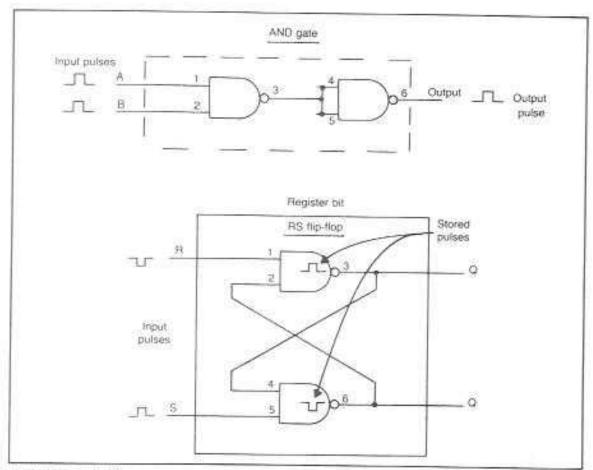

ISBN 0-8306-9099-9 ISBN 0-8306-9399-8 (pbk.)

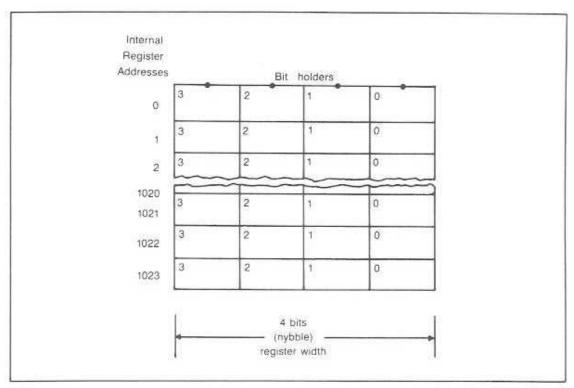

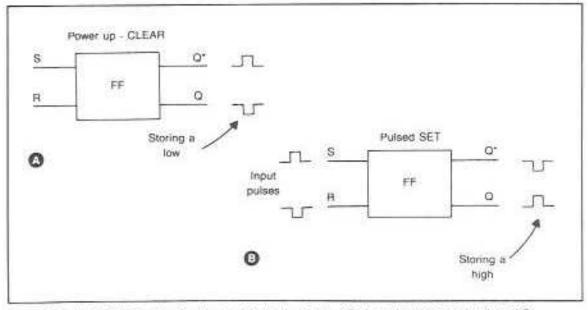

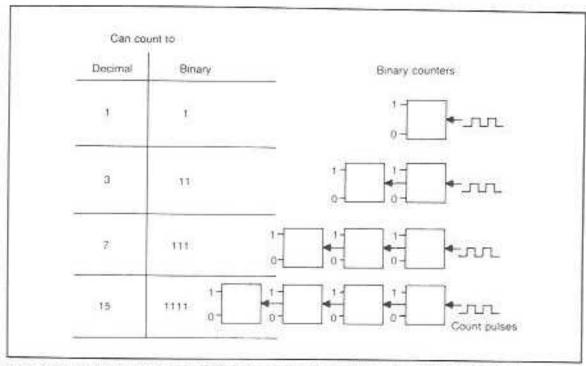

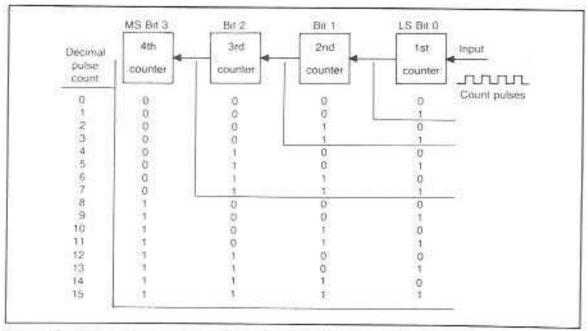

1. Commodore 128 (Computer) 2. Commodore 128 (Computer)

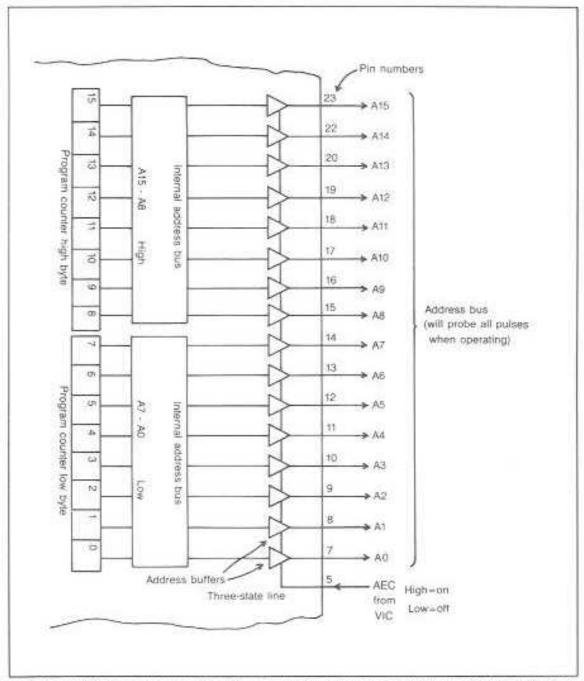

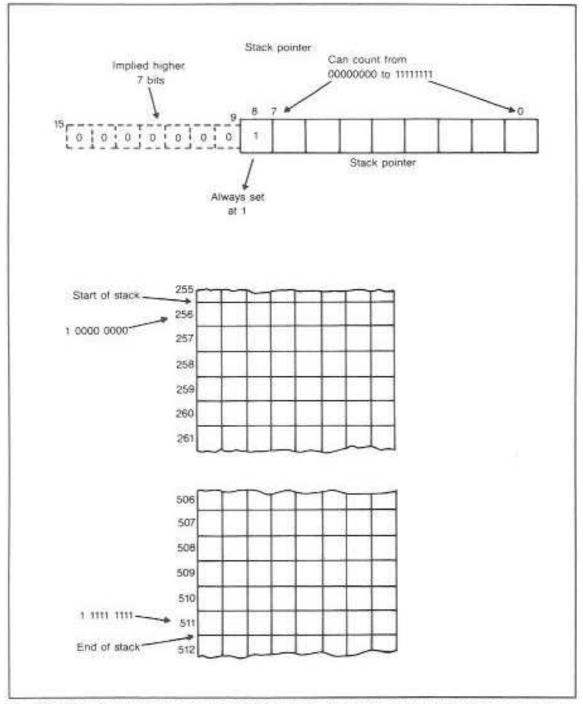

-Maintenance and repair. I. Title: II. Title: Trouble shooting

and repairing your Commodore 128.

QA76.8.C645M37 1988 621.391'6—dc19

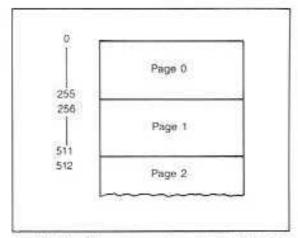

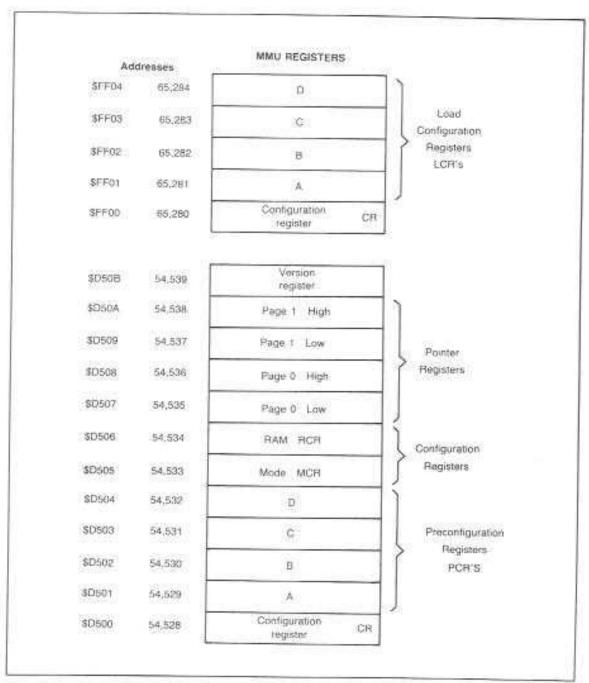

88-20129 CIP

TAB BOOKS Inc. offers software for sale. For information and a catalog, please contact TAB Software Department, Blue Ridge Summit, PA 17294-0850.

Questions regarding the content of this book should be addressed to:

Reader Inquiry Branch TAB BOOKS Inc. Blue Ridge Summit, PA 17294-0214

## **Contents**

|   | Acknowledgments                                                                                                                        | viii |

|---|----------------------------------------------------------------------------------------------------------------------------------------|------|

|   | Test Point Charts                                                                                                                      | ix   |

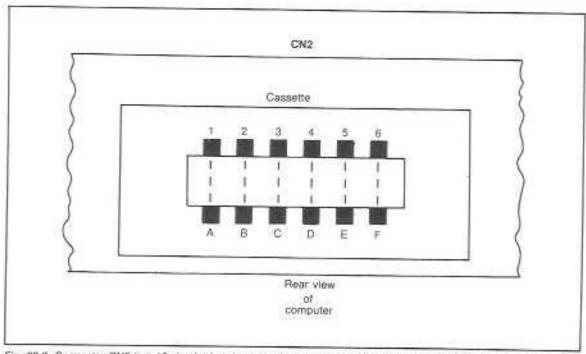

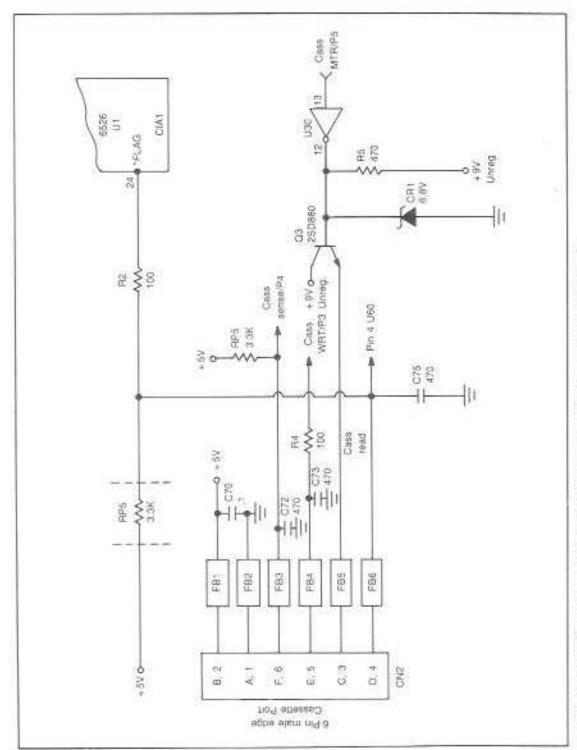

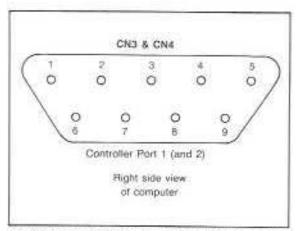

|   | Introduction                                                                                                                           | х    |

| 1 | C128 Briefing Session                                                                                                                  | 1    |

| T | The Symptom Devices—Diagnostic Programming—Printboard Landmarks—An Overview of Trouble Analysis                                        |      |

| 2 | Disassembly                                                                                                                            | 20   |

|   | Getting the Hood Up—Freeing the Printboard—The Power Supply Box—Visual Repairs—Cleaning Static Electricity                             |      |

| 3 | Chip Location Guide                                                                                                                    | 39   |

| U | Specific Information—Chip Survey                                                                                                       |      |

| 4 | Chip Changing Techniques                                                                                                               | 49   |

| 1 | The Rugged Chips—Tristating TTLs—The Sensitive Chips—The DIP Package—Socketed Chips—Soldered-in Chips                                  |      |

| 5 | The LSI Chips                                                                                                                          | 67   |

| U | The Microprocessors—The 6526 Complex Interface Adapters—The VIC and Video Controller Chips—6581 Sound Interface Device—The PLA and MMU |      |

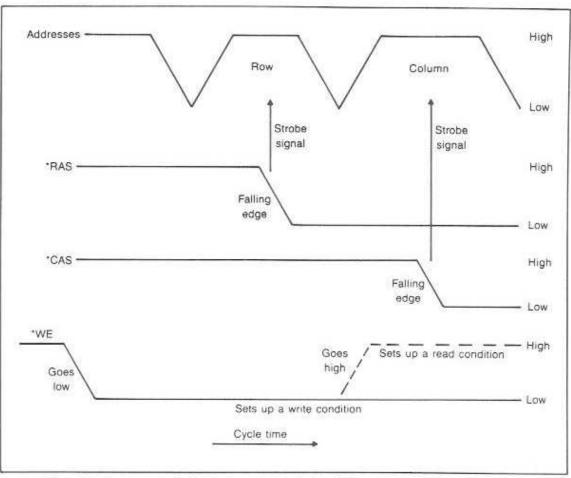

| 6  | Dynamic Random Access Memory Static RAM—Dynamic RAM                                                                                                                                                                                                                                                                                                                                                                                                            | 86  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

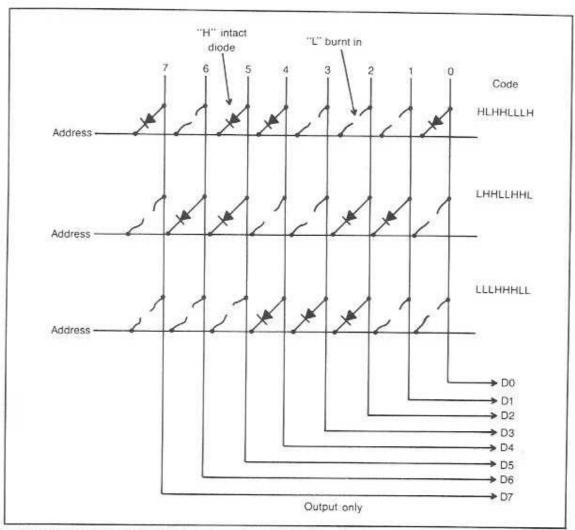

| 7  | Read Only Memory Block Diagram—The Rest of the ROMs                                                                                                                                                                                                                                                                                                                                                                                                            | 104 |

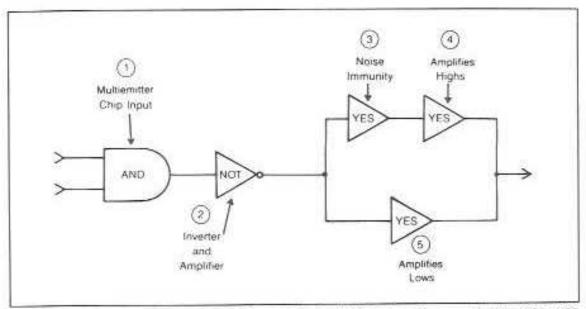

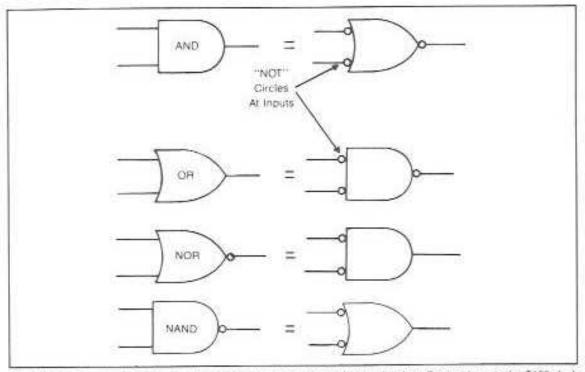

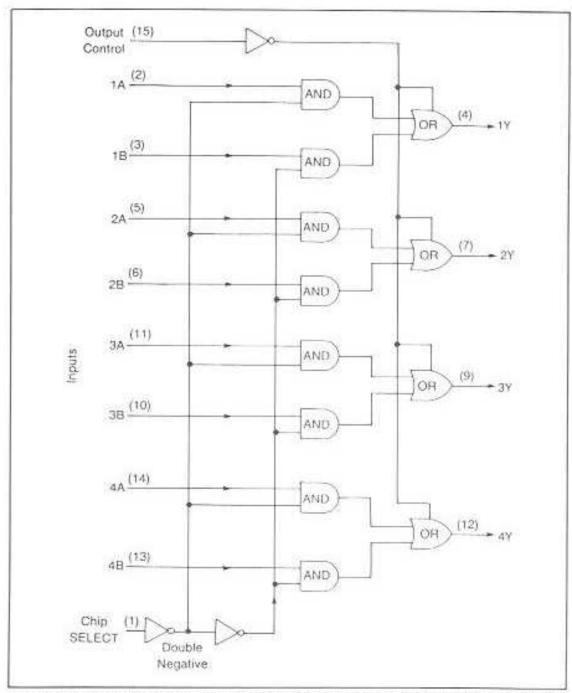

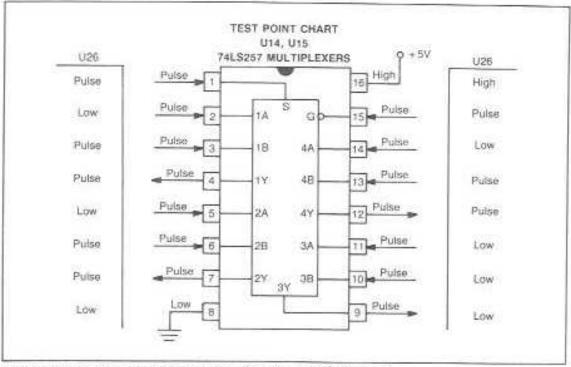

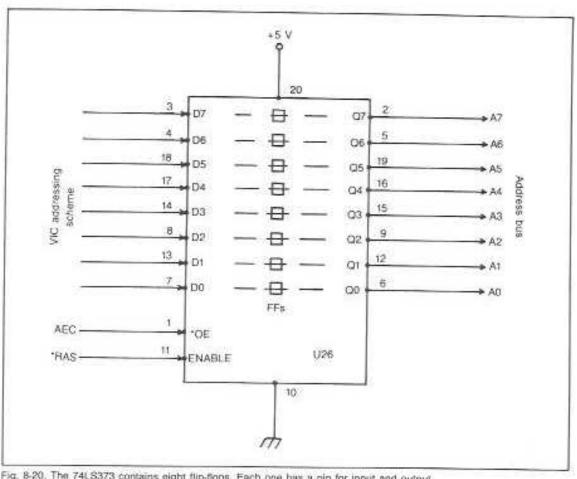

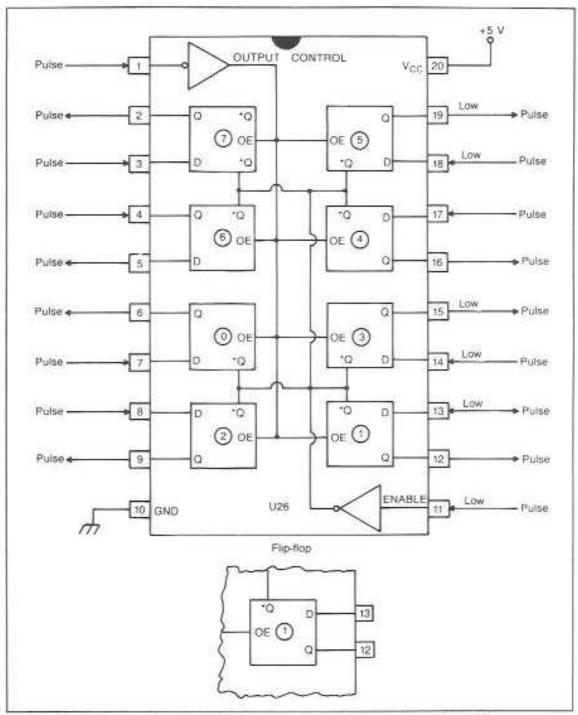

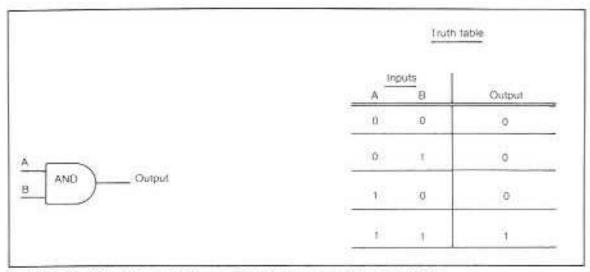

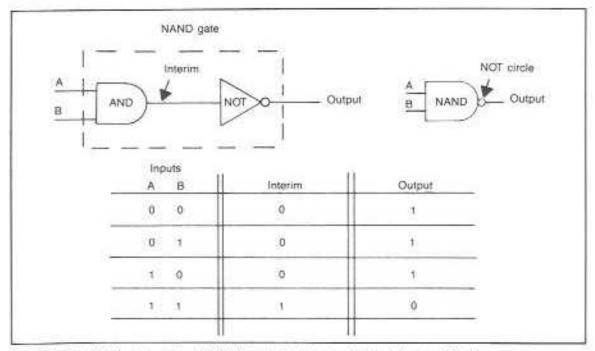

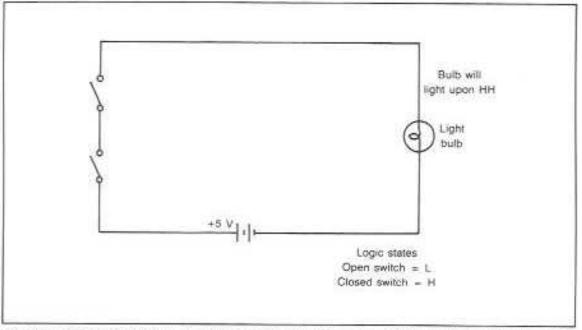

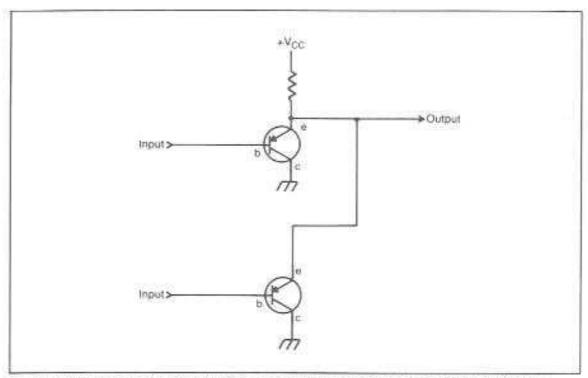

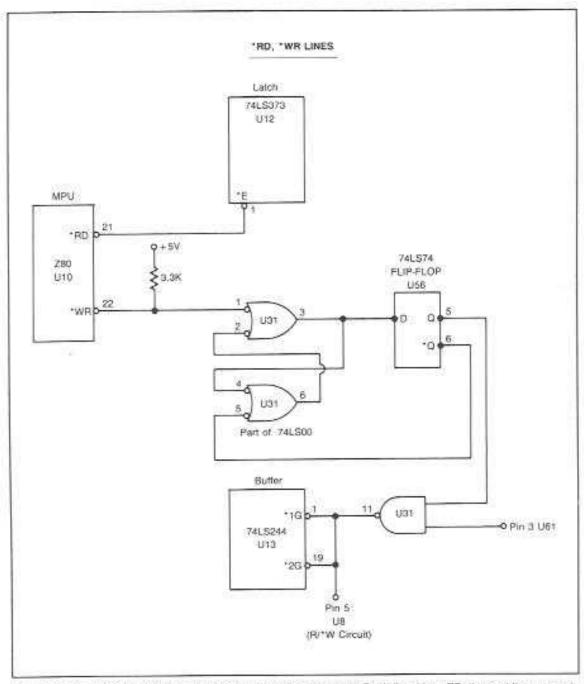

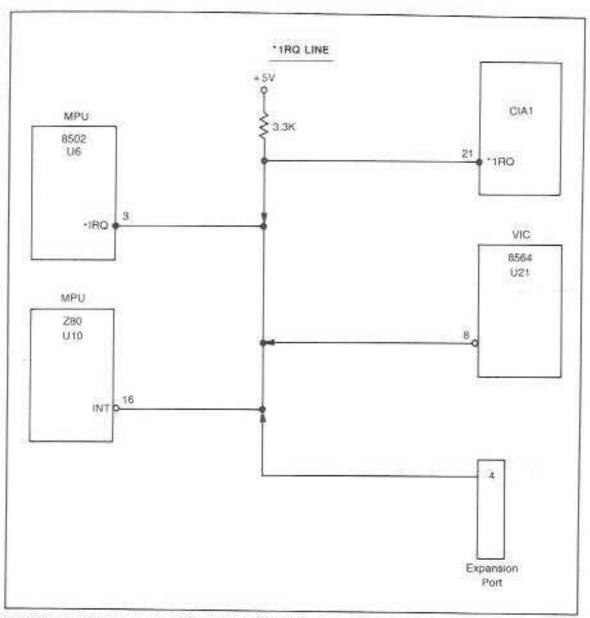

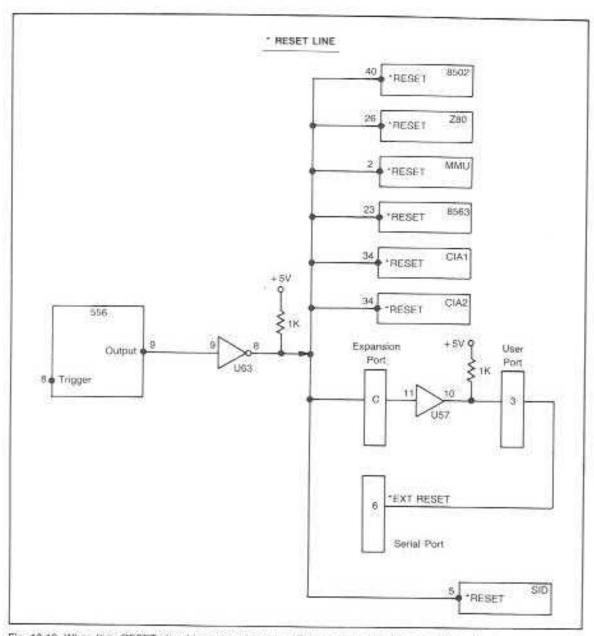

| 8  | Other Integrated Circuits  The 7406 Hex Inverters—The 7407 Hex Buffer/Drivers—The 74LS08 Quad 2-Input AND Gates—The 74LS00 and 74LS03 NAND Gates—The 74F32 and 74LS32 Quad 2-Input OR Gates—The 74LS74 Dual D Flip-Flop—The 74LS138 1-of-8 Decoder—The 74LS257 Multiplexers—The 74LS373 Octal Latches—The 74LS244 Octal Drivers—The Transceiver 74F245—The Schmitt Trigger 74LS14—The 4066 Quad Bilateral Switch—The 556 Dual Timer—Other Chip-Like Components | 118 |

| 9  | The System Block Diagram  Block Diagram—The 8502 and Dynamic RAM—The MPU and ROM—MPA and CIA Interface—The MPU and VIC—The MPU and SID—The MPU and the Video Controller                                                                                                                                                                                                                                                                                        | 150 |

| 10 | Servicing the Logic Gates  Decimal and Binary—Hexadecimal—Peek and Poke—Gates—Gate Testing Techniques                                                                                                                                                                                                                                                                                                                                                          | 167 |

| 11 | Servicing Digital Registers  Flip-Flops—Computing Registers                                                                                                                                                                                                                                                                                                                                                                                                    | 188 |

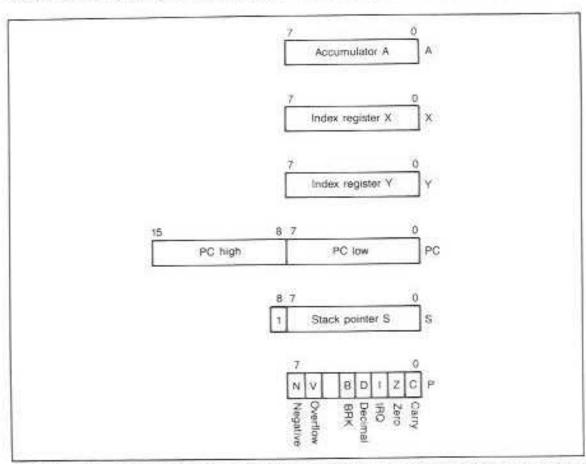

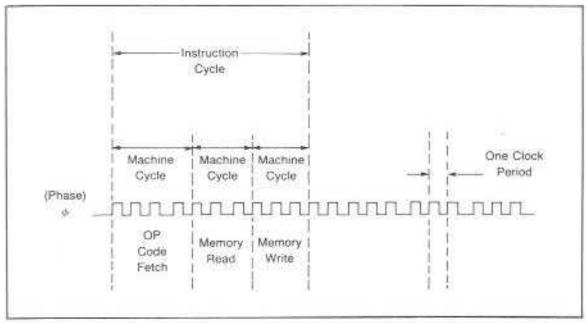

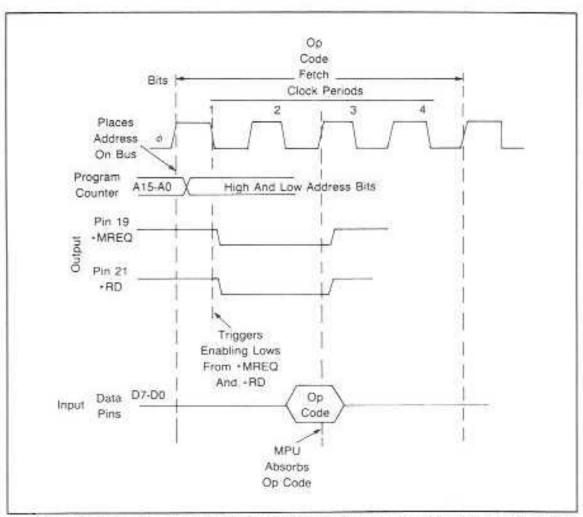

| 12 | 8502 Microprocessor  Address and Data Bus Lines—Stack—Arithmetic Logic Unit—Accumulator—Instruction Set—Index Registers—Flag Register—The 8502 Signals—Testing                                                                                                                                                                                                                                                                                                 | 207 |

| 13 | Z80 Coprocessor Z80 Block Diagram—Z80 Schematic Diagram—Z80 Instruction Set—Z80 Connections—The Computer Won't Start                                                                                                                                                                                                                                                                                                                                           | 231 |

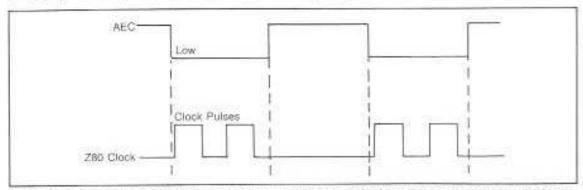

| 14 | Programmed Logic Array PLA Internals—PLA Pinout                                                                                                                                                                                                                                                                                                                                                                                                                | 240 |

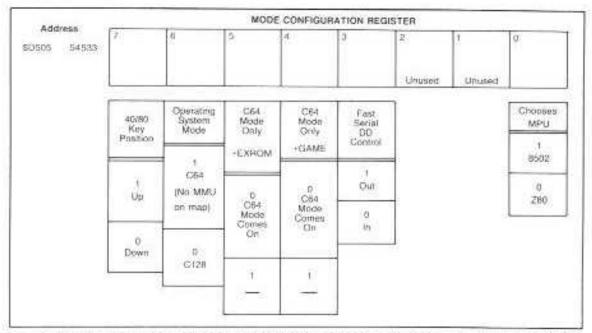

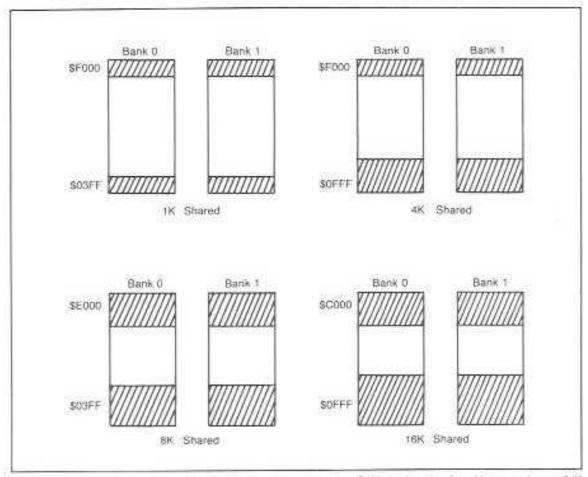

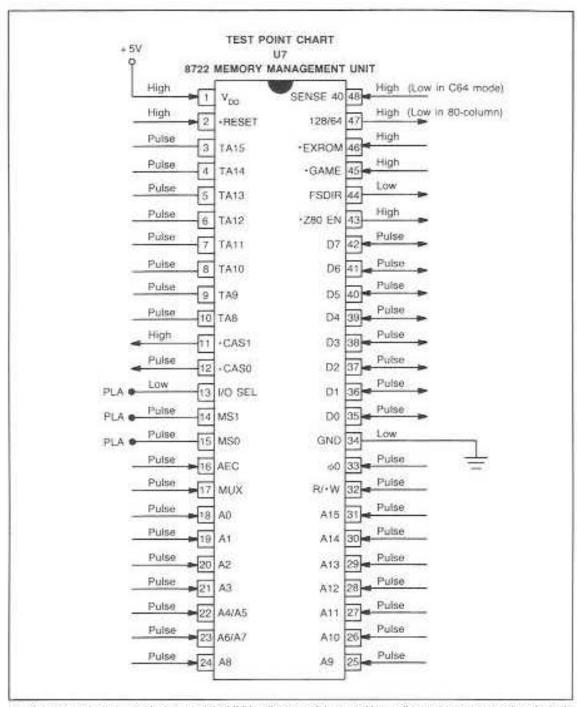

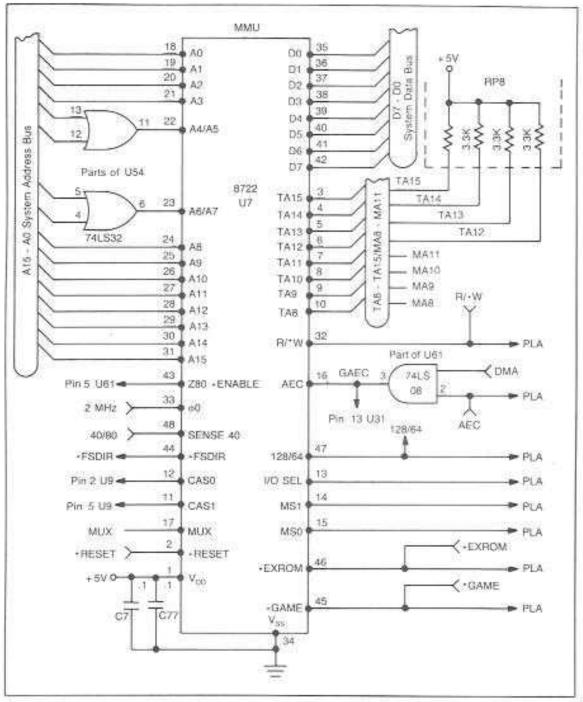

| 15 | Memory Management Unit  Bank Contents—MMU Registers—Mode Configuration Register—Ram Configuration Register—The Page Pointers—Version Register—The MMU Pinout                                                                                                                                                                                                                                                                                                   | 249 |

| 16 | All the Memory Maps The C128 Maps—The C64 Maps—The CP/M Map—PEEK and POKE—MEMORY and FILL                                                                                                                                                                                                                                                                                                                                                                      | 266 |

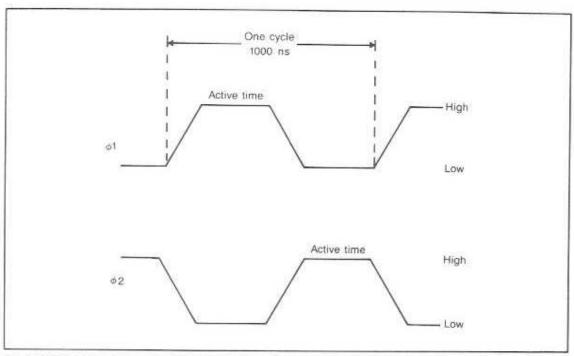

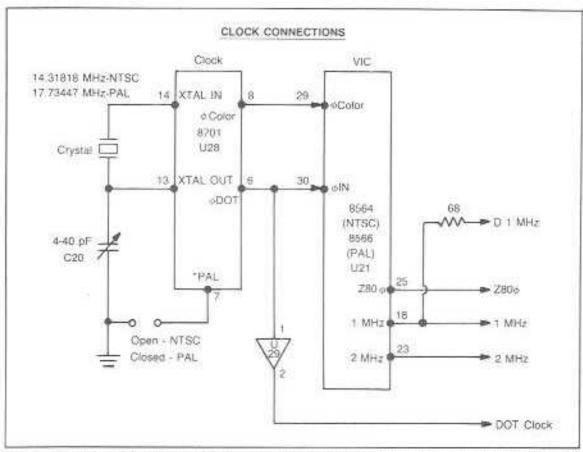

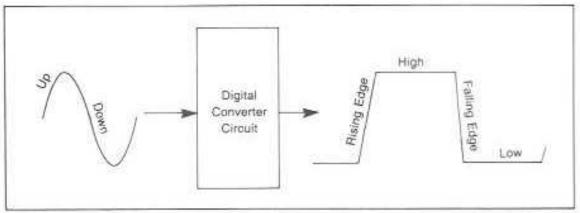

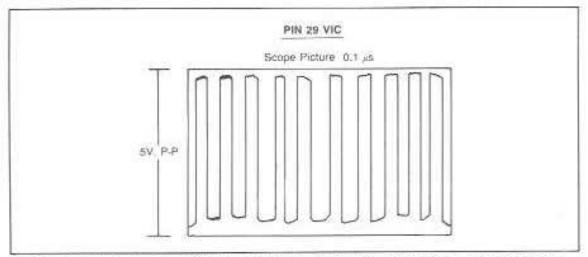

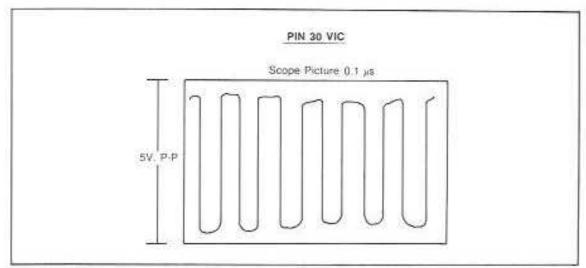

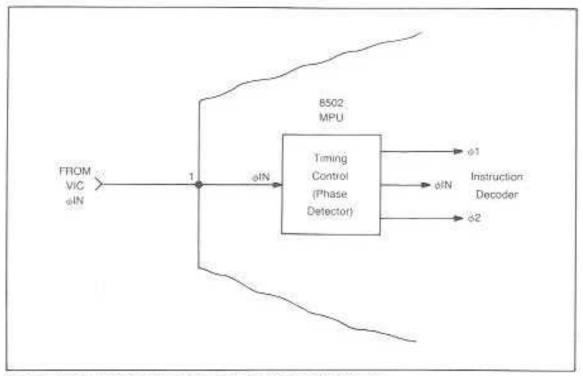

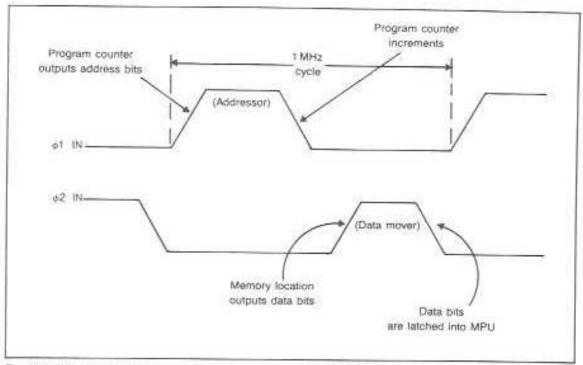

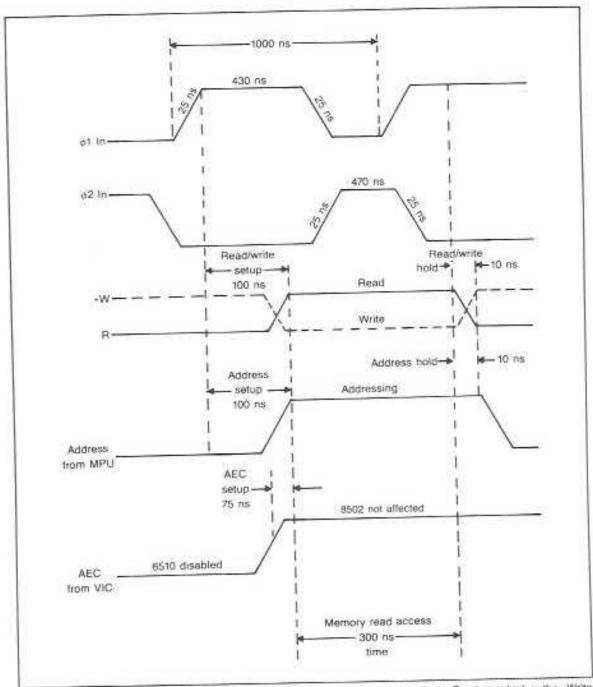

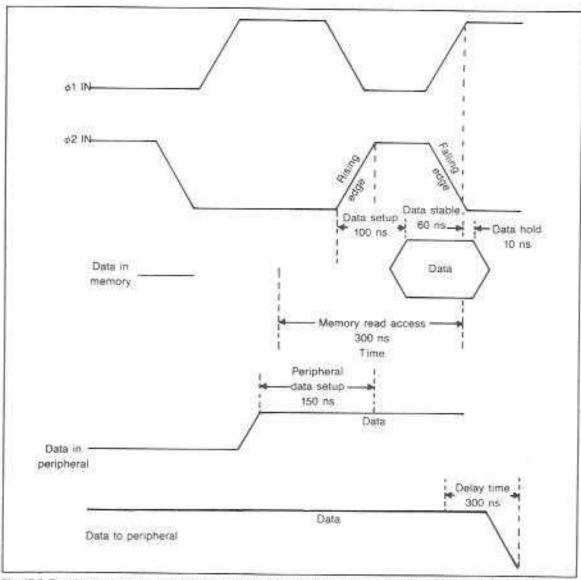

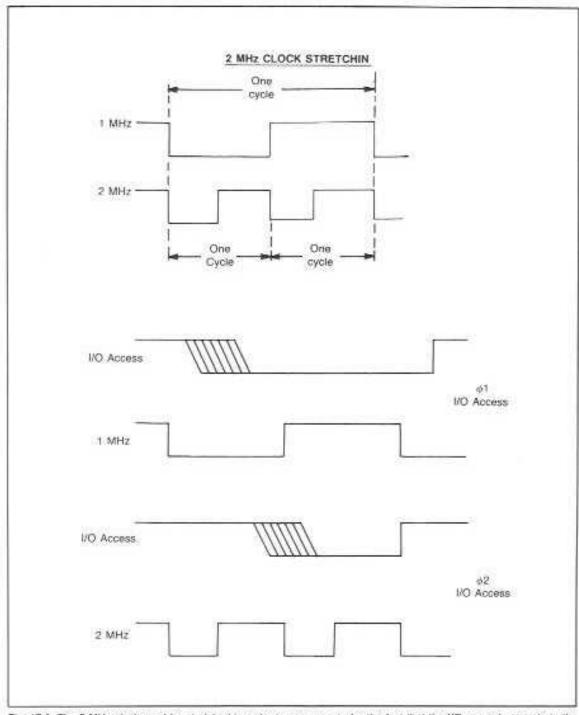

| 17 | The Clocks Sine Wave to Square Wave—8502 Timing Control—Other Timing Signals—The Z80 Timing—Testing the Clock                                                                                                                                                                                                                                                                                                                                                  | 280 |

| 18 | Address, Data and Control Buses  All Those Address Buses—The Data Bus—The 80-Column Display Bus—The Control Lines—Testing the Bus Lines                                                                                                                                                                                                                                                                                                                        | 298 |

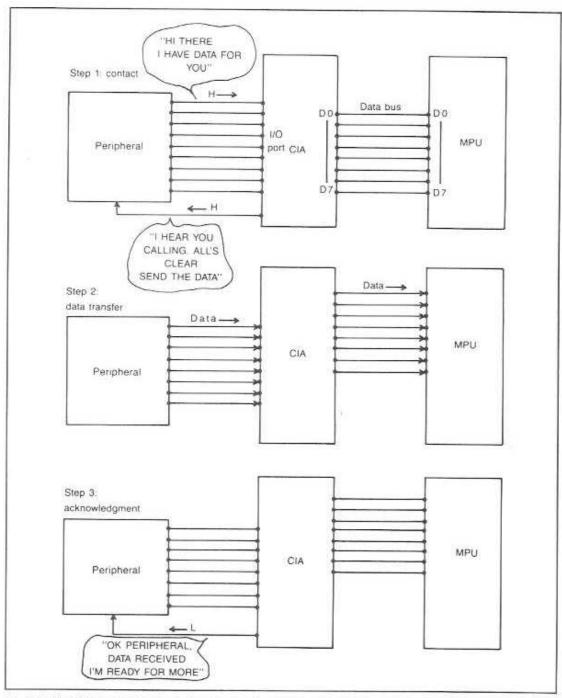

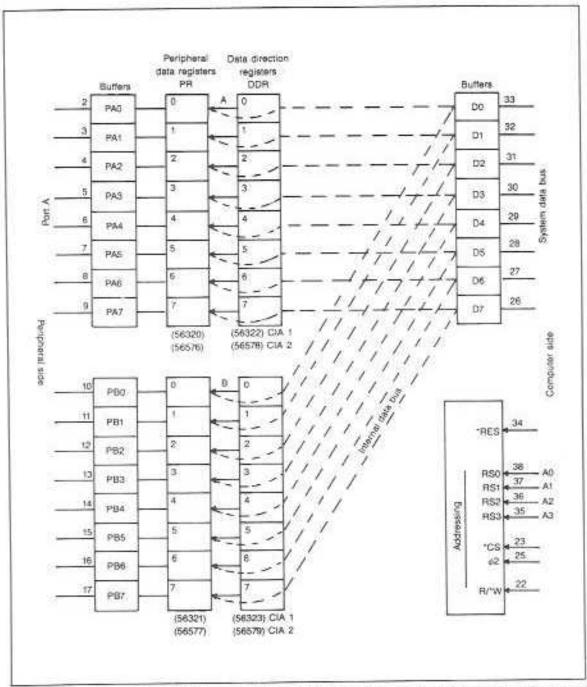

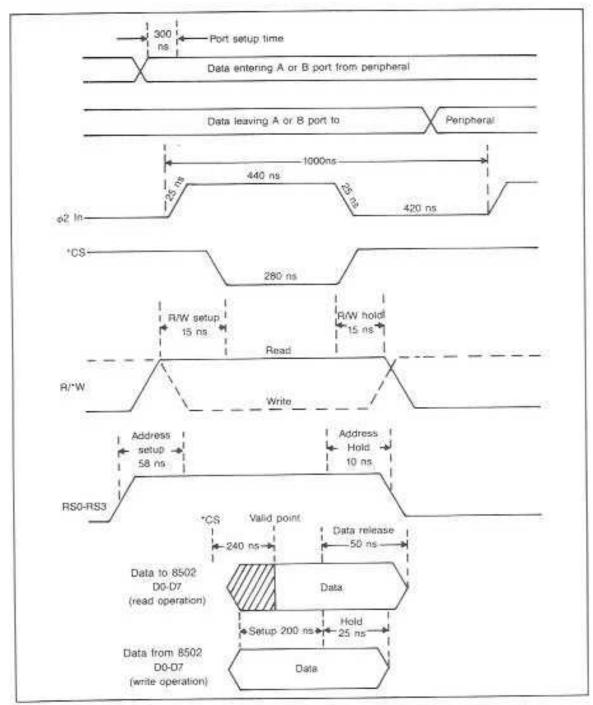

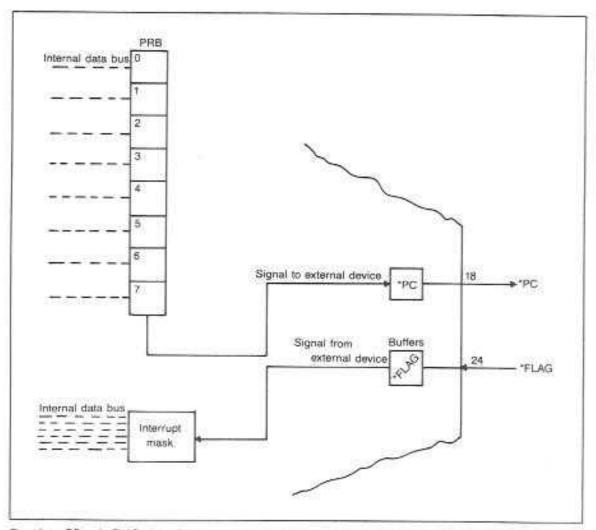

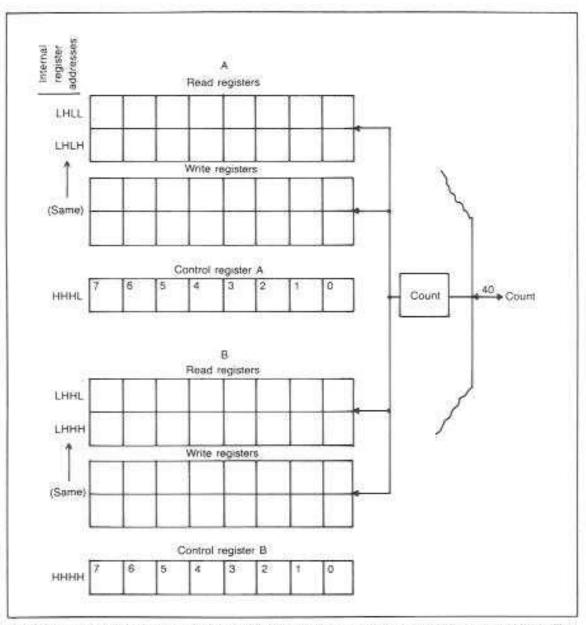

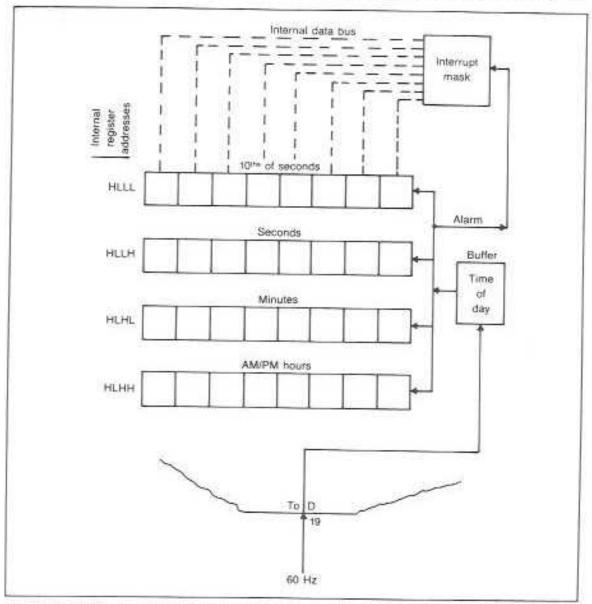

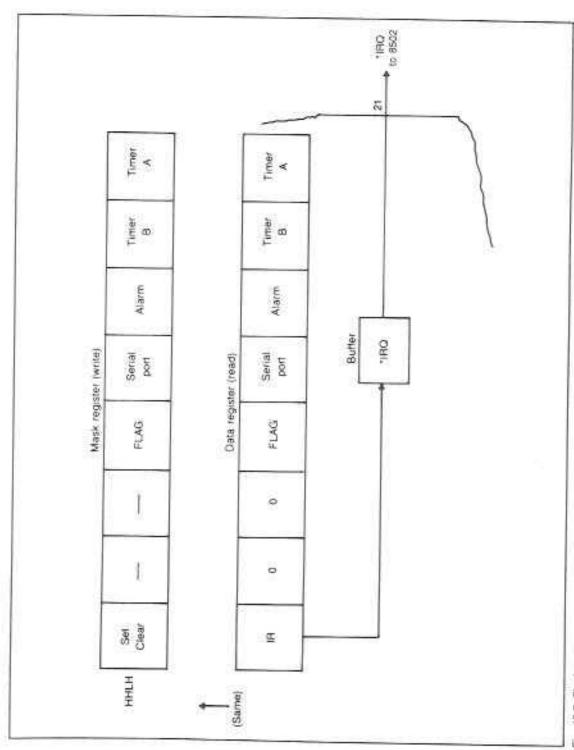

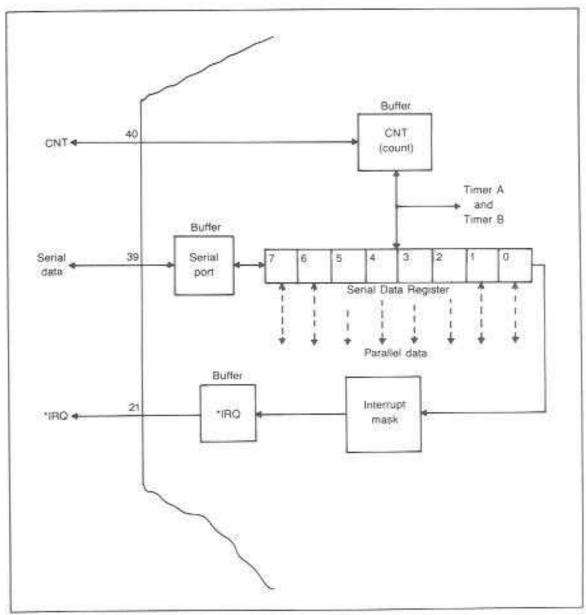

| 19 | Complex Interface Adapters  Addressing and Controlling—Internal Data Transfer—Timing—I/O Ports—•PC and •FLAG Pins—Timers — Real Time Clock — Interrupt Control Register — Serial Data Register — Operation — CIA1—CIA2—Testing                                                                                                                                                                                                                                 | 321 |

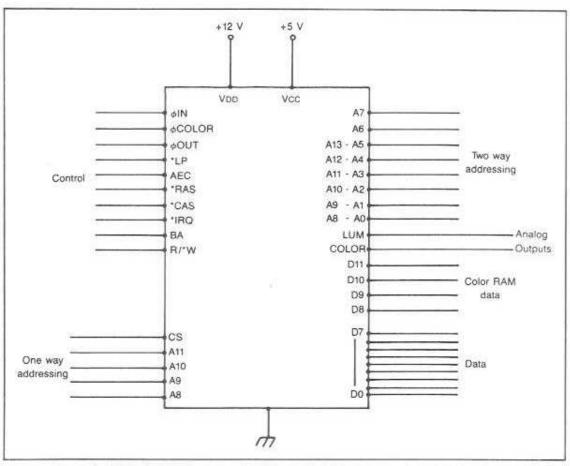

| 20         | 8564 Video Interface Chip                                                                           | 337 |

|------------|-----------------------------------------------------------------------------------------------------|-----|

| 20         | VIC Graphics—VIC Pin-by-Pin Operation—Sprites—Other VIC Features—Light Pen—Video Output—<br>Testing |     |

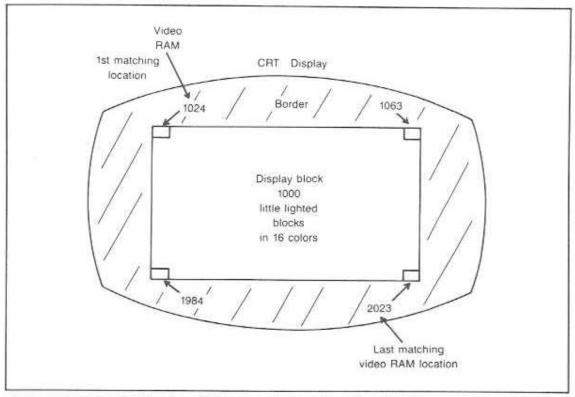

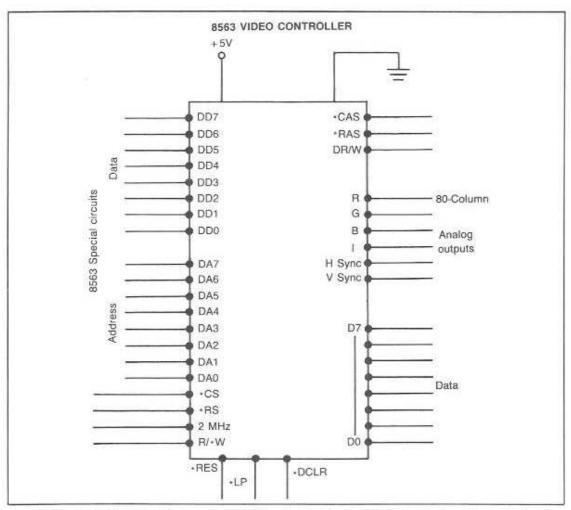

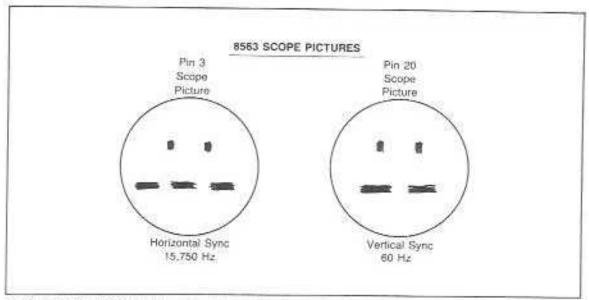

| 21         | 80-Column 8563 Video Controller                                                                     | 354 |

| <b>—</b> 1 | The 8563 RAM—Pin-by-Pin Checkout                                                                    |     |

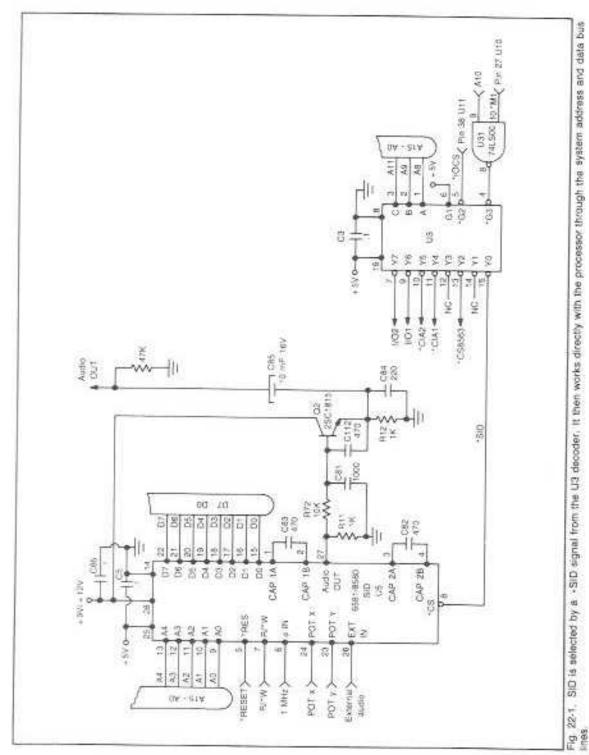

| 22         | Sound Interface Device                                                                              | 364 |

| And And    | Pinout—Special Inputs—Operation—Registers—Timing—Testing                                            |     |

| 23         | Inputs and Outputs                                                                                  | 379 |

| -0         | Checking Out I/O Troubles—RF Modulator                                                              |     |

| 24         | The Power Supply                                                                                    | 398 |

|            | First StepPoint-by-Point Checkout                                                                   |     |

|            | Appendix                                                                                            | 406 |

|            | Index                                                                                               | 431 |

|            |                                                                                                     |     |

## Acknowledgments

I'd like to thank my wife Lea for running interference and fielding interruptions, as usual, while I wrote the book. I would also like to thank my favorite photographer, my son-in-law, Michael Gorzeck, for taking the step-by-step disassembly photos

in Chapter 2. I hope your computing is uninterrupted, but should your C128 start acting up, perhaps this book will be directly responsible for getting it up and working once again.

#### Test Point Charts

| U Number | Generic Number | Given Name                | Figure | Table |

|----------|----------------|---------------------------|--------|-------|

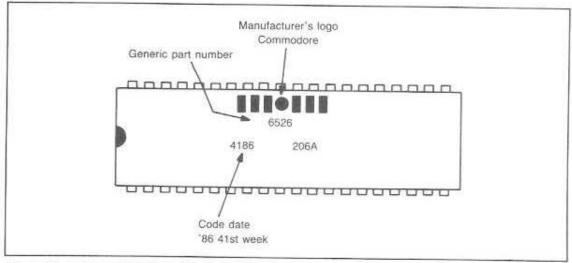

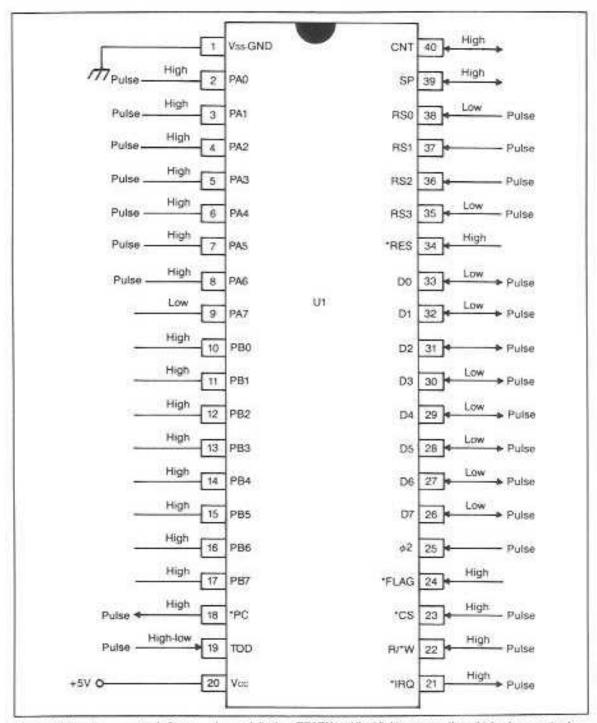

| Ut       | 6526           | Complex Interface Adapter | 19-9   |       |

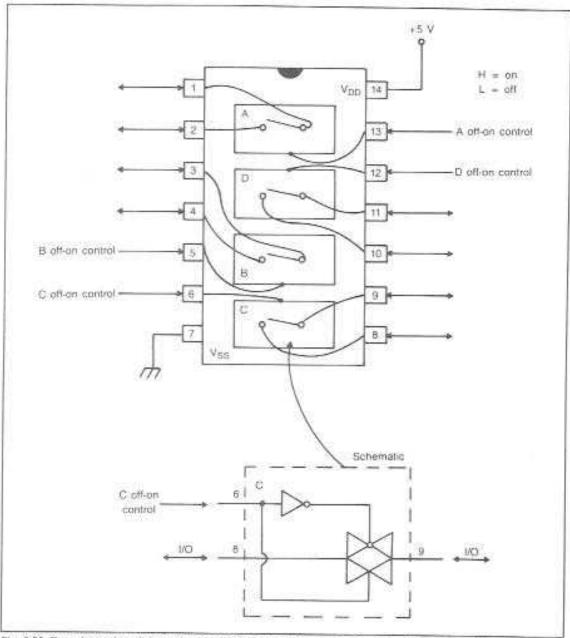

| U2       | 4066B          | Quad Bilateral Switch     | 8-26   | 8-10  |

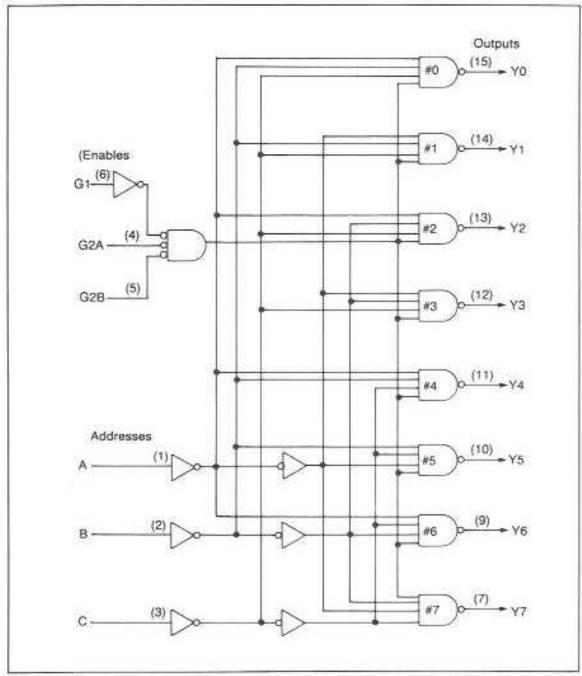

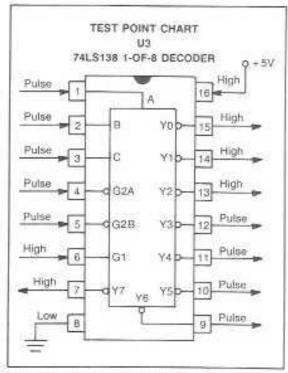

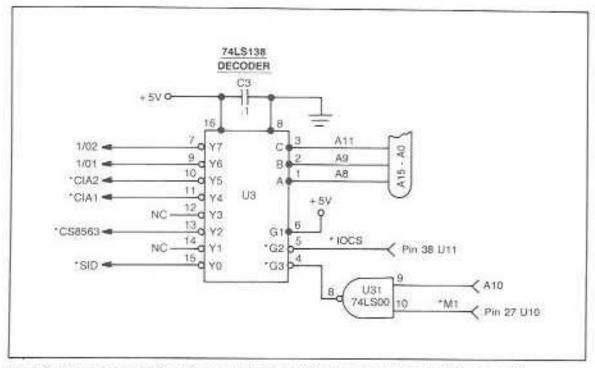

| U3       | 74LS138        | 1-of-8 Decoder            | 8-16   |       |

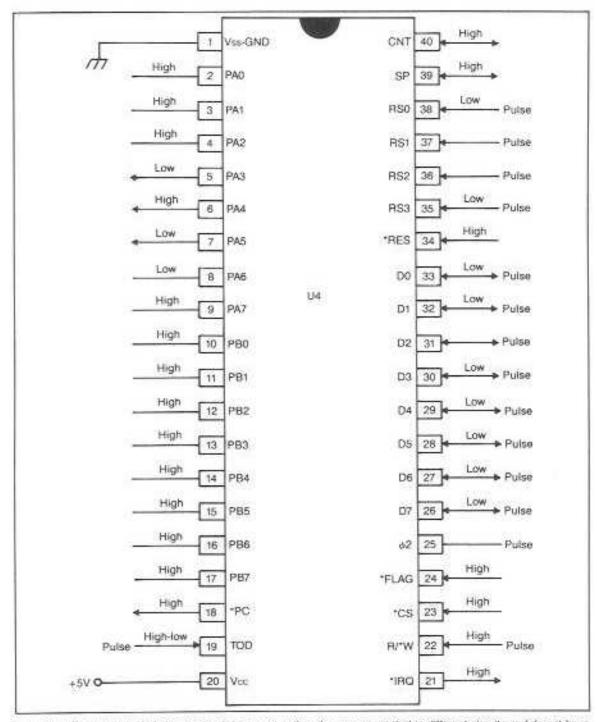

| U4       | 6526           | Complex Interface Adapter | 19-10  |       |

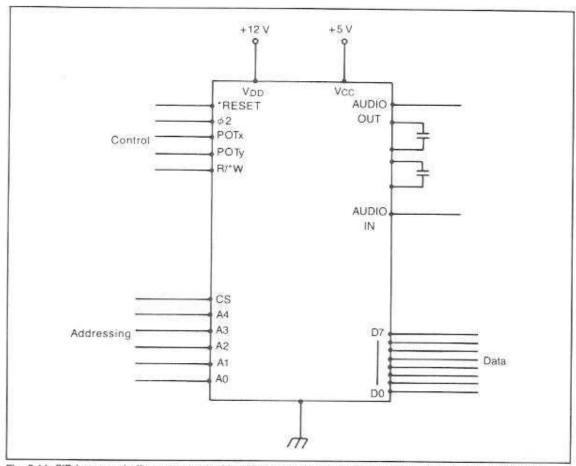

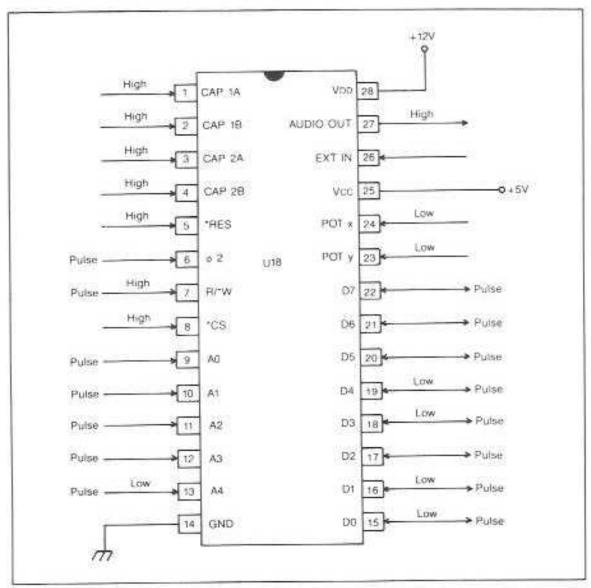

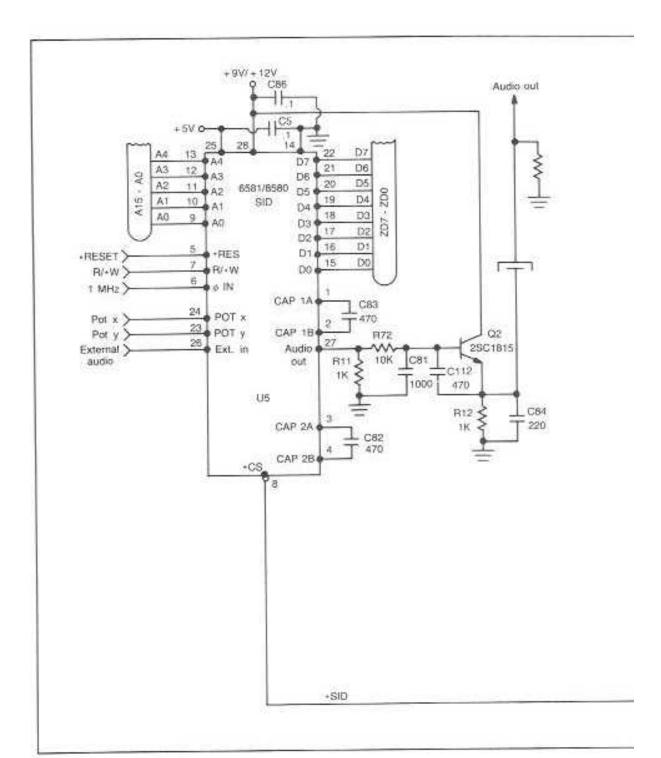

| U5       | 6581           | Sound Interface Chip      | 22-2   |       |

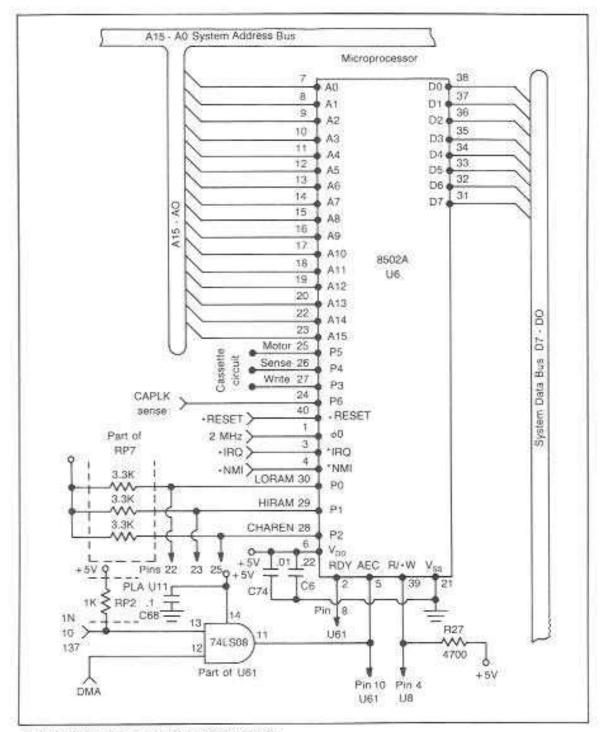

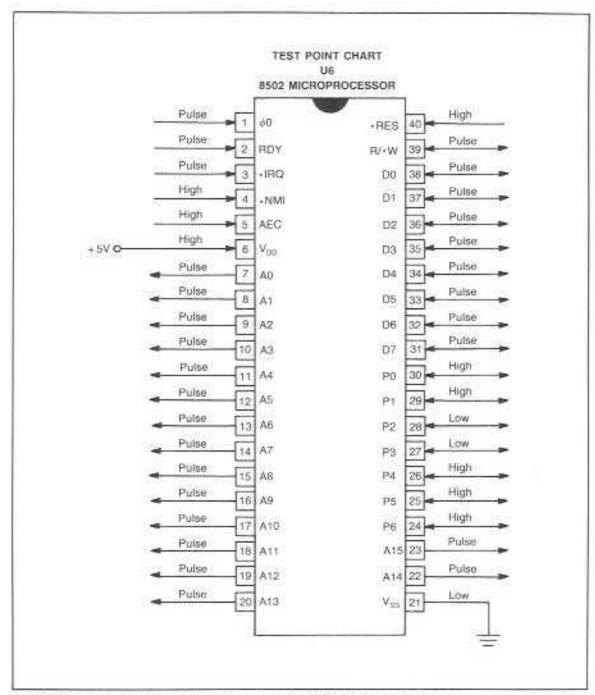

| U6       | 8502           | Microprocessor            | 12-20  |       |

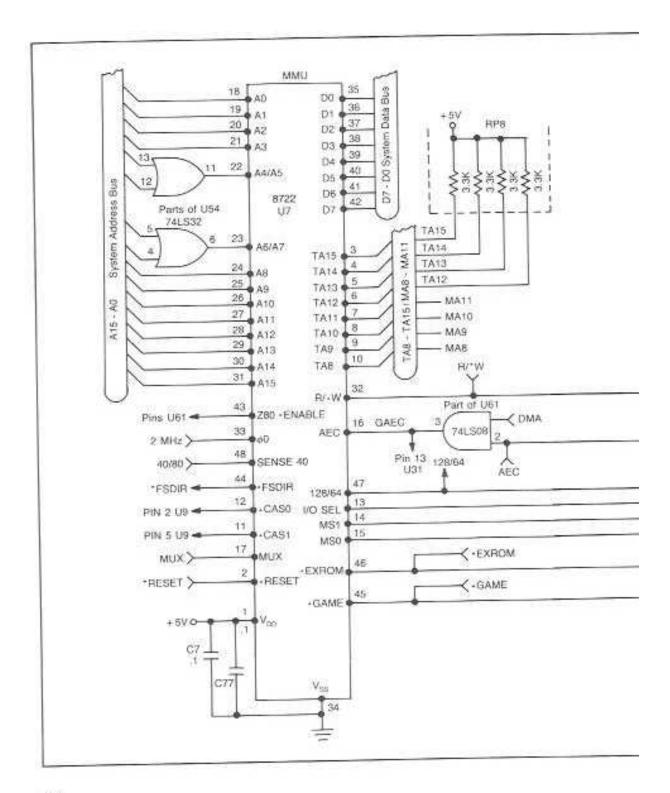

| U7       | 8722           | Memory Management Unit    | 15-6   |       |

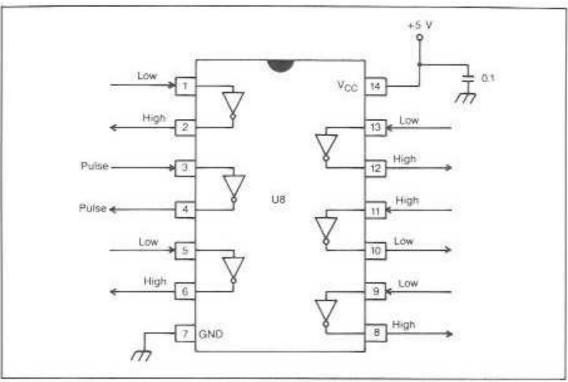

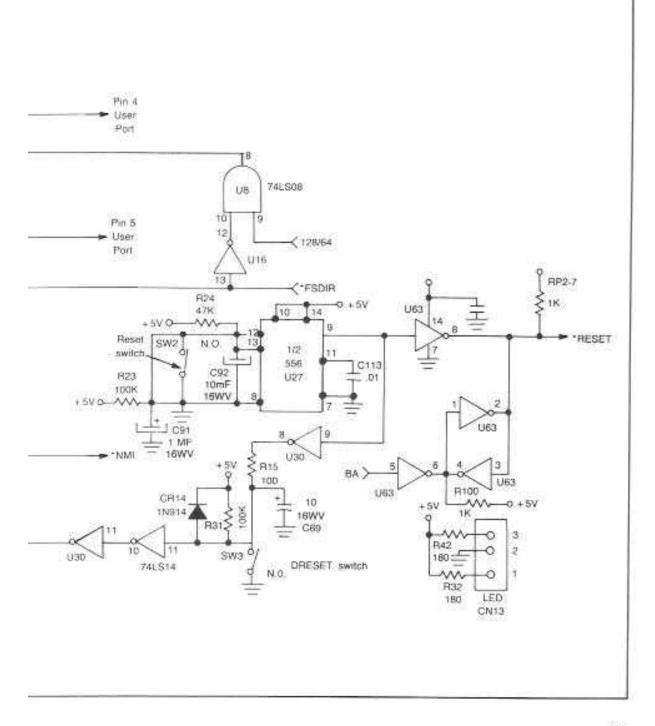

| U8       | 74LS08         | Quad 2-Input AND Gate     | 8-6    | 8-3   |

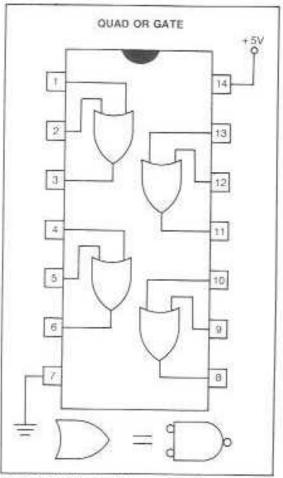

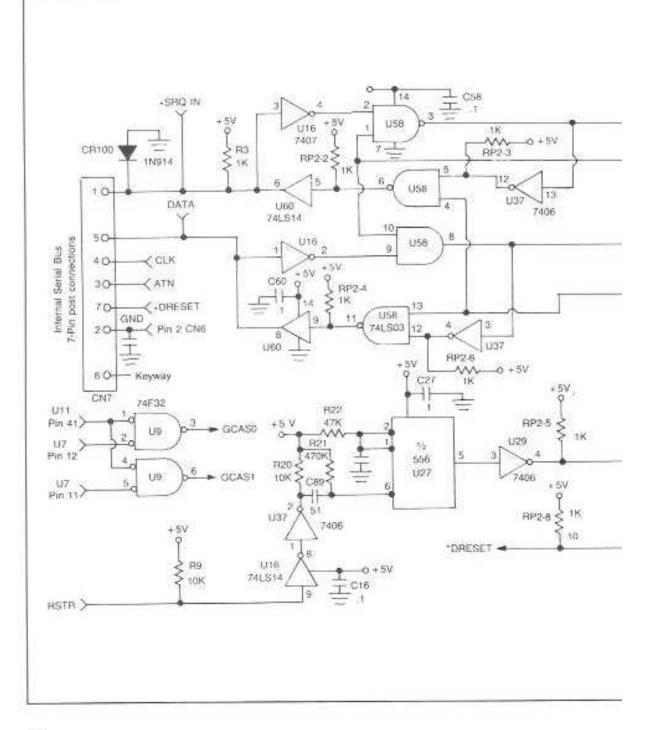

| U9       | 74F32          | Quad 2-Input OR Gate      | 8-13   | 8-5   |

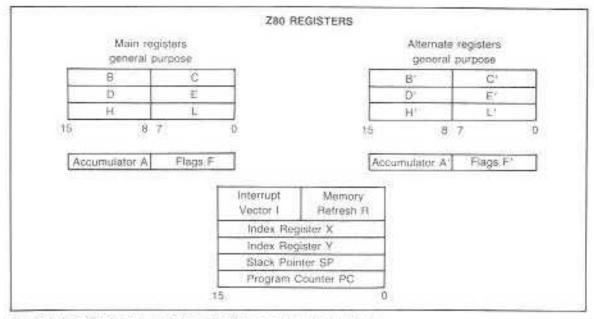

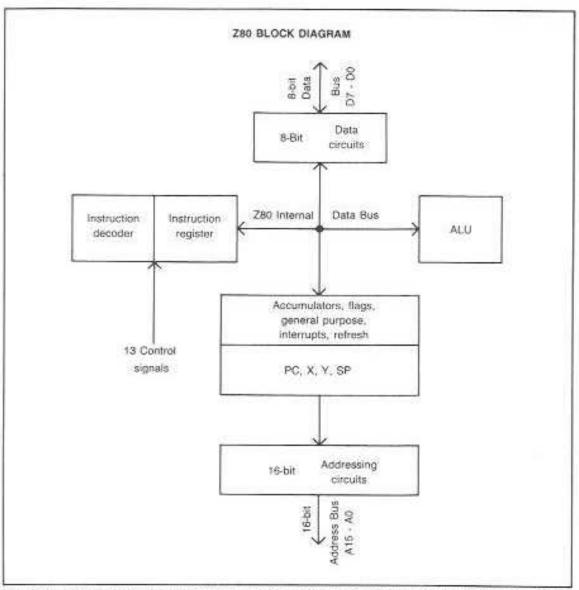

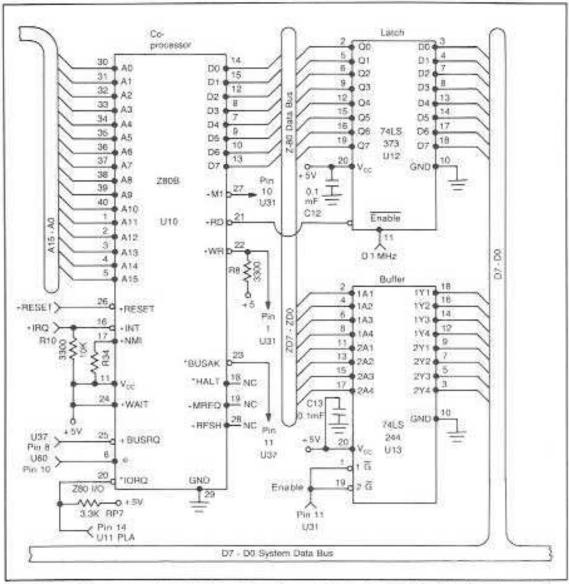

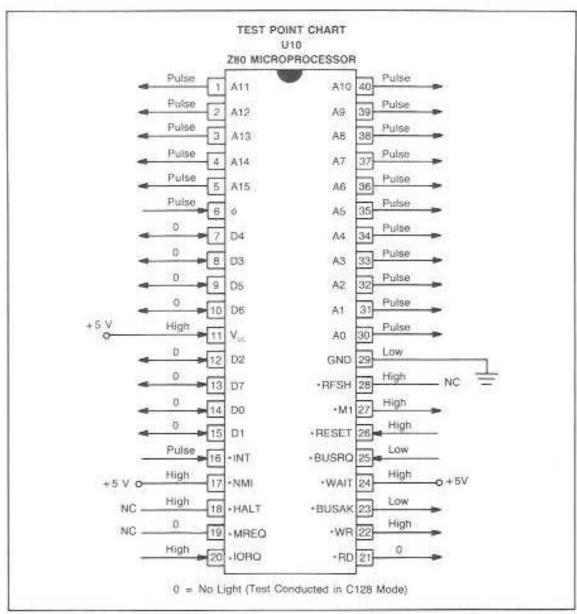

| U10      | Z80            | Microprocessor            | 13-4   |       |

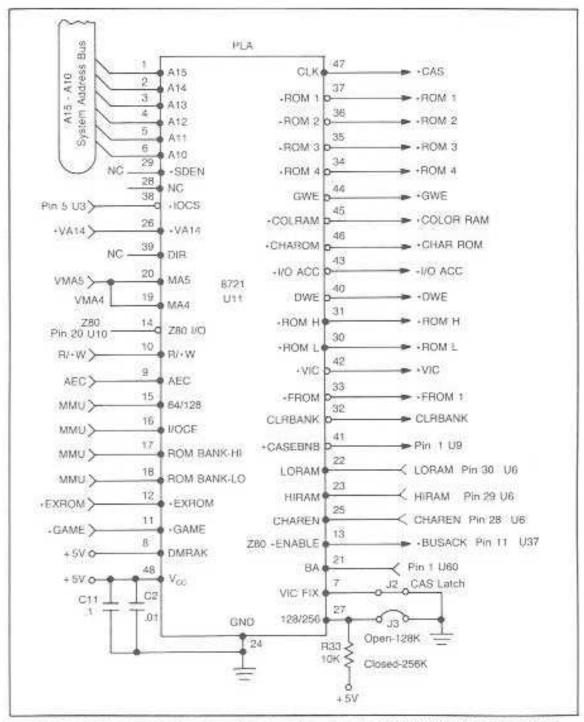

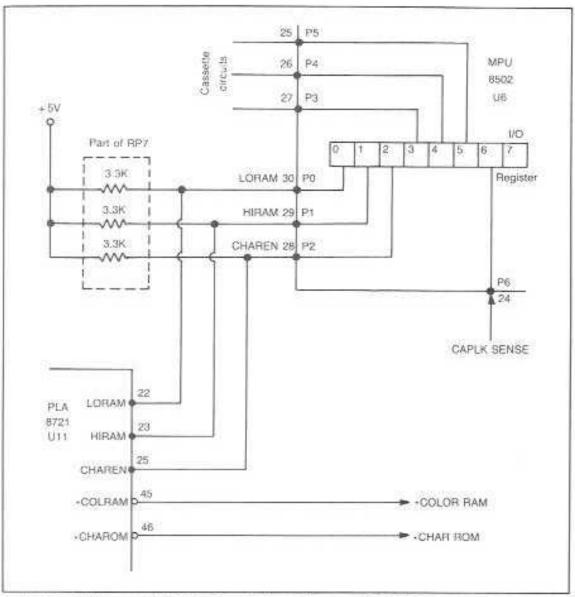

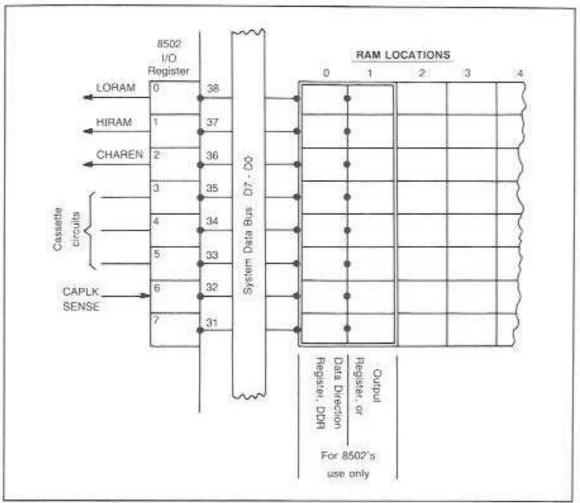

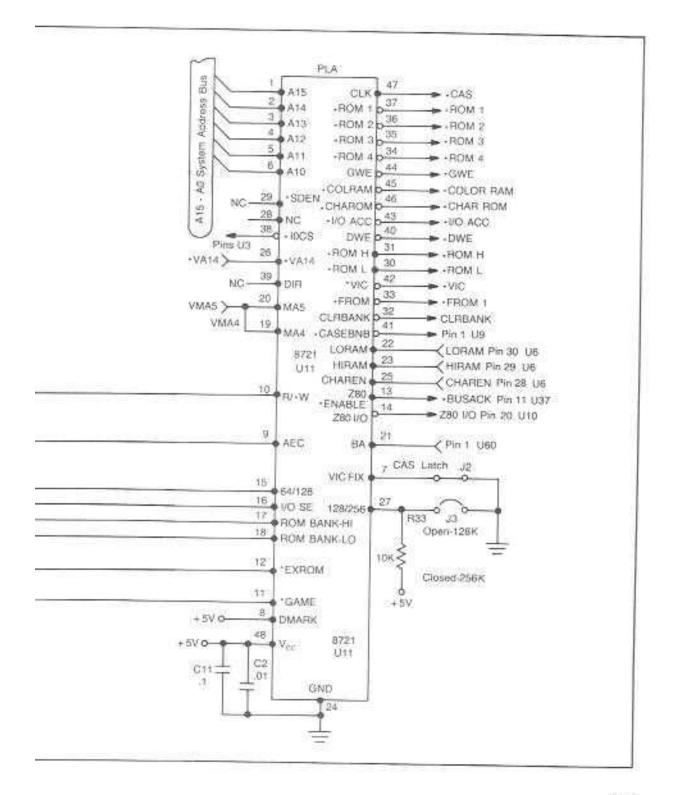

| U11      | 8721           | Programmed Logic Array    | 14-6   |       |

| U12      | 74LS373        | Octal 3-State D Latch     | 8-21   | 8-8   |

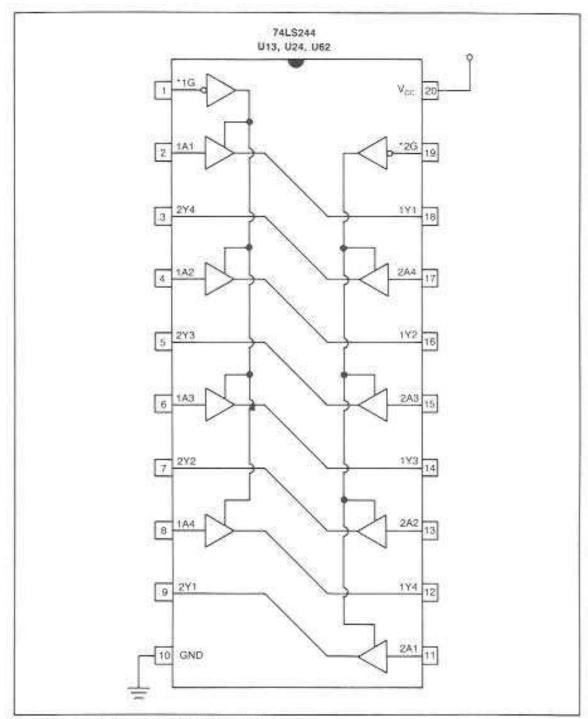

| U13      | 74LS244        | Octal 3-State Driver      | 8-22   | 8-9   |

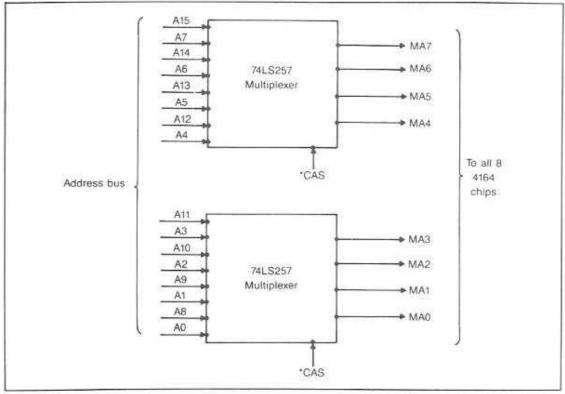

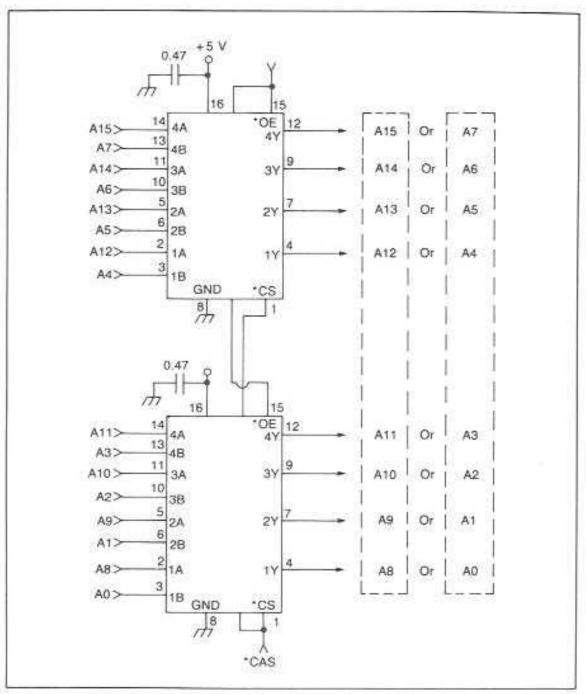

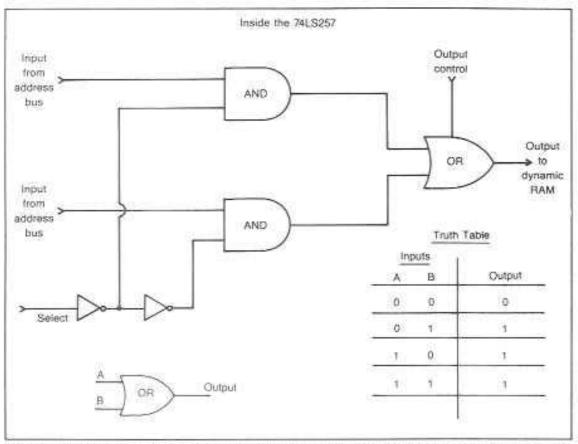

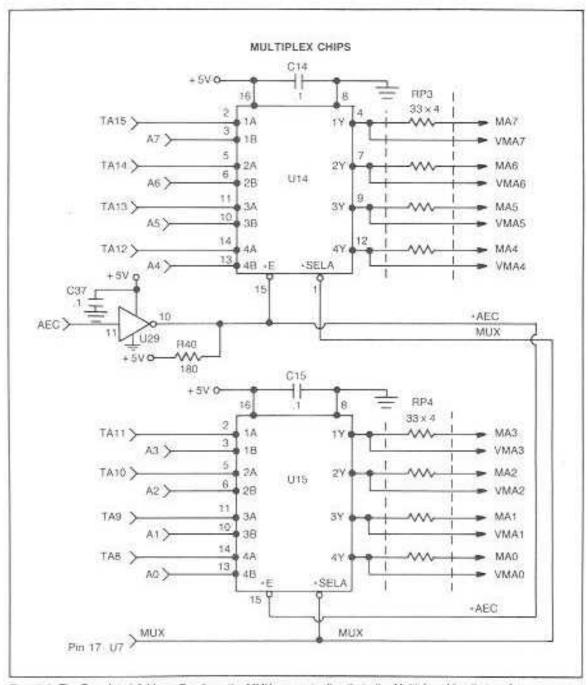

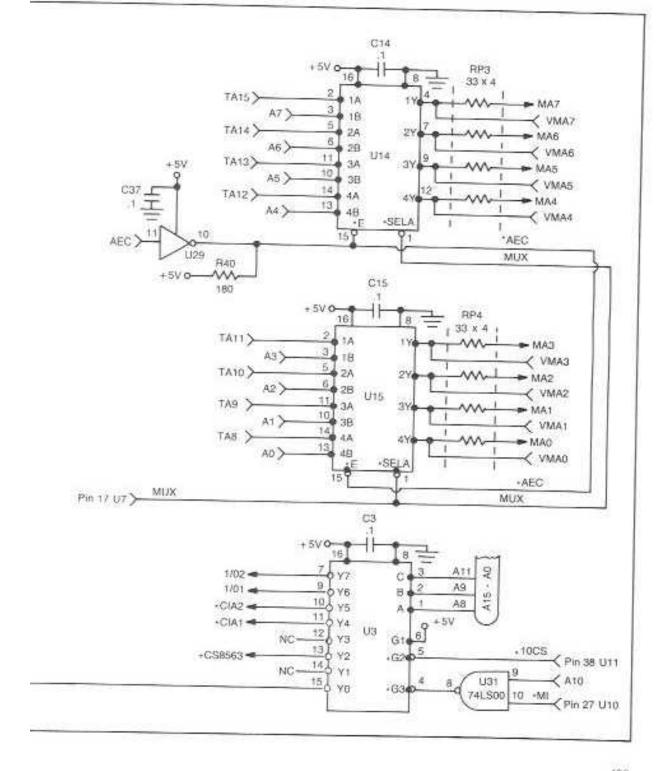

| U14      | 74LS257        | Quad 2-Input Multiplexer  | 8-19   |       |

| U15      | 74LS257        | Quad 2-Input Multiplexer  | 8-19   |       |

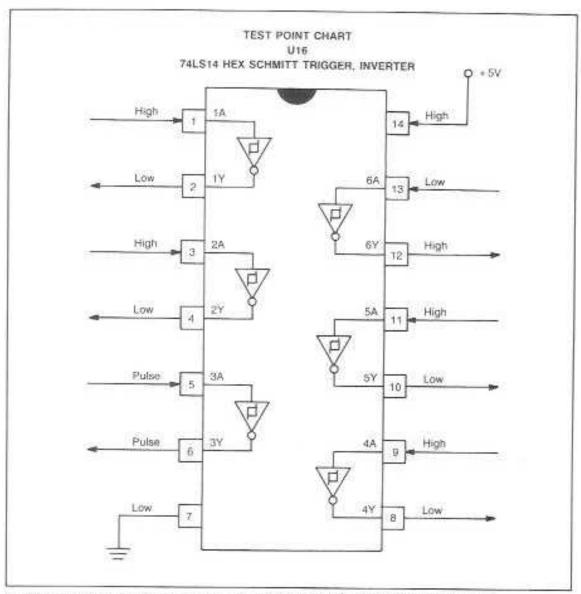

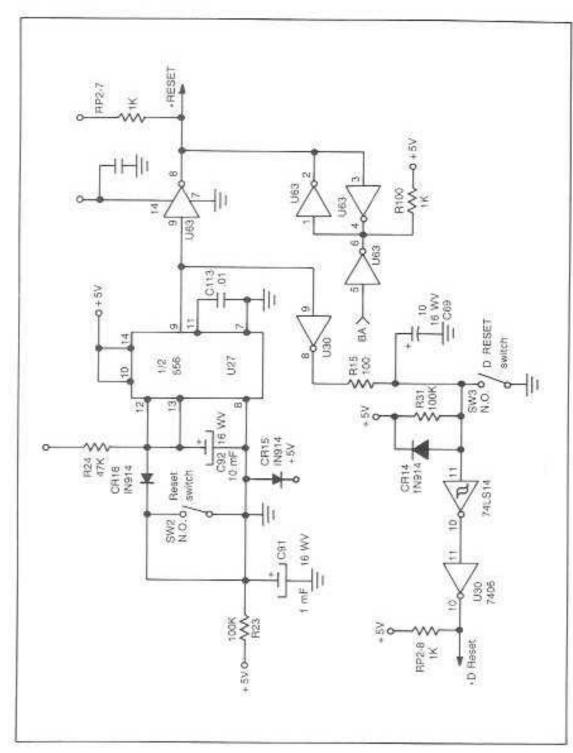

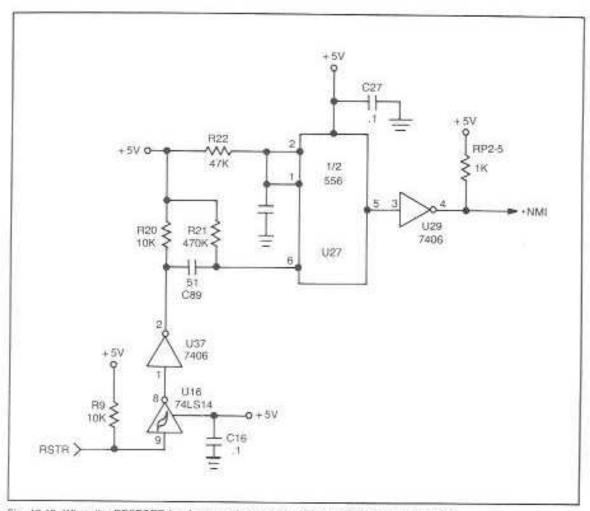

| U16      | 74LS14         | Hex Schmitt Trigger       | 8-24   |       |

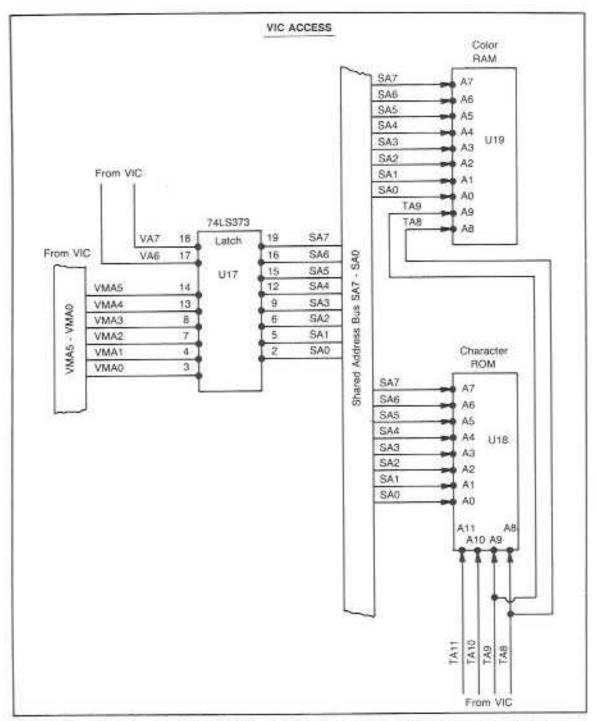

| U17      | 74LS373        | Octal 3-State D Latch     | 8-21   | 8-8   |

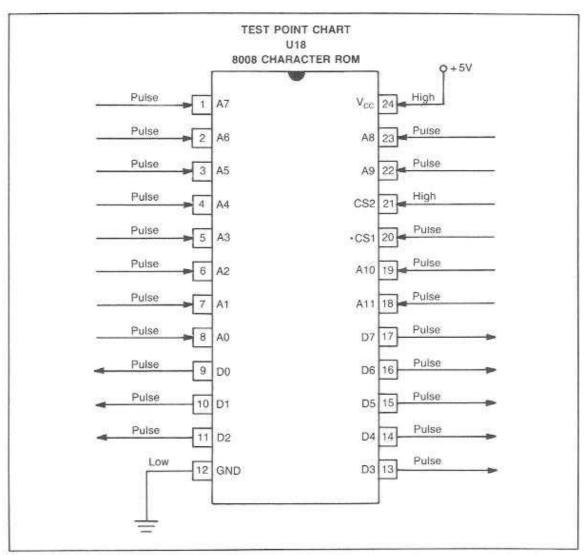

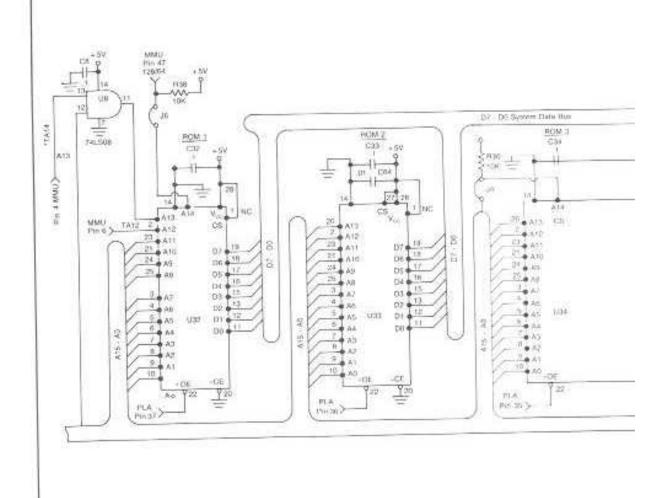

| U18      | 390059-01      | Character ROM             | 7-3    | 12020 |

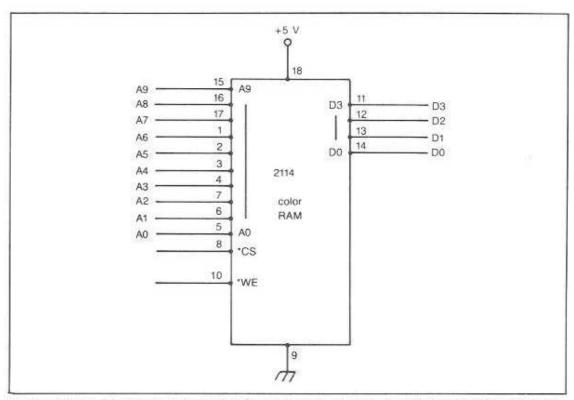

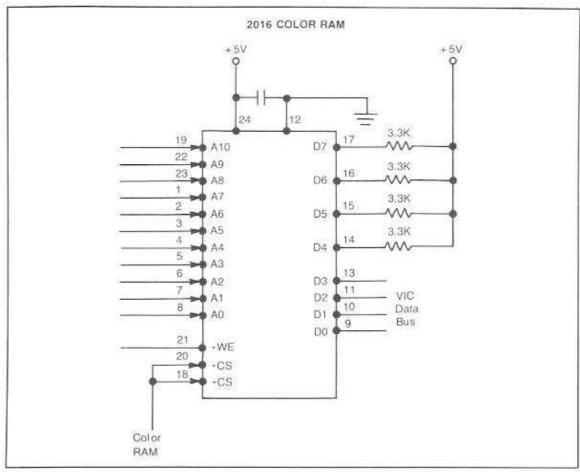

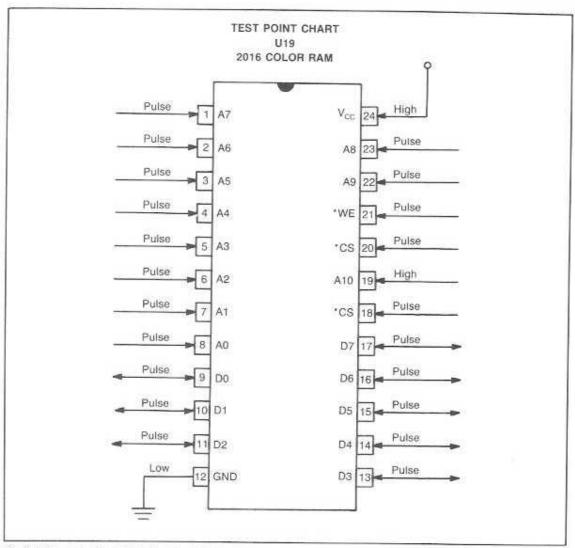

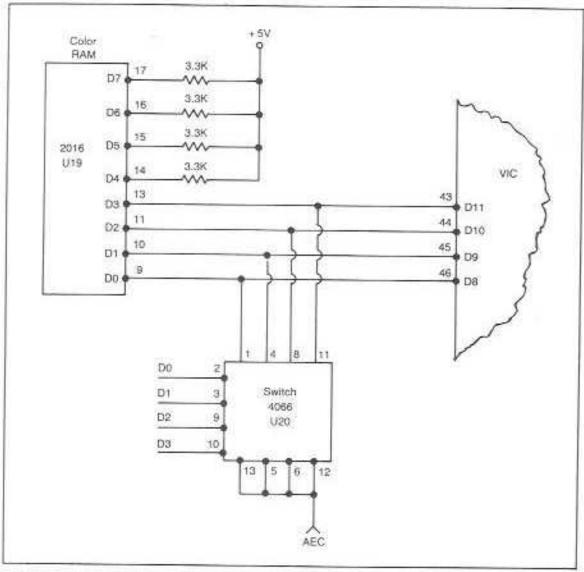

| U19      | 2016           | Color RAM                 | 6-7    |       |

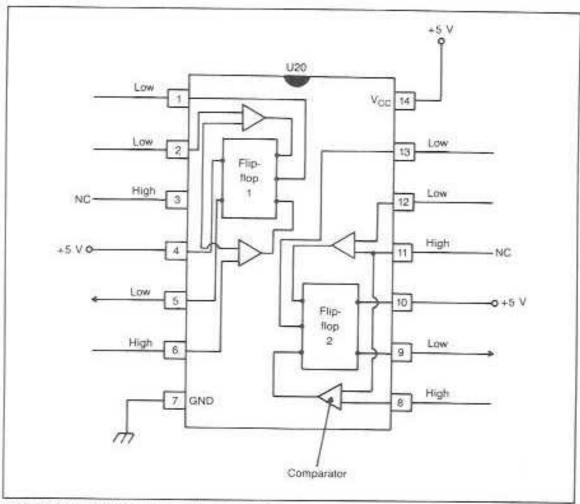

| U20      | 4066B          | Quad Bilateral Switch     | 8-26   | 8-10  |

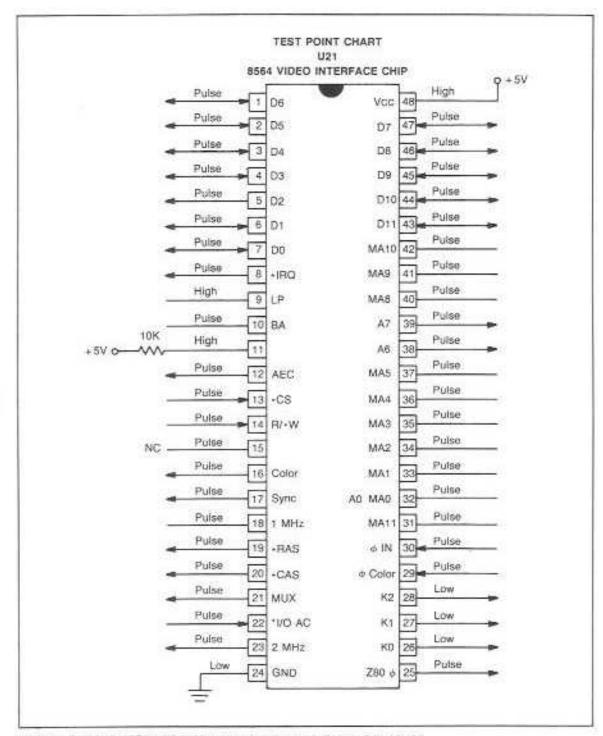

| U21      | 8564           | Video Interface Chip      | 20-1   | 0.10  |

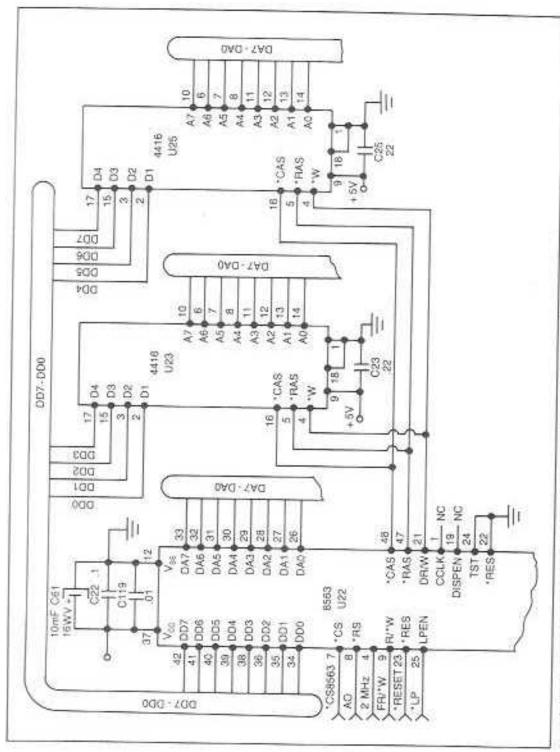

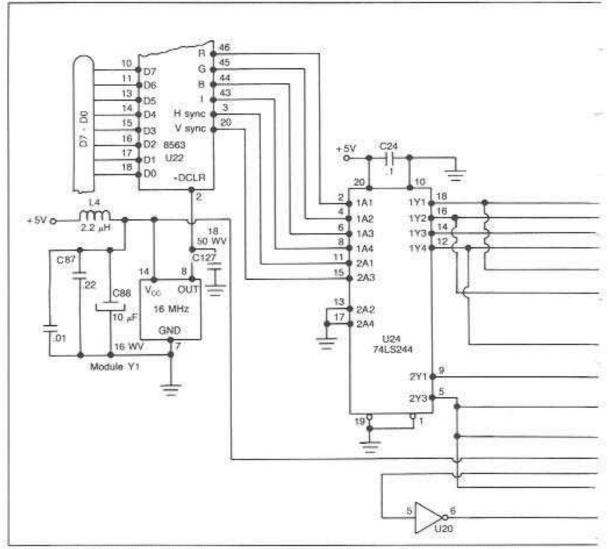

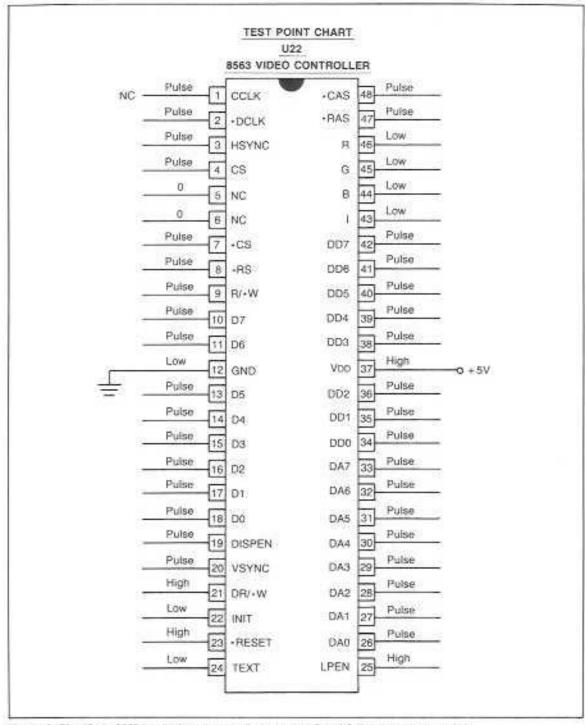

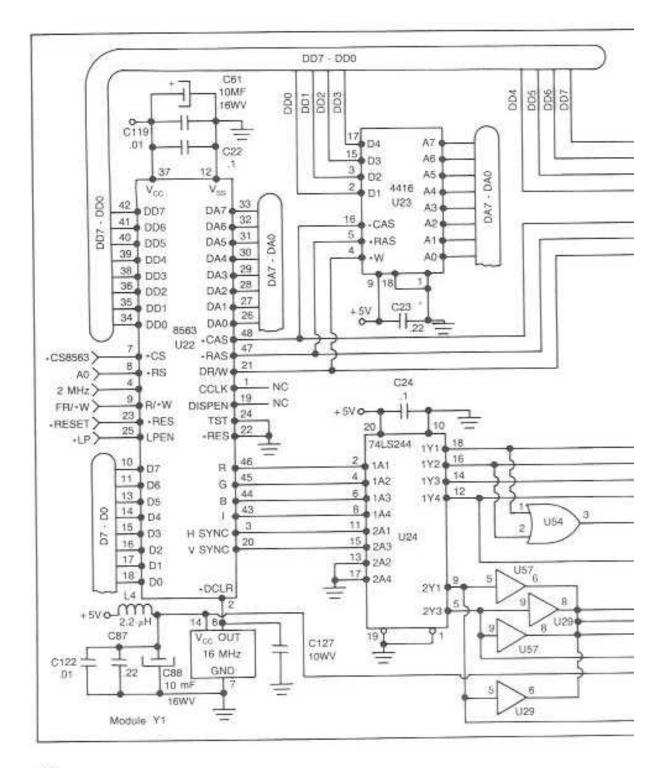

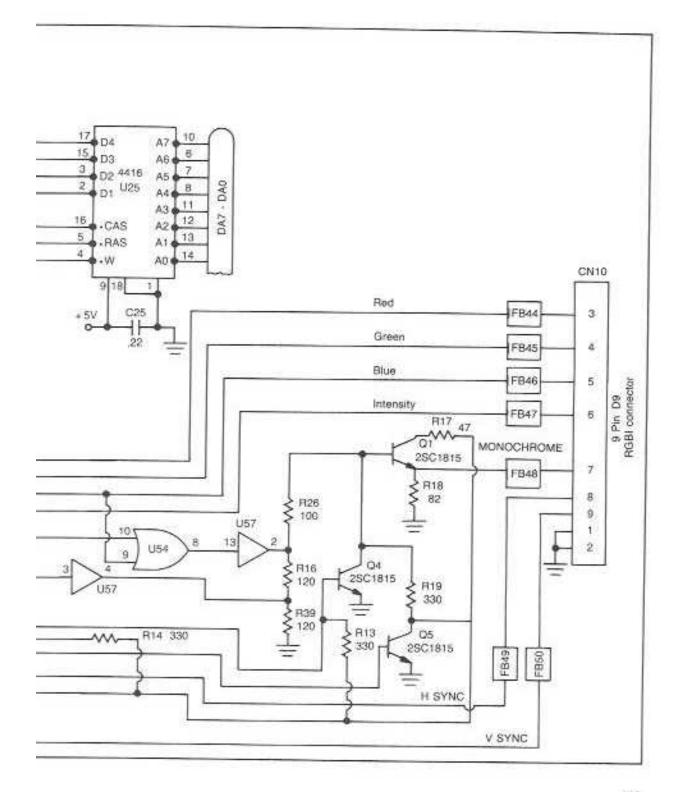

| U22      | 8563           | Video Controller          | 21-3   |       |

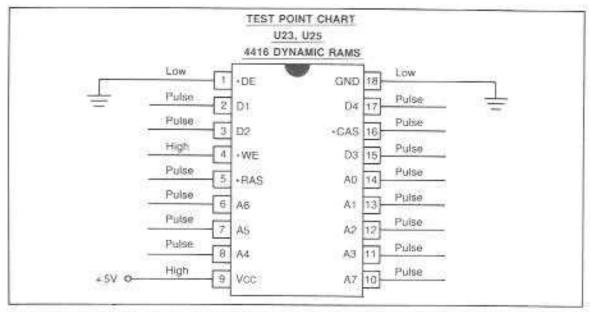

| U23      | 4416           | DRAM                      | 21-2   |       |

| U24      | 74LS244        | Octal 3-State Driver      | 8-22   | 8-9   |

| U25      | 4416           | DRAM                      | 21-2   | 0.0   |

| U26      | 74LS257        | Quad 2-Input Multiplexer  | 8-19   |       |

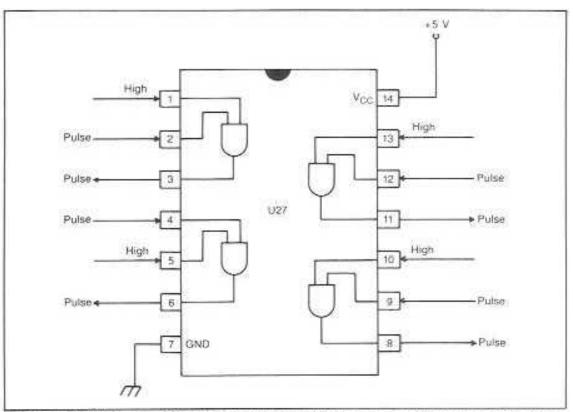

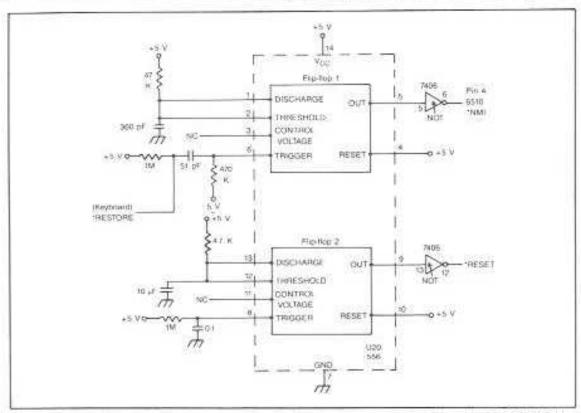

| U27      | 556            | Timer                     | 8-28   |       |

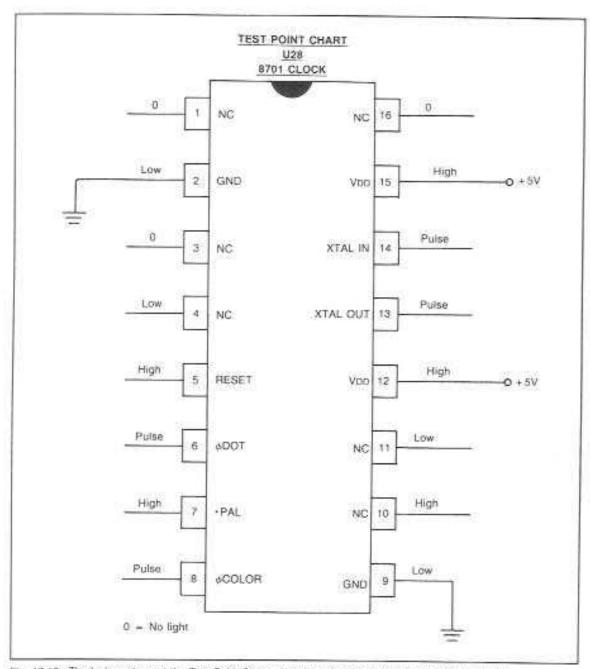

| U28      | 8701           | Clock                     | 17-16  |       |

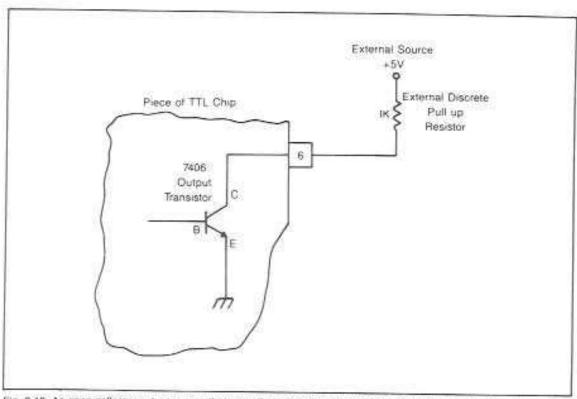

| U29      | 7406           | Hex Inverter Buffer       | 8-4    | 8-1   |

| U30      | 7406           | Hex Inverter Buffer       | 8-4    | 8-1   |

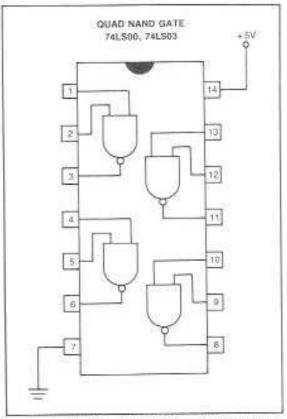

| U31      | 74LS00         | Quad 2-Input NAND Gate    | 8-9    | 8-4   |

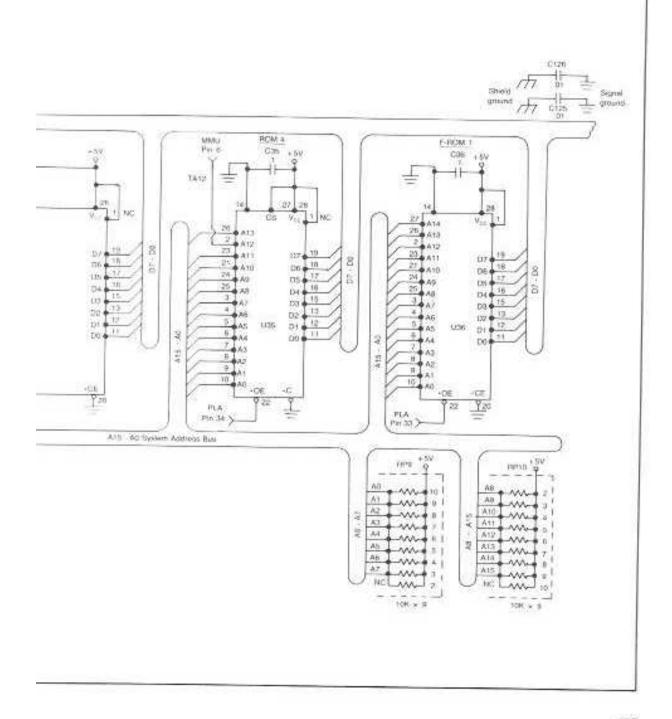

| U32      | 251913-01      | Read Only Memory          | 7-6    | 0.4   |

| U33      | 318018-02      | Read Only Memory          | 7-6    |       |

| U34      | 318019-02      | Read Only Memory          | 7-6    |       |

| U35      | 318020-03      | Read Only Memory          | 7-6    |       |

| U36      |                | r Function ROM            | 1-0    |       |

| U37      | 7406           | Hex Inverter Buffer       | 8-4    | 8-1   |

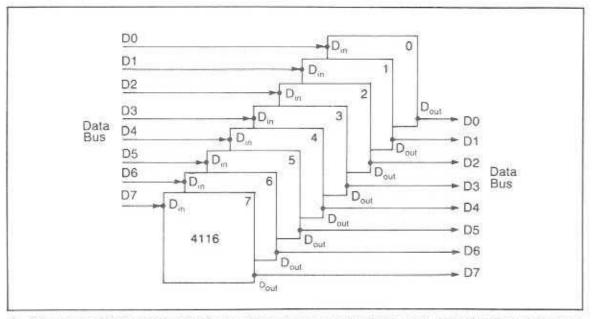

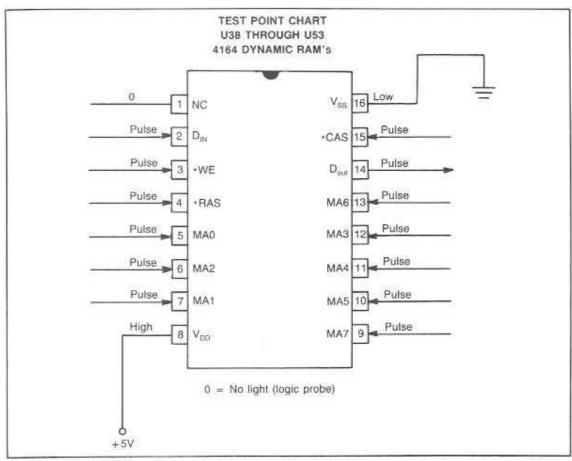

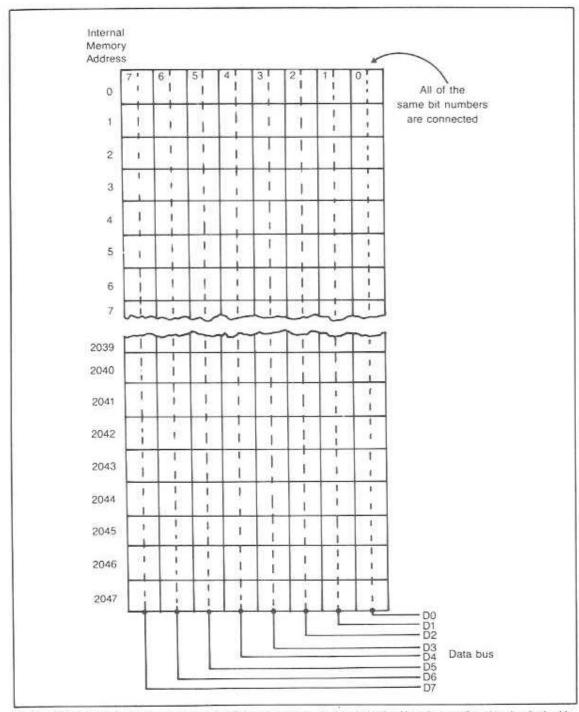

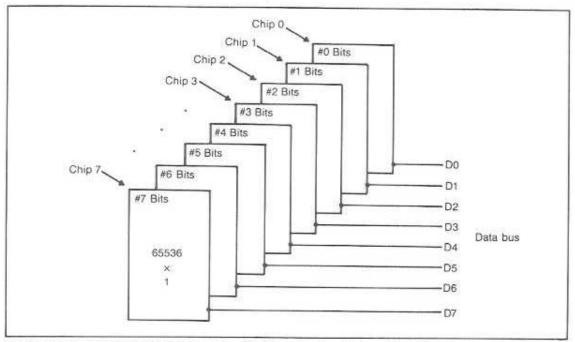

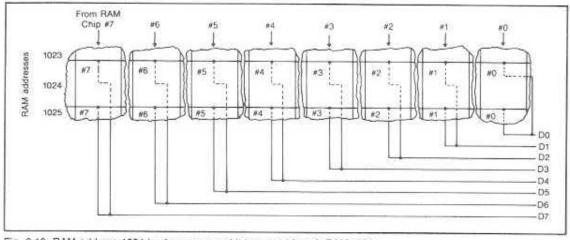

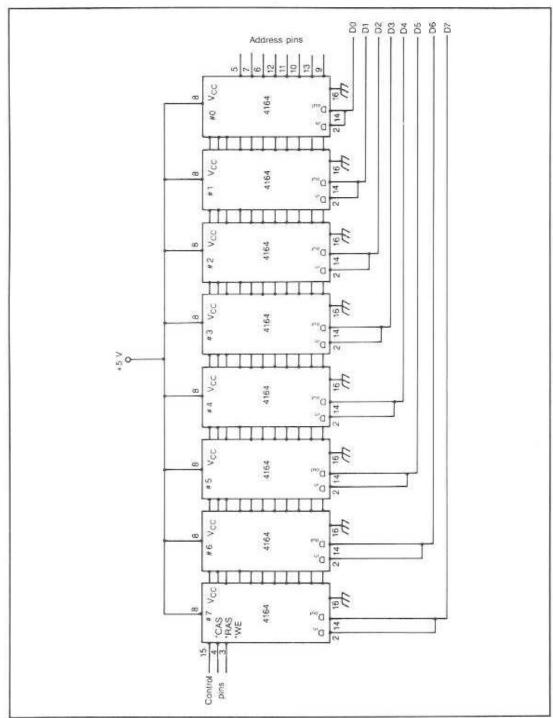

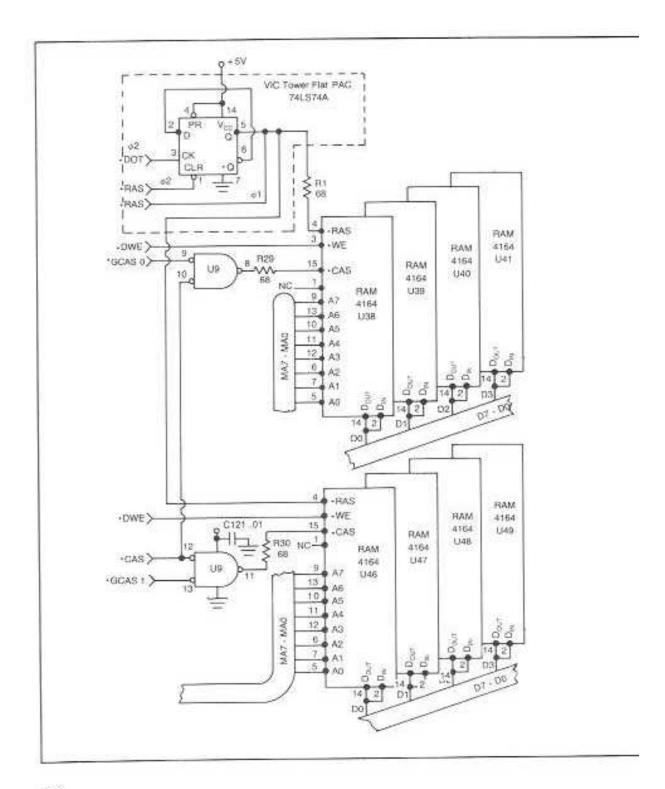

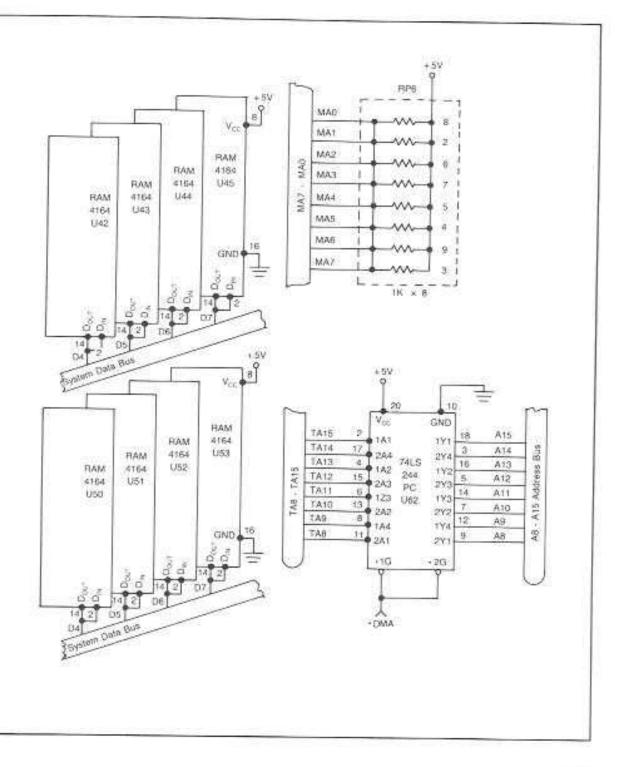

| U38-U53  | 4164           | DRAMs                     | 6-1    | u-1   |

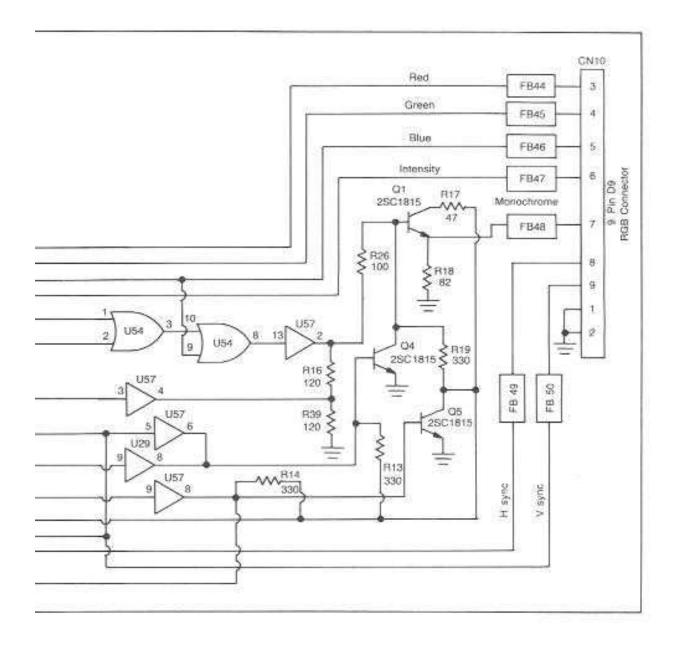

| U54      | 74LS32         | Quad 2-Input OR Gate      | 8-13   | 8-5   |

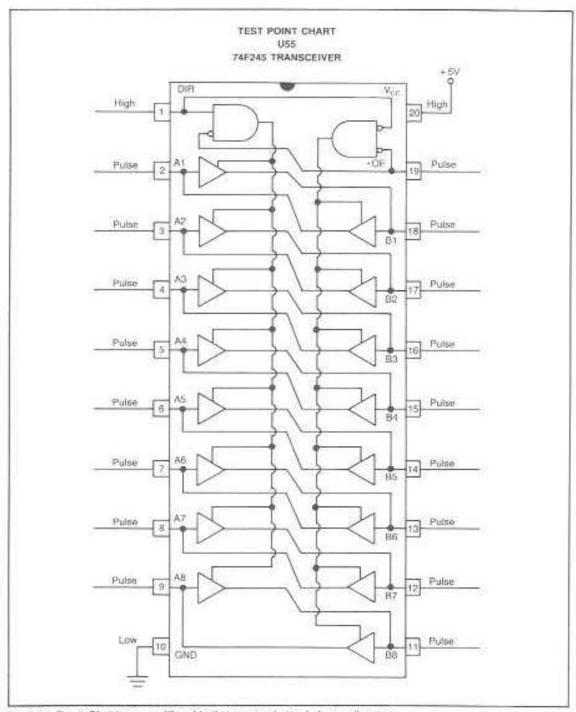

| U55      | 74F245         | Transceiver               | 8-23   | 9.9   |

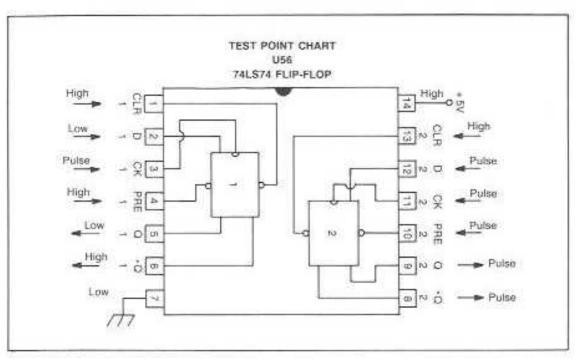

| U56      | 74LS74         | Dual D Flip-Flop          | 8-14   |       |

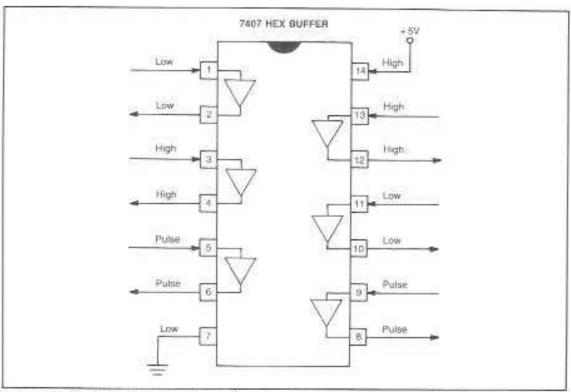

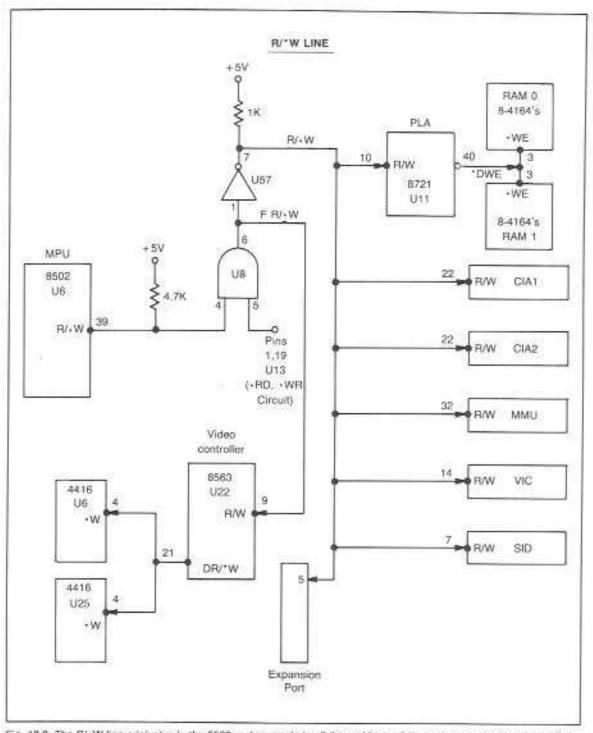

| U57      | 7407           | Hex Buffer                | 8-5    | 8-2   |

| U58      | 74LS03         | Quad 2-Input NAND Gate    | 8-9    | 8-4   |

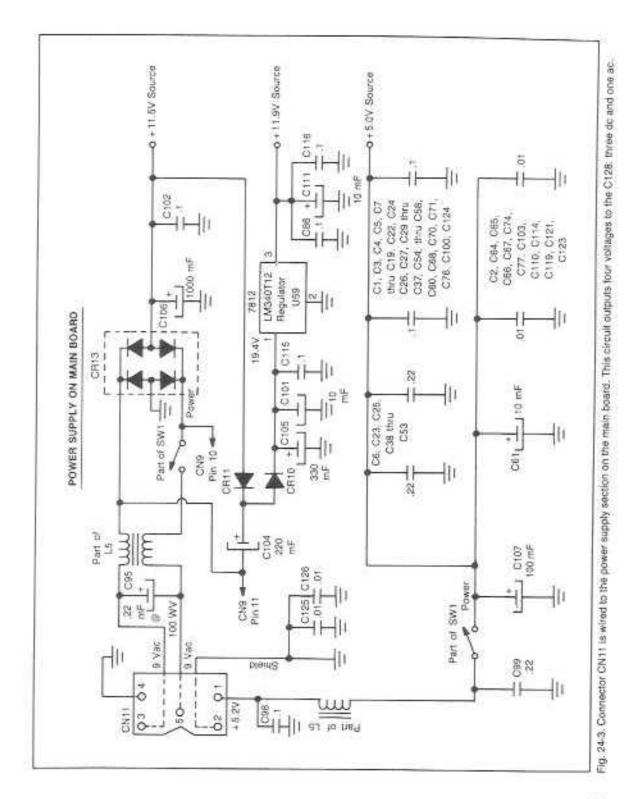

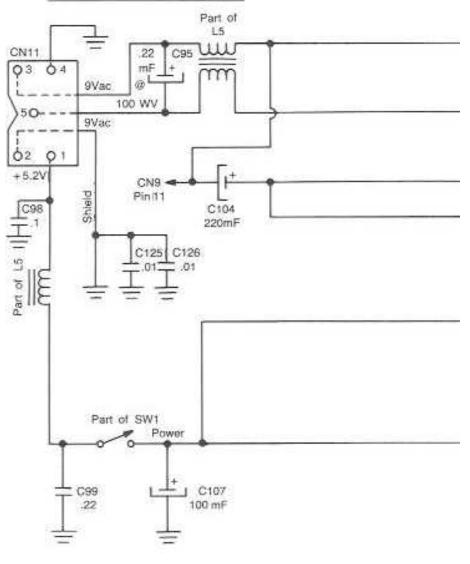

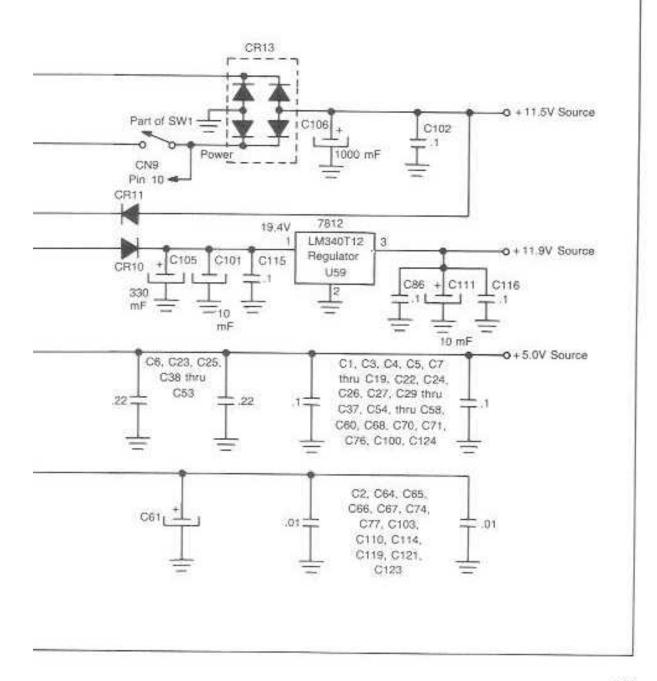

| U59      | 7812           | 12 Volt Regulator         | 24-3   | M23   |

| U60      | 7407           | Hex Buffer                | 8-5    | 8-2   |

| U61      | 74LS08         | Quad 2-Input AND Gate     | 8-6    | 8-3   |

| U62      | 74LS244        | Octal 3-State Driver      | 8-22   | 8-9   |

| U63      | 7406           | Hex Inverter Buffer       | 8-4    | 8-1   |

### Introduction

A fter I reassemble a computer like a C64 or C128 following a repair job, I usually type in some little test program and run it. One of my quick favorites is this two line tester:

10 ?RND(1); 20 GOTO10

The test lines cause the screen to fill up with a stream of scrolling decimal numbers. This tells me that most of the chips in the machine are okay because they are participating in the action. It is a good, fast checkout exercise.

One time, after taking the step-by-step disassembly photos for Chapter 2 and reassembling my C128, I routinely typed in the test lines. The line number 10 appeared fine, but when I hit the ? key to command a PRINT, nothing happened. I tried the ;. It didn't work either.

Instead of using the ?, I typed in PRINT and left off the semicolon. Then I ran the lines. Instead of filling the entire screen with decimal numbers, a row of decimal numbers started scrolling up the left side of the screen.

I breathed a sigh of relief. The C128 itself was okay. It looked like the trouble was strictly related to the keyboard. I took the top off the machine again and spotted the trouble. The keyboard port plug was not seated properly. I had evidently pulled the plug out a fraction during the final moves of the reassembly. I seated it firmly and put the screws back in. Sure enough, all was well again.

Easy-to-fix trouble is typical of the majority of computer problems. If you develop a simple problem and take it into a repair shop, you'll be presented with a bill—after the shop gets to your C128, takes it apart, diagnoses the circuit area, pinpoints the cause, and remedies it. In addition, days and even weeks could elapse without the use of your computer.

To avoid a lot of expense and hassle, all you have to do is learn how your C128 works, from the viewpoint of the hardware. Even though you might be a top programmer or an expert computer operator, the troubleshooting and repairing of your C128 can only be accomplished by approaching the machine from a hardware point of view. It will be easier to gain the repairer's viewpoint if you are a programmer or operator, but the hardware approach is different from the software approach, and requires a different dimension of thought.

A car as an extension of your legs is analogous to a computer as an extension of your brains, and driving a car is analogous to programming a computer. The average auto driver knows little about how the car's engine burns gasoline. In the same way, the programmer has only a smattering of what the computer's circuits are doing as it consumes electricity. When the auto breaks down, the driver takes it to the mechanic to be fixed. When the C128 breaks down, the programmer looks for a computer troubleshooter.

In one respect, this book, besides covering routine, easy repairs, is the manual the computer technician uses to make the necessary tests, no matter how difficult, to get your C128 "up" and working again. However, this book is much more than that. Besides containing the specific information on voltages, logic states and parts, this book is also a training course to give Commodore 128 owners the information that, added to programming skills, will give you the missing hardware point of view that will enable you to gain complete mastery over your computer.

In order to be able to figure out and repair a circuit failure in your C128, first of all you must be able to picture in your mind how the circuit is working. Tried and true electronic service pathways that have been developed over the years are useful. By following these methods, and using your natural puzzle-solving abilities, you will be able to pinpoint defective components or connections. Once the trouble is located—the most trying part of a repair job—then the rest of the chore is either replacing the part or repairing the connection.

The starting point of any repair is to carefully analyze the symptoms of trouble. One symptom is the computer not being able to display all the keys on the keyboard, A number of others exist. In Chapter 1, all the common symptoms are discussed. An analysis of each symptom points to a circuit area that could possibly contain the source of the trouble. In each circuit, there are primary suspects that should be examined first. However, in order to get to the circuits, you must be able to take the C128 apart. It is not difficult, and Chapter 2 goes into the details; it's all about knowing where the screws are.

You must use the right tools for the disassembly. Dismantling and reassembling must be performed correctly, and with care, to avoid mishaps. You are working with tiny items, and each move must be made slowly and then it must be checked. A wrong move could cause "induced" troubles that will complicate things.

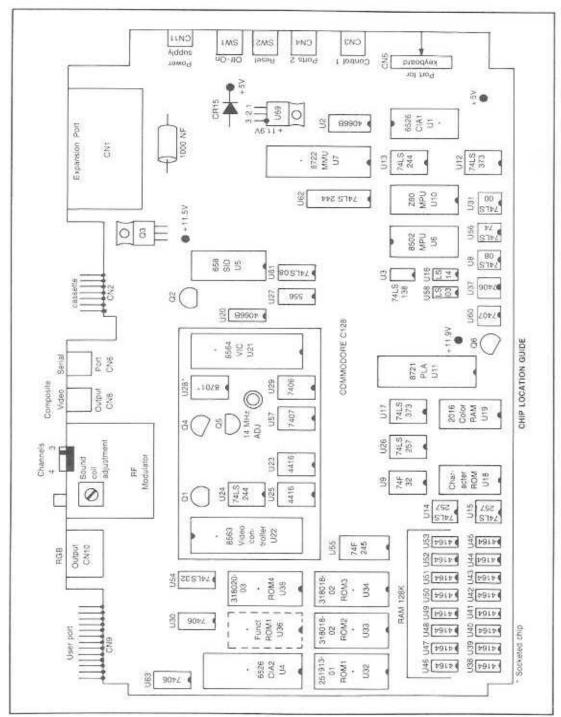

Chapter 3 contains the most used piece of service information: the chip location guide—the main printboard layout of the 63 chips in the computer, plus other prominent landmarks. The guide lets you relate all the information you learn to the location of any chip you might want to examine on the board, and is used over and over again on every repair job. Its use results in many repairs without any other service information.

Chapter 4 provides the mechanical and electronic techniques that must be used if and when chips have to be replaced. The tools and thinking that go into the ticklish job of changing an integrated circuit chip is reviewed. Changing a chip is not like changing a vacuum tube, and is similar to, but much more exacting than, changing a transistor. These four chapters will teach you how to quickly repair at least 50 percent of C128 failures.

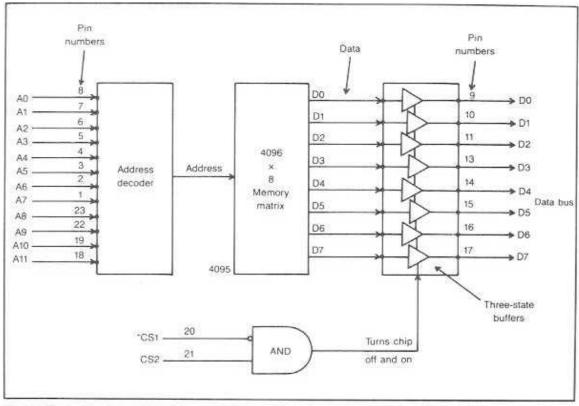

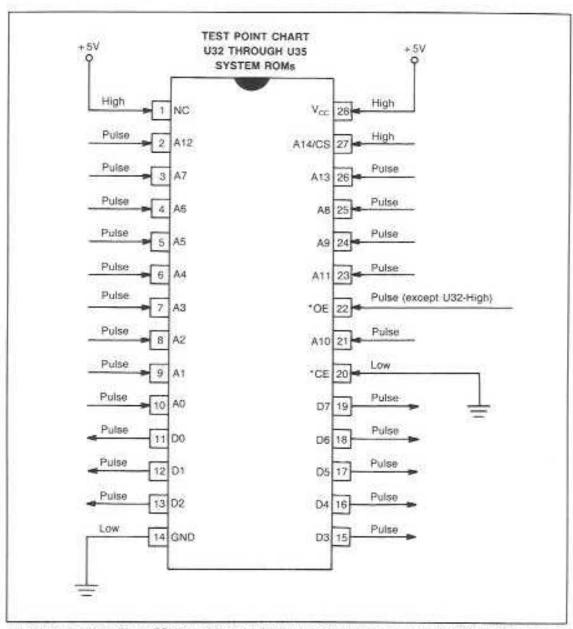

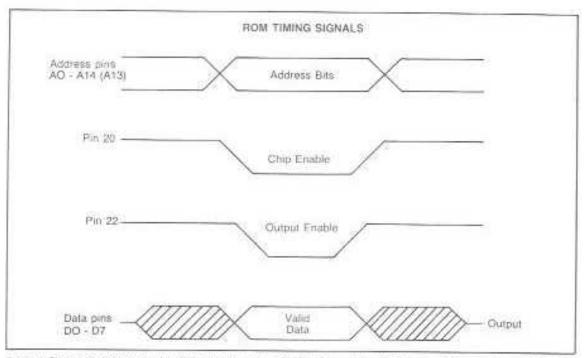

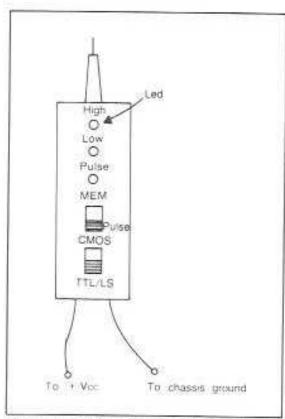

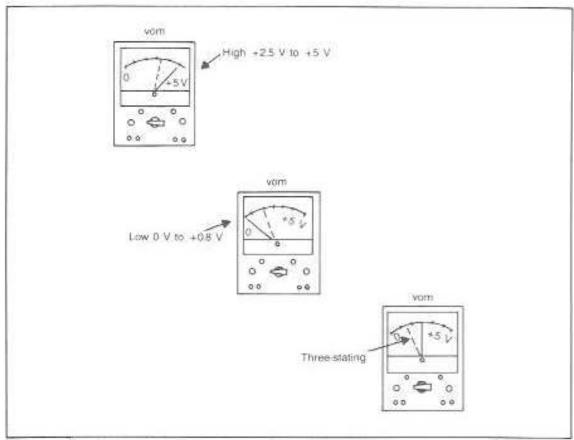

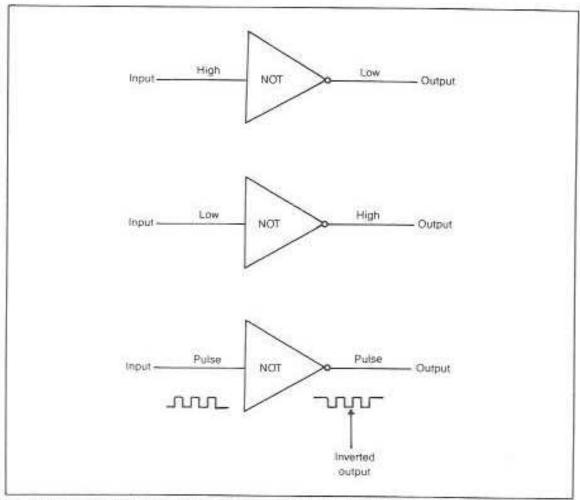

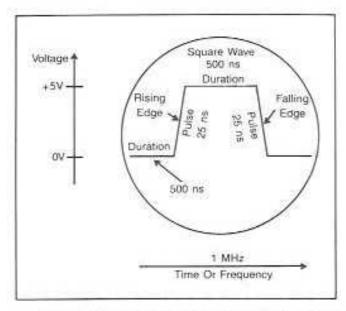

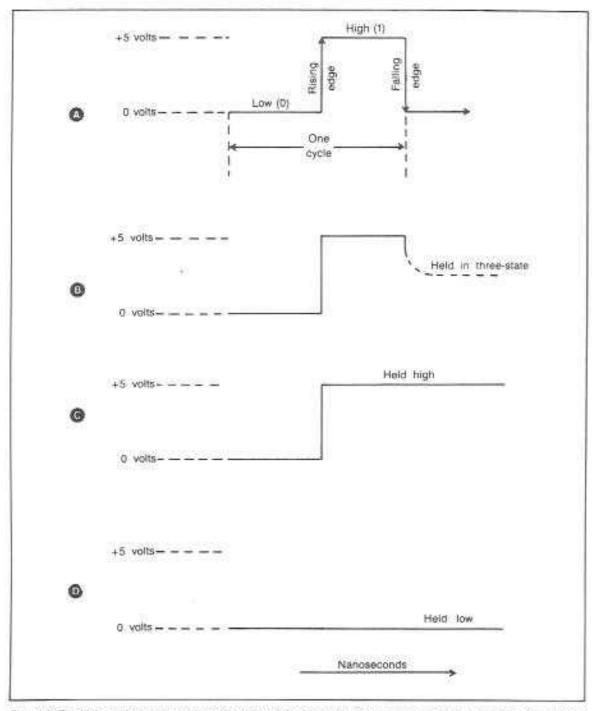

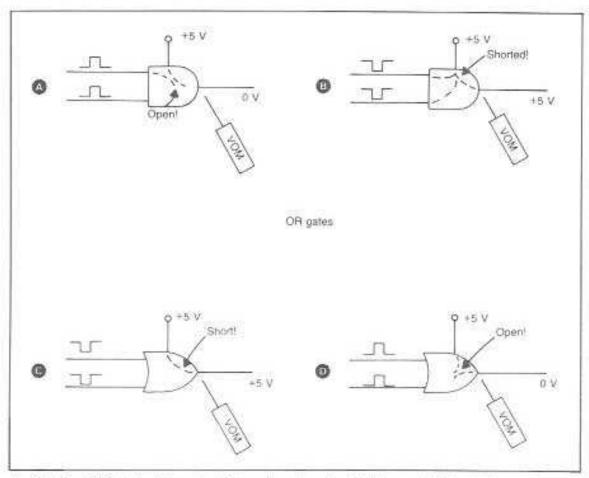

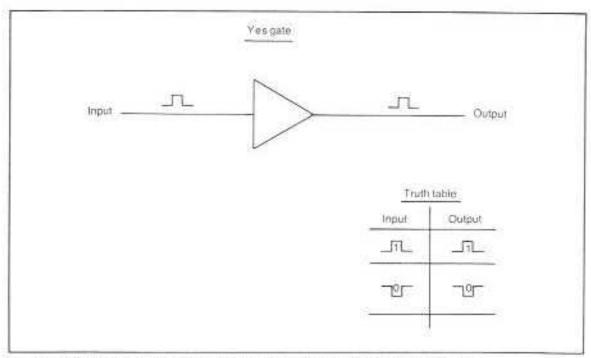

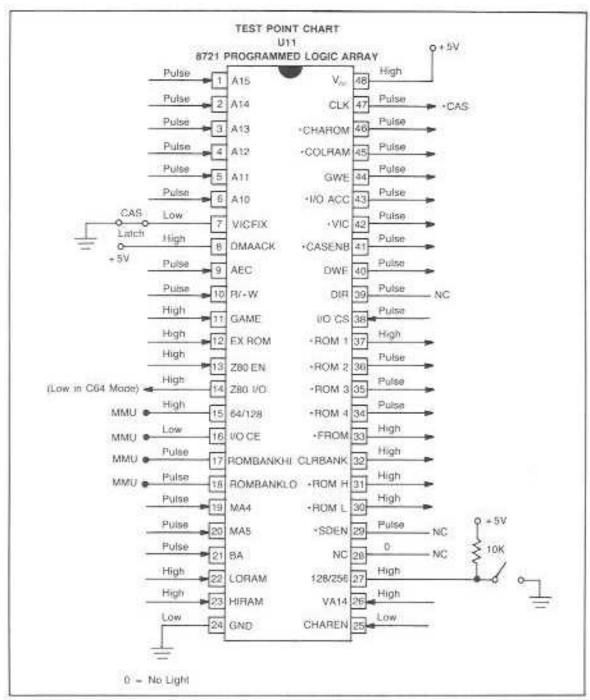

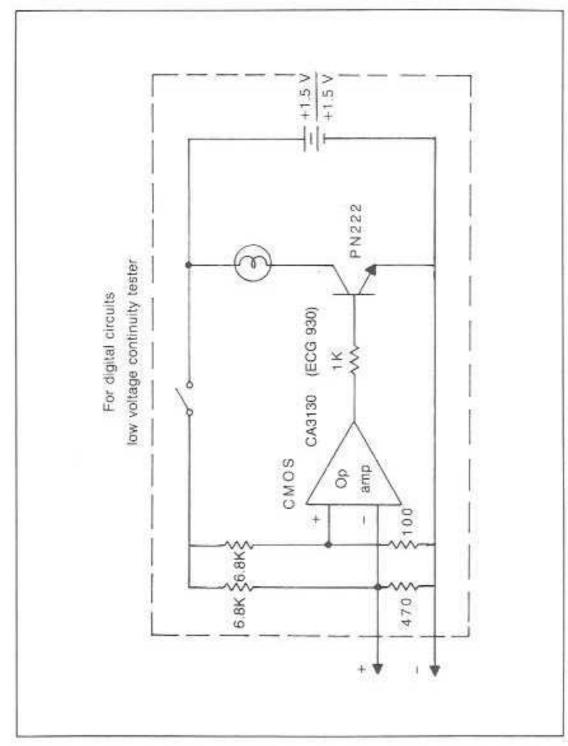

Chapters 5 through 8 introduce you, with more intimacy than previous chapters did, to the chips in your machine. Starting in Chapter 6, you'll find the first of the test point charts that make it a simple matter to quickly check out every chip in the computer. Each chart is the top view of a chip showing the exact pinout. The name of each pin is given and, where practical, a sketch of the chip's insides is also shown. Arrows show the direction of the signal flow. Attached to each arrow is the actual reading you should receive if you probe the test point with a logic probe or vom (voltohm-milliammeter).

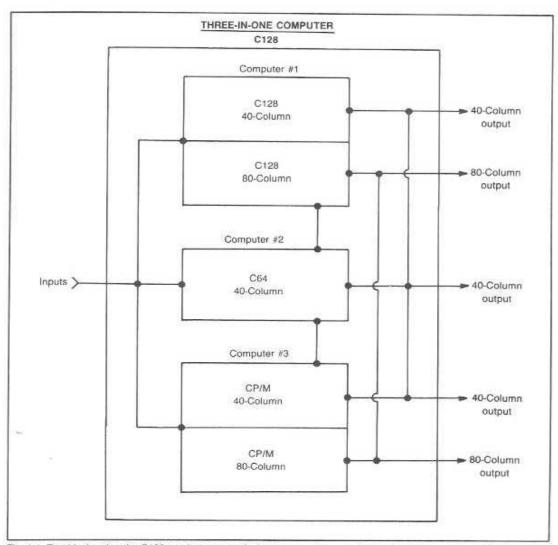

The readings were made on a computer that was first turned on in C128 mode, 40-column, with the READY sign on the screen and with the cursor blinking. When you read your chips, the logic state of each test point should match up with the charts. If all the pins on the chip read correctly, then that chip is deemed okay. Should one or more readings on a chip be incorrect, then this is a symptom of trouble and bears further investigation.

Actually, what you are doing is checking the input and output status of the chips. The inputs and

outputs are clearly shown by the arrows. If all signals are being input properly but are not outputting

correctly, chances are that the chip's internal circuits are not passing the signals. That would indicate a bad chip. On the other hand, if an input signal

is incorrect, odds are that the chip is okay but that

the circuit feeding the chip is not getting a signal to

the pin. That circuit or bus line could have a short

or an open condition. The test point charts are your

entree to quickly getting repairs underway and locating troubles.

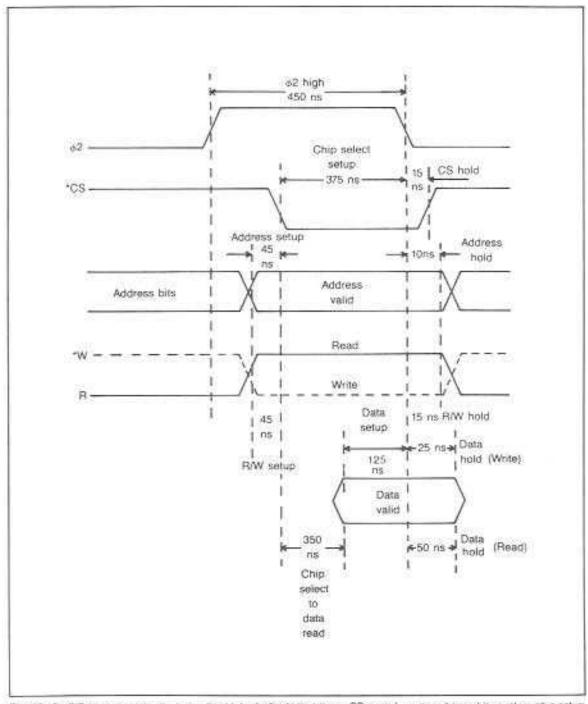

Chapters 5 through 24 comprise a servicing manual and a technical reference manual written on a technician's level. There are discussions of each chip with considerable detail, and even some timing diagrams for the chips that require them. You will gain mastery over your C128 by gradually absorbing the material. You might find that your programming skills will also improve as you gradually realize what is actually happening to the 1's and 0's as they flash around the digital circuits.

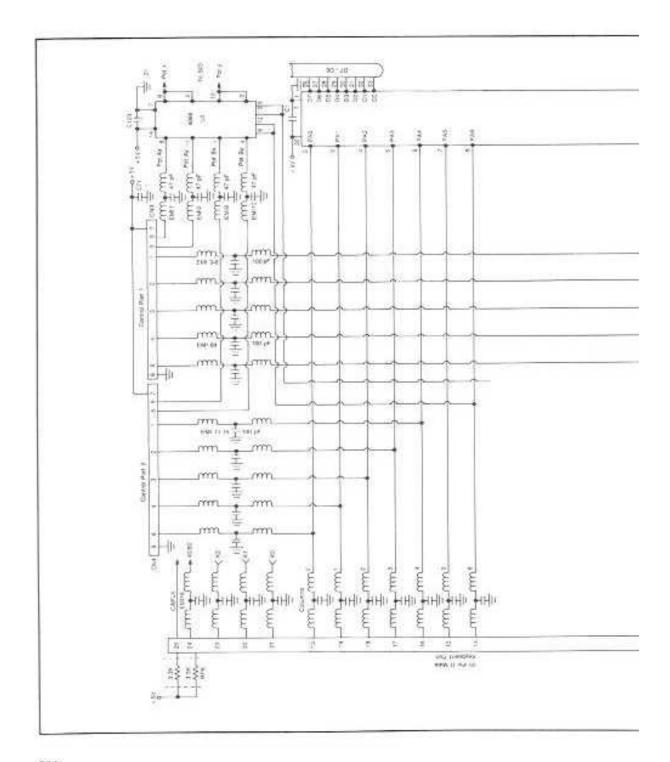

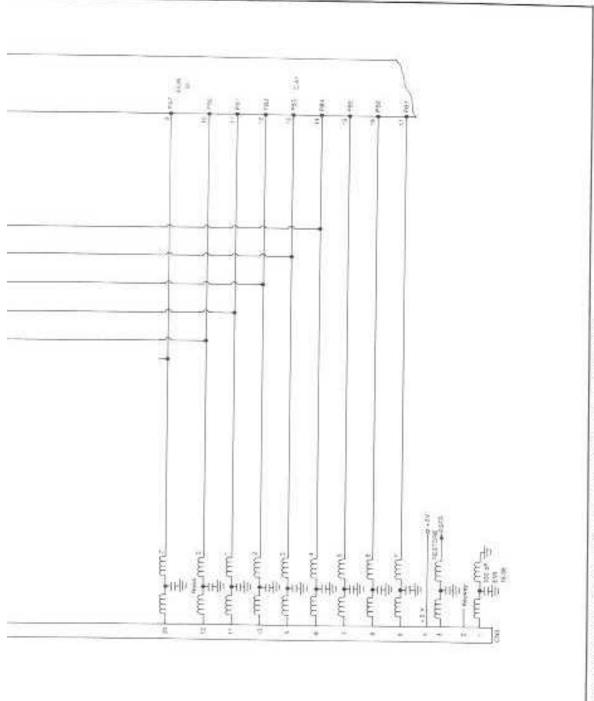

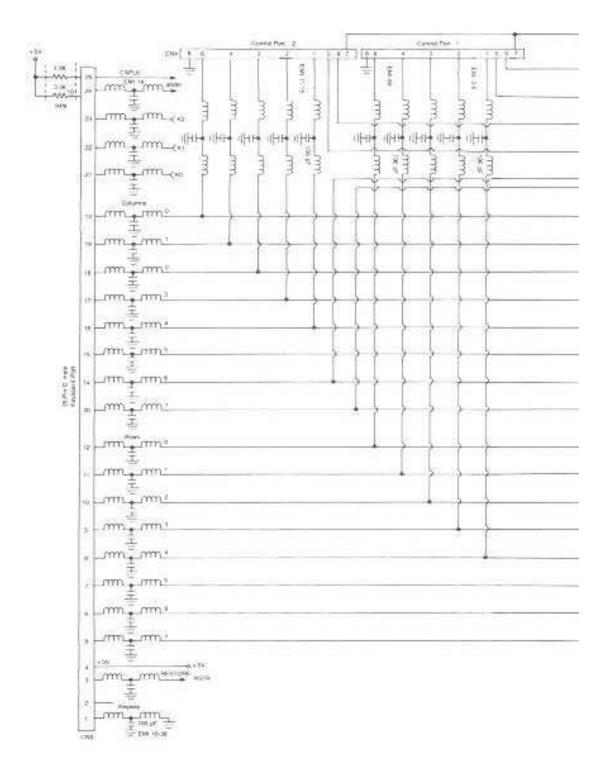

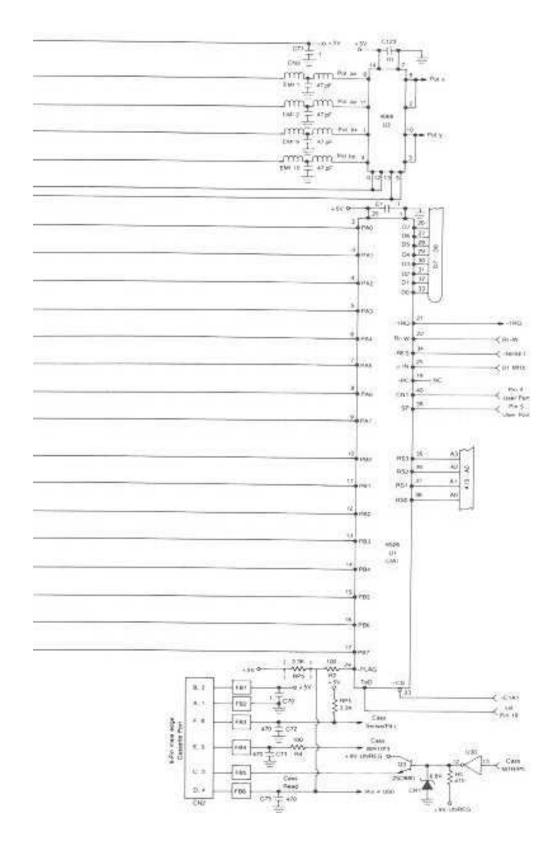

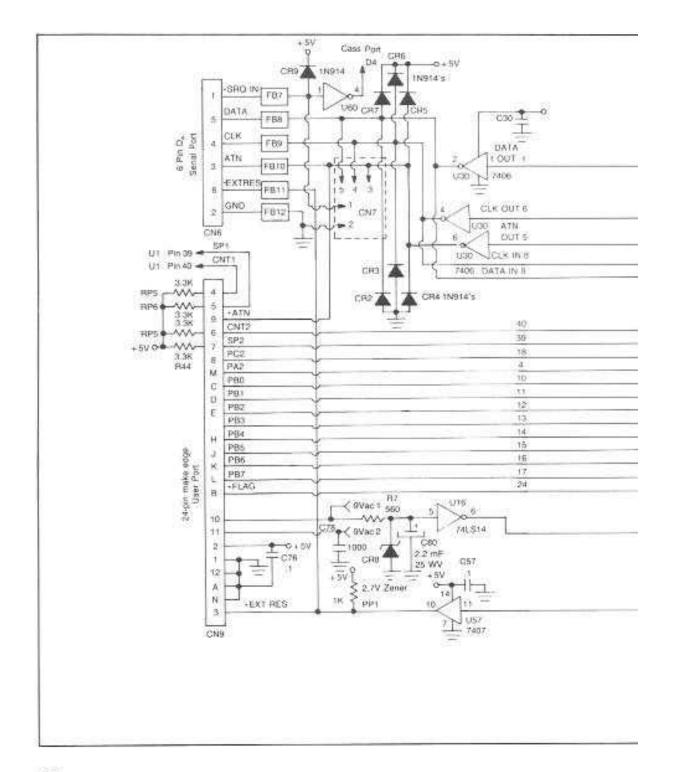

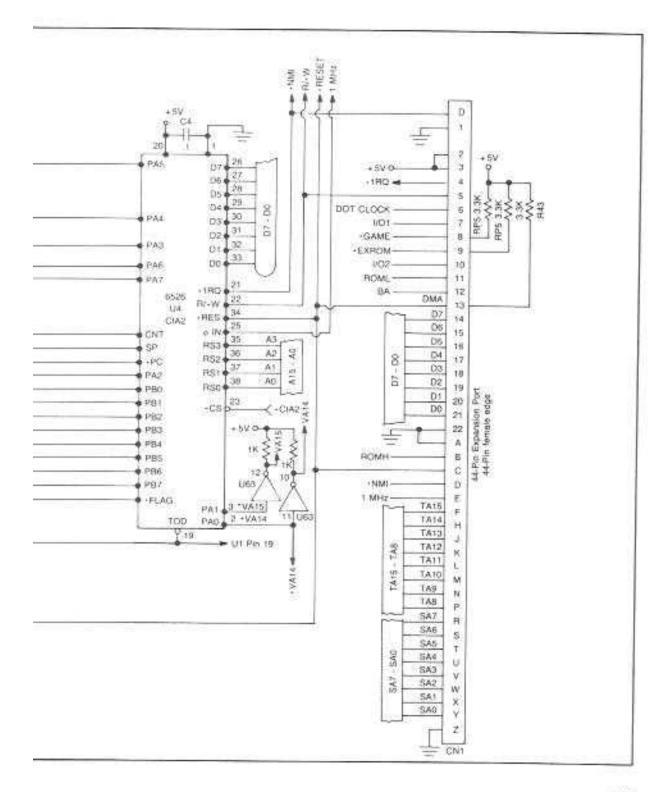

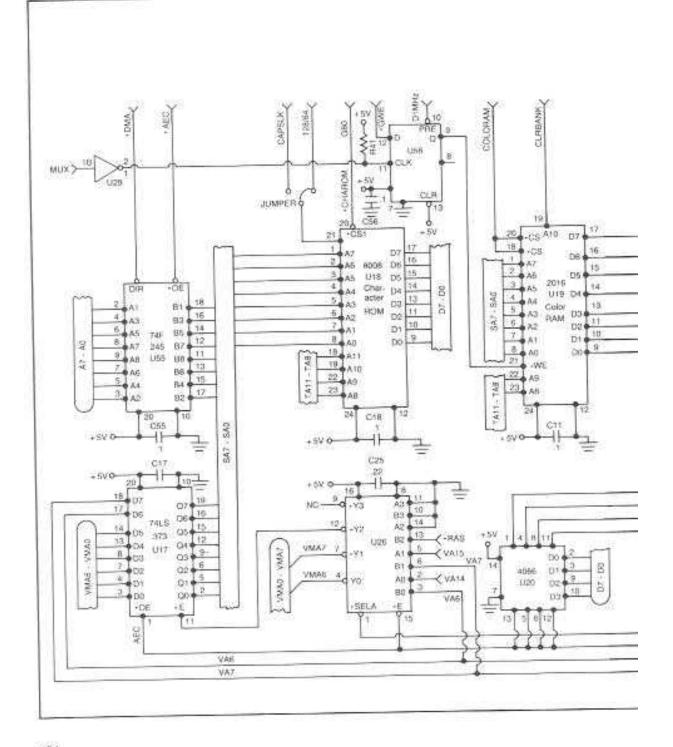

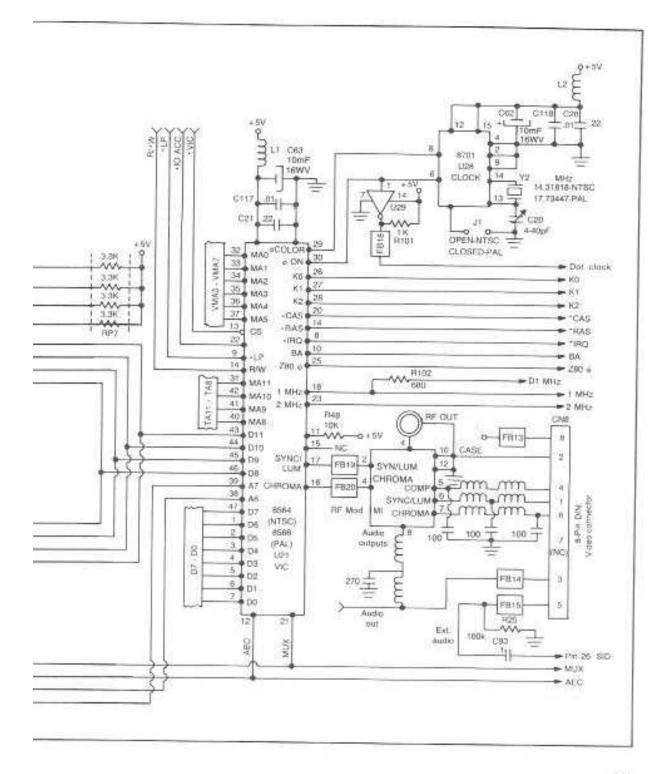

This book ends up with a master schematic of the C128. The schematic is needed during a difficult repair after the circuit area containing the trouble has been located and the wiring details are needed to pinpoint the prime suspects. The schematic contains all the part numbers. These same part numbers are found printed clearly on the printboard. For example, a U6 is found printed on the board next to the 8502 MPU. The schematic reads U6 as the part number for the 8502. All the transistors, capacitors, etc. are identified in the same way. With the chip location guide, the test point charts, the theoretical discussions of the circuits, and the master schematic, you should be able to cover all the information required for the troubleshooting and repair of your computer.

Chapters 10 and 11 are a short course in logic gates and digital registers with specific reference to the gates and registers in the C128. The way the machine uses binary, hexadecimal and decimal is included too. This knowledge enables you to work out BASIC PEEK and POKE routines to signal trace circuits that the 8502 MPU is able to address. The C128 also has a machine language monitor that can also be used for signal tracing with its commands. The ability to convert from decimal to binary to hex and back should be one of the tools of your servicing repertoire.

To be able to make the easy repairs on your C128 really pays off. The easy repairs are at least half of the total repairs. While your C128 is still in warranty, there is no problem—Commodore is very accommodating. However, once the warranty period is over, the complication begins. If the machine fails, you must take it to a repair station. This often takes some weeks, and the machine can be returned with a healthy repair bill. If, on the other hand, you are able to do the troubleshooting and repair yourself, then the savings in time and money become quite worthwhile-besides the feeling of accomplishment you get when you fix your machine. If, during the life of your machine, you happen to get one repair from this book, the savings will more than pay for the price of the book. Then, of course, there is the knowledge you'll gain from the experience.

## 1. C128 Briefing Session

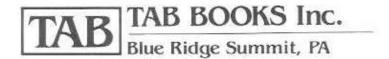

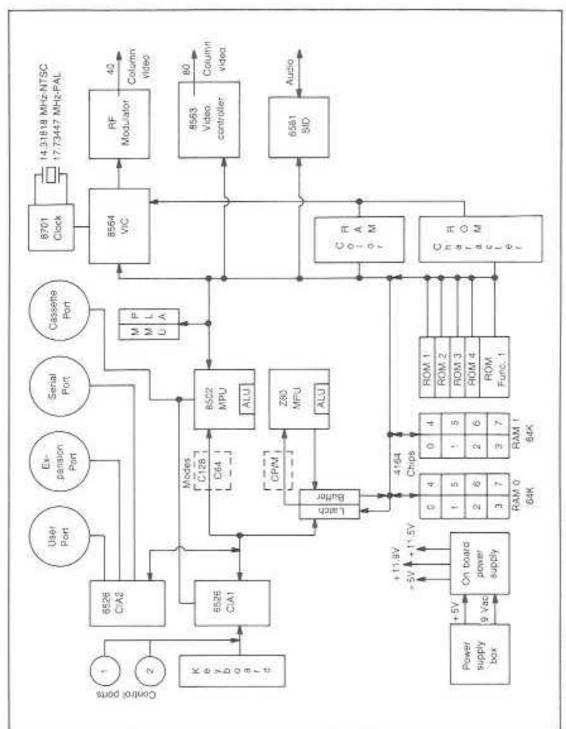

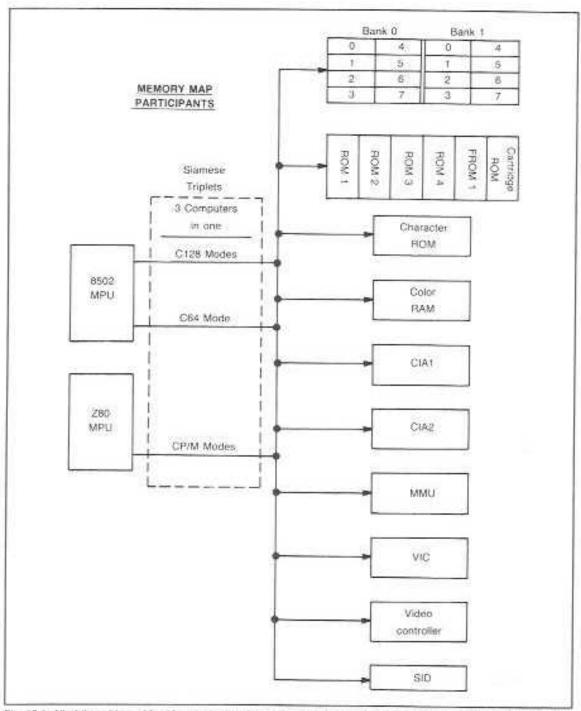

The unusual thing about troubleshooting a C128 in comparison to trying to fix most other computers is that the C128 case contains a form of Siamese triplets. Three complete computer systems are in the one case. The three computers are joined together at their inputs, outputs, MPUs (Micro-Processing Units), and memory. They also share many of the other circuits. They cannot be physically separated from each other.

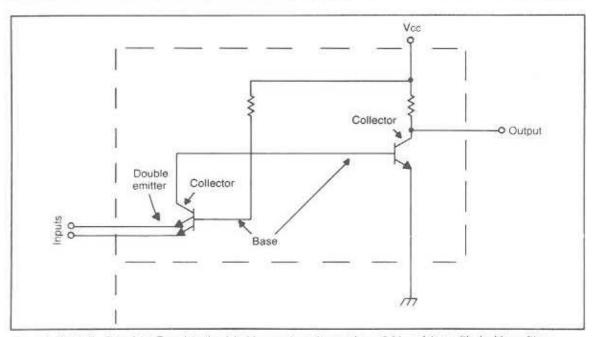

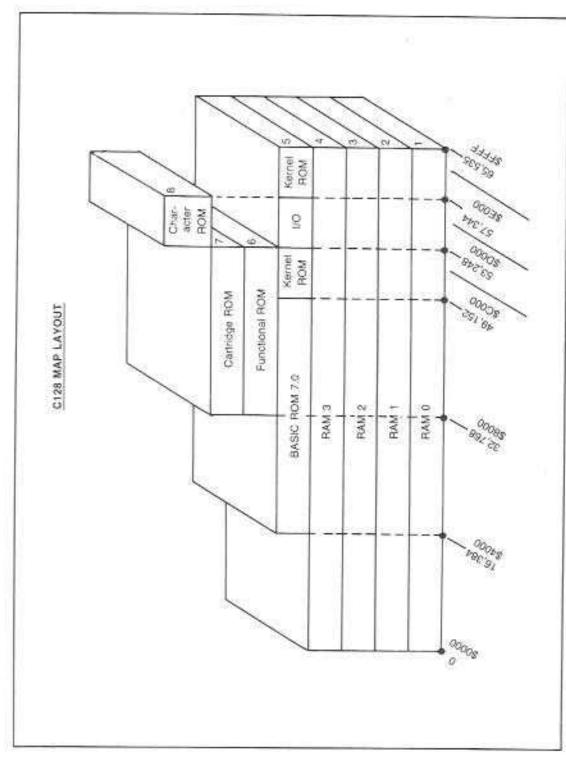

The triplet feature of the C128, as might be imagined, can complicate and confuse the situation when trouble strikes. However, if you are properly briefed and are aware of the three-in-one computer feature, as shown in Fig. 1-1, then symptom analysis can be accomplished without difficulty, and that is what this book is all about. It covers the three computers in the C128 case from a troubleshooting point of view.

#### THE SYMPTOM DEVICES

The input and output devices of your computer are diagnostic tools. The most valuable of them is the TV display. Most computer troubles show up on the TV display. In many cases, you can look at what is happening, or not happening, in the display and be directed to the circuits that are in trouble.

Other input or output devices that could also aid in interpreting symptoms are: the printer, the disk drive, the cassette, the keyboard, the modem, a cartridge, the joysticks, etc. When these devices "act you have to decide whether the computer is at fault or the device is bad. The decision is easy if you substitute a device that is known to be good for the one exhibiting the symptom. If the new one works properly, then the old one is defective. If the trouble persists, the finger of guilt points to the computer circuits. Table 1-1 is a trouble chart that indicates the computer circuit that could be the problem when peripherals stop operating, but are proven to be good. These input and output devices are excellent symptom indicators. However, as mentioned, the TV display reveals the most symptom information. The symptoms that displays show become classics, have names of their own, and contain valuable

Fig. 1-1. Troubleshooting the C128 can become confusing because there are three separate computers joined together like Siamese triplets.

troubleshooting information when interpreted properly. Let's go through them one by one.

#### The Items in a Normal Display

Before you can spot trouble in a display you must know what the display should look like when there isn't any trouble. Table 1-2 shows the five possible types of display devices you might be using. They are (1) your home TV, (2) a monitor that displays a composite color TV signal, (3) a monitor that needs an RGBI signal, (4) a monochrome monitor, (5) a direct monitor.

## Table 1-1. When a peripheral won't work because of computer trouble, these chips are the prime suspects.

| Symptom                          | Possible Defect<br>in C128 | Try                                            |

|----------------------------------|----------------------------|------------------------------------------------|

| Disk won't work                  | CIA2                       | Replacing chip                                 |

| Printer stops                    | CIA1/CIA2                  | Replacing chip                                 |

| Keyboard won't work              | CIA1/ or Keyboard          | Replace chip or repair<br>or replace keyboard  |

| Modem not operating              | CIA1/CIA2                  | Replacing chips                                |

| Loses audio<br>40-column display | SID                        | Replacing chip                                 |

| loses video                      | VIC/RF Modulator           | Replace VIC or replace<br>or repair RF Mod box |

| 80-column display                |                            |                                                |

| loses video<br>Cartridges        | 8563/74LS244/4416's        | Replacing chips                                |

| won't work<br>Control port       | CIA2/MMU/PLA               | Replacing chips                                |

| won't work                       | CIA1                       | Replacing chip                                 |

| Cassette won't work              | 8502/CIA1/7406.U30         | Replace chips or transistor                    |

Table 1-2. The C128 outputs five different signal types from its two video output circuits. One type of signal is for each of five different kinds of monitors.

| Available Modes   | Output Circuits          | Display Device                                 |

|-------------------|--------------------------|------------------------------------------------|

| C128<br>40-column | RF Modulator<br>8564 VIC | Home TV<br>Composite Monitor<br>Direct Monitor |

| C128<br>80-column | 8563 Video<br>Controller | RGBI Monitor<br>Monochrome Monitor             |

| C64<br>40-column  | RF Modulator<br>8564 VIC | Hame TV<br>Composite Monitor<br>Direct Monitor |

| CP/M<br>40-column | RF Modulator<br>8564 VIC | Home TV<br>Composite Monitor<br>Direct Monitor |

| CP/M<br>80-column | 8563 Video<br>Controller | RGBI Monitor<br>Monochrome Monitor             |

Because most people use their home TV, I'll use it as the example. In general though, the discussion covers all five types. The differences are covered in detail in Chapters 20 and 21.

The C64 mode of the C128 is built to come on as shown in Fig. 1-2. Item number 1 in the picture is a light blue border. Item number 2 is a dark blue display block. Item number 3 is a sign-on message ending with READY. Item number 4 is the blinking cursor. These signals emerge from the RF socket in the back of your C128, passing through the cable and entering the TV via the Computer/TV switchbox, into the VHF antenna terminals of the TV.

There is one more signal from the C128 that is not displayed. The above four signals are packaged up in a TV frequency set for either Channel 3

Fig. 1-2. In C64 mode the display normally comes on with a light blue border, a dark blue display block, light blue characters, a READY prompt and a blinking cursor.

or 4. The Items are modulated in these TV channel frequencies and are then demodulated in the TV so that they may be displayed on the screen. The modulation-demodulation process degrades the signals slightly. That is why the monitors are preferred over a home TV display. For monitors, the signal items are sent directly to the monitors through the composite video socket or the RGBI socket without having to go through the modulation-demodulation in the RF Modulator circuits. The home TV is quite satisfactory and handy.

When you turn on your C128, you should see with the 40/80 key in the up position, and in C128 mode, a black block, a green border, green lettering and a cursor. If anything is missing, then you are experiencing trouble. Incidentally, if the block and the border show, but the lettering and cursor are missing, then the first thing you should do is check the 40/80 key. It should be in the up position. If it is depressed, it could cause the lettering and cursor to be missing on your home TV screen.

When the 40/80 key is up, the signal is coming out of the RF socket and shows all four Items on the display. However, when the 40/80 key is depressed, the signal is switched around and the four Items appear out of the RGBI socket. The RF socket only puts out the display block and the border.

#### The Dead Computer

The most common problem with the C128 is a complete loss of power. When this happens, the TV display shows a blank screen. If the display is a home TV, then the picture will appear as if there isn't any antenna attached. Most TVs at that time will show a screenful of snow, or some snowy distant channel as shown in Fig. 1-3. When you flip the C128 off-on switch, nothing shows on the display. The red pilot light might or might not go on.

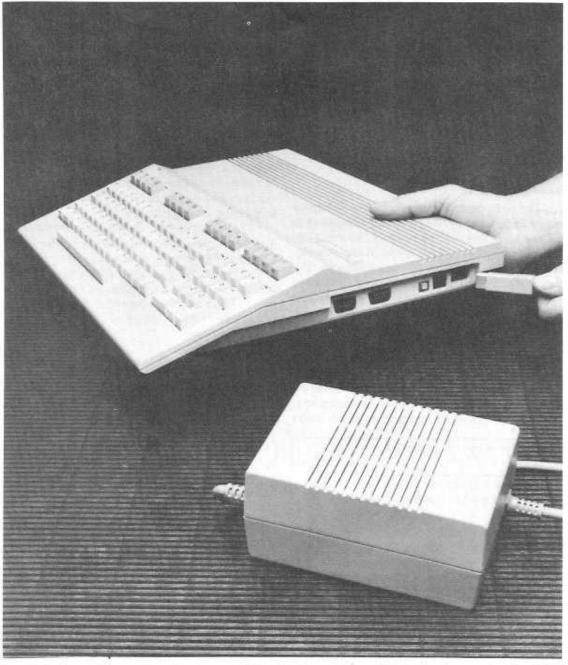

You must make the obvious service moves first. Check to be certain that the computer box is plugged properly into the wall socket on one side, and the computer on the other, as seen in Fig. 1-4. If the plugs are okay, then feel the casing of the power box. Is it slightly warm? If it is, then the box is prob-

Fig. 1-3. When your home TV or monitor comes on as usual but your C128 won't display anything, your computer is playing dead.

Fig. 1-4. The first obvious step to take when the C128 is playing dead is to make sure that the power box is plugged into the wall socket and into the side of the computer.

ably okay. If it is stone cold, then it could be the troublemaker. Trying a new one will prove the point. If a new one fires up the computer, then the old one is bad. Should the new one not work either, then the old one is probably fine.

Once you complete these quick checks and the computer is still dead, your next step is to turn to Chapter 24. There you will find the next troubleshooting steps. You'll need to take some ac and dc voltage readings, and probably disassemble the power box and the C128.

#### Garbage Display

The next most common symptom is loosely known as "garbage." It is generally thought of as a screenful of meaningless numbers, letters, symbols, white spaces and black spaces as shown in Fig. 1-5. The trouble could happen during start up. The display fills up with garbage instead of the normal sign-on with the READY prompt. The garbage could contain a flashing cursor, or the cursor could also be missing. Other times the garbage could suddenly appear while you are computing. Your program crashes and the computer locks up.

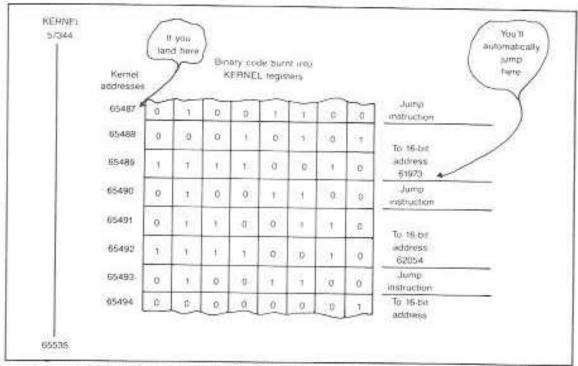

The reason why garbage appears on the screen, instead of the normal sign-on picture, is because the microprocessor is out of control—it is running wild. Normally the processor conducts its duties under

Fig. 1-5. When the display fills up with GARBAGE instead of the READY sign-on message and the blinking cursor, the trouble is hidden somewhere in the digital circuits of the computer.

the careful control of the C128's operating system in the ROM (Read-Only Memory) chips. When for some reason the operating system loses control, the processor simply goes mad, spewing addresses, data and control signals around the computing circuits without any rhyme or reason. The result is: the TV display fills up with nonsensical characters, numbers, symbols and spaces.

The garbage symptom does not pinpoint the trouble to a single circuit. The failure could happen in almost any of the digital circuit components or chips. Your approach therefore must be: first, locating the general circuit area of the trouble before you can zero in on a specific circuit; second, locating a component, connection or chip.

This procedure requires you to learn how the digital circuits are processing data from a hardware and voltage point of view, at the technician's level of understanding. Then you can intelligently make appropriate logic probe, voltage and scope readings to hunt down defects. Chapters 6 through 23 contain the information that will aid you in pinpointing the troublemaker.

#### **Empty Display Block**

The empty display block is the same symptom as what occurs when the 40/80 key is accidentally depressed. As shown in Fig. 1-6, the border and dis-

Fig. 1-6. A variation of garbage is a display block that is blank. The border and empty block can be seen but no characters appear. Striking the keyboard has no apparent effect.

play block are present but the block is completely empty. You can strike the keyboard but try as you may, nothing shows up—the block remains devoid of characters or symbols.

When the display block is empty and the 40/80 key is up, you have a circuit problem that results in another form of garbage. Here again the same circuits come under suspicion. The fault could be located anywhere in the digital circuits. It is a troubleshooter's job to take test readings and, from the results of the readings, deduce what circuit area is in trouble. Again, an understanding of Chapters 6 through 23 should clear up the maze of chips and printboard copper traces.

Chapters 6 through 23 contain troubleshooting techniques and theory of operations along with detailed test point charts showing voltage and logic states that are normally present on the test nodes when the READY sign appears. What you do is run voltage or logic probe tests, as described in Chapter 4. If you take some test readings and one or more of the test results do not match up with what is supposed to be at the connections, then you have found a clue that could lead to the fault.

#### No Color

The C128 is a color computer. Special circuits in the machine generate the colors that appear in the display. Should the C128 display a picture with good characters and symbols, except for the fact that the picture is missing coloring, then no color indicates trouble in the color circuits.

The color signal is originated in the clock circuits. Chapter 17 covers the clock. The colors are output for the 40-column displays in the 8564 VIC chip. Chapter 20 explains the 8564 chip. The colors for the 80-column displays are output by the 8563 Video Controller chip. The discussion on the 8563 is in Chapter 21. When there is no color, turn to these chapters to find out how the color is generated and how it passes through the computer. Once you brief yourself on the color theory of operation, you can then figure out how the coloring is failing to appear and take the repair measures to restore color.

#### No Video, Sound Okay

This symptom is almost like the dead computer symptom except for one important difference: the sound from the computer is still emanating from the TV display. This means that the computer is fine, except for the video circuits. Because there are a number of different types of video outputs possible from the C128, you must make some simple isolation tests to determine which videos are missing and which ones are present. The possible video outputs you can obtain from the C128 are the following.

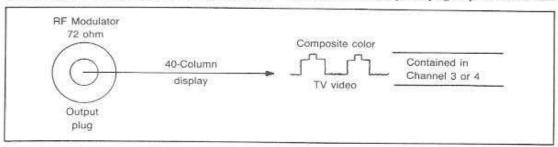

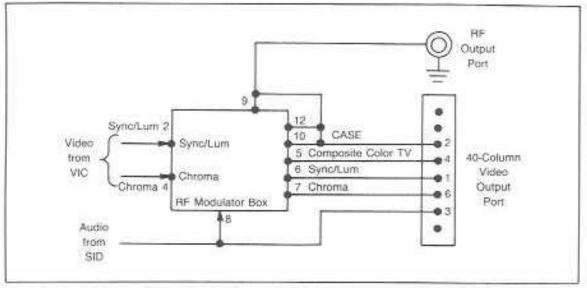

The RF output plug sends a composite TV signal contained in a TV Channel 3 or 4 envelope (see Fig. 1-7). A home TV can use this signal just as if it was coming from a TV station. This RF output has a 40-column display only.

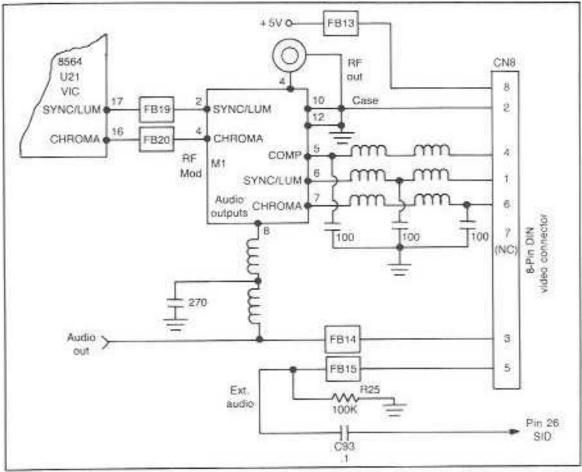

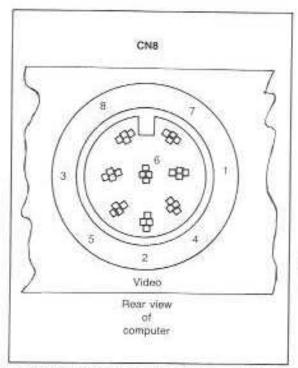

The Video output plug is tricky. It puts out two different type 40-column signals. First of all, it outputs through pin 4 a composite TV signal without the TV Channel 3 or 4 modulation envelope (see Fig. 1-8). This signal can be displayed on a composite monitor TV. Secondly, the plug outputs another dual

Fig. 1-7. The RF Modulator output plug sends a 40-column composite color TV signal on a Channel 3 or 4 frequency. It works fine on a home TV.

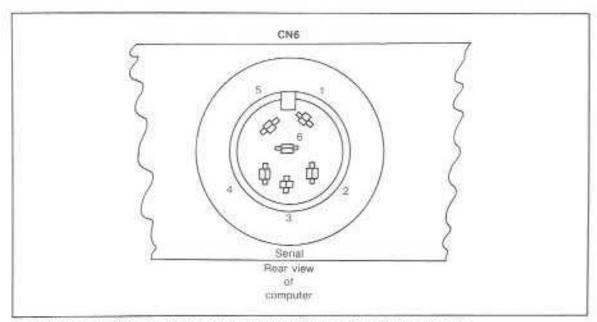

Fig. 1-8. The Composite Video Port sends out a number of signals. At pin 4 is a 40-column composite color TV signal without Channel 3 or 4 modulation. At pins 3 and 5 are audio output and input signals. Pins 1 and 6 output separate 40-column LUM/SYNC and CHROMA.

signal. From pin 1 it emanates a Luminance/Sync signal. From pin 6 comes a Chroma signal. These two signals can be injected into a direct TV monitor to produce a display. There aren't too many of these monitors around except for the Commodore 1702 and perhaps a few others. However, the combination signals are available at the pins and can prove useful during the testing of video signals. Any ordinary TV scope will show them nicely.

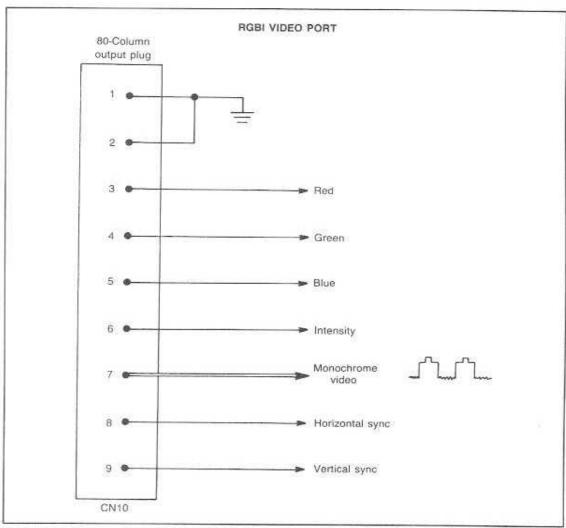

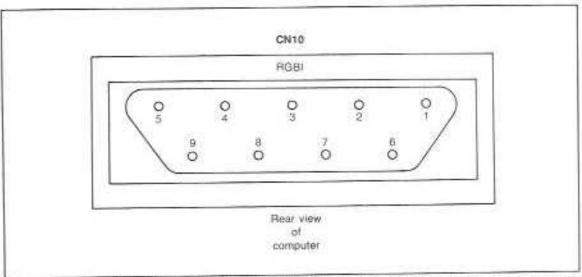

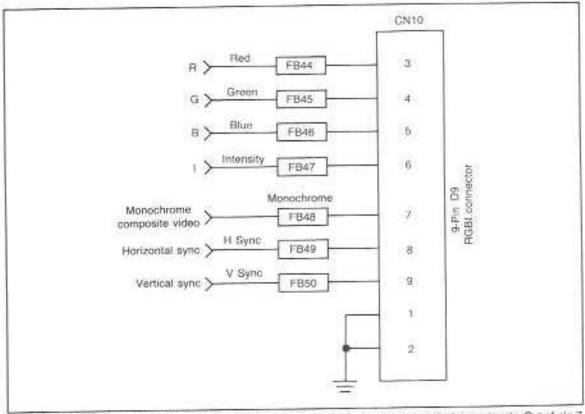

The RGBI plug is also not straightforward. It also outputs different signals (see Fig. 1-9). It puts out a normal 80-column RGBI signal that can drive an RGBI Monitor. The RGBI signal exits through most of the nine pins of the RGBI plug. In addition, another separate 80-column signal is output from pin 7 of the RGBI plug. It is an 80-column Monochrome signal that can be used on an ordinary composite TV monitor. It is similar to the 40-column signal com-

Fig. 1-9. The RGBI Port outputs two separate signal-types. From pin 7 emanates an 80-column Monochrome Video. All the rest of the signals combined produce an 80-column RGBI signal with correct horizontal and vertical sync.

ing out of pin 4 of the composite video plug—only this pin 7 output from the RGBI plug has 80 columns. The columns are different because the 40-column output comes from the VIC 8564 chip and the 80-column output comes from the 8563 video controller chip.

Table 1-2 shows the different outputs. The isolation test techniques are discussed in detail in Chapters 20 and 21. Chapter 20 covers the 40-column outputs and Chapter 21 covers the 80-column outputs.

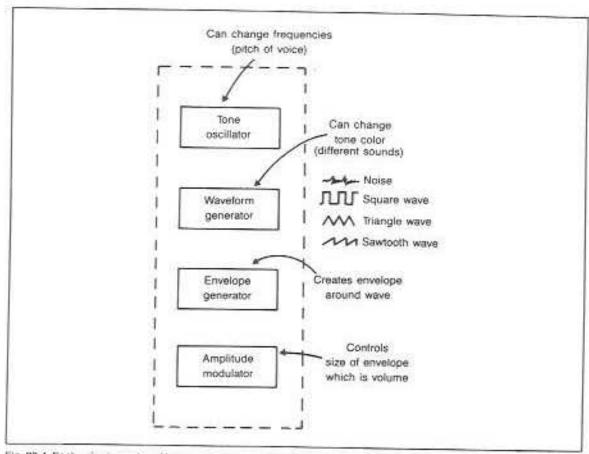

#### No Sound

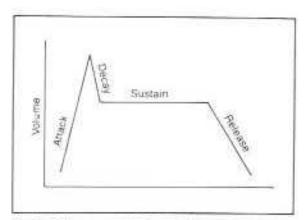

There are separate sound circuits in the C128. They are covered in Chapter 22. The sound circuits are mostly contained in the 6581 Sound Interface Device, called SID. When sound troubles happen, they are usually related to that chip and its adjoining circuits.

SID, and the microprocessor it is operating with, form a bond between them. It's as if they are a small computer system of their own. This makes sound troubles relatively easy to test and handle. Sound testing is discussed in greater detail later in this chapter. For all the details though, turn to Chapter 22.

#### Peripheral Device Problems

As you know the C128 mode is the centerpiece of the computer system. Feeding into the C128 are the keyboard, disk drives, cassette, joysticks, paddles, light pens, inscription pads and so on. The computer processes these inputs and then outputs to the printers, disks, cassette, modem, TV display, etc.

As mentioned earlier, when a peripheral device stops operating normally and causes trouble, the first step is to substitute the troubled peripheral with one that is known to be good. If the trouble ceases and normal computing continues, then the trouble is in the peripheral. Repairing peripherals is a separate job and is covered in other books. However, when the new peripheral also won't work, then the trouble is in the C128.

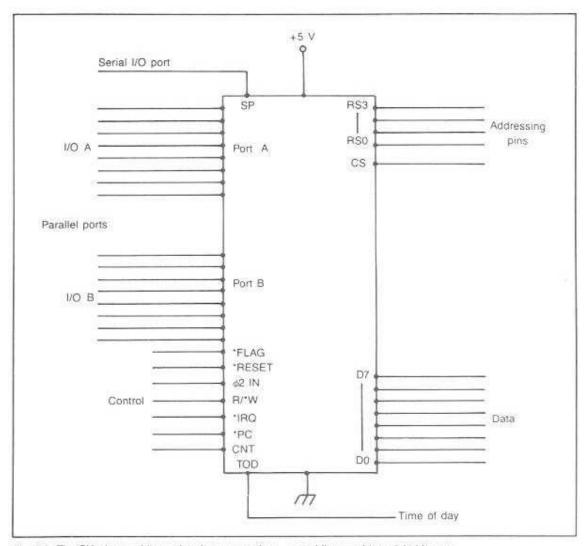

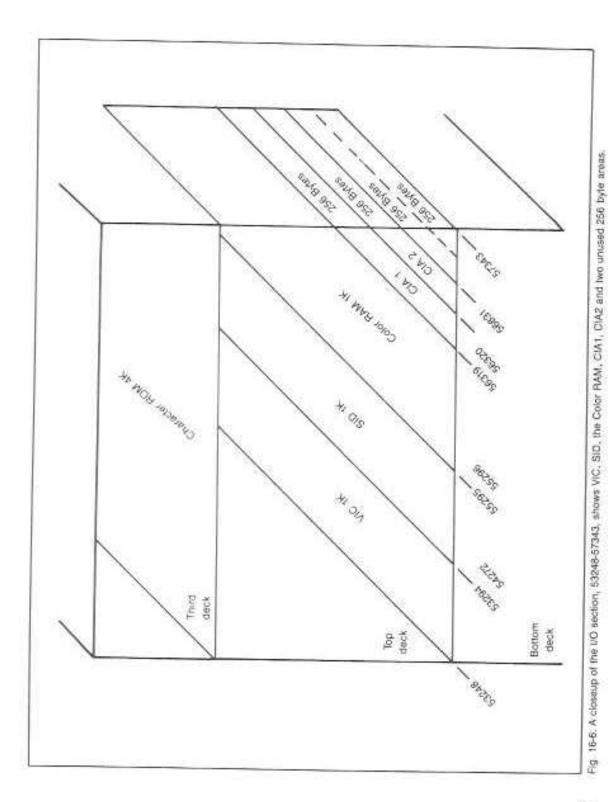

When you decide that the C128 is at fault, turn to Chapter 23, which discusses the inputs and outputs of the C128. There you will find the circuits and plugs that receive the inputs and send out the outputs. The chapter guides you to specific circuits, as found in Chapter 19. In Chapter 19 are discussions on the 6526 Complex Interface Adapter (CIA) chips. These two chips handle most of the I/O (input/output) work that is required for all the peripherals except the ones that produce the video displays and the audio output.

#### DIAGNOSTIC PROGRAMMING

Once you get into this book, you'll progress through the following steps.

You'll get an idea of what the printboard looks like as you take it apart with directions in Chapter 2.

- (2) You will become familiar with the location of the chips as described in Chapter 3.

- (3) Chapters 5 through 9 will give you a good idea of what the C128 is doing.

- (4) You will be briefed enough to intelligently perform a lot of your own tests using PEEK and POKE in BASIC, or the machine language monitor commands: MEMORY and FILL (M and F), which perform the same jobs.

#### PEEK and POKE

Using the function PEEK and the statement POKE gives the C128 the opportunity to test itself and then tell you about it. It is an excellent self-test and works well as long as the C128 is not down completely. Should there be a power supply problem, or other major problem, then the computer obviously can't test itself. However, if the machine is operating somewhat, but is exhibiting glitches or other erratic behavior, then you can often pinpoint the circuit and chip that is defective with these test techniques. If you have been doing any programming at all in BASIC, then you are well prepared to write a tiny test program, run it, and come to diagnostic conclusions.

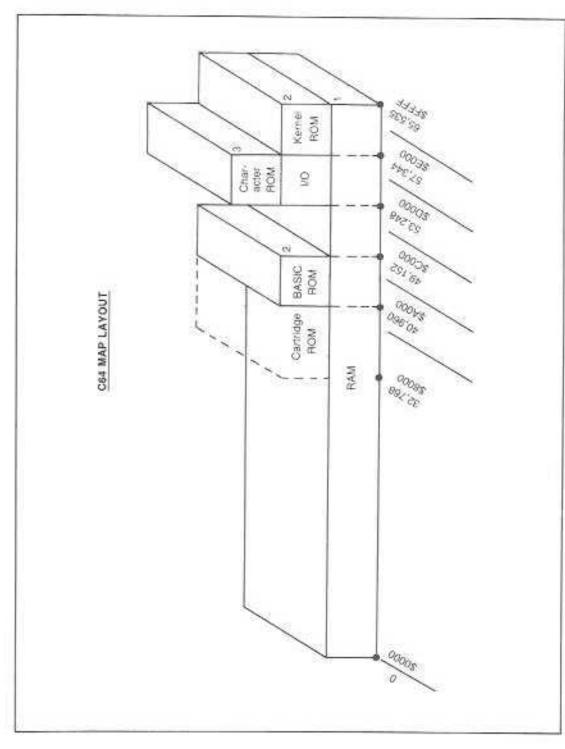

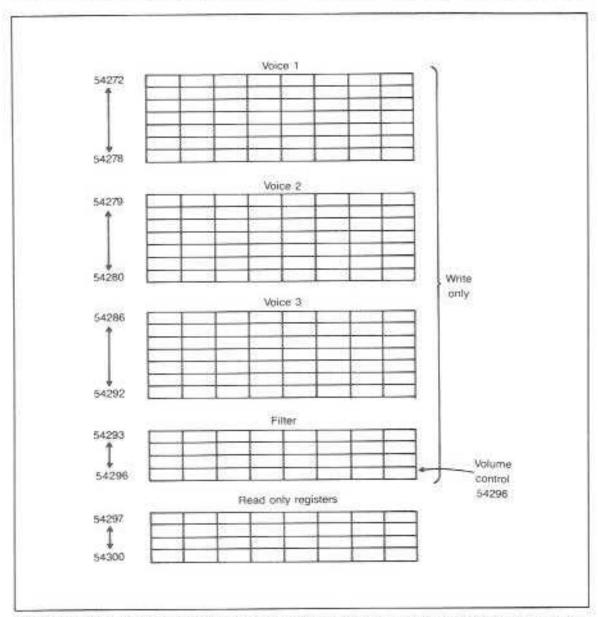

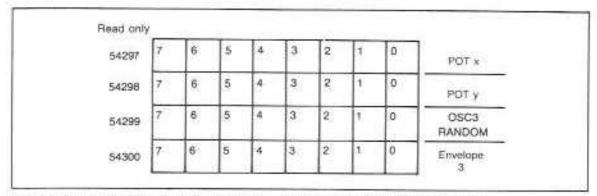

PEEK allows you to read the contents of any of the locations in the C128 or C64 memory map. This includes all the ROMs as well as the RAM (Random Access Memory) chips, and includes addresses on the map that are in registers on large chips like VIC, SID, and the CIAs. As long as the location is on the map, you can read its decimal contents which in turn can be converted to hexadecimal and binary.

POKE permits you to load a byte or bits into all of the memory addresses, with the exception of the read-only locations (ROM). POKE gives you the ability to run test data back and forth between the processor and the residents of the memory map.

Two ways might be used to get the PEEK and POKE tests to operate. First, you can use them directly without program numbers. Simply type in the desired program line, then press RETURN. If the line orders a PEEK, then the addressed location will yield its contents and PRINT on the display the decimal number equal to the binary contents of the location. Should the line command a POKE, then the binary equivalent of the decimal number you put

in the line will be put in the location addressed by the line. It's really easy because PEEK is, in reality, a "read" operation and POKE is actually a "write." In the direct mode (e.g., LIST or RUN) these operations are performed without further ado.

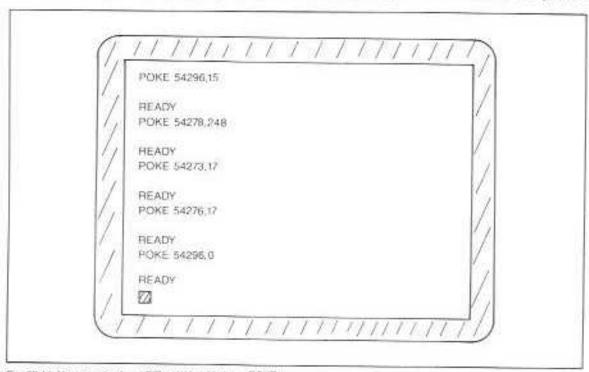

Otherwise, you could write a tiny test program with numbered lines. You could, for example, write to some locations, install numbers in the locations with POKEs, and then read those locations with PEEKs. Another common test program could POKE numbers into registers to see if the registers are performing. When you POKE registers on a chip, it is exactly like working the switches of a control board of the chip.

When you use POKE and PEEK as a signal injector and location tester in the C128, the only tricky part is having a clear idea of the relationship between decimal numbers and the set of bits in a byte that the decimal numbers represent. When you POKE a number into memory, you type a number that is code for a particular set of digital bits. As you PEEK a memory location, a decimal number is returned to you and is PRINTed on the screen. The decimal number is the code for the set of eight bits that are contained in the register you have just read.

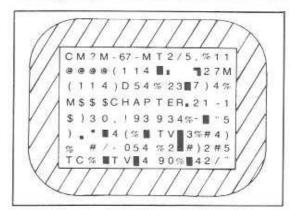

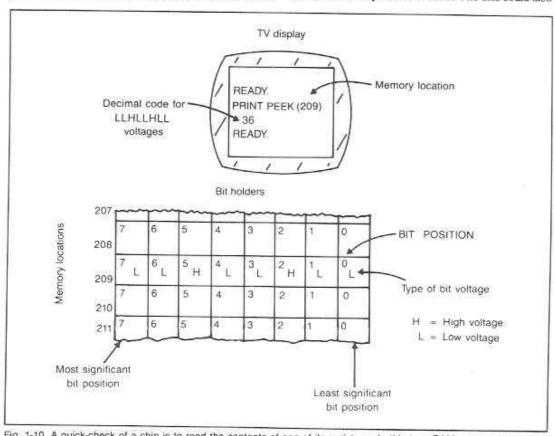

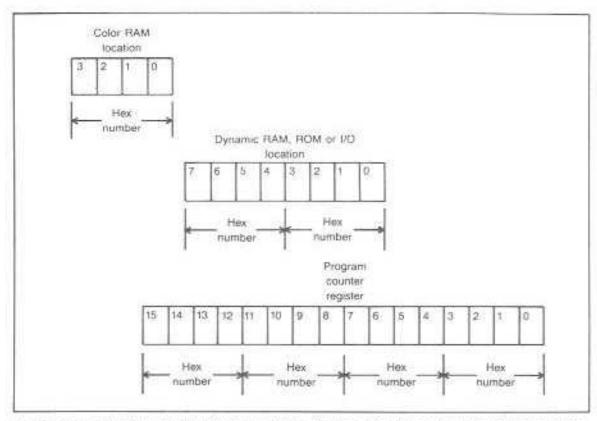

For example, if you are in the C64 mode, then you could desire, for troubleshooting reasons, to learn what the contents of address number 209 are. It's easy. Simply type in: PRINT PEEK (209). As seen in Fig. 1-10, the answer 36 is PRINTed on the display below your command line. This 36 is decimal for the binary bits 00100100. The bits could also

Fig. 1-10. A quick-check of a chip is to read the contents of one of its registers. In this test, RAM register 209 in C64 mode is read with a PEEK. When decimal number 36 is returned, the register is considered okay.

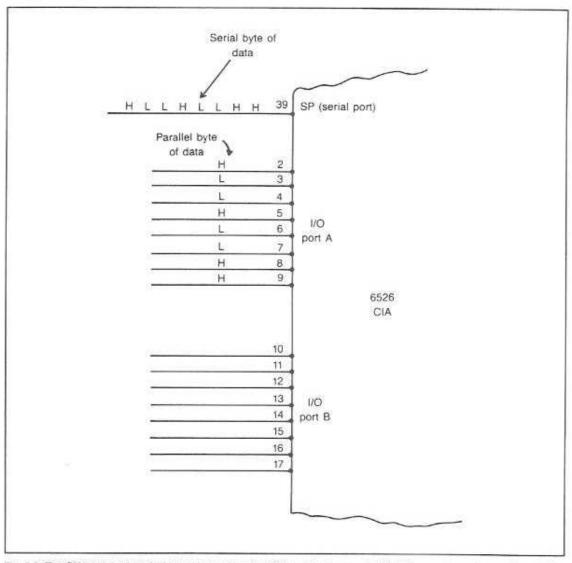

be called LLHLLHLL. The programmer usually thinks of the bits as 1's and 0's, while the electronic troubleshooter sees the bits as H's and L's (Highs and Lows). Anyway, the PEEK function can easily read the contents of location 209 while the C128 is used as a C64. A programmer might need the binary arrangement to switch data around in the program. A troubleshooter could use the information to compare the actual contents of 209 to what is supposed to be in 209 at that time. If the correct bits are present, then the location is considered okay. Should the bits be missing or incorrect, then that is a clue that could lead to the pinpointing of a fault.

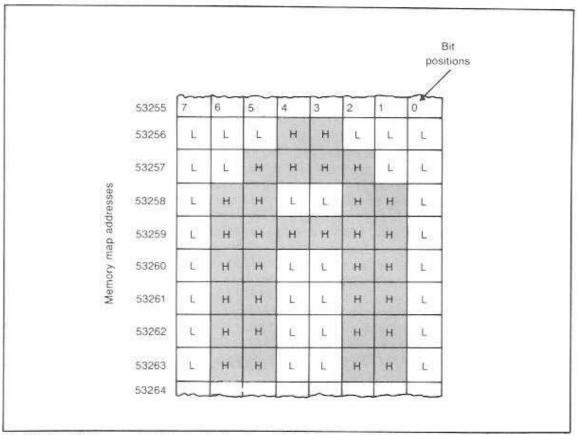

Another example of using these techniques also refers to the C128 acting as a C64. Suppose that you want to quick-check the operation of the color RAM chip. A fast test could be a change of border color on the display. Location 53280 controls the color of the border. It so happens that if you write the decimal number 8 to that location, the border will change to orange-if the chip is okay. You can enter POKE 53280,8 onto the keyboard. As you hit RETURN, the TV picture border should change from light blue to orange. If it does, then the quickcheck infers that the color RAM chip is okay. Should the POKE produce no effect, or the wrong effect, then the chip or its associated circuits are indicated to be in trouble. This is only a quick-check. The inference is that if the chip responds well to one sure test then odds are good that the chip is okay. There is always the possibility that there could be some other subtle form of trouble that the test is not revealing. However, when a test like this is made and works out okay, chances are very good that the entire chip is okay.

The 53280 is the decimal address of the color RAM register. The decimal eight is a set of bits, called 00001000 or LLLLHLLL. The color RAM uses the four lowest bits, HLLL, to switch the border color to orange.

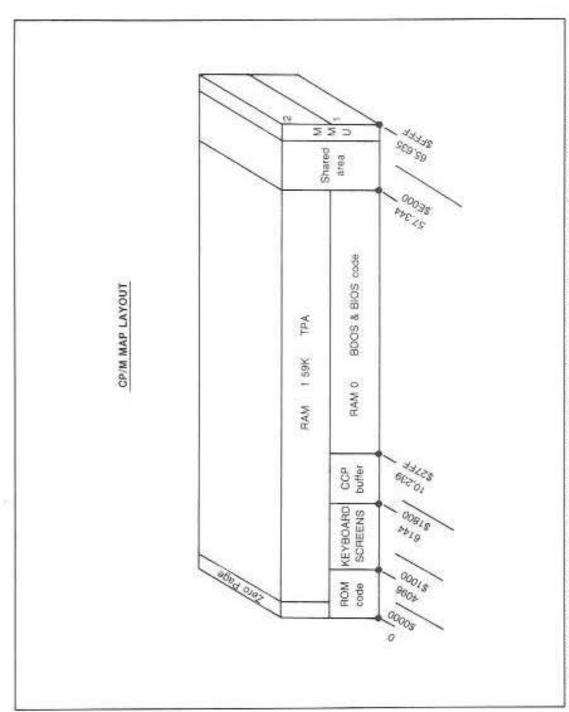

PEEK and POKE can be used as a location tester or signal injector. BASIC is used in both the C128 and C64 modes. It is not used in the CP/M mode. These easy tests are not readily available in CP/M as they are in BASIC. CP/M and BASIC are not permitted to run at the same time. When in C128 or C64 mode you'll find that the PEEK function and the POKE statements can be used over the entire 128K RAM that the C128 uses, and the full 64K RAM that the C64 has privy to. In addition, POKE and PEEK can be applied to the various static RAM chips, the ROMs, the I/O chips as well as the addresses on the video and sound chips. You should consider the locations on the memory map as bit holders and the decimal data you read out of the locations and write to the locations as code for the bits. There will be more on these techniques as you go through the book.

#### Diagnostic Programs

Besides reading and writing to individual addresses with PEEK and POKE directly, you can, once you acquire a troubleshooting point of view, also write programs that perform batteries of tests and check out large portions of the memory map. One useful diagnostic programming technique is to place PEEK and POKE in loops. A POKE in a loop can make the C128 able to write to a large group of memory locations automatically, one after the other. A PEEK in a loop could have the C128 read many memory locations and print the results in decimal on the screen.

For example, a diagnostic program could be used to test the ability of memory locations to contain data, while at the same time checking out bus lines for continuity. You would first write program lines that POKE data into locations. Then you write PEEKs to check and see whether the POKEs ever arrived and were installed okay. If all the locations you wrote to are holding the data securely, then they and the bus lines connected to them are considered okay. Should some or all of the data not have reached their destinations, you can then trace out the path they were to have taken. Some sort of problem stopped the data flow. You have diagnosed a suspect circuit area with your test program. There will be more on these techniques in Chapters 14, 15, 16 and 18.

In addition to writing your own test programs, there are diagnostic programs available. Check with your local software store for the names of ones that are for sale. For example, there is one diagnostic that has been around quite awhile for the C64. You can use it for the C128 when it is in the C64 mode. It is called "64 Doctor." It is manufactured by:

Computer Software Associates 50 Teed Dr. Randolph, MA 02368

Commercial diagnostics are normally fancier than the ones you will produce—they are prettied up with graphics. Once you load the diagnostic into the machine, then a menu pops up. One option checks out the disk system and the C64 mode's internal RAM. It is limited in that it can only test 64K of the 128K in your machine. Next, there are tests for the keyboard, a printer (if it is connected), a cassette (if it is connected) and joysticks. Another test runs patterns to check out your color TV or monitor. Lastly, the program makes the SID chip perform some music.

This diagnostic also works out the graphics on the C64 mode. It produces sprites that look like a TV set, a printer and so on. The sprites march around the display.

For troubleshooting, a program like this has use but is limited. First of all, if the computer is down completely, then it can't run any program, including the diagnostic. However, the program can sometimes decide whether a peripheral problem is located in the peripheral itself, or if the computer circuits are not performing properly. Should you be unable to substitute a peripheral that is known to be good for a suspect peripheral, as a test, this program could help.

While these programs are fun and occasionally useful during troubleshooting, they can be valuable before you begin a programming session. Should you be planning a long program, it is a good idea to exercise the C128 everyday before you put program lines into the machine. If the machine exercises okay, then it is safe to work on. It is very frustrating to spend hours programming, and then discover there is some fault with the computer.

#### PRINTBOARD LANDMARKS

A C128 user is mostly concerned with software and applications. However, when trouble strikes. that focus must be changed. You must switch your view from the software to the hardware that is running the software. The next chapter describes how to open up the C128 and get the printboard out in the open. Once the printboard is exposed, you will see a complex maze of chips, capacitors, resistors, foil connecting lines and many other items. In order to make any sense out of the layout, you have to find out what all those components and connections are. The place to start is with the landmarks. Once you recognize them, you'll start to get to know your way around.

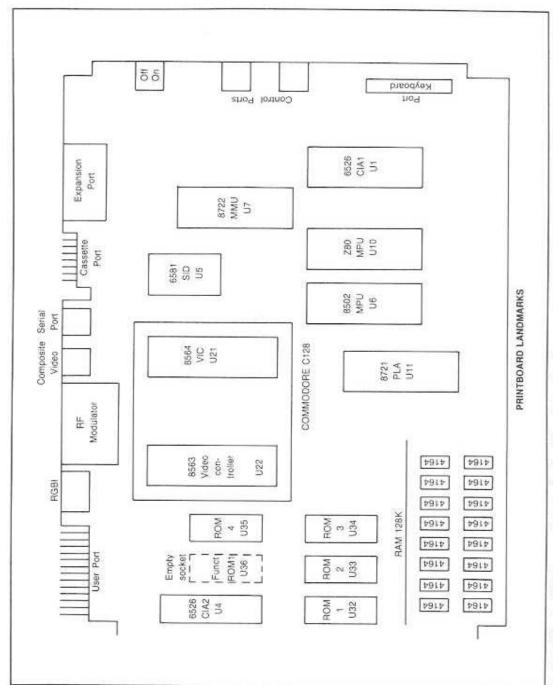

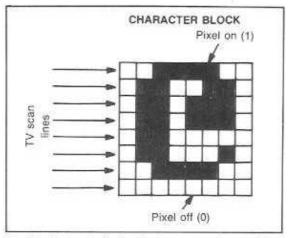

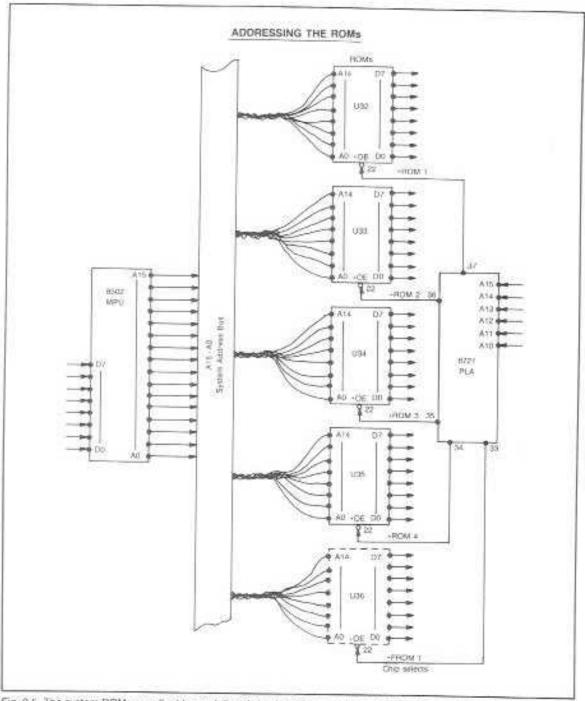

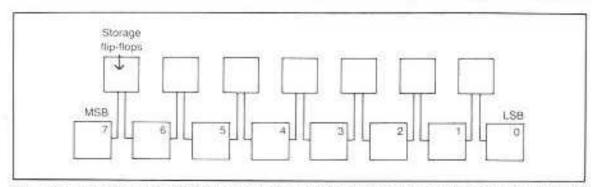

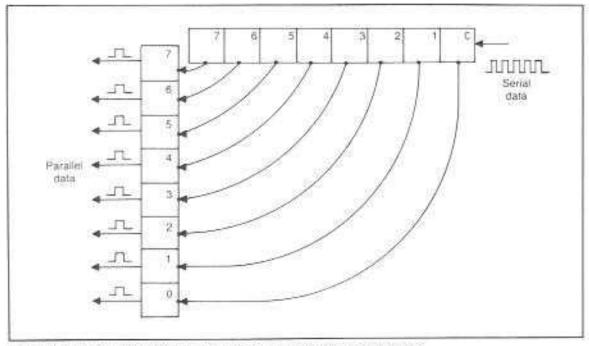

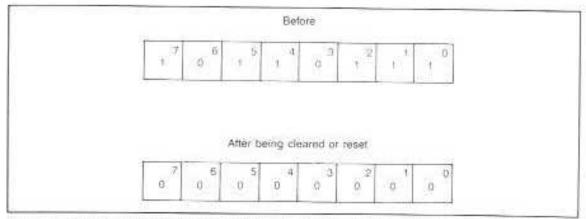

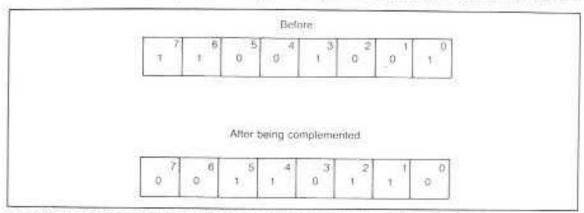

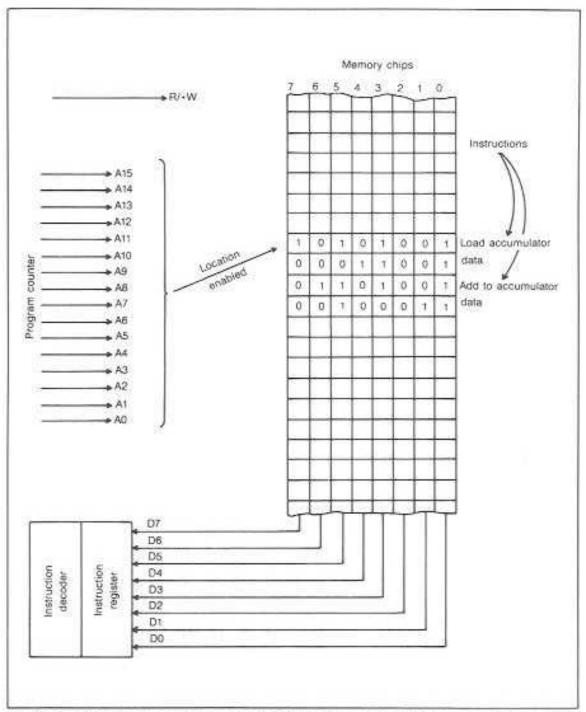

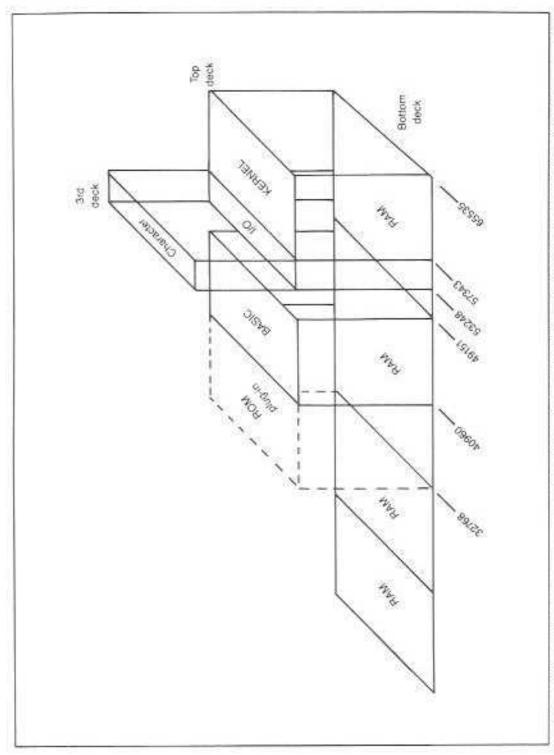

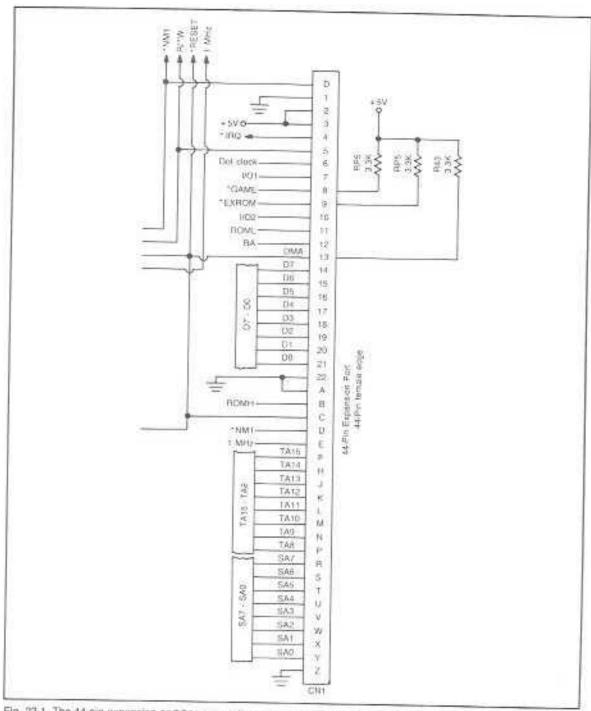

The main landmarks are the large chips, the group of ROMs, and the collection of 16 RAMs. A close look reveals the data and address buses coursing over the board. Figure 1-11 depicts the nine large chips, the locations of the ROMs, and the RAMs.

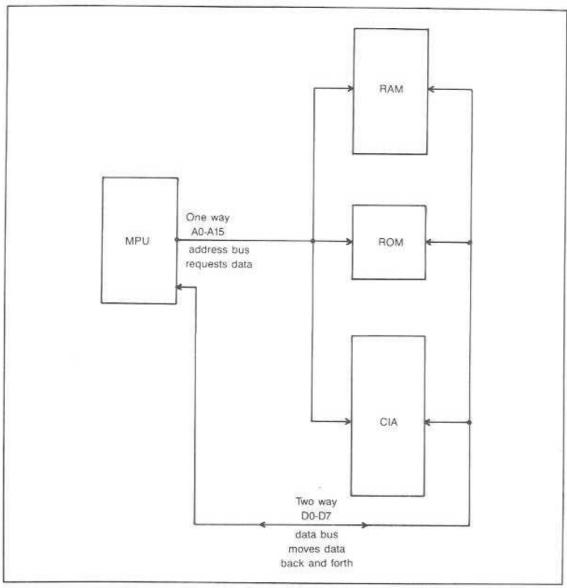

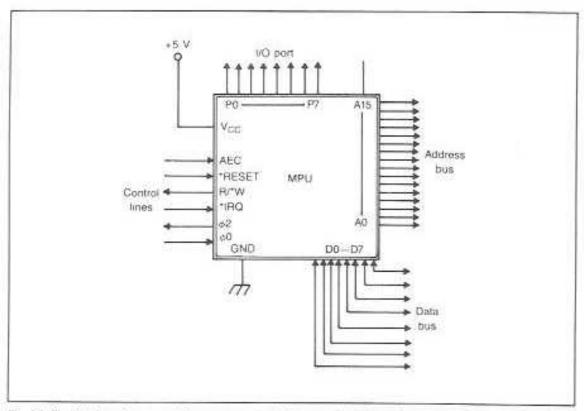

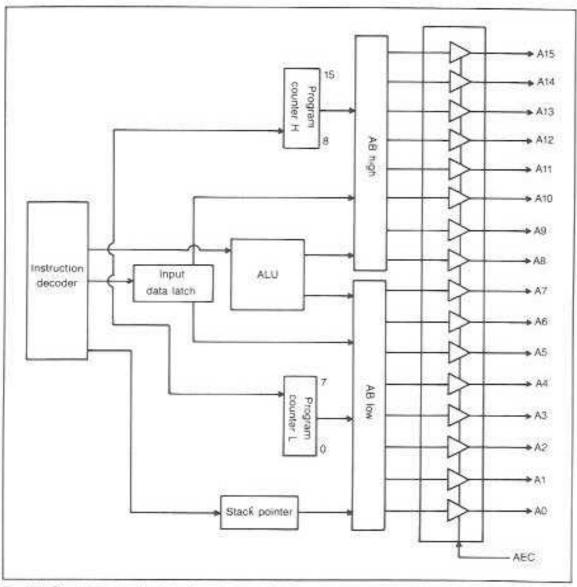

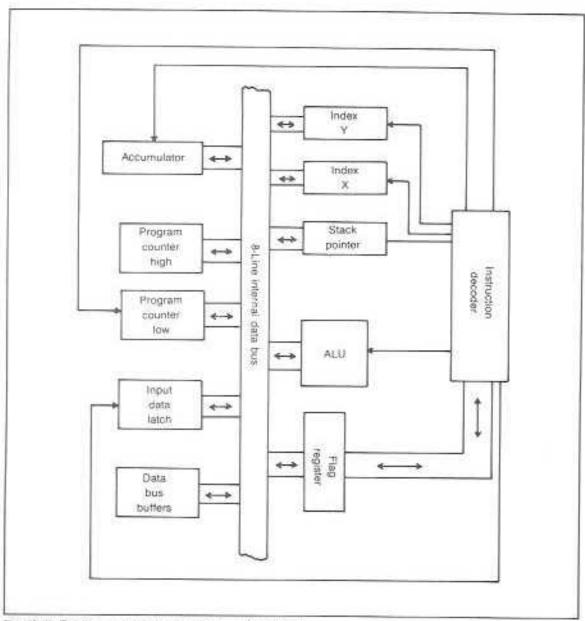

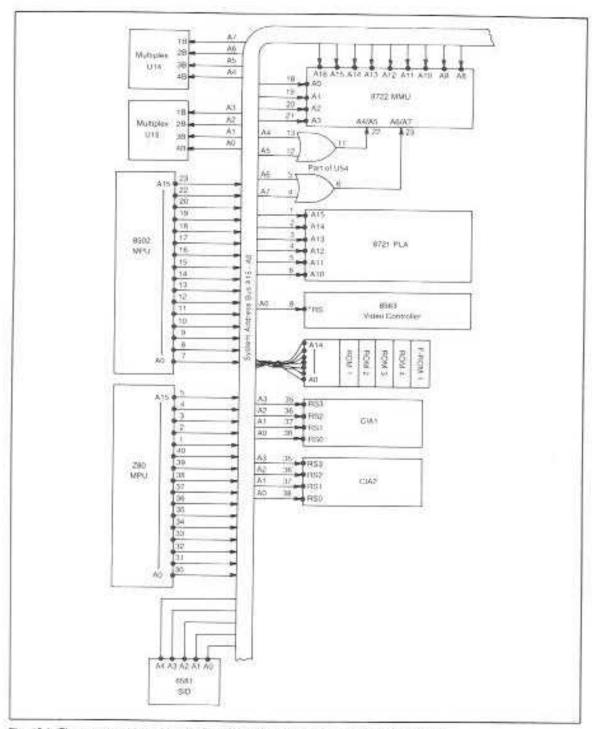

Figure 9-1 is a block diagram of how these chips are connected electronically, and the directions that the data takes. The data flows over the system data bus. The data enters the circuits via the keyboard into a CIA, and passes onto one of the MPUs. The MPU then reads the ROMs, reads and writes to the RAMs, and then outputs to one of the video chips, a second CIA and to SID. The video chips in turn output to the display and SID outputs to a sound system.

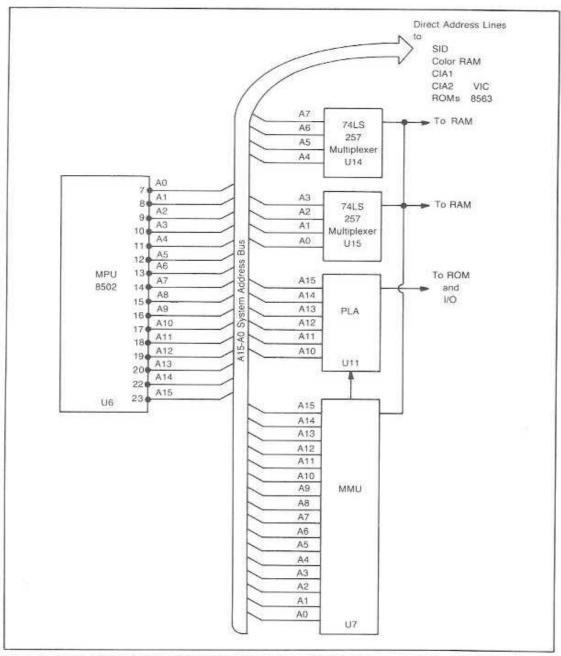

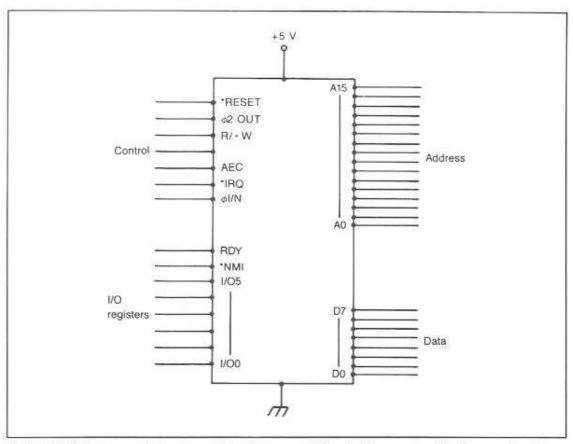

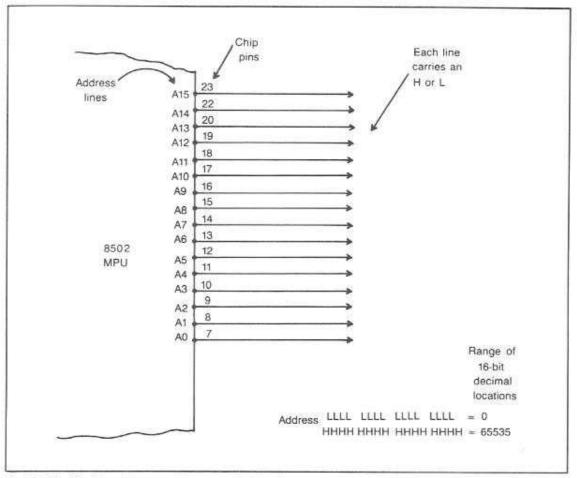

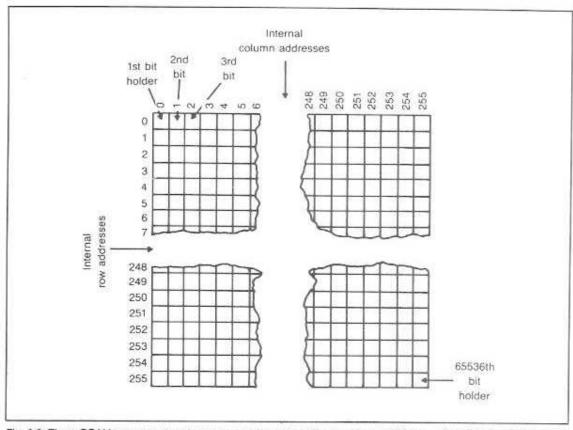

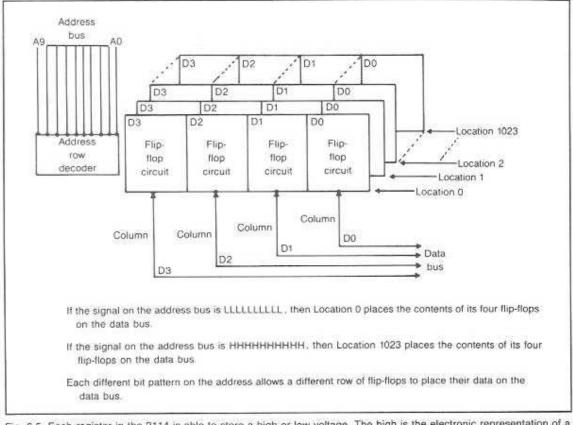

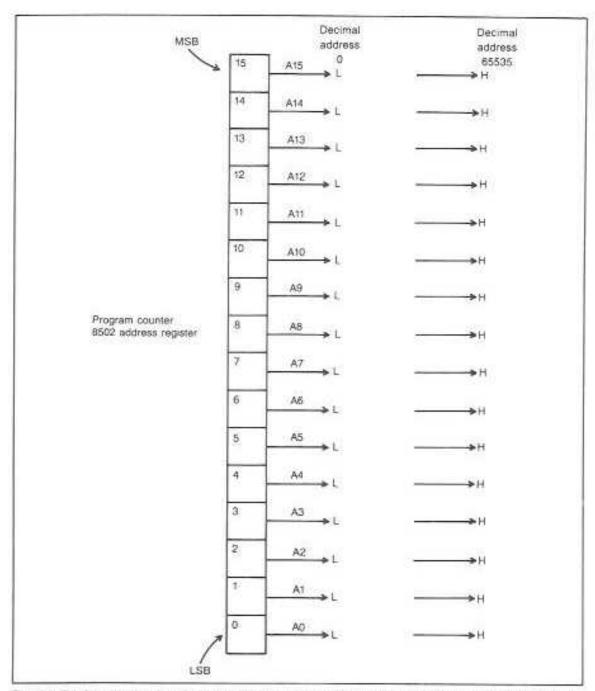

Figure 1-12 shows how the address bus performs, and how the chips are involved. The addressing emanates from the MPUs. They send the address signals to the PLA (Programmable Logic Array) and the MMU (Memory Management Unit). These two chips then form the various addresses and they are able to contact all the residents of the memory map. When a memory location is addressed by this system, then data can be sent to its bit holders.

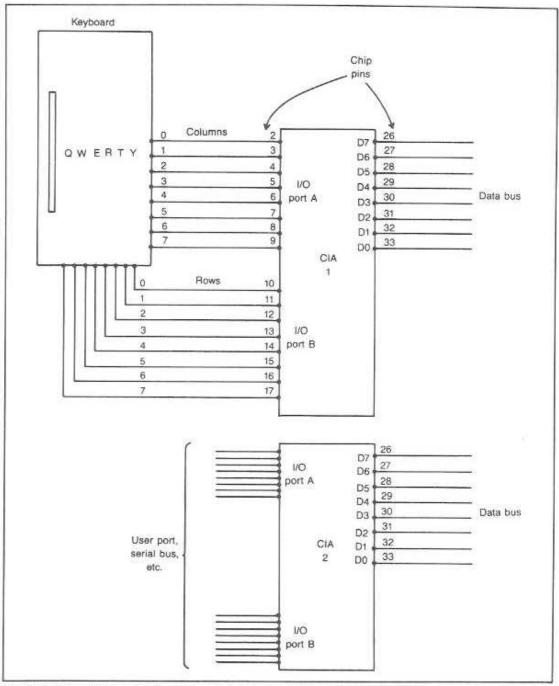

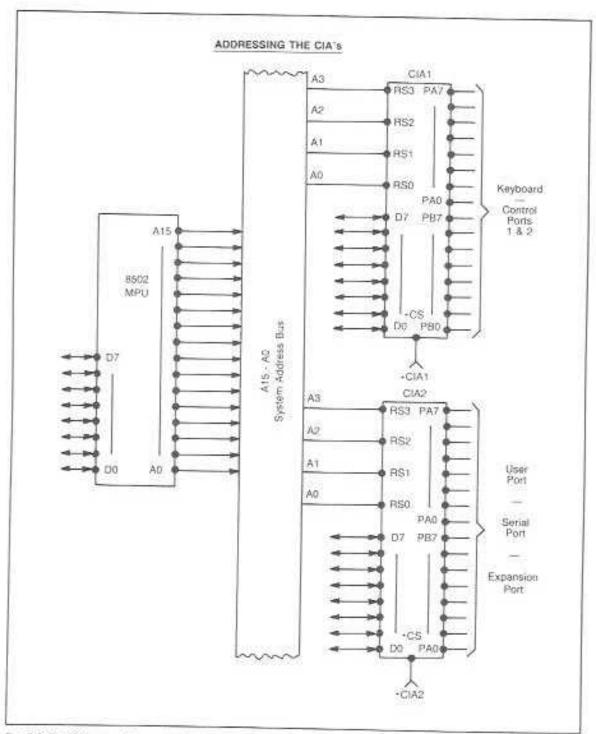

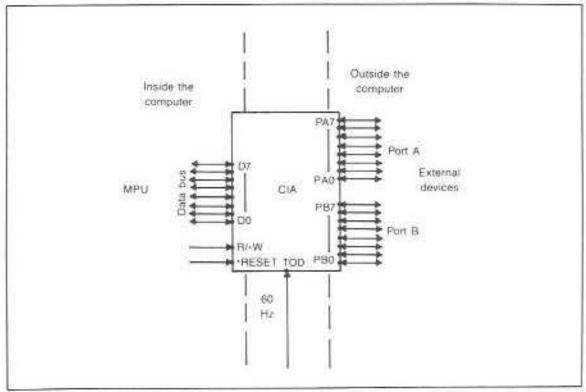

#### Complex Interface Adapters

The two CIAs, U1 and U4, are physically located on the two sides of the printboard. U1 is found in the lower right-hand corner and U4 is on the edge of the left side just above the center of the board. Both chips are plugged into 40-pin sockets. They are both numbered 6526 and are called CIAs for Complex Interface Adapters. The right side one is

Fig. 1-11. When the C128 is opened, the landmarks of the printboard can be seen. The landmarks are the large chips, the RAM and ROM sets, the metal boxes and the various ports.

Fig. 1-12. The 16 lines of the addressing system originate in the MPU. They are named A0 through A15. The lines go to all the residents of the memory map. The 16 lines are able to address 65,536 individual register locations.

wired to a plug that the keyboard is connected to. This is the keyboard's port of entry.

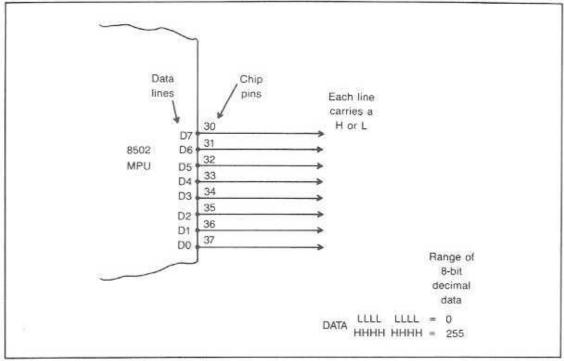

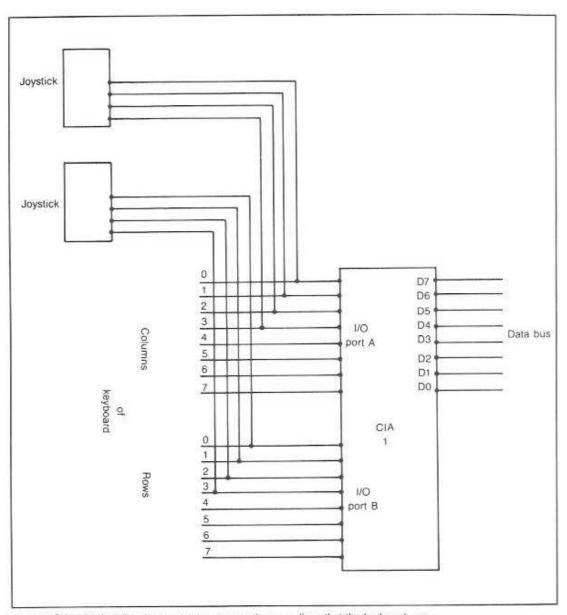

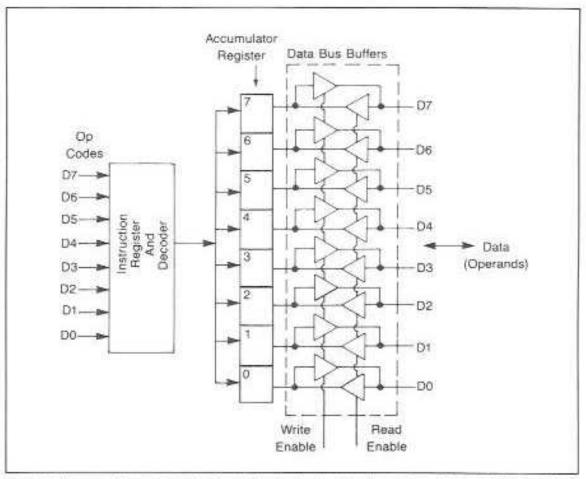

The right side CIA, called "CIA1" on the schematic, besides letting the keyboard pulses in, also is the port of entry for the two input plugs the joysticks and other peripherals use. When a key is struck or a joystick is moved, the electronic signal generated enters U1, the CIA1. The signal is processed by CIA1 and is then output to the eight parallel copper traces called the "System Data Bus." The data bus then acts as the pathway for the signals to connect up to the microprocessor further down the board.

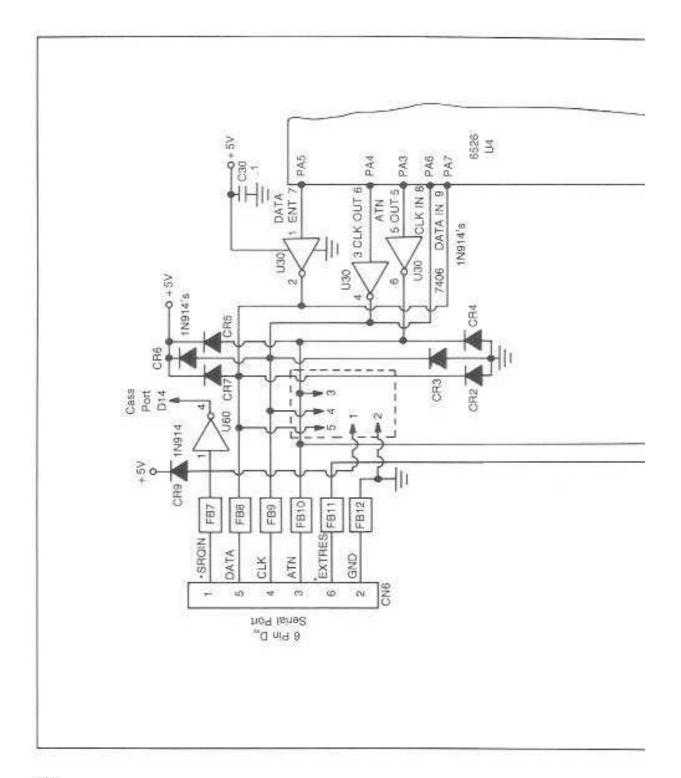

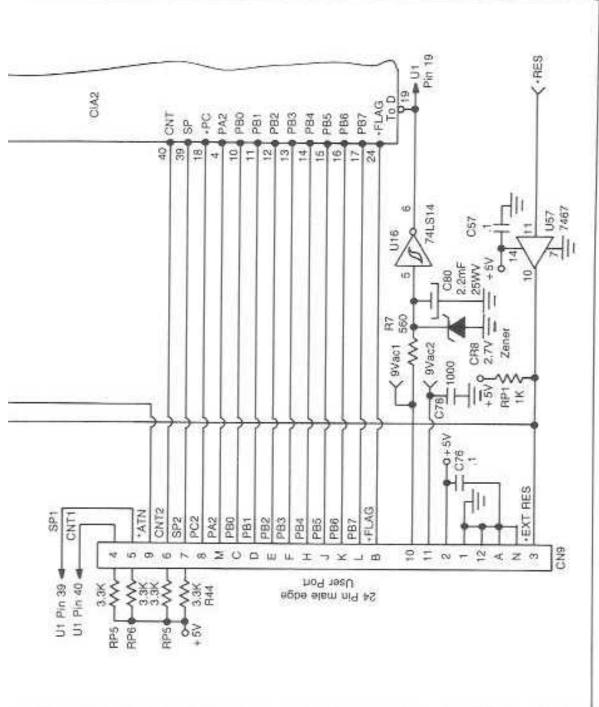

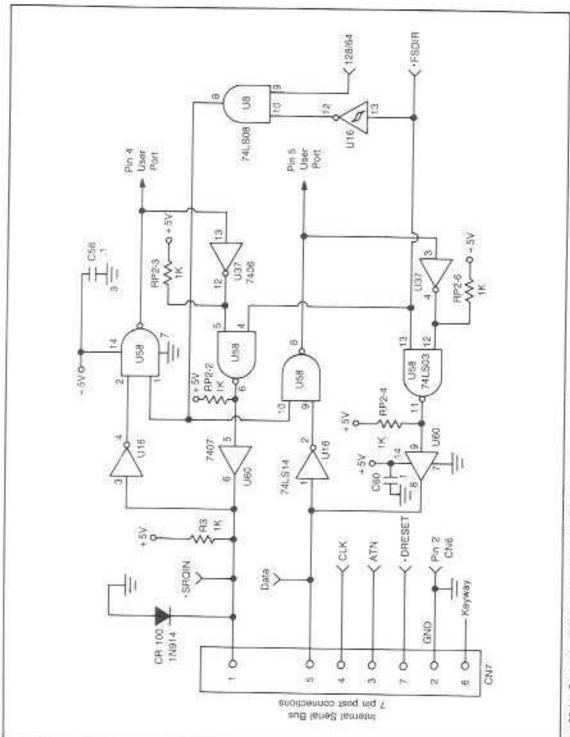

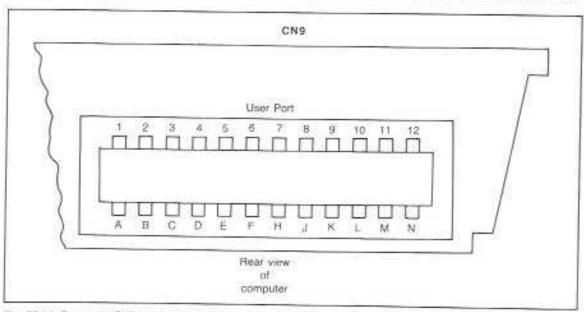

U4, called "CIA2," on the left side of the board, is the port of entry for signals entering or leaving the User Port and the Serial Socket. CIA2 performs in the same manner as CIA1.

When I/O troubles crop up, an easy analysis can clue you into the circuit area that could possibly be containing the fault. This is shown in Table 1-1. For instance, troubles with keyboard or control port inputs could be originating in U1, the CIA1. Problems with the input or output of the User Port or the Serial Port could be a CIA2 circuit flaw. Chapter 23 goes into details on this I/O subject.

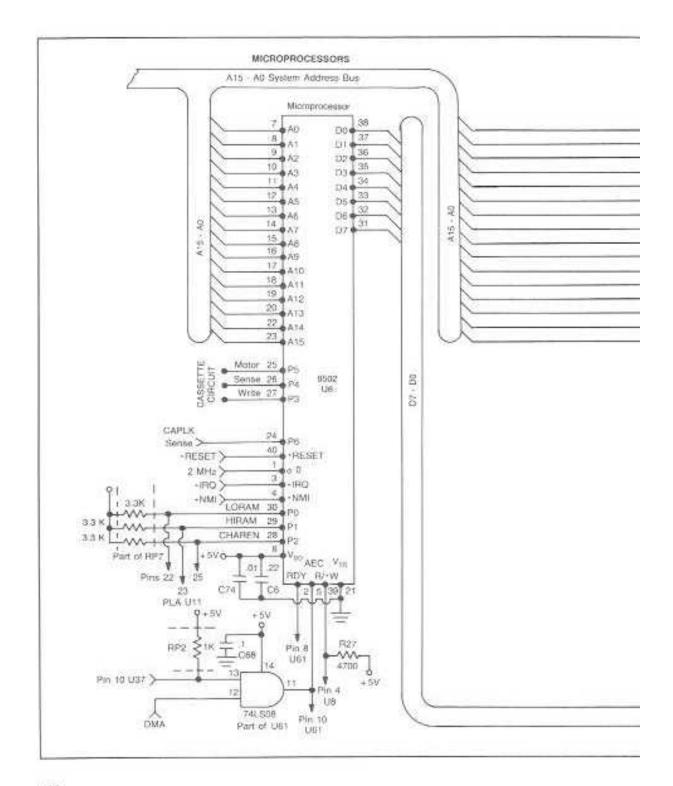

#### The Microprocessors

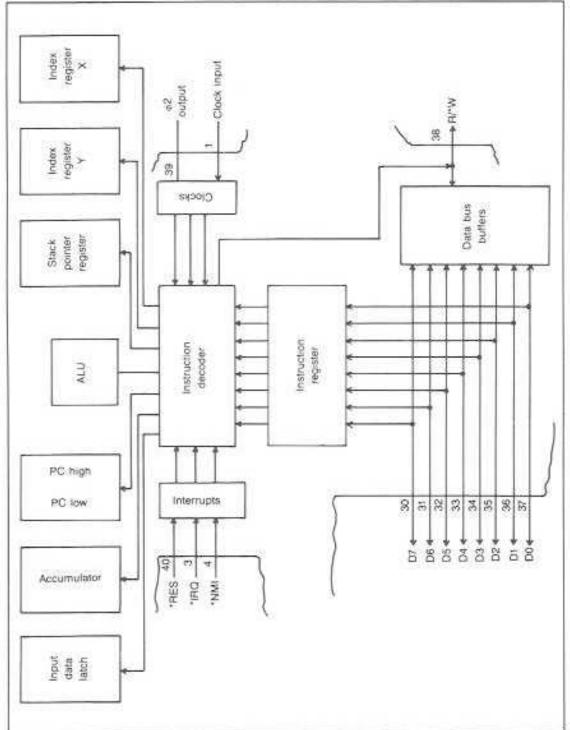

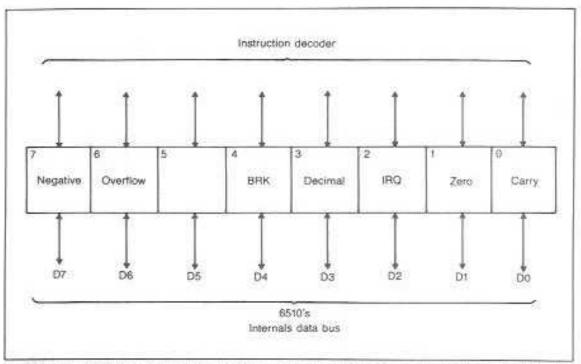

There are two microprocessors in the C128. The main processor is U6, an 8502. It is an upgrade of the 6510 processor found in the C64, which in turn is an upgrade of the 6502 that resided in the VIC 20 computer. All three processors use the same Instruction Set.

The 8502 sits in the lower right quadrant of the printboard. It is in the center of the circuit. It is the originator of the data bus and the address bus. It does not have addresses on the memory map. It can be likened to a central telephone exchange—the locations on the memory map are the telephone numbers that the exchange services. The CIAs have addresses, and when the 8502 dials them up they respond over the data bus. While the addresse bus is only one-way from the 8502 to the addressed location, the data bus is two-way and can be read from, or written to, by the 8502.

The 8502 is used when you put the C128 into the C128 or C64 modes. Besides connecting to the CIAs, the data bus from the 8502 hooks up to all the rest of the memory map locations. This is discussed in detail in Chapter 18.

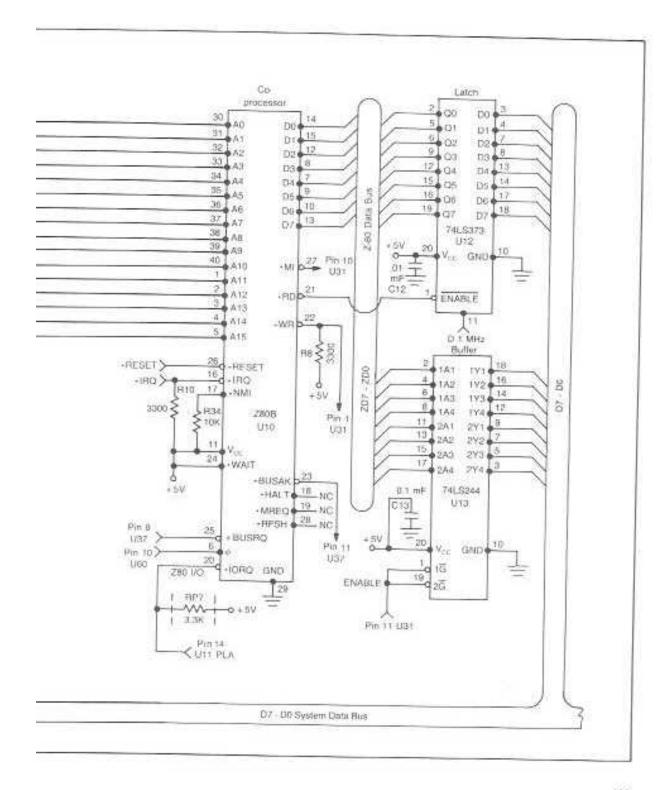

U10, the Z80 microprocessor, is called the "Coprocessor." It is a full-fledged processor on its own. But since the 8502 handles the C128 and C64 chores, the Z80 is given a subservient role. The Z80 conducts the CP/M activities of the machine. It is located on the board, next to the 8502, on the right Both processors have 40 pins. However, the 8502 is plugged into chip sockets but the Z80 is not. The Z80 is soldered directly to the printboard.

The two processors work independently of each other. When the 8502 is operating, the Z80 is disabled and sits quietly. As the Z80 takes over for the CP/M operations, the 8502 is turned off and just waits idly by. With the two separate processors, the C128 total machine thus becomes a form of Siamese twin. The twins are joined at the I/Os and memory. Furthermore, since the 8502 is conducting both C128 and C64 operations separately from each other, a third machine is present making the C128 package Siamese triplets.

When trouble strikes a processor, the function it is executing will fail. If the 8502 gets sick or dies, the C128 and C64 operations will be the ones to suffer. When the Z80 passes away, the CP/M operations won't work. The 8502 and its problems are covered in Chapter 12. The Z80 processor is discussed in Chapter 13. There is more about both of them in Chapter 5.

#### The Addressing Management Chips

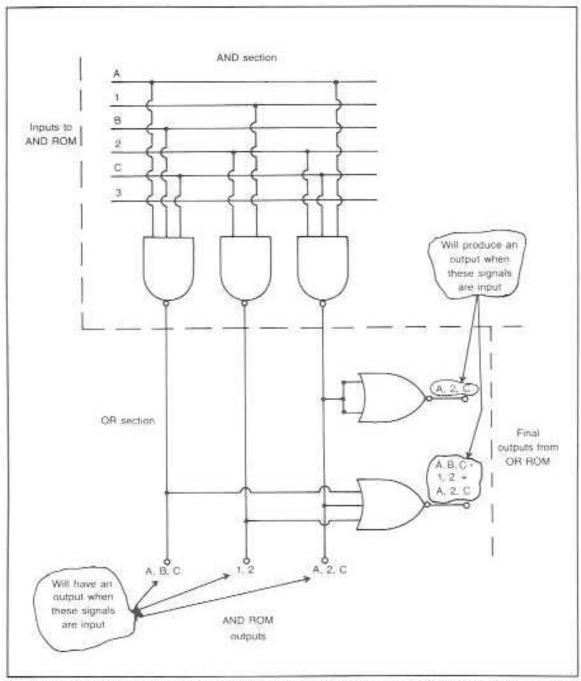

When one of the processors dials up an address, all of the bits do not travel directly to the desired location. Some of them are routed to two substation chips. They are U11, the 8721 PLA and U7, the 8722 MMU. The PLA, U11, is a 48-pin chip and is soldered at center bottom of the printboard. The MMU, U7, is also a 48-pin chip and is located in a socket on the right-hand side of the board about halfway down. The PLA is covered in detail in Chapter 14. PLA stands for Programmed Logic Array. The

MMU is discussed in Chapter 15. MMU is short for Memory Management Unit.

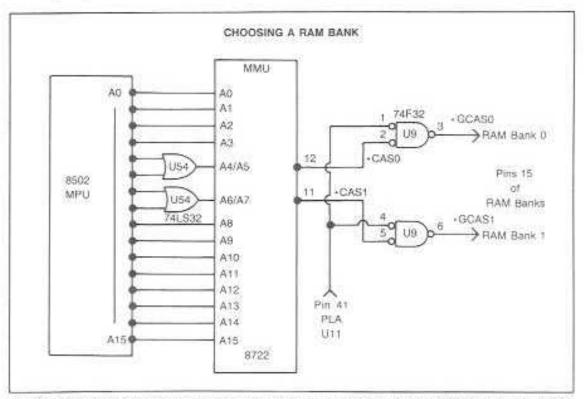

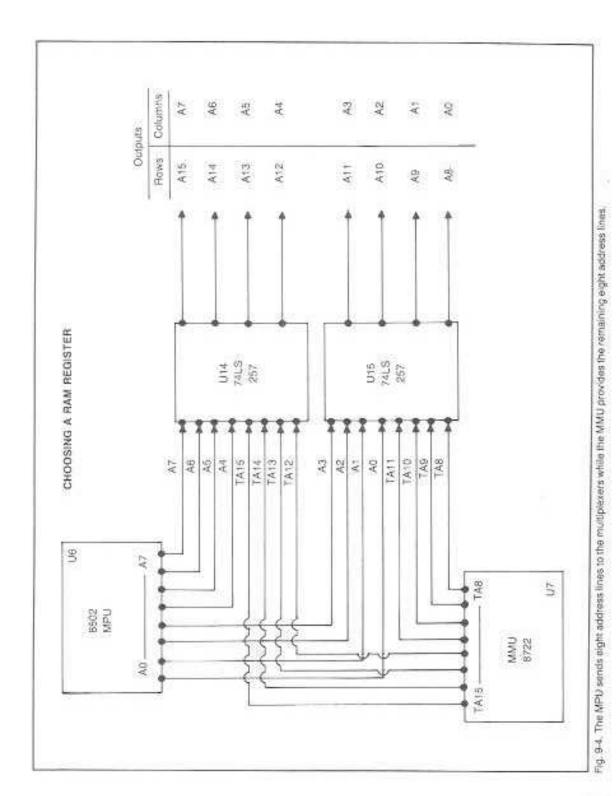

The two large chips work together to keep the addressing straight. With two processors, five various operating modes, two separate type video output chips, 128K of memory in two 64K banks and many other complications, these chips have their registers full.

When trouble strikes in these chips or their circuits, the main symptom is bad addressing, which can result in garbage or other related symptoms.

#### The Video Output Chips

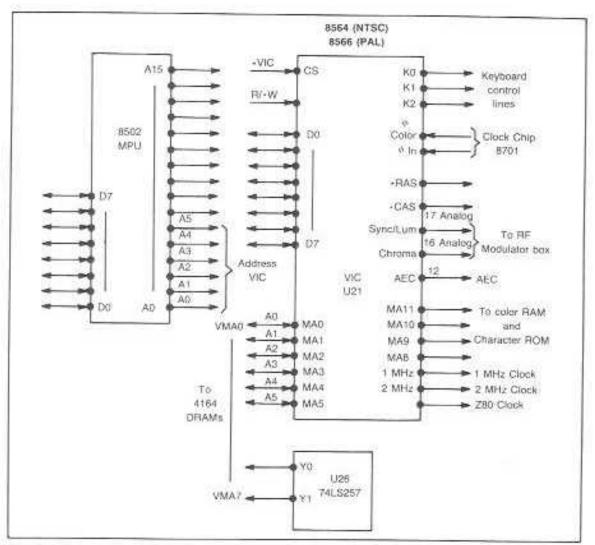

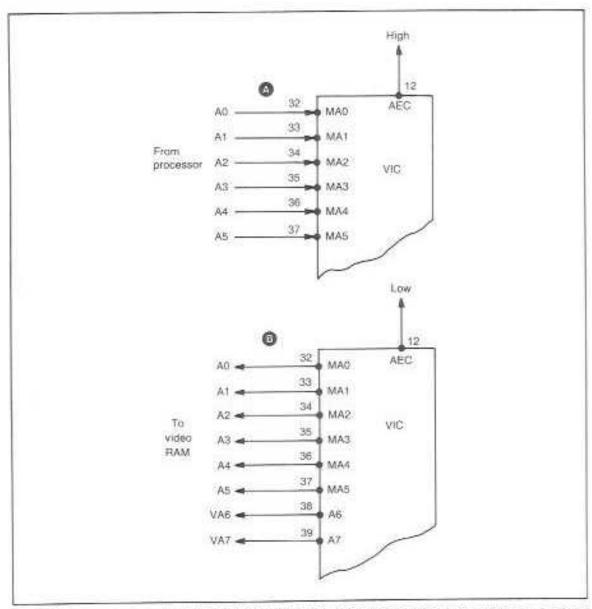

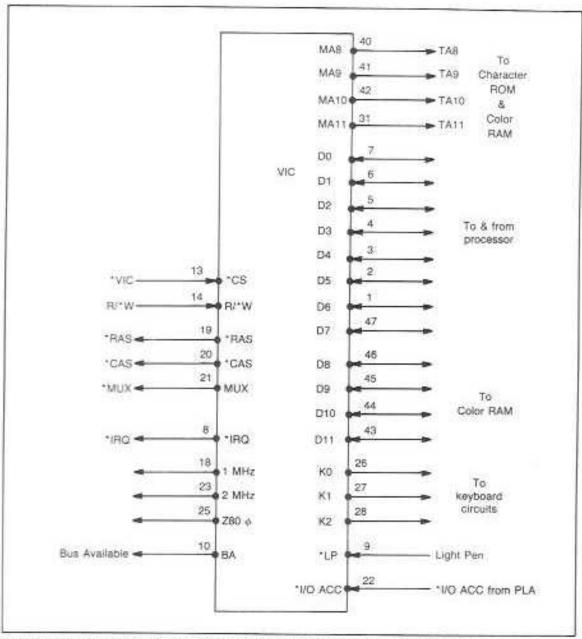

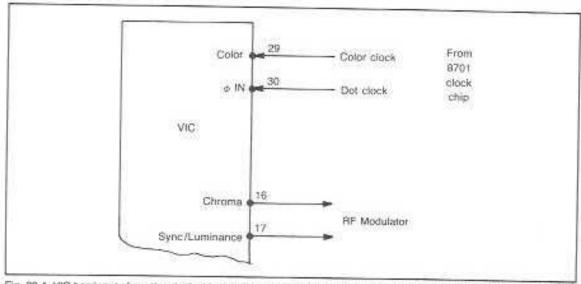

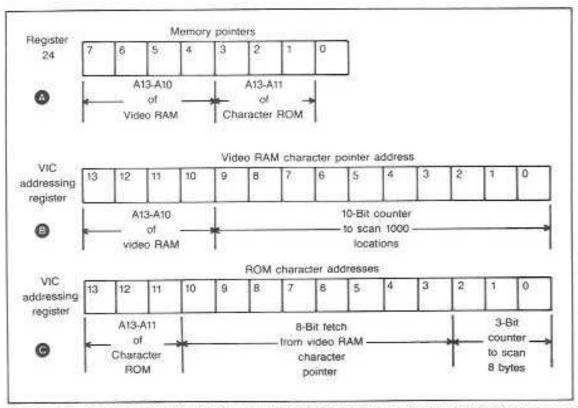

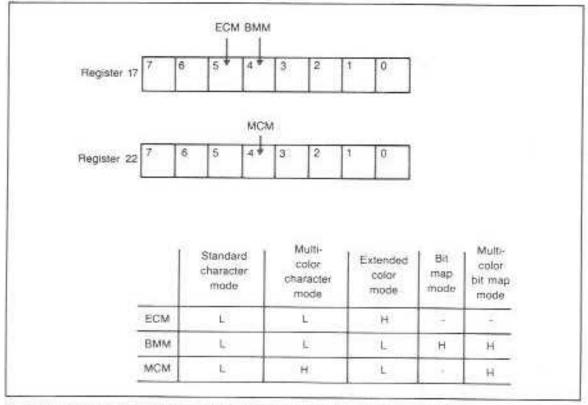

In the upper left quadrant, near the center of the printboard is a metal shielded enclosure. Inside the enclosure, on the right, is a 48-pin VIC chip soldered to the board. It is U21 and named the 8564. It is an upgrade of the VIC chip found in the C64. VIC stands for Video Interface Chip.

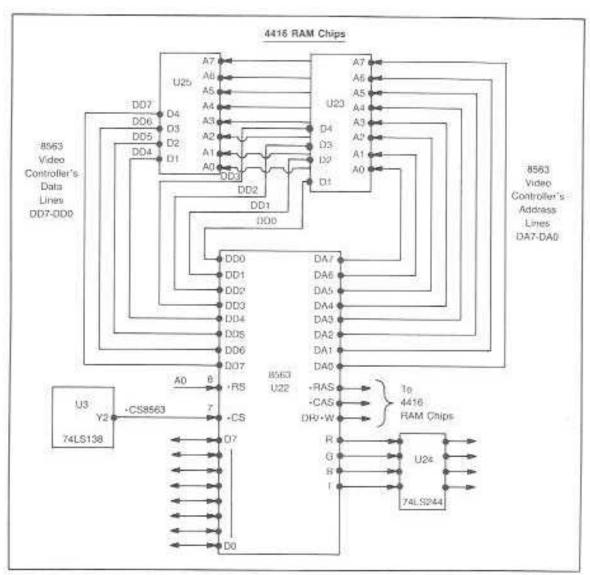

On the left-hand side of the enclosure is another 48-pin chip plugged into a socket on the board. It is U22, the 8563. It is the Video Controller.

These two chips are quite complex and are sometimes referred to as microprocessors. They can do almost the same job as a processor. VIC chips can be used in video game machines as a processor and also as an I/O chip.

The VIC 8564 is the subject of Chapter 20 while the 8563 video chip details are in Chapter 21. These two chips do not work together. Like the 8502 and the Z80, when one is on the other one is off. The VIC chip is used exclusively for all 40-column operations. This includes the C128 40-column mode, the C64 40-column mode and the CP/M 40-column mode. The 8563 Video Controller is used exclusively for all 80-column operations. This includes the C128 80-column mode and the CP/M 80-column mode. The C64 does not have an 80-column mode.

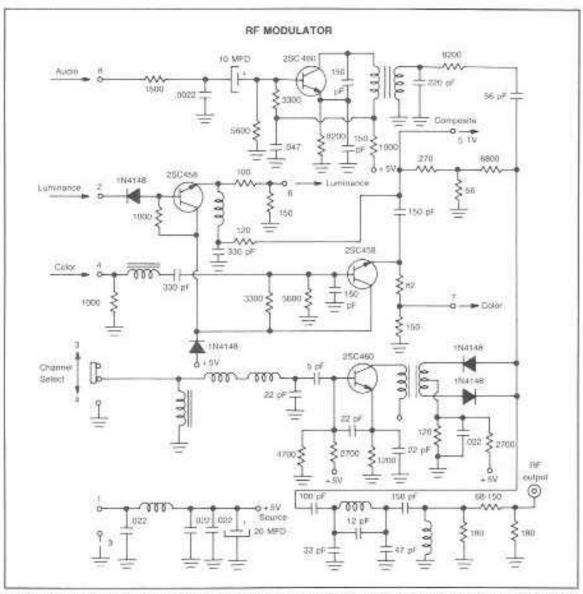

The VIC 8564 outputs directly to both the RF Modulator box at the top of the printboard and to the Composite TV Video plug to the right of the RF Modulator box. These are the exclusive 40-column outputs. The 8563 video controller chip outputs to the RGBI output plug only. This plug puts out only 80-column video signals.

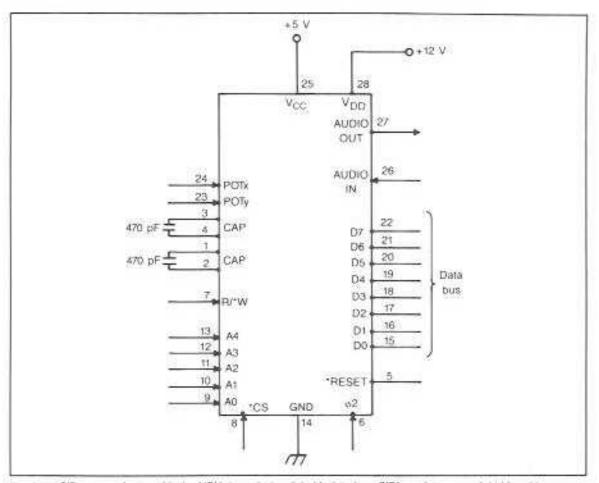

#### The Sound Interface Device

Sitting in a socket to the right of the board's center, in the top half of the board, is SID, the 6581 audio producer. SID is only a 28-pin chip and has little to do with any of the circuits except for the microprocessors. SID takes care of all the sound requirements of the C128. It is connected to address and data bus lines. SID is covered in detail in Chapter 22. When sound troubles occur, SID is the prime suspect.

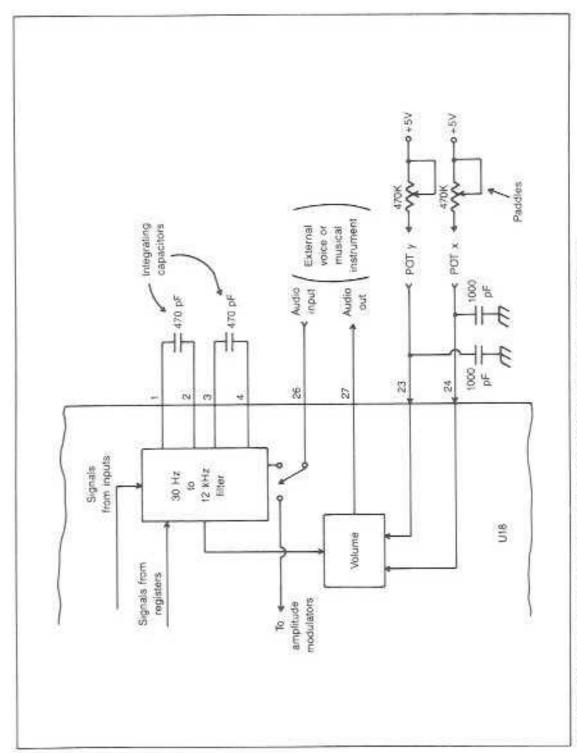

SID outputs its audio to both the RF Modulator and to a couple of pins on the Composite Video plug. The RF Modulator has audio from SID sent into its audio input plug. The Composite Video connector devotes two pins to audio. Pin 3 handles the audio output from SID. However, pin 5 takes care of any audio input that comes from an external device. The outside audio is then sent to SID where it can enter the chip and be processed according to SID's dictates.

#### AN OVERVIEW OF TROUBLE ANALYSIS

When trouble occurs with your C128 system, the first step, as discussed earlier in this chapter, is to determine whether the trouble is in the computer or in a peripheral. When the trouble is in a peripheral, you have the peripheral fixed. Should the trouble be in the C128 itself, then this book applies.

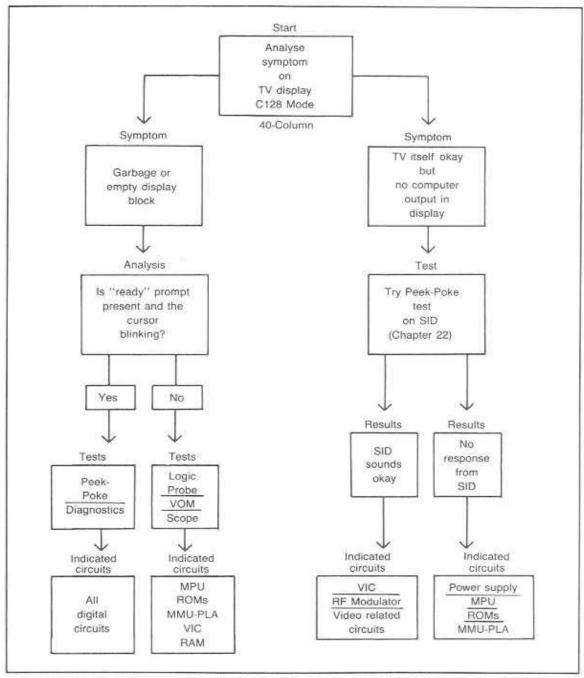

Figure 1-13 is a flow chart that could help you decide the general circuit area on which you should focus. Before you start on the flow chart, if the computer appears dead and the indicator light is out, go no further—the trouble is in the power supply. Chapter 24 contains the service information for that condition.

Should the light be on, then the flow chart can begin. Start by analyzing the symptom. The purpose of the analysis is to decide on what service approach to take. For example, if the usual sign on display is completely gone, and you know the TV is okay, then the computer is not putting out any video signal in that mode. What you must do is figure out if all of the computer signal is gone, or just the video.

A quick test could be to write a test program to SID and determine if SID is outputting. There is

Fig. 1-13. When trouble strikes, a good starting procedure will save you from wasting time. This is an example of the way to go from symptom to pinpointing the defect.

a small PEEK and POKE program in Chapter 22 that will do this. If SID remains quiet, then there isn't any computer output, sound or video. This indicates power supply trouble even though the indicator light is on. Chapter 24 has the test procedures.

On the other hand, if SID does start making test tones then the computer is putting out some signals. By the process of elimination, the video circuits are the prime suspects. Look over the video chapters, 20 and 21.

The other general symptom is: some sort of display, but not a useful one. There could be garbage on the screen, an empty display block, a display that has locked up and won't respond to keyboard strikes, or just erratic operations. You could, in those cases: try the reset button; turn the computer off and on; depress the RUN/STOP and RESTORE keys at the same time. If these measures do not cure the problem, then examine the READY prompt and the cursor. Are they present and is the cursor flashing? If so, you might be able to use PEEK and POKE tests or a diagnostic program you have.

When the READY prompt and the cursor are disabled, then you probably can't get the computer to cure itself. At that point you must resort to the various logic probe, vom and scope tests as described in the book.

## 2. Disassembly

When a C128 gives up the ghost and you make a decision to repair it, then most of the time you must take it apart. The first time you start taking out the screws, you are sure to be hesitant. You know from past experience with many other repair jobs that you could just possibly cause some additional troubles by simply taking it apart. You don't want to start a repair job by causing trouble.

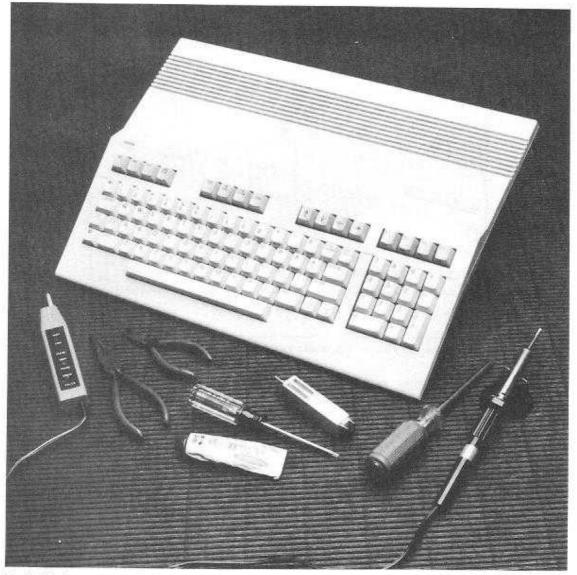

Fortunately, the C128 is assembled in a sensible manner, which makes the disassembly relatively easy, although extreme care and slow moves are the order of the day. The first steps are common sense. Arrange a large enough place for your work. Gather your tools together. Be sure to have good lighting and place a rubber mat on the bench. Disconnect all the attachments to the C128. Place it on the soft mat. Figure 2-1 illustrates progress to that point.

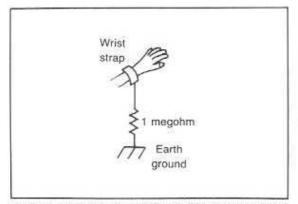

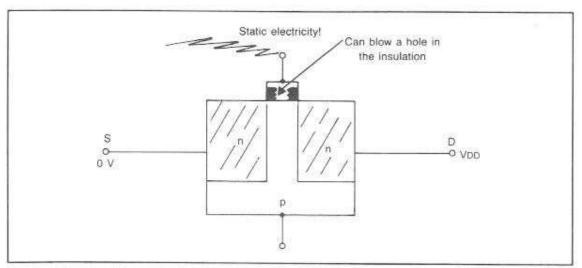

It is a good idea to have the bench area as clean as possible. Dirt and filings that accidentally get into the computer could end up as additional troubles. It is not a good idea to work on the C128 in a low humidity environment. Should it be cold outside but warm and dry inside, with static sparks flying and popping as you walk on the carpet, be extra careful while working on the computer. Static electricity could be death to computer chips. There will be more about the static electricity precautions in Chapter 4.

#### GETTING THE HOOD UP

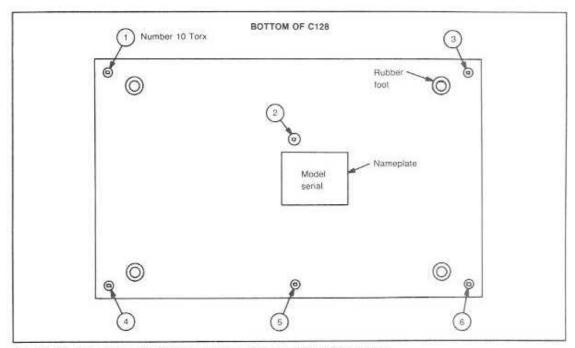

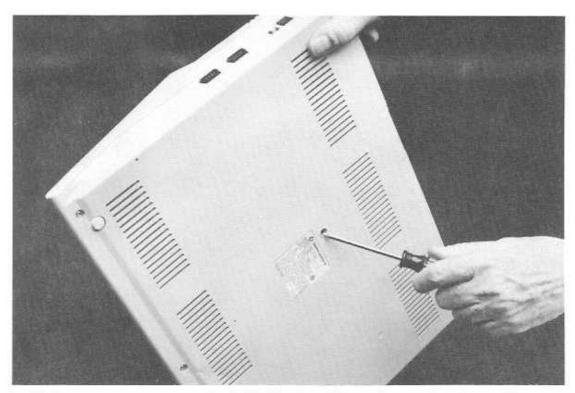

The C128 is put together as a sandwich. The top slice holds the keyboard, the bottom slice holds the printboard, and the components are connected to the printboard. The first thing to do is take the C128, turn it upside down and place it on the soft pad, keyboard on the bottom. Then check the screws. There are six of them. They are located as shown on Fig. 2-2.

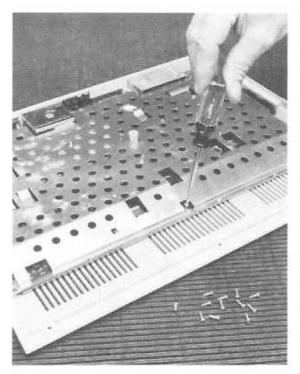

The six screws on my model are tiny little jeweler's types with a number 10 Torx hole instead of a screwdriver slot. You should have the correct form of driver to remove the screws. I purchased my number 10 Torx screwdriver at Sears for \$3.99 plus tax. With the correct screwdriver, the little ones

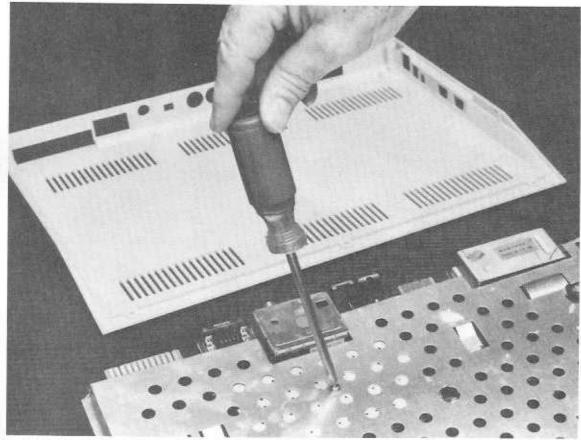

Fig. 2-1. To disassemble the C128, you need a number 10 Torx screwdriver, a Phillips head screwdriver, long nose pliers and a low-wattage soldering iron. For the reassembly, a tube of heat-transferring silicone paste should also be used. The logic probe, chip straightener-inserter and small cutters are also useful during troubleshooting.

come right out, as in Fig. 2-3. If you should not have the Torx driver, you'll have a hard time removing the screws.

Once the six screws are out, then place them all together in a safe place so that they will all be available for replacement. Grasp the C128 so that it doesn't open and turn it back so that the keyboard is on top once again, then try to pry the top away from the bottom.

The case is plastic and the top edge is seated in little holders. Sometimes the edges get wedged in the holders and it appears difficult to separate the

Fig. 2-2. On the bottom of the C128 are six Torx screws located at these spots.

top of the case from the bottom. Be persistent and keep prying, gingerly. The top will dislodge itself and separate after some prying.

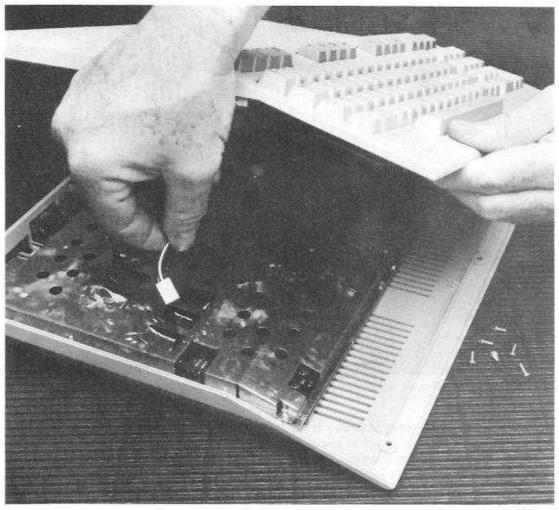

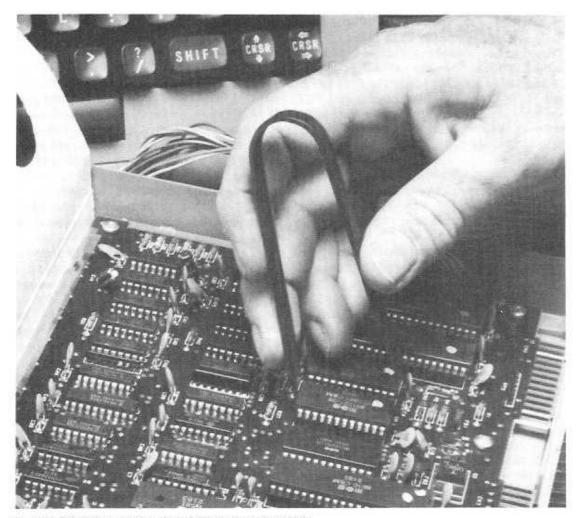

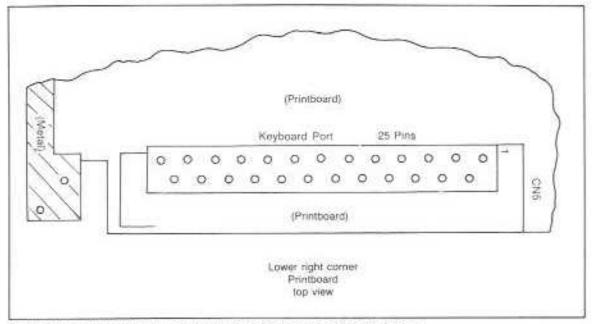

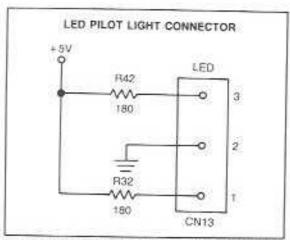

Once you separate the top and bottom, then lift the left side up first. The power indicator is on the left side. A three wire socket on the printboard holds the indicator three wire plug. Disconnect the plug, as in Fig. 2-4. Raise the top of the case and the top will swing up from left to right. The reason that the top will not come straight up is another number 10 Torx screw, seen in Fig. 2-5, on the lower right side of the printboard that is holding a ground strap connected to the keyboard. Then you will see that the keyboard is plugged into a 25-pin socket on the main board. Unplug the keyboard, as in Fig. 2-6, and the top of the case is free.

Unless the keyboard itself has troubles, there is no reason to remove it from the top casing. However, should you need to remove the keyboard from the top, it is easily taken off by removing six more number 10 Torx screws. The keyboard will then be free.

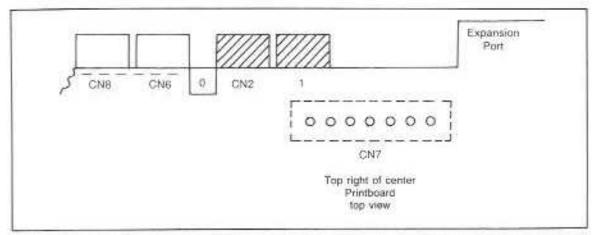

#### FREEING THE PRINTBOARD

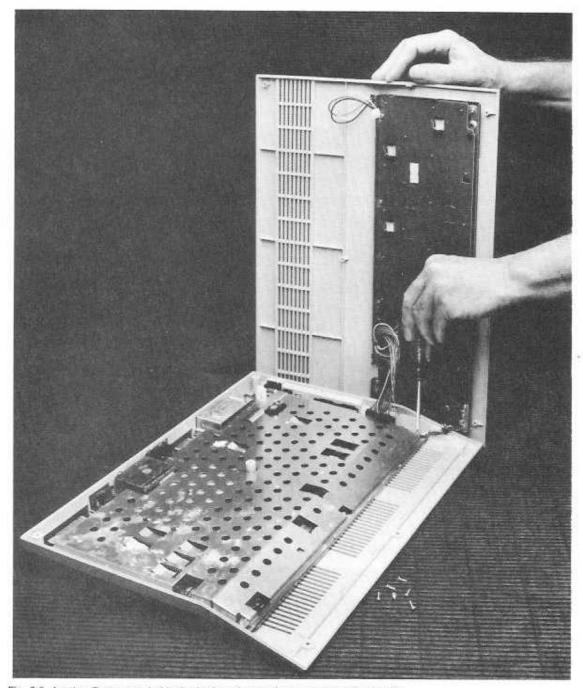

Once the top is off, you'll be looking down at a metal shield that covers the entire printboard, top and bottom. The shield is ventilated with a lot of holes, but it covers the entire board. In order to do any testing or parts replacing on the main board, this shield must come off.

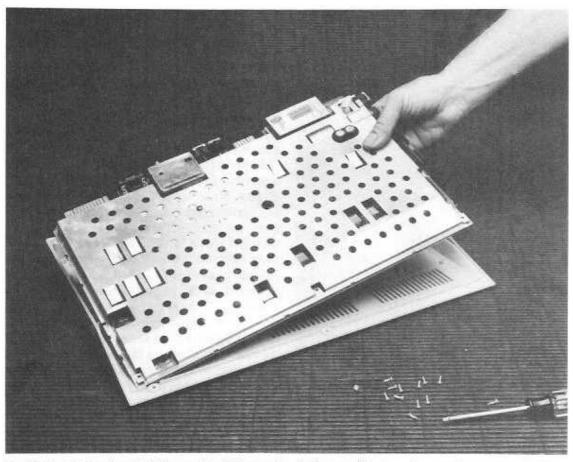

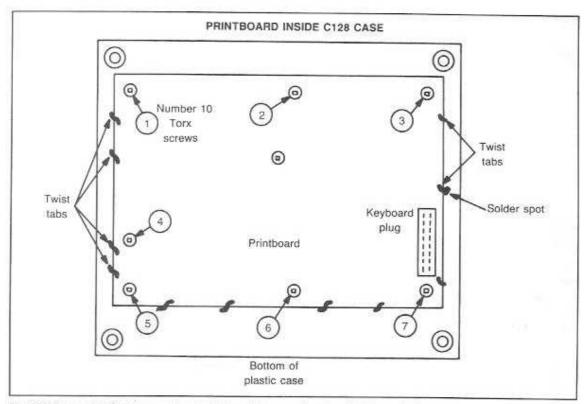

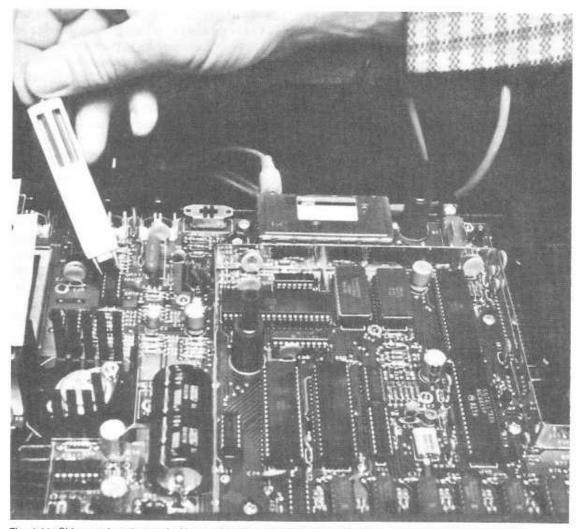

The first step is to remove the seven number 10 Torx screws, in Fig. 2-7, that are securing the printboard-shield assembly to the bottom of the cabinet. The printboard and shield assembly will then lift right out of the cabinet bottom, as Fig. 2-8 shows. The next step is to separate the printboard from the shield.

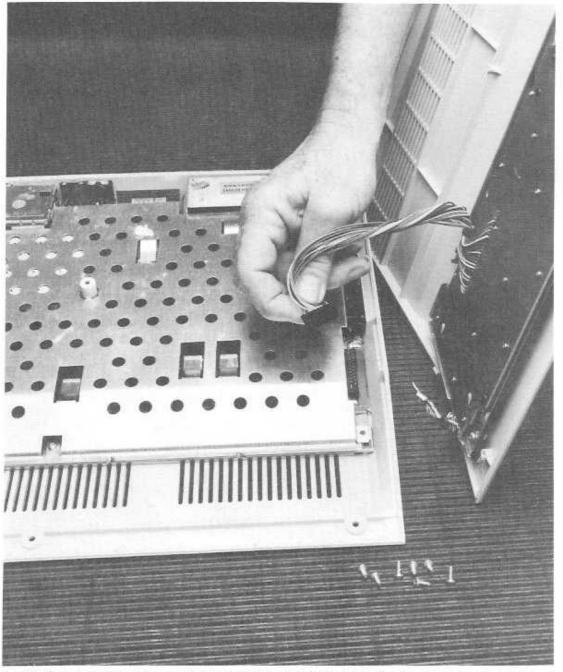

A close examination of Fig. 2-9 shows that the shield has eleven twist tabs hooking the top and bottom parts of the shield together. The tabs are located on the front and sides of the shield. These tabs must all be straightened. Once the tabs are no longer holding the top and bottom of the shield together, there is one last connection and one more screw. The connection is a solder spot next to a twist tab

Fig. 2-3. The six Torx screws are removed easily. Don't forget the hidden center screw above the nameplate.

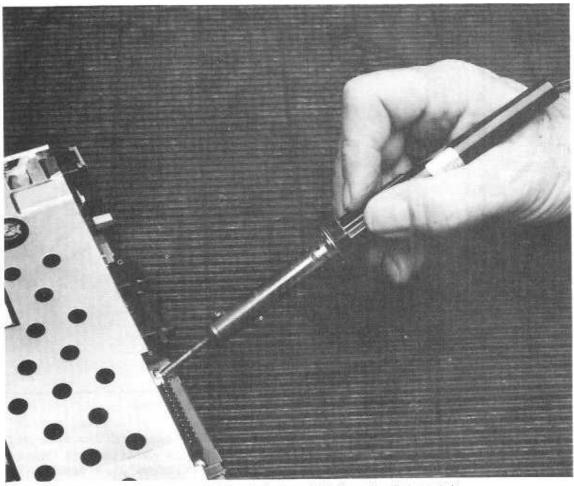

holding the shield to the printboard, as seen in Fig. 2-10. It is located on the right side of the board. After you desolder that connection, there is a Phillips head screw, shown in Fig. 2-11, located on the top of the shield right in front of the RF Modulator box. Once that screw is out, then the shield can be removed, top and bottom, as seen in Fig. 2-12.

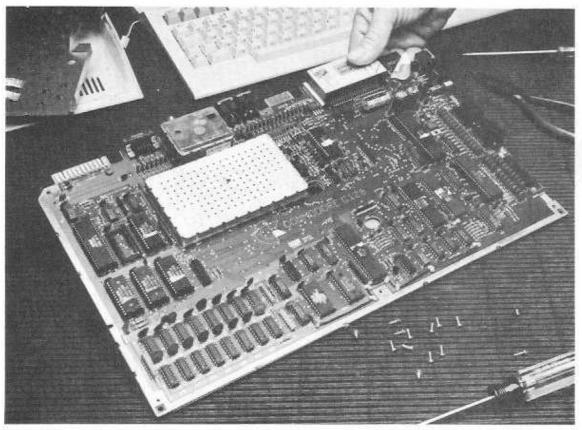

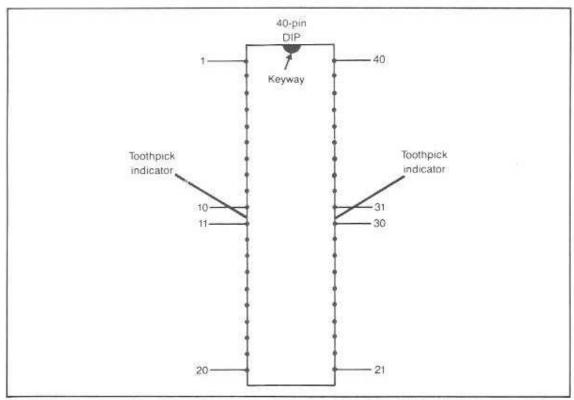

Once the shielding is removed, then the printboard is revealed. You'll see 55 of the C128's inventory of 63 chips on the board. Some are plugged into sockets while others are soldered directly to the board without the convenience of sockets. If you need to change a chip in a socket, it is a ticklish job to make sure the pins are lined up properly, but the job shouldn't take more than a minute or two. Should you be unfortunate enough to have to replace a chip soldered to the board, you have a tedious soldering job ahead fraught with the danger of "inducing" additional problems. Chapter 4 details the techniques required for replacing chips in sockets or soldered to the board.

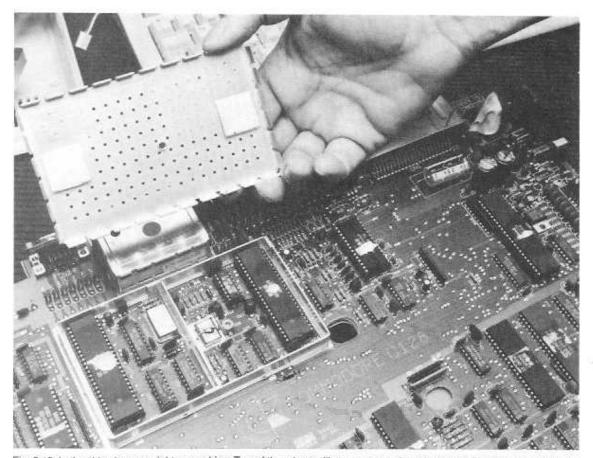

In the top left quadrant is the RF Modulator box and the metal shield box containing video associated chips. The top of the video box comes off, as shown in Fig. 2-13, and you'll see eight more chips. You'll find six small chips, U22 (the video controller) on the left and U21 (the VIC) on the right.

When you remove the shielding, note that there is a heatsink that is designed to touch the shield on the VIC. The sink is covered with a white silicon paste to conduct the heat away from VIC. Should you disturb this heat connection be sure to apply fresh silicon paste. You can obtain it in any electronic store, such as Radio Shack.

It is vital that, as you take apart the C128, you perform the disassembly in a slow and careful manner. Note the way it comes apart so you will be able to get it back together again without undue difficulty.

Fig. 2-4. Once the screws are out the top will dislodge itself. Lift the left side and disconnect the LED pilot light plug.

## THE POWER SUPPLY BOX

Power supply troubles are among the most common in computers. If the computer is dead, then the first step is to check out the supply box. Chapter 24 goes into detail on the techniques required. If you find that the box is, indeed, the source of the trouble, then the next step is to try and disassemble the box. Sometimes this is an easy task and at other times is almost impossible. This is because there is no one box that is found with all C128's. They all produce the same supply voltages for the C128, but with slightly different circuits and very different casings.

The last two boxes I encountered had two different casings. One was very heavy, which meant that it was probably potted (a heavy waxlike plastic was poured into the box to seal the circuits in place).

Fig. 2-5. Another Torx screw holds the keyboard ground strap to the main chassis.

Fig. 2-6. The keyboard plugs into the main chassis with this 25-pin plug. It pulls off easily. When reinserting make sure the plug is seated snugly.

Fig. 2-7. Seven more Torx screws secure the printboardshield assembly to the bottom of the case.

In spite of the fact that it was potted, I attempted to pull it apart because the trouble was definitely in the box. There was one long bolt. I removed it and tried to pry the top from the bottom of the case. They were so stuck together that the only way they would come apart was if I broke them apart. I opted to simply replace the power supply with a new one. It was the economical thing to do.

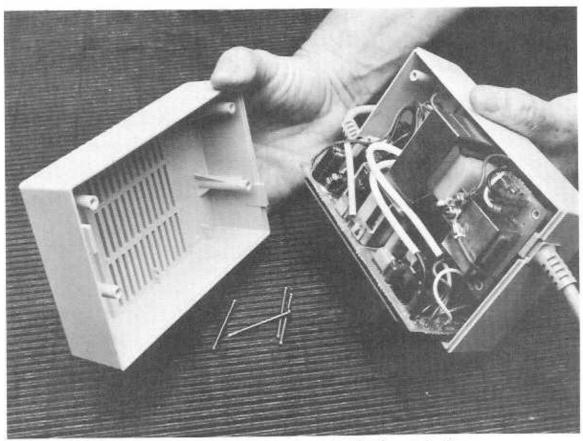

On the other hand, another box I worked on was easy. It was much lighter than the first one. The box was not potted. It had four long bolts as shown in Fig. 2-14. Once they were removed with a thin Phillips head screwdriver, then the top lifted right off.

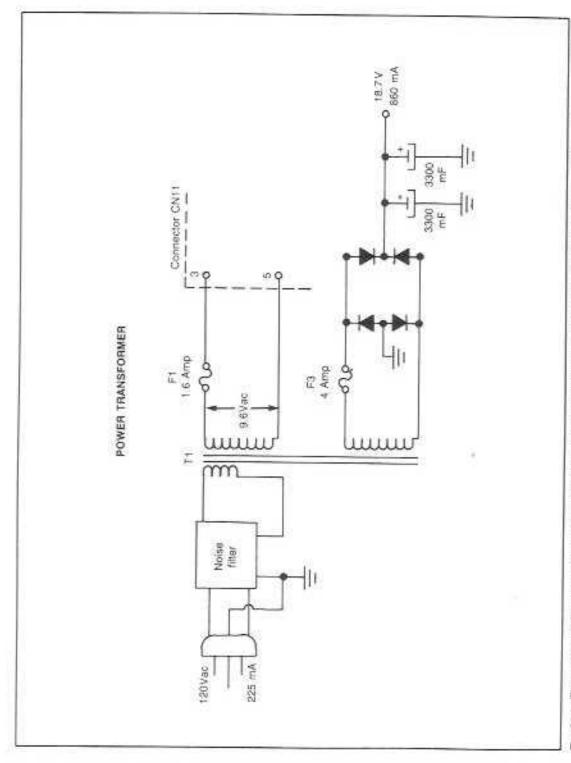

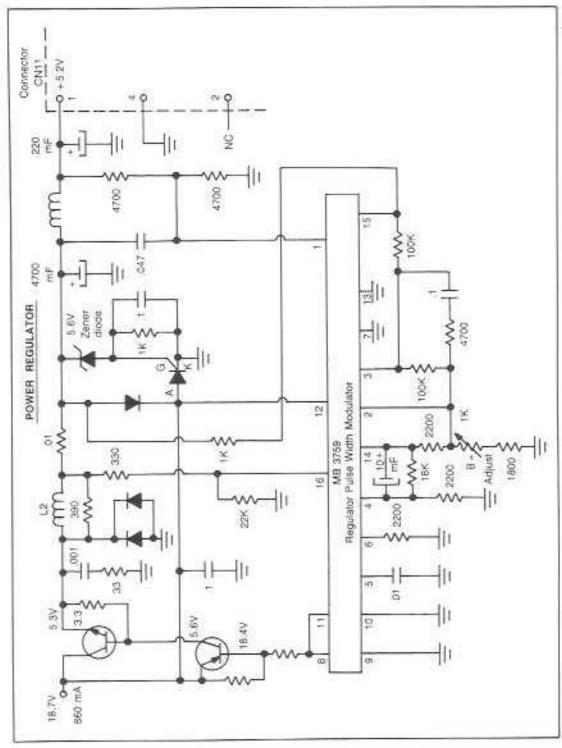

Inside the box is a small printboard and some other circuits, as shown in Fig. 2-15. There are also two small fuses in fuse clips. Replacing a bad fuse might be a quick repair. In addition a power transformer, some diodes, filter capacitors, transistors and one integrated chip are in the box. Chapter 24

details the circuit and the troubleshooting methods needed to fix troubles.

### VISUAL REPAIRS

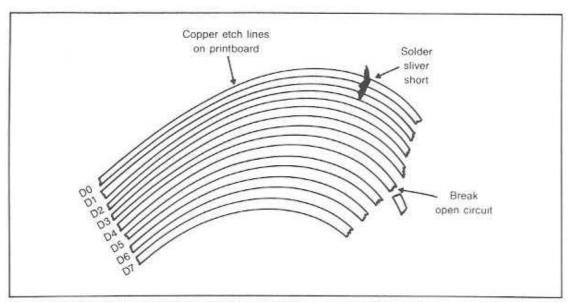

After you disassemble the C128, then you are afforded an excellent easy kind of repair that can produce a repair in a small percentage of cases: some troubles can be seen and promptly remedied. One such kind of trouble is accidentally installed in the computer during manufacturing. After the printboard is assembled, then it is soldered with automatic machinery. During the soldering process, the machinery generates hot gases that can expand rapidly and shoot hot liquid solder into the air. As the solder cools and falls, it hardens. The solder then drizzles down and some of it could find its way onto a newly assembled printboard. The drizzle contains solder flux which can act as glue. Where the solder falls it sticks.

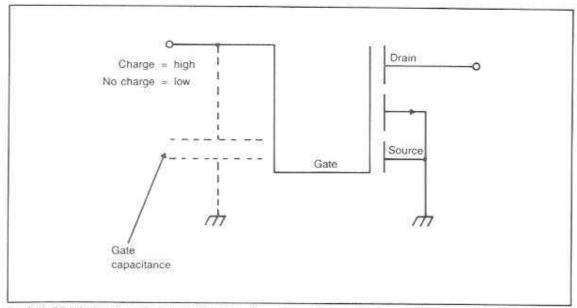

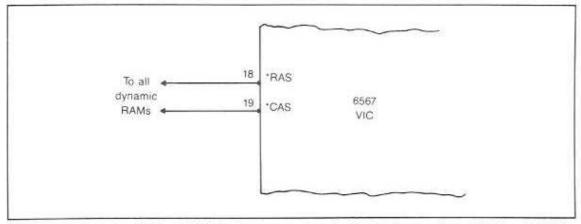

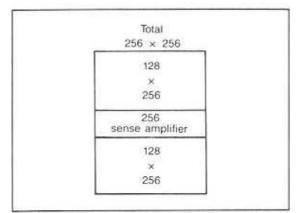

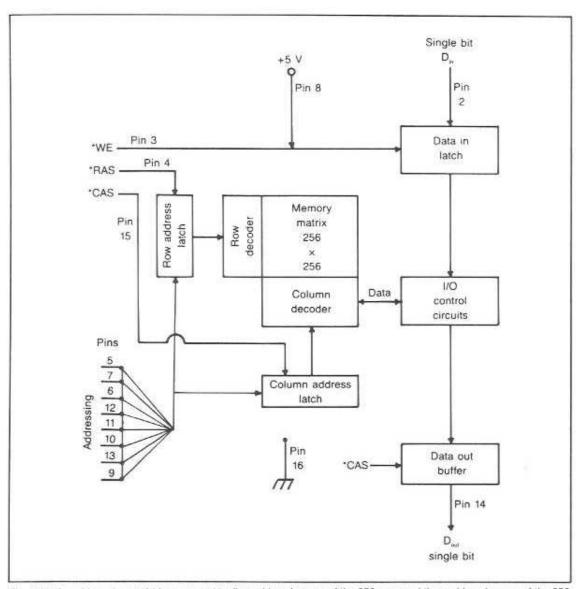

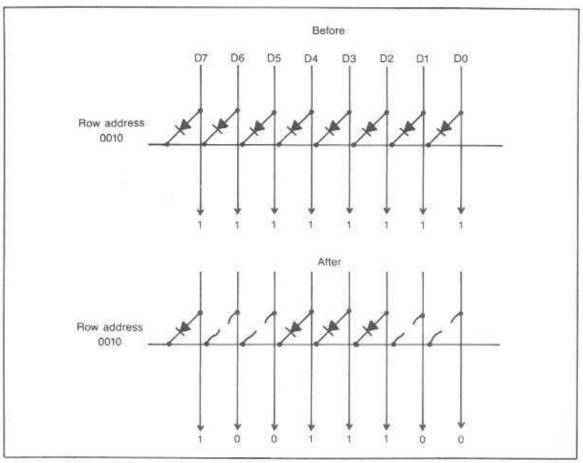

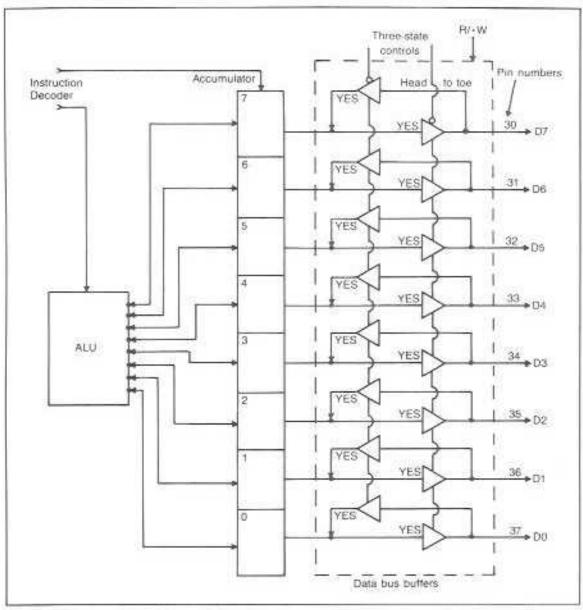

Of course, the factory knows all about this, and the board goes through extensive cleaning in the final stages. However, as hard as they try, an occasional sliver of solder will stick in a place where it frustrates removal, as shown in Fig. 2-16. Also, it does not cause any problems at that time, so it sneaks through quality control, and is shipped out with the finished computer.