THE INS AND OUTS OF THE M

# M 3FM 3866

**ON THOMASSON**

#### THE INS AND OUTS OF THE

### TIMEX TS 1000 & ZX 81

**DON THOMASSON**

**MELBOURNE HOUSE**

Published in the United Kingdom by: Melbourne House (Publishers) Ltd., Glebe Cottage, Glebe House, Station Road, Cheddington, Leighton Buzzard, Bedforshire, LU7 7NA, ISBN 0 86161 118 7

Published in Australia by:

Melbourne House (Australia) Pty. Ltd.,

Suite 4, 75 Palmerston Crescent,

South Melbourne, Victoria, 3205,

National Library of Australia Card Number and

ISBN 0 86759 119 6

Published in the United States of America by: Melbourne House Software Inc., 347 Reedwood Drive, Nashville NT 37217.

Copyright (c) 1983 by Don Thomasson.

The circuit diagram on pages 8 and 9 and other proprietery content of the circuits the TS1000 and ZX81 are copyright property of Sinclair Research Ltd.

All rights reserved. This book is copyright. No part of this book may be copied or stored by any means whatsoever whether mechanical or electronic, except for private or study use as defined in the Copyright Act. All enquiries should be addressed to the publishers.

Printed in Hong Kong by Colorcraft Ltd.

#### **Contents**

| Introduction                       | p11  |

|------------------------------------|------|

| Internals                          | p13  |

| The External Interface             | p43  |

| Externals                          | p50  |

| Appendix A — Basic Programs        | p95  |

| Appendix B — Machine Code Programs | p100 |

|  | • |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

#### **Illustrations**

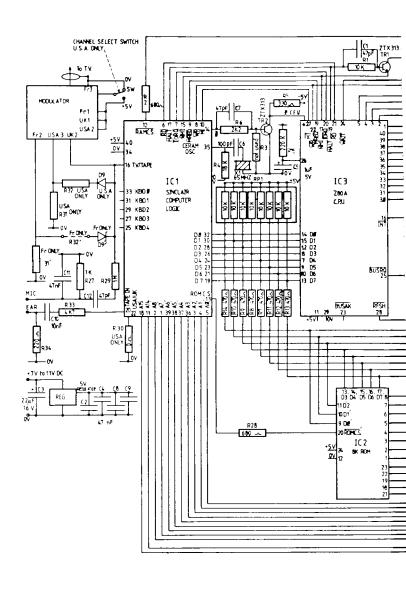

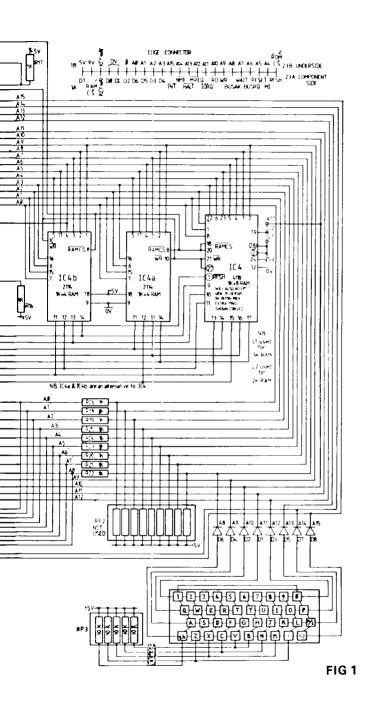

| Fig. 1  | Circuit Diagram              | p8,9        |

|---------|------------------------------|-------------|

| Fig. 2  | Memory Map                   | p21         |

| Fig. 3  | RAM Layout                   | p25         |

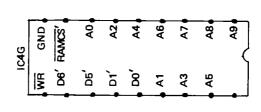

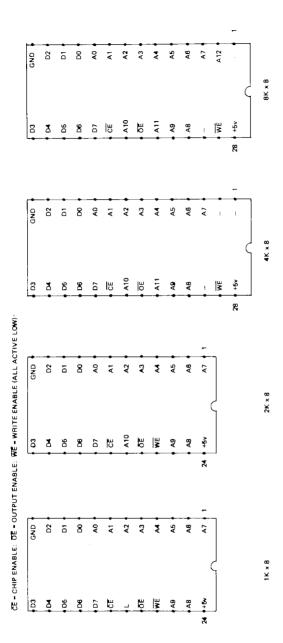

| Fig. 4  | RAM Pinouts                  | p27         |

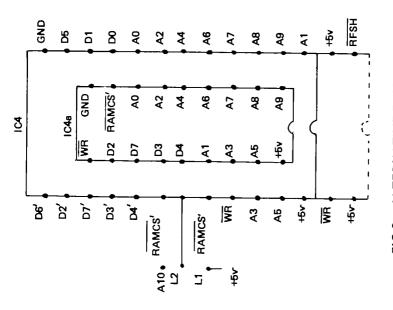

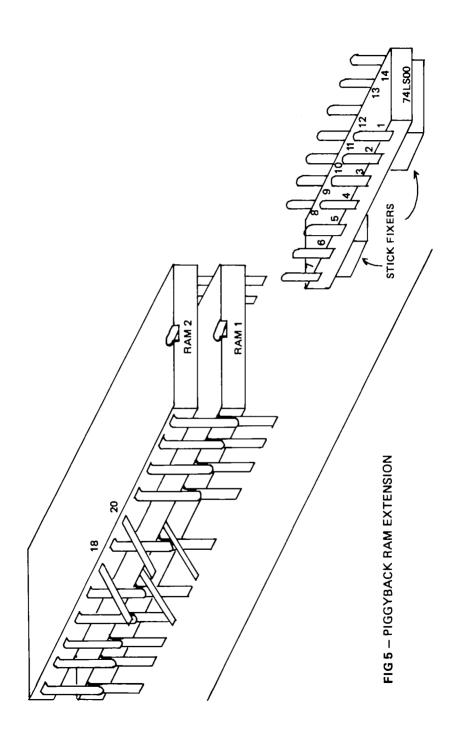

| Fig. 5  | Piggyback RAM                | p28         |

| Fig. 6  | Piggyback RAM connections    | p 29        |

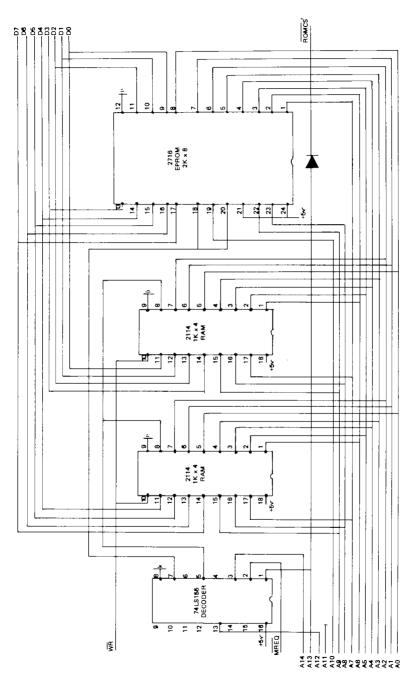

| Fig. 7  | ROM/RAM Addition             | p31         |

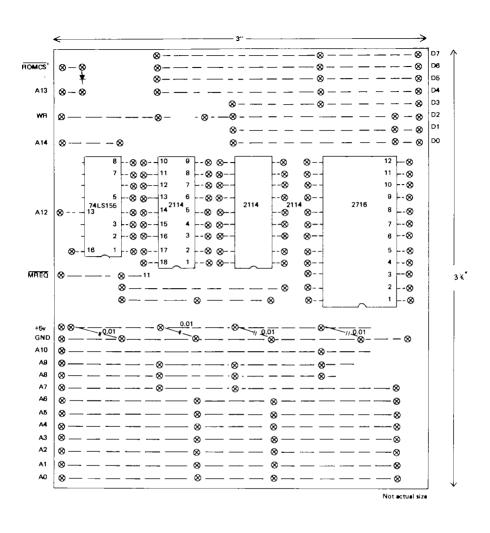

| Fig. 8  | ROM/RAM Memory Map           | p32         |

| Fig. 9  | ROM/RAM Layout               | p33         |

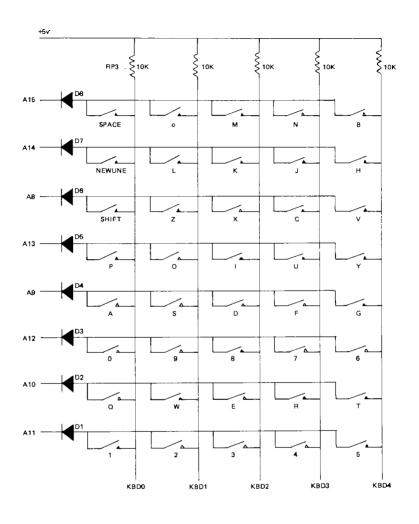

| Fig. 10 | Keyboard Circuit             | p38         |

| Fig. 11 | Keyboard Connections         | p39         |

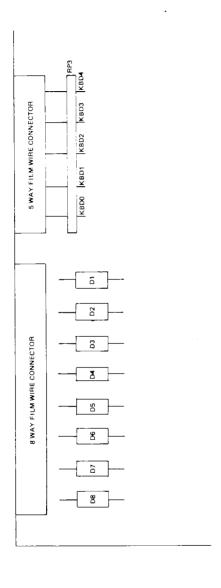

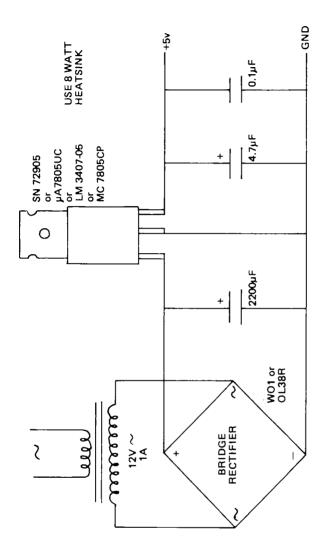

| Fig. 12 | Power Supply                 | p51         |

| Fig. 13 | Nested Connection System     | p52         |

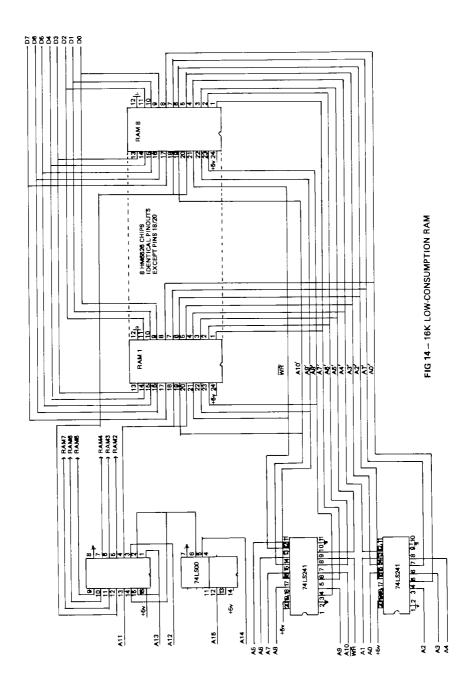

| Fig. 14 | 16K RAM                      | p <b>54</b> |

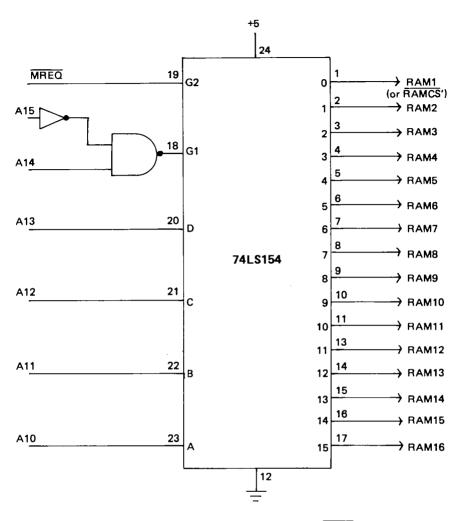

| Fig. 15 | Sixteen-way Decoder          | p55         |

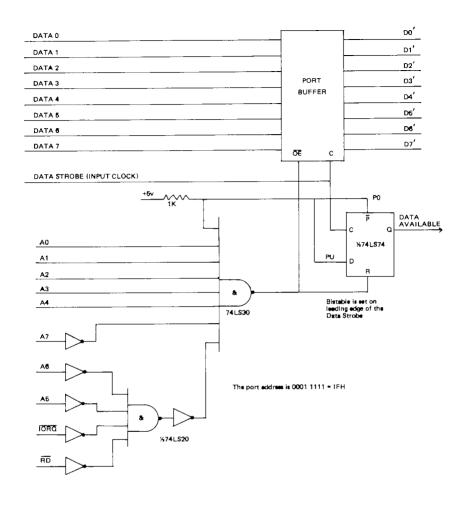

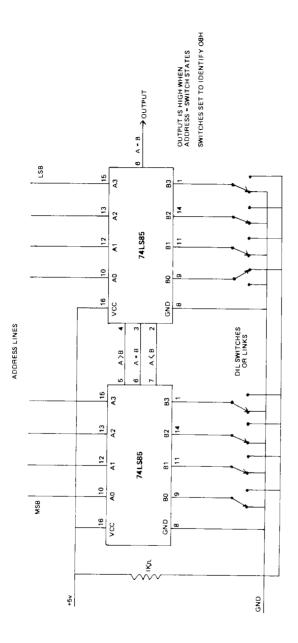

| Fig. 16 | Input Port                   | p <b>59</b> |

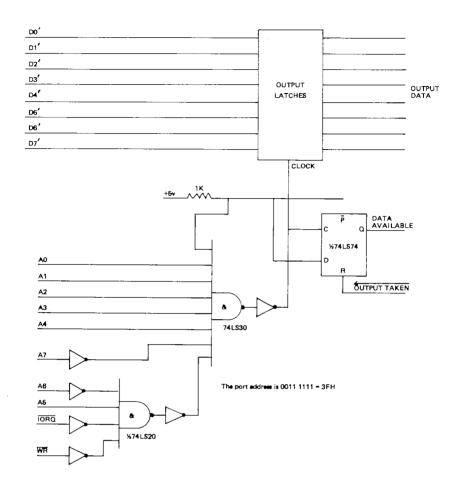

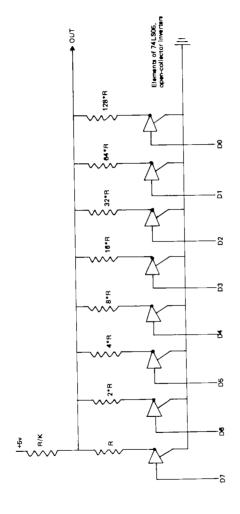

| Fig. 17 | Output Port                  | p61         |

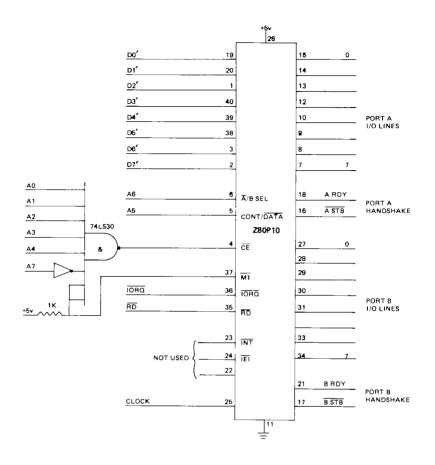

| Fig. 18 | Z80 PIO                      | p65         |

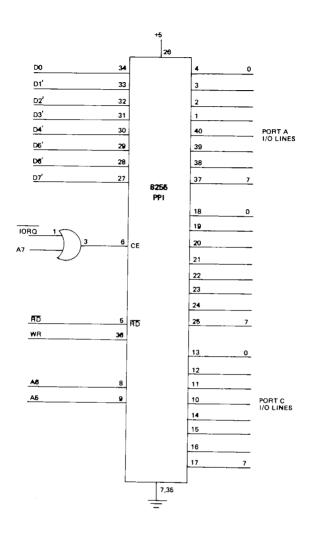

| Fig. 19 | 8255 PPI                     | p67         |

| Fig. 20 | Printer Driver Scheme        | p 69        |

| Fig. 21 | DA Converter                 | p74         |

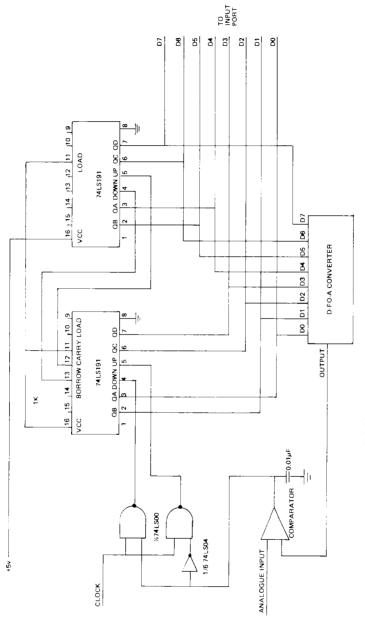

| Fig. 22 | AD Converter                 | p77         |

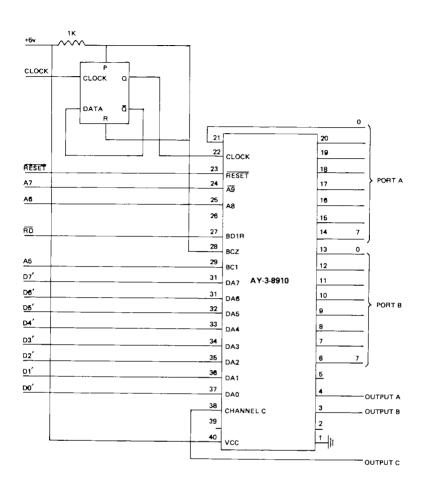

| Fig. 23 | Programmable Sound Generator | p79         |

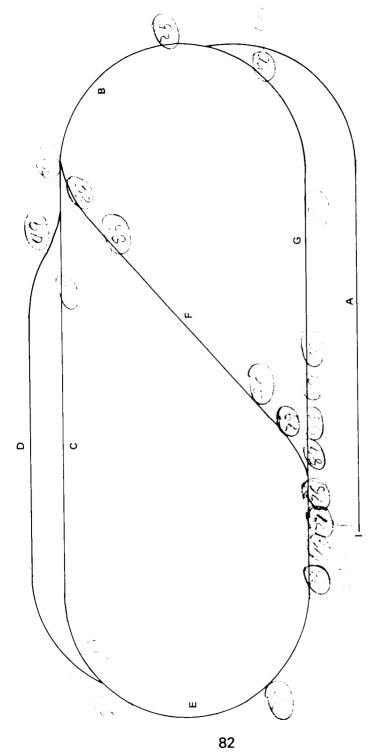

| Fig. 24 | Model Railroad               | p82         |

#### **Tables**

#### INTRODUCTION

A computer, even one as small and inexpensive as the TS1000 or the ZX81, can provide seemingly endless interest. There is so much to be discovered, so much pleasure in the realisation that writing programs is not impossibly difficult, so much satisfaction in the tracking down of elusive 'bugs'.

In time, however, even this brave new world may fade a little, the shine of novelty wearing away, and that is the signal to explore further, to find out what is inside the box, to connect external bits and pieces, to make the computer do something new. This book is your guide in that exploration, your map of safe paths, your warning of dangers.

The first warning is perhaps the most important. Computer components are not partial to being handled too casually. Some electrical work, such as the addition of extra accessories to a car, is unlikely to land anyone in serious trouble. The battery may go flat, or some wires may overheat, but unless the car itself catches fire the damage can usually be mended fairly easily. Putting a damaged computer right can be a lot more difficult.

The most common source of trouble is due to hamfisted use of the soldering iron, which can overheat components or wreck printed circuit boards. Those who doubt their skill in this direction should practice on something less vulnerable before they tackle changes to the ZX81. If the soldering iron is removed as soon as it has done its work, there should be no difficulty. The trick lies in judging when the work is done.

Another cause of damage is static electricity. Most computer components are designed to work at relatively low voltages, and the charges that make your clothes crackle when you take them off in dry weather would be more than enough to punch holes in the insulation of many chips. Walking across a nylon carpet can charge you to similar levels. It does you no harm, because the power involved is minute, but it can make you fatal to any integrated circuit which you touch.

It is therefore wise to guard against static build up, by simple precautions that should become a habit. If you always touch an earth point on a component or circuit before you touch anything else, the voltage levels will be equalised, removing the danger. Those who handle computer systems professionally may be required to observe rather more stringent rules, but equalisation of voltage levels remains the key point.

Remember that the soldering iron is connected to earth, so before you use it you should earth both yourself and the equipment.

You should also switch power off before making any changes to the system. Clearance between pins and circuit tracks is so small that accidental shorts are only too easy to create. Before restoring power, make a careful check for stray whiskers of wire and splashes of solder, which can cause expensive damage, and are likely to produce obscure faults that are difficult to trace.

You should not allow yourself to be too discouraged by these warnings. Keeping to the rules should see you through.

You may be aware that the TS1000 and ZX81 computers are essentially the same machine: The ZX81 was developed by Sinclair Research in 1981 in the UK and is still marketed by Sinclair in the UK and distributed by them through much of the world. The TS1000 is manufactured by the Timex Corporation under licence from Sinclair Research, and the major difference is that TS1000s come with 2K of RAM, while the ZX81s come with 1K. In this book, any information about the ZX81 also refers to the TS1000, unless specifically noted. For ease of reading, the two computers are simply referred to as the ZX81.

The book is divided into three parts: The first examines the inside of the ZX81, the second deals with the external interface, and the third describes some systems which can be added to the basic ZX81 via that interface. The division is not rigid, because most of the changes that can be made affect more than one area, but in broad terms each section prepares the ground for what comes next.

#### **INTERNALS**

Before looking inside the ZX81, let us consider what we expect to find. There will be a microprocessor, some RAM (Random Access Memory) for it to talk to, and some fixed data in ROM (Read Only Memory) to tell the processor what to do. There must be some provision for communication with the outside world, or we would never find out what was happening inside the system.

That description of a minimum computer system also constitutes a fair definition of the ZX81, but two factors give the machine a unique personality, the programs which are held in the ROM and the highly specialised ULA (Uncommitted Logic Array) which the manual calls the 'dogsbody'. The program and the ULA complement each other, and changing either would be both difficult and expensive, which places a limit on the alterations which can be made to the system as a whole. Within that limit, however, quite a lot can be done.

The key feature of the ZX81 is its apparent ability to maintain a video display with minimal resources. The task is demanding. Line synchronising pulses must be generated every 64 uS, with a modification of their pattern to produce frame synchronising pulses. During 40 uS periods between line sync pulses a string of up to 256 data bits must be output to form the display, at a rate of 61/2 bits per microsecond. Some computers need 30 integrated circuits to achieve this.

In SLOW mode, the ZX81 appears to handle the display output tasks while it is busy executing a program, but that is an illusion. The program runs for only about a quarter of the time, during the periods when the display scan is not demanding detailed output data. While the pattern data is being output, the whole system is occupied with that task, and normal processing is suspended.

In FAST mode, the display is abandoned to its own devices, so processing can be continuous, and therefore four times as fast.

To refresh the display, it is necessary to read codes from the display file in RAM, use them to form pointers to character pattern data in ROM, then transmit the pattern bits serially as video output. All parts of the system are involved, because the processor supplies the base address used in accessing the pattern data. The 'dogsbody' chip controls the whole operation.

Quite apart from this, the ULA chip has other duties:

- Generation of a 6.5 MHz clock, using a ceramic filter as a frequency standard.

- Derivation of a 3.25 MHz clock for the processor.

- Driving the tape recorder in SAVE

- Responding to tape output in LOAD

- Sensing keyboard action

- Deciding when ROM and RAM should be active, on the basis of the address provided by the processor.

- Controlling general system timing.

It is scarcely surprising that some of these tasks come into conflict with each other, imposing system limitations. The display cannot be maintained during SAVE and LOAD, which must act continuously to maintain the correct baud rate for the data passing to and from the tape. In any case, the same pin on the ULA provides both the video signal and the output to the tape recorder, hence the odd patterns on the screen when tape is in use.

Another point is that software-controlled timing of inputs or outputs cannot be completely precise. The stop-go processing must introduce some degree of jitter. For longer intervals, the PAUSE command provides a solution, but such tasks as output waveform generation must be performed in FAST mode.

The other principal factor limiting the system performance is the ROM-borne program. This is entirely conditioned by the assumption that BASIC will normally be used, and in that role it performs very well, but the use of machine code is not as simple as might be wished. It can be run, but only via BASIC.

A rather important deficiency is the lack of IN and OUT instructions in the BASIC repertoire, which means that they have to be implemented in machine code if external devices are to be brought into play.

However, most of the limitations mentioned can be overcome by a little ingenuity, once their nature and origin are understood.

#### **Getting Inside**

Opening up the ZX81 is no problem once you know that three screws are hidden under the stick-on rubber feet. Remove these and the two visible screws, and the underside of the case, which is really the cover, will come away, revealing the underside of the circuit board, which is held in place by two more screws. As the screws are of different sizes, it is useful to make a note of their positions.

When the last screws have been removed, the circuit board can be turned over, but it will still be attached to the case by the keyboard connections, so handle it carefully. Touch the case of the video modulator first, to equalise voltages and avoid static damage. The modulator is easy to identify by its metal case and the connector marked 'TV'.

The circuit board carries four — sometimes five — integrated circuits, the modulator, and a number of smaller components. The metal case is a heat sink to help cool the voltage regulator, to which it is bolted. If that is on your right, furthest away from you, the 'dogsbody' chip is in front of it, next to the modulator, then comes the ROM chip, and then the processor. On the left is the RAM, which may be implemented as one 24-pin chip or two 18-pin chips, the board layout allowing for either configuration. The ZX81 has 1K of RAM, the TS1000 has 2K.

Of the smaller components, the keyboard connector is obvious because the keyboard film wire goes to it, the clock

circuits are on the near side of the board, close to the 'dogsbody' chip, together with some odd circuit elements, the area near the three jack sockets contains filter circuits for the tape input and output and for some video output standards, and most of the remaining components are resistors, diodes, or decoupling capacitors. If the details of the assembly fail to match the picture in the manual, there is no need to worry, as the layout permits a number of variations.

One variation is the omission of sockets for the RAM, which is a pity, as it makes modification in this area more difficult.

The printed circuit can be separated from the keyboard by pulling the film wires out of their sockets, and this makes handling easier, but it should be done sparingly, as the wires are easily damaged.

The internal circuits consume about 300 mA, and the external power unit is capable of delivering up to 700 mA, but a second limit on available current is set by the internal regulator, which gets rather hot under the collar if it is asked to do too much. It can be loaded by about another 50-100 mA, but if more power is required it should be obtained from a separate regulator driven from the +9v supply rail. The outputs of the two regulators should not be joined together, as has been done in some proposals, as one will then tend to take all the load.

#### The Circuit

The circuit diagram (Fig. 1) is not too easy to follow, so it has been supported by a signal list showing the main interconnections. (Table 1).

The system is broadly what one would expect, but there are a few surprises. For example, address lines A0-A8 go directly from the processor to the RAM, but are connected to the ULA and ROM by series resistors, allowing the ULA to control the ROM address directly when picking up pattern data, as will be explained when the display system is examined. Similarly, the data lines go directly from the processor to the ULA, but are passed to the ROM, the RAM and the outside world

## ZX81 SIGNAL LIST (1)

| Notes                               | R18-R26: 1K. See A0'-A8'  KD6 KD = Keyboard diode.  Link L2 connects A10 to pin 19 of a 24-pin RAM, pin 21 of a 28-pin RAM.  Link L1 replaces A10 by +5v | Secondary Address Lines,<br>linked to the main lines<br>by resistors |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Other                               | R26<br>R18<br>R24<br>R24<br>R23<br>R20<br>R22,<br>R22,<br>RD4<br>KD3<br>KD3<br>KD3<br>KD5                                                                | R26<br>R18<br>R19                                                    |

| External Other                      | 78<br>88<br>88<br>98<br>108<br>228<br>218<br>208/11A<br>198<br>178<br>168<br>158<br>148<br>138                                                           | 111                                                                  |

| D Z                                 |                                                                                                                                                          | <b>υ4</b> κ                                                          |

| IC2<br>ROM                          | 1                                                                                                                                                        | 8 7 9                                                                |

| IC4<br>28-pin<br>RAM                | 10<br>3<br>3<br>3<br>4<br>4<br>7<br>7<br>7<br>7<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                    |                                                                      |

| IC4 IC4<br>24-pin 28-pin<br>RAM RAM | 8 1 22 22 23 5 5 5 6 6 6 6 6 7 6 6 6 6 7 6 6 6 7 6 6 6 7 6 6 6 7 6 6 6 6 7 6 6 6 6 7 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6                             |                                                                      |

| IC4b<br>RAM                         | 7 5 9 1 9 1 5 1 5 1 5 1 5 1 5 1 5 1 5 1 5                                                                                                                |                                                                      |

| IC4a<br>RAM                         | 7 10 0 10 10 10 10 10 10 10 10 10 10 10 1                                                                                                                | 111                                                                  |

| CPU<br>CPU                          | 30<br>31<br>32<br>33<br>36/16<br>37<br>40<br>40<br>40<br>5                                                                                               | 111                                                                  |

| SIGNAL NAME                         | Address Lines A0 A1 A2 A3 A4 A5 A6/INT A7 A8 A9 A10 A11 A11 A11 A15                                                                                      | <b>ZX81 Signal List (2)</b><br>A0'<br>A1'<br>A2'                     |

|                                 | R7-14: 470 ohms<br>RP1: 10K to +5v                                                                                     | Secondary Data Lines,<br>linked to the main data<br>lines by resistors.                            | Emitter of TR1<br>Base of TR1 via R1/C1. |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------|

| R25<br>R24<br>R23<br>R20<br>R21 | R14,RP1<br>R10,RP1<br>R9,RP1<br>R8,RP1<br>R7,RP1<br>R11,RP1<br>R12,RP1                                                 | R14<br>R10<br>R8<br>R7<br>R11<br>R13                                                               | Emitter of TR1<br>Base of TR1 vi         |

|                                 |                                                                                                                        | 4 4 8 9 8 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                            | 12A<br>13A                               |

| 36<br>37<br>38<br>39<br>1       | 32<br>30<br>28<br>24<br>23<br>21                                                                                       | 1111111                                                                                            | 15                                       |

| 23 - 23 - 23                    |                                                                                                                        | 9<br>11<br>11<br>11<br>11<br>11<br>11                                                              | 1 1                                      |

|                                 | 1111111                                                                                                                | 12<br>13<br>13<br>13<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15 | 1 1                                      |

|                                 | 1111111                                                                                                                | 9<br>14<br>17<br>11<br>13                                                                          | 1.1                                      |

|                                 |                                                                                                                        | 4611151                                                                                            | 11                                       |

| 11111                           |                                                                                                                        | 11124112                                                                                           | 1.1                                      |

|                                 | 41<br>21<br>8<br>7<br>6<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | f (3)                                                                                              | 17                                       |

| A3,<br>A5,<br>A6,<br>A8,<br>A8, | Data Lines  D0  D1  D2  D3  D4  D6  D7                                                                                 | ZX81 Signal List (3) DO' D1' D2' D3' D4' D5' D6' D6'                                               | Other Lines<br>NMI<br>HALT               |

|                                                    |                      | 1        | 1    | Collector of TR2, R5 to +5v | Numerous points. | Numerous points. | R2 R2:680 ohms | R2     | R28 R28:680 ohms | R28    | RP3 (10K to +5v). Keyboard | RP3. Keyboard | RP3. Keyboard | RP3. Keyboard | RP4. Keyboard | Linked to Ground for USA standard | Base of TR2 via R6/C7 | Modulator. MIC. (via filters) | EAR via filter. | R4 to Ground. Ceramic filter via C6 | C3 to Ground. Regulator. PSU. |

|----------------------------------------------------|----------------------|----------|------|-----------------------------|------------------|------------------|----------------|--------|------------------|--------|----------------------------|---------------|---------------|---------------|---------------|-----------------------------------|-----------------------|-------------------------------|-----------------|-------------------------------------|-------------------------------|

| 144<br>154<br>174<br>194<br>204<br>214             |                      | 22A      | 23A  | <b>6B</b>                   | 18               | <b>4B/5B</b>     | 1              | 8      | 1                | 23B    | 1                          | ļ             | 1             | ١             | 1             | 1                                 | ١                     | I                             | I               | İ                                   | <b>2B</b>                     |

| e r 8 8                                            |                      | 5        |      | 1                           | <del>8</del>     | æ                | 12             | l      | 13               | 1      | 8                          | 31            | නු            | 27            | 22            | 22                                | 4                     | 16                            | 20              | 32                                  | ١                             |

|                                                    |                      | I        | j    | 1                           | 24               | 12               | ١              | ł      | 1                | 70     | ļ                          | 1             |               | 1             | I             |                                   | I                     | I                             | I               |                                     |                               |

| 23/27                                              |                      | 1        | -    | I                           | 2/26/28          | 14               | 1              | 20/22  | l                | l      | l                          | l             | 1             | 1             |               | I                                 | I                     | 1                             | 1               |                                     | 1                             |

| 1   1   2                                          |                      | i        | ł    |                             | 24               |                  |                | 18/20  | 1                | ļ      | 1                          | I             | ı             | ١             | I             | I                                 | I                     | I                             | I               | I                                   | 1                             |

| 2                                                  |                      | 1        | I    | 1                           | 8                | თ                | I              | ∞      | I                | 1      | 1                          | ١             | I             | I             | I             | I                                 | •                     | I                             | 1               | I                                   | ı                             |

| 2                                                  |                      | 1        |      | ١                           | 18               | တ                | 1              | œ      | 1                | 1      |                            | ļ             | 1             | 1             | l             | 1                                 | I                     | 1                             | ١               | 1                                   | I                             |

| 19<br>22<br>23<br>23<br>24<br>25<br>26             | ₹                    | 27       | 78   | 9                           | 1                | 53               | 1              | ١      | ١                |        | ١                          | ١             | ļ             | I             | 1             | 1                                 | 1                     |                               |                 | 1                                   | 1                             |

| MREQ<br>IORO<br>ND<br>WR<br>BUSAK<br>WAIT<br>RESET | ZX81 Signal List (4) | <u>Σ</u> | RFSH | Ю                           | +5^              | Ground           | RAMCS          | RAMCS' | ROMCS            | ROMCS' | KBD0                       | KBD1          | KBD2          | KBD3          | KBD4          | USA/UK                            | CLOCKOUT              | TV/TAPE                       | TAPEIN          | CERAMOSC                            | <b>^6</b> +                   |

through series resistors.

The clock oscillator consists of a 6.5 MHz ceramic filter working in conjunction with circuits in the ULA. This generates the 'dot frequency' for the display, and the ULA must also divide the clock down to 3.25 MHz to serve the needs of the processor. The lower frequency appears on pin 14 of the ULA, and is amplified by TR2.

The other transistor, TR1, is used in a rather odd circuit. The transistor base goes to HALT, and the emitter goes to NMI, so collective current will only be drawn if HALT is false (at a positive voltage) and NMI is true (at near-zero volts). When current is drawn, WAIT is pulled down, becoming true. This puts the processor into a wait condition when NMI is true and HALT is not, another specialised function used by the display system.

Oddest of all, however, is the connection of the INT line to address line A6. This generates an interrupt when the current address is of the form XX0X, XX1X, XX2X, XX3X, XX8X, XX9X, XXAX, or XXBX, another element in the Machiavellian complexities of the display system. Unfortunately, this debars the use of interrupt by add-on circuits, a severe limitation.

The video output system caters for three national standards, those of France, Britain and America. In view of the origin of the equipment, it is not surprising that the British standard is the simplest, pin 16 of the ULA being connected directly to the modulator. For the French standard, a diode and two resistors are added, while the American version involves a different diode and resistors, a channel select switch on the corner of the board next to the regulator, and a connection earthing pin 22 of the ULA. The purpose of this link is discussed in the section covering the keyboard.

Very little change is permissible in the parts of the circuit which have been described. The system is too closely integrated to permit change without disruption. The areas yet to be examined, the RAM, the Keyboard, and associated parts of the system, allow more scope for ingenuity.

| A15 | A14 | A13 | A12      | A11      | A10 | Standard Memory Map                               |

|-----|-----|-----|----------|----------|-----|---------------------------------------------------|

|     |     |     |          | 1        | 1   |                                                   |

|     |     |     | 1        | 0        | 1   |                                                   |

|     | i   | 1   | ļ        | 1        | 9   |                                                   |

|     |     |     | 0        | -        | 01  |                                                   |

|     | 1   |     |          | 0        | 0   |                                                   |

|     | ļ , |     | 1        | 1        | 1 0 |                                                   |

|     |     |     | '        | 0        | 1   |                                                   |

|     |     | 0   |          | 1        | 1 0 | 8000-FFFF                                         |

|     |     |     | 0        | 0        | 1   | Copy of lower                                     |

| 1   |     |     | -        | 1        | 0   | helf of store                                     |

|     |     |     | 1        |          | 0   |                                                   |

|     |     | 1   |          | 0        | 0   |                                                   |

|     |     |     | 0        | 1        |     |                                                   |

|     |     |     | "        | 0        | 1   |                                                   |

|     | 0   |     |          | 1        | 1   |                                                   |

|     |     |     | 1        | 0        | 0   |                                                   |

|     |     | 0   | <u> </u> | <u> </u> | 0   |                                                   |

|     |     |     | 0        | 1        |     |                                                   |

|     |     |     |          | 0        | 1 0 |                                                   |

|     |     |     |          | 1        | 1 0 |                                                   |

|     |     |     | 1        | 0        |     |                                                   |

|     |     | 1   | -        | 1        | 1   |                                                   |

|     |     |     | 0        | ļ        | 0   | 4400-7FFF                                         |

|     | 1   |     |          | 0        |     | 15 copies of                                      |

|     | 1   |     | 1        | 1        | 1   | 1K RAM                                            |

|     |     | 0   |          | 0        | 1 - |                                                   |

|     |     | "   |          | 1        | 1 0 |                                                   |

|     |     | -   | 0        | 0        | 1 0 | 4000-43FF; 1K RAM                                 |

| 0   |     |     |          | 1        | 1   | - 1440A - 141 T T T T T T T T T T T T T T T T T T |

|     |     |     | 1        | 0        | 0   | 2000-3FFF                                         |

|     |     | 1   |          | -        | 0   | Copy of BK                                        |

|     |     |     | 0        | 1        | 1 0 | ROM                                               |

|     | 0   |     |          | 0        | 1 0 |                                                   |

|     |     |     |          | 1        | 1 0 | _                                                 |

|     |     |     | 1        | 0        | 1   | 0000-1FFF                                         |

|     |     | 0   |          | 1        | 0 1 | 8K ROM                                            |

|     |     |     | 0        |          | 0   |                                                   |

|     | 1   |     |          | 0        | ö   |                                                   |

FIG 2 — ADDRESS BITS A10-A15 DIVIDE STORE INTO 64 1024-BYTE SEGMENTS

No reference has been made to the Printer, which is a standard accessory for the ZX81, but which may not be available for use with the TS1000. Virtually no circuitry at all is provided to serve this accessory, which connects to the external connector. All its needs are catered for by a section of the ROM program, which passes out data in the simplest possible form. However, the printer cannot be ignored completely, as certain input/output addresses are dedicated to it, and these may be called if LPRINT or LLIST are invoked by mistake. An output to port FB enables or disables the printer, and also conveys data. while an input on the same port provides an indication that the printer is (or is not) ready to respond. Note that FB in binary is 11111011. The low bit is the significant fact, when coupled with the high state of the other bits. A number of other input/ output addresses with bit 2 low will serve in place of FB, and all such addresses should be avoided for other purposes.

#### The Memory Map

The processor generates sixteen address bits, which appear on kines A0-A15. This allows 65536 addresses to be defined, in the manner illustrated in Fig. 2.

Normally, bit 15 determines whether the upper or lower half of the address range is to be used, and bit 14 determines which quarter within that half is to be used, and so on. The ZX81 works in a slightly different way.

In the basic machine, A15 is ignored, so the contents of the lower half of the address range can be found repeated as a 'ghost' in the upper half of the range. Add 32768 to an address in the lower half of the range, and the contents of the address so formed will be same as the contents of the lower address.

A14 is used to select ROM when it is zero, and RAM when it is 1. In the basic machine, A13 is ignored, so there are again ghost copies within the respective quarters of the memory range.

Internal 1K RAM uses bits A0-A9, A10 being added with 2K memory. External 16K memory uses A0-A13. Each added bit

suppresses part of the ghosting, and some add-on memories suppress the ghosting entirely.

The 8K ROM uses A0-A12, and in the basic machine produces a ghost at 2000-3FFF.

Those who want to explore the ghosts will find the DUMP programs in Appendix A useful. The hexadecimal form may call for more thought by those not familiar with that form of notation, but it will be found to give a clearer picture of the memory structure.

The ghosts must be eliminated if the memory area they occupy is to be put to other use, and this is done by pulling ROMCS' or RAMCS' high, according to whether the ghost originates from ROM or RAM. The elimination must be selective, on the basis of the address pattern for the area to be cleared. For example, the upper half of memory could be cleared by pulling both chip-select lines (ROMCS' and RAMCS') high when A15 = 1, but they must not be forced low when A15 = 0. Even in this relatively simple case it would be wise to make a check before firm installation, as it appears that suppression of the ghost might affect the operation of the display routine.

The input/output address map is more difficult to fathom. Most Z80 systems use only bit A0-A7 to define I/0 addresses, but the processor does generate nominal sixteen bit addresses for IN and OUT instructions:

IN A, (N): The contents of register A define the upper eight bits, the value of N defines the lower eight bits.

OUT (N), A: The contents of register A define both the data and the upper eight address bits, the value of N determines the lower eight bits.

IN, r (C): The contents of register BC define the address.

OUT (C), r: The contents of register BC define the address.

The addresses used by the basic ZX81 system have lower bytes FB, FD, FE and FF. However, the decoding is simplified

to a point where any even-numbered address will read the keyboard, and if the four addresses are written out in binary it becomes clear that only the low bit is being checked:

FB: 11111011 FD: 11111101 FE: 11111110 FF: 11111111

It is therefore necessary to limit addresses used for external equipment to those with the three least significant bits high, and bit 7 should preferably be low, to avoid conflict with FF. The concise rule is that addresses may be used if they are one less than a multiple of eight in the range 0-127. This allows sixteen addresses. Some expansion might be possible by utilising the upper eight bits, but these are also used by the ZX81, and caution is necessary.

It would be fair to say that the addresing systems of the ZX81 have been whittled down to a minimum, and that this can produce problems when the system is extended. In the case of memory addresses, the two chip select lines allow clearance of ghosts, but there is no comparable facility for input/output. One user did experiment with the insertion of a resistor in the IORQ line to the ULA, hoping to use it to allow the input to the ULA to be pulled high, making internal input/output inactive, but the scheme failed on timing grounds, and also because the display system got itself into a terrible tangle, with interesting but unreadable results.

There is one important way out. The ZX81 provides no IN or OUT functions in its BASIC, which means that special machine code routines have to be provided to drive input/output functions. On the other hand PEEK and POKE provide convenient access to all memory locations, so it would be much more satisfactory to be able to use memory addresses as channels for input/output data.

Nothing could be simpler. Where a normal input/output circuit uses IORQ as a qualifier, MREQ is used instead. Any ghosts in the memory area used must be suppressed, but the

FIG 3 — ALTERNATIVE RAM LAYOUTS

limitation in available addresses is overcome, and no machine code need be provided. It may be a coward's way out, but there are times when bravery is wasted...

#### Internal RAM

The provision of a thousand or two thousand bytes of storage sounds ample for simple programs until the way the bytes are used is examined in detail. The Display File alone can absorb up to 792 bytes, with a full screen, and this is usually the first area to suffer when memory is used up. The system variables take up another 125 bytes, and room still has be to found for the program, the input buffer and the stacks. As programs become more ambitious, the need for extra store rapidly becomes evident, especially if only 1K is available.

The advice from Sinclair, not unnaturally, is to buy a RAM pack, but that is not the only option.

The RAM layout is shown in Fig. 3. Provision is made for two 1K X 4 memories, using 18-pin 2114 chips, or one 24-pin chip can be used, giving either 1K X 8 or 2K X 8. For the 2K memory the small link beside the 24-pin RAM position must be moved from L1 to L2 in order to bring address line A10 into play.

This allows uprating of a ZX81 1K memory to 2K, as in the TS1000, but there is scope for further development. As Fig. 3 shows, the connection pads for a 28-pin chip have been designed into the layout, and this is almost connected in the way required by the  $4K \times 8$  static chips which are beginning to surface. Fig. 4 shows how the pinouts of the 24 and 28 pin RAMS compare. Some of the connections are already provided, and the rest would not be too difficult to make. It would not be impossible to accommodate an  $8K \times 8$  RAM, but the '64K' RAMs are still a mite expensive.

The big bugbear in any internal RAM change is the need to remove existing RAM from the circuit board, unless a chip socket is provided. The correct approach is to clear the solder from each pin in turn, using a 'solder sucker' after just melting the solder on a pin with a brief touch of the iron. When most of

FIG 4 - PINOUTS FOR COMPATIBLE RAM RANGE

FIG 6 - CONNECTIONS FOR PIGGYBACK RAM EXTENSION

the pins are free, the last few will probably yield to a bit of gentle leverage combined with short dabs of the iron, but all the surplus solder needs to be cleared away to allow a replacement chip to be inserted.

The coward's approach is to snip the pins of the original chip with a pair of very fine-nosed cutters, so that the pins can be removed independently, but that means the chip has to be thrown away. Solder clearing is still essential.

When a change has been made, the check PRINT PEEK 16388 + 256\* PEEK 16389 should give a RAMTOP value expressing the full size of the enlarged memory. The figures are:

1K memory: RAMTOP = 17408 2K memory: RAMTOP = 18432 4K memory: RAMTOP = 20480 8K memory: RAMTOP = 24576 16K memory: RAMTOP = 32768

If the expected figure fails to appear, a careful check for shorts between pins may discover the reason, that being the commonest cause.

Those who have no objection to the somewhat dubious practice of soldering one IC to the pins of another may take a different line towards memory expansion, though they will need to keep a wary eye on available headroom.

Fig. 5 shows the arrangement for a pair of 2K × 8 RAMs (e.g. Hitachi 6116). Pins 18 and 20 of both RAMs must be bent out sideways so that they can be connected separately, and a lead must be brought away from the pad to which one of the lower pins would otherwise be linked. Selection logic must then be provided, as shown in Fig. 6, the chip being a 74LS00 quad NAND gate mounted upside down on the circuit board by 'sticky fixers', the little pads with adhesive on both sides. Remember that the pins will be seen in reverse, making the numbering look unusual.

When the original chip enable, taken from the unused pad for pin 18 or 20 of the RAM, is low (active), one or other of the

| A14 | A13 | A12 | A11 | A10 |                               |                                                                      |

|-----|-----|-----|-----|-----|-------------------------------|----------------------------------------------------------------------|

|     |     |     | 1   | 1 . | GHOST OF 1K RAM<br>3000-3FFF  |                                                                      |

|     |     | 1   | '   | o   | GHOST OF 1K RAM<br>3800-38FFH | A5 A16 is ignored,<br>the whole area gives<br>a ghost at A000-BFFF H |

|     |     |     | 0   | 1   | GHOST OF 1K RAM<br>3400-37FFH | A14 = 0 and A13 = 1 are required conditions                          |

| 0   | 1   |     |     | o   | 1K RAM<br>3000-33FFH          | A12 selects ROM or RAM A11 is ignored                                |

|     |     |     | 1   | 1   | GHOST OF 2K ROM<br>2800-2FFFH | A10 is ignored by RAM                                                |

|     |     | 0   |     |     |                               |                                                                      |

|     |     |     | 0   | 1   | 2K ROM<br>2000-27FFH          |                                                                      |

|     |     |     |     | 0   |                               |                                                                      |

FIG 8 - MEMORY MAP OF ROM/RAM ADDITION

FIG 9 — POSSIBLE LAYOUT FOR ROM/RAM ADDITION, USING 0.1" VEROBOARD

( ⊗ indicates a wrong pin)

outputs of the NAND gate complex will be low, according to the state of A11, and one of the two RAMs will be enabled. The same scheme can be used with 1K RAMs, in which case A10 should replace A11.

Having considered possible ways of extending RAM, it is reasonable to look at possible ways of extending ROM, too. Many useful snippets of machine code have been proposed in the journals, and it is much better to have them available in ROM than to have to load them at the start of a session or after a power break.

The obvious choice for the ROM is a 2716 EPROM (Texas use 2516 for the equivalent.) This provides storage of 2K bytes of fixed data. It has to be programmed, but some suppliers will set up customer's programs for a reasonable charge, or a friendly owner of a programming device might help.

It is convenient to have some RAM associated with the ROM, and this should be set in a memory area where it will not be open to corruption by the programs in the main ROM. A pair of 2114 RAMs, each giving 4  $\times$  1K storage, will serve very well, and if both ROM and RAM are placed in the 2000-3FFF region they will be out of harms way.

The circuit is shown in Fib. 7, with the memory map in Fig. 8. The diode connecting A13 to ROMCS' suppresses the ghost of the main ROM when A13 is high, and the ROM/RAM combination is disabled when A13 is low, avoiding any clash between the two store sections. The 74LS155 decoder sets up the memory map, using A12, A13 and A14. As A11 is ignored, and A10 is used only with the EPROM, there will be ghosting, and additional decoding is necessary if the ghosts need to be cleared to make way for other store or memory-mapped addresses.

Construction is a matter for personal taste, but Fig. 9 shows a possible arrangement. This would be a tight fit inside the case, but a smaller layout would make the wiring more difficult. Note that the conductive strips on the Veroboard need to be cut where a given strip is used for more than one signal. If the

assembly is mounted inside the ZX81 case, make sure that no shorts can occur by placing a sheet of insulating material between the two circuit boards.

If the problem of programming the EPROM can be solved, this assembly can be used to create a completely independent operating system, removing some of the limitations of the BASIC interpreter program, especially where machine code is concerned. There are so many possible routines that could be included that it would be a pity to describe only a small sample, but Appendix B gives an indication of what can be done, while some of the input/output routines which are described in the section on Externals could be useful.

Access to the EPROM programs is made by the USR function, as described in the manual.

#### The Display System

The method of producing the display is very complex, involving both hardware and software, and uses some obscure or unadvertised characteristics of the Z80 processor. Only a superficial description can be given here, but it should suffice as a useful guide for those who wish to explore more deeply.

The display phase is initiated by a pulse generated by the ULA which is passed to the processor as a non-maskable interrupt (NMI). This causes the processor to jump to location 0066H, where there is an interrupt servicing routine. This increments A', the alternative A register, and if the result is not zero the interrupted program is resumed. If A'=0, however, all the main registers are pushed on to the stack to preserve the data being used by the interrupted routine, HL is set to the Display File address held in 400CH, and then bit 7 of HL is set. A HALT instruction follows.

The processor now begins to execute two actions alternately: One action performs a NOP (no operation) instruction, which puts the contents of the program counter on to the address lines. The other action is a Refresh cycle, which puts out an address with the lower eight bits determined by the contents

of the Refresh register, and the upper eight bits determined by the contents of the I (interrupt vector) register, which are initialised to 1FH.

It should be noted, however, that the circuit using transistor TR1 holds the processor in a WAIT state until NMI becomes false. The length of NMI therefore determines a period during which display action is held in abeyance.

When the output of a line begins, there is no time to hang about. The processes involved are much too rapid to be handled by the processor, which continues to output the two addresses described above, one after the other. The program counter address is set to point to the display file by performing a nominal jump to the address contained in HL, and the ULA uses this address to read character codes from the display file. As soon as a code has been read, it is used to form an address based on the processor output during refresh, the character code, and the output of a three bit counter in the ULA. The address is:

where I is the number in the I register (1EH), CODE is the code read from the display file, and COUNT is the output of the three-bit counter. The address points to a pattern byte stored in the top of ROM at 1EOO-1FFF. The byte is read by the ULA and output serially to the video modulator at a 6.5 MHz clock rate.

COUNT is incremented by each television line sync pulse, and determines which of the eight bytes forming the character is to be used. Each line of characters in the display file is read eight times before the system moves on to scan the next line.

The following BASIC program illustrates this action, and may help to make it comprehensible:

```

10 INPUT CODE

```

20 CLS

30 FOR C = 0 TO 7

40 LET PATTERN = PEEK (7680 + CODE\*8 + C)

```

50 FOR B = 1 TO 8

60 LET A = INT (PATTERN/128)

70 LET PATTERN = 2* (PATTERN - 128*A)

80 LET Z$ = CHR$ 8

90 IF A = 1 THEN LET Z$ = CHR$ 128

100 PRINT Z$;

110 NEXT B

120 PRINT

130 NEXT C

140 GOTO 10

```

A character code (0-63) is input. C represents the binary counter, and the PEEK address is that defined above for pattern access in the real system. The bits of the pattern are represented on the screen.

The BASIC performs the progress slowly, but the actual output of data handles a new byte every 1.23 uS, filling out one pattern row of a 32-character line in 40 uS, the time which the television scan takes to traverse the display area. It all fits in beautifully, but working it out must have cost a few headaches . . .

When 256 bytes have been output, making up a complete line of characters, it is necessary to move on to the next line of characters in the display file, and this is handled by the main interrupt routine at 0038H.

For the present purpose, however, the point of most importance is the effect which this system has on extensions of the basic ZX81. One slightly unexpected point is that if more than 16K of RAM is provided it is important to make sure that the display file does not lie across the boundary set at address 8000H. If it does, the system will fall apart, because the significance of setting bit 15 in the display file address will be different for the two parts of the file, and the pointer to the file will get lost.

In FAST mode, there is no need to worry about display system for most of the time. NMI is suppressed, so that display action does not occur.

FIG 10- KEYBOARD CIRCUIT

FIG 11 - LAYOUT OF KEYBOARD CONNECTIONS

In SLOW mode, the main point to watch is that any of the pointers used in the display system are left well alone. Attempts to poke into the display file can cause a crash if the character displaced is a NEWLINE, but poking is possible if a check for NEWLINE is made first.

On the whole, it is best to skirt round the display system wherever possible. This is yet another case where discretion is the better part of valour.

#### The Keyboard

Whatever else may be said about it, the keyboard system of the ZX81 is an outstanding example of simple ingenuity. Forty pressure pad switches and eight diodes, plus connections, account for all the visible hardware.

As shown in Fig. 5, the switches are connected in a matrix of eight rows and five columns. The rows are connected through diodes to address lines A8-A15, and the columns are connected to input port FE, which is hidden in the 'dogsbody' chip.

To interrogate the keyboard, it is necessary to read from port FE while holding one of the top eight address lines low and the others high. That may sound as if a conjuring trick is needed, but instruction ED 78 makes it all easy. The instruction mnemonic is IN A, (C), and the action is to input data from a port defined by the contents of the C register, the data passing to the accumulator. The small print remarks in passing that the upper eight address lines happen to be determined by the contents of the B register.

The instruction sequence to check a key might be:

LD BC, FEFEH IN A, (C) BIT O, A

The contents of B would set address line A8 low while holding A9-A15 high. Row 3 of the keyboard would therefore be pulled low, and if any switch in that row was pressed the corres-

ponding column output would be pulled low. The check on bit 0 would give a zero result if the Shift key, in column 1, is pressed.

The keyboard input routine is located at 02BB on, though this section only sets low bits in HL to indicate which key is pressed. Further processing, taking note of the current working mode, is needed before the actual meaning of the depression can be determined.

Providing a more orthodox keyboard is no great problem. A well-spaced layout is so large that the usual practice is to mount the circuit board inside the keyboard case, taking care that the power, TV and tape recorder connections and the external interface are conveniently accessible. The replacement keyboard can be wired by ribbon cable to the pins of the film wire sockets, since suitable replacement film wire would be more difficult to provide.

In passing, it may be remarked that the film wire may kink or otherwise suffer damage if it is pushed into the sockets carelessly. In such a case the remedy is to clip off the ends and so provide fresh material, but this cure will only work a limited number of times.

In addition to providing the forty replacement key switches, some further improvements can be made with a new keyboard. One of the most obvious is the provision of a proper Reset key.

The reset line of the ZX81 is pulled towards +5v by a resistor, and tied to ground through a large capacitor. At switch-on, the capacitor delays the rise in voltage, so that the processor is initially held in the reset state. As the voltage on the reset line rises, the processor is freed to work normally.

All that is needed to provide a manual reset is to connect a switch between the reset line and ground. When the switch closes, the line is grounded, and the reset state is entered. Open the switch, and the line voltage rises towards +5v, allowing normal action to be resumed. This can, of course, be

provided without changing the keyboard, the switch being fitted at a convenient position in the ZX81 case.

A slightly less obvious change is the provision of single keys for functions that normally need two. Double pole switches are needed, and these are connected in parallel with the normal switches, as follows:

Function select: Shift and Newline

Rubout: Shift and 0 Edit: Shift and 1

Similar treatment may be convenient for the 'arrow' functions, Graphics, etc. This is a matter of taste.

Unfortunately, a general repeat function does not seem feasible, though it would be very useful. It would require a method of interrupting all the keyboard paths to simulate repeated key depressions. The permissible repeat rate varies widely, too, as the response to some key actions can take a relatively long time.

Finally, some other uses of the keyboard input port must be noted.

The keyboard column outputs appear on bits 0-4 of the port, corresponding to pins 33, 31, 29, 27 and 25 of the ULA. Bit 5 of the port is similarly related to ULA pin 22, which is tied to ground in the American version. When the keyboard routine has checked the keyboard inputs, it goes on to check bit 5, and if the bit is high (MARGIN) is set to 37H (55), the value for a 50Hz television frame scan. If the bit is low, (MARGIN) is set to 1FH (31), the value for a 60Hz frame scan.

Bit 6 of the port signals, by a high state, that data from tape is available, one bit at a time, and Bit 7 provides the data.

# THE EXTERNAL INTERFACE

The connector which forms part of the rear edge of the ZX81 circuit board carries most of the signal lines which are likely to be needed for communication with external devices. However, the utility of some of the signals is restricted by the way in which they are used by the internal system, so the connection of external equipment must be approached with a measure of caution. A detailed examination of the signals here will lay the ground for the descriptions of specific add-on facilities

# Address Lines: A0-A15 Sixteen active high outputs.

The address lines are driven directly by the processor, and should not be too heavily loaded. If more than two TTL inputs have to be driven, the lines should be buffered, but the buffering must be simple, or there may be unacceptable signal delays.

The lines serve both memory and input/output, the latter normally using only lines A0-A7, though the state of lines A8-A15 can be determined by certain input/output instructions, as described in relation to the ZX81 keyboard system.

In theory, all the address lines ought to be taken into account, but the discussion of the ZX81 memory map showed that this was not entirely essential. What is essential is that there should be no overlap between the memory or input/output address areas used by different devices. This can be assured by adequate decoding, and the disablement of internal ZX81 memory where necessary, using RAMCS' and ROMCS' (see p45).

The external lines are coupled to the ROM address inputs via 1K ohm resistors. This allows the ULA to take over control during screen refresh.

#### Data Lines: DO'-D7'

Eight active high lines, bidirectional

The main data lines are not brought to the external connector, which receives the secondary data lines, coupled to the main lines via 470 ohm resistors. The main lines connect only to the processor and ULA, the subsidiary lines serving the memory.

Use of the data lines is controlled by strict rules. When data is being output by the ZX81, no external device may drive the lines. When data is being input by the ZX81, only one external device may drive the lines. (Though this second rule can be broken if the implications are properly understood.)

The usual way of satisfying the rules is to use devices with 'tristate' outputs, which disconnect themselves from the output lines except when they are enabled. The enable signals are obtained by decoding address and control line signals.

Loading on the data lines should be kept light. The use of buffering is complicated by the bidirectional use of the lines, but is not impossible.

# Memory Request: MREQ

One active low line, output.

The processor makes this line low when it wishes to communicate with memory, whether reading or writing.

# Input/Output Request: IORQ

One active low line, output.

The processor makes this line low when it wishes to communicate with an input/output channel.

#### Read: RD

One active low line, output.

The processor makes this line low when it wishes to receive data.

# Write: WR

One active low line, output.

The processor makes this line low when it wishes to transmit data.

# **ROM Chip Select: ROMCS'**

One active low line.

This line is connected to the chip enable pin of the ROM, and is driven by the ULA through a 680 ohm resistor. If the line is pulled high by an external device, the ROM will be disabled, and both the normal output and the 'ghosts' will disappear. This must be done selectively, on a basis of the address in use. If the line were pulled high by a direct connection to +5v, the system would fail to work. At the least, the line must be allowed to go low for addresses in the 0000-1FFF range, i.e. when A13, A14 and A15 are all low, unless an alternative ROM program is supplied externally.

However, it is both permissible and useful to disable the internal ROM when A13 or A14 or A15 is in a high state, as this eliminates all the 'ghosts' of the ROM.

# RAM Chip Select: RAMCS'

One active low line.

This line works on the same principle as ROMCS', but is connected to the RAM chip enable pins. If external RAM running up from address 4000 is provided, RAMCS' may be tied to +5v or otherwise taken high. This disables the internal RAM completely. (If +5v is used to pull the line up, it should be applied through a 330 ohm resistor as a safety precaution. This also applies to ROMCS'.)

If the internal RAM is to remain in use, with external RAM in other areas, the internal RAM should be enabled only when A14 is high and A10, A11, A12, A13, A15 are all low. If the 2K internal modification has been carried out, A10 must be deleted from the address lines used.

#### Reset: RESET

One active low line.

If this line is taken low, the processor action stops, and when the line is released the processor will restart by reading an instruction from location 0000. When power is first applied, the Reset line is held low by capacitor C5, which charges up slowly through R15 until the processor is enabled to start. Shorting the Reset line to ground discharges the capacitor, and releasing the short produces a normal restart from 0000.

The line may be used to reset external devices in the same circumstances.

In some Z80 systems, the start location is varied by creating artificial data as Reset is released, but this requires direct access to the processor data lines, which is not available at the external connector. Those who are interested in using an alternative ROM program which can be entered automatically may like to investigate the possibility of supplying an artificial absolute jump instruction (e.g. C3 XX XX) in response to the first three processor reads after reset is released . . .

#### Halt: HALT

One active low output line.

If HALT is low, the processor is obeying a HALT instruction. The line goes high in response to an interrupt or the release of Reset.

This signal is used by the internal system, and may be of possible use in determining whether processing or display refresh is being executed.

#### Wait: WAIT

One active low input line.

Making this line low puts the processor in an idle state. The line is normally used for gaining extra time for slow memory or input/output devices to respond, but in the ZX81 it has a special use, being controlled by TR1. It is therefore doubtful whether

external use is practicable, though some experiments might be worthwhile if response time proves a problem.

# **Bus Request: BUSRQ**

One active low input.

# **Bus Acknowledge: BUSAK**

One active low output.

If BUSRQ is made low, the processor is asked to yield control of the system. When the current instruction has been executed, the processor will make BUSAK low to signal acceptance, and will then allow the lines which it controls to 'float', so that they can be controlled by other means.

Making use of this state is a complex matter, and is made more so by the presence of the ULA. However, the signals may be of use in FAST mode, when the ULA is less active.

# Clock: 0

One active low output.

The clock generator runs at 6.5 MHz, but a divider in the ULA generates a 3.25 MHz clock for the Z80, and this is available externally.

#### Refresh: RFSH

One active low output.

The Refresh signal is intended for use with dynamic RAM, and the circuit diagram proposes its use for that purpose, but it is also affected by the ROM program, and may not be trustworthy in SLOW mode. It has been assumed that static memory is safer.

# Non-Maskable Interrupt

One active low input.

The NMI line is controlled by the ULA, calling a jump to location 0066 when it is low. It is not available for external use.

# Interrupt: INT

One active low input.

The interrupt line is coupled to A6 inside the ZX81, and is not available for external use.

# Machine Cycle 1: M1

One active output.

The processor makes this signal low during the first cycle of an instruction fetch. It is also made low, with  $\overline{IORQ}$ , to indicate that an external interrupt vector is required. No external use can be envisaged.

#### Ground

Two connector pins are used, to ensure good contact.

#### +5 volts

This line is supplied from the output of the internal regulator, and may be used for loads of up to 50-100 mA. Higher loads may damage the regulator, and even 100 mA will add to the internal heat dissipation to an undesirable degree. This line must not be connected to +5v derived from an external source, as one or the other will tend to take the whole load.

#### +9 volts

This line comes from the external power pack. The off-load voltage is appreciably above the nominal value, falling sharply as load is applied. However, it can be fed to a regulator in external equipment to derive a stabilised 5v supply, providing the total current drawn by external equipment does not exceed 400 mA. For higher currents, a separate power source is necessary.

#### Using the Interface

It may appear that there was no sense in bringing out some of the interface lines, as they cannot be used by external equipment, but it should be noted that they have a value for the manufacturer, in that the board can be plugged into test gear for a comprehensive check.

In terms of user requirements, there is a great deal that can be done with the signals provided, as will be shown on the following pages.

# **EXTERNALS**

Before getting down to the creation of add-ons, it is as well to consider how far you may want to go. A random addition of one section after another may lead to chaos, so some advance planning is useful, taking the limiting factors as a starting point.

The most important limitation may well be the power supply. A small system drawing 50-100 mA may rely on the internal regulator, but heavier demands, up to about 400 mA, will require a separate regulator driven from the +9v supply. If more than 500 mA will be drawn, then a separate power source is necessary, such as that shown in Fig. 12. More than one of these sources may be used in conjunction, but the various 5v lines must not be linked, or something is likely to cook.

The next limitation to consider is the available range of addresses. Relatively few input/output addresses are available for external use, but memory mapping may provide an alternative.

An extremely elementary but important limitation is that the external connections of the computer need to be made available to all the add-on devices. Some professionally made devices use the system illustrated in Fig. 13, which allows one device to be plugged into another. This is quite a satisfactory scheme, providing the individual units are coupled by spacers and through-bolts, so that the connector is not under mechanical stress.

Another approach uses a motherboard with sockets to connect up the individual devices. This has the advantage that an extra power supply can be mounted on the motherboard, but it is likely to be more expensive, due to the cost of the connectors.

One problem with large systems that may not become apparent until too late is that the first connector — and the part

FIG 12 - ADDITIONAL POWER SUPPLY (1A AT 5v)

FIG 13 - NESTED CONNECTION SYSTEM FOR ADD-ONS

of the circuit board with which it mates — may be put under strain, or the actual computer may not be easy to position conveniently for use. The obvious answer is to insert a connection lead between the computer and the add-on complex, but this needs to be done properly. If a casual bunch of wires is used, there may be cross-talk between different lines, and that can be a serious problem.

One approach which has been found to work well is to use ribbon cable, earthing alternate conductors to form a sort of screen. Two such cables will probably be needed, one for the upper connections and the other for the lower.

More generally, it is only too easy to forget that computer circuits work at frequencies well above those which were regarded as the top radio bands a few years ago. This means that the layout of wiring is important. Excessive neatness obtained by lashing bunches of wires together is a sure road to failure.

A good recipe is to start with one of the standard Veroboard layouts, keeping the connections on one side of the board parallel as far as possible. Solder pins can be used to simplify wiring, though they are not essential.

Since the add-on systems which are to be described are basic types open to considerable variation, it will not be possible to describe the construction in full detail, but in most cases the circuit diagrams have been drawn in such a way that layout is suggested. What the diagrams cannot show effectively is the need to put decoupling capacitors, usually of 0.01 uF, across the power feeds to each integrated circuit. These should be near the component they serve.

Test add-ons as much as possible before linking them to the computer, using lash-up test rigs, and there will be a lot less difficulty in getting the overall system going.

#### **External Store**

The first add-on that occurs to mind is external memory, and the first memory component that you think of may be the 2114

For any RAM to be enabled, G1 and G2 must be low, i.e. MREQ = 0, A14 = 1, A15 = 0. If the A15 input is omitted, ghosting will occur at COOO—FFFFH, which may not be important.

FIG 15 - ENABLE DECODER FOR SIXTEEN IK RAMS

$1K \times 4$  RAM, mainly because it is cheap and readily available. Unfortunately, it is also rather greedy where power is concerned. Intel quote 50/70 mA, which would soon absorb available current. A 16K RAM extension, using the internal RAM chip to provide 1K, would involve 30 2114s, which would draw at least 1.5 A.

Some of the more recent static RAM chips are much more modest in their requirements. The HM-6515 1K  $\times$  8 CMOS RAM draws around 10 mA, and so does its 2K companion the HM-6516. These devices cost more, but are easier to use.

Fig. 14 shows a 16K RAM built up from HM-6516 components. Address lines AO-A10 go to all eight RAM chips, and so does the  $\overline{WR}$  line, so these signals are buffered by 74LS241 octal buffers. The data lines also go to all the RAM chips, but the loads in this case will be light, so no buffering is needed.

With +5V and ground, that accounts for 22 of the 24 RAM pins. The remaining pins are chip enable and output enable, and these are driven selectively by a 74LS155 decoder. Two elements of a quad NAND gate chip, 74LS00, enable the decoder when A15 = 0 and A14 = 1, to put the RAM array in the 4000 - 7FFF address range.

Each RAM needs a decoupling capacitor of 10 nF connected to +5v and ground close to the chip.

This is one possible configuration of external RAM among many, but it should provide a useful guide to the form of other arrangements. If A15 and A14 are exchanged, the RAM will respond to addresses in the 8000-BFFF range, and if the inverter in the A15 line is removed the address range will be COOO-FFFF.

Consider the circuit for a moment: Using  $2K \times 8$  RAMs allows simpler decoding. With 1K RAMS, a 74LS154 16-way decoder would have been needed. (Fig. 15) In this case, the internal 1K RAM could have been used, its select line being connected to one output of the 74LS154. With 2k RAMS in use, the internal RAM must be permanently disabled.

Setting up a good external memory is thus a matter of compromise and balance. A more expensive type of RAM chip may save cost elsewhere, and is likely to simplify the wiring. Cut down on RAM cost, and there will be a penalty elsewhere.

The use of dynamic RAM is not viewed with enthusiasm. According to the circuit diagram, RFSH can be used in its intended role, but there must be a question mark over that. Dynamic RAM also involves address switching to place AO-A6 and A7-A13 on the seven address pins in turn, and though this minimises the task of address decoding it is a complicated alternative. If you want to experiment in this area — Good luck!

The provision of external ROM is very little different from the provision of RAM. The  $\overline{RD}$  signal replaces  $\overline{WR}$ , but the rest is essentially the same.

A point worth making, however, is that with RAM it is permissible to scramble the address lines or the data lines, since no one cares exactly which of the internal storage elements is used for a particular purpose. This is not permissible with ROM, which has to be set up on the assumption that the address lines are correct. This is a question of compatibility between the equipment which creates the ROM and the equipment which uses it.

It should also be remembered that if ROM is placed in the middle of a RAM area, the initialisation program will ignore the existence of the higher block of RAM, even if an attempt is made to bring it into action by modifying RAMTOP.

The best place for ROM is in the 2000-3FFF area, and since the presence of ROM usually implies the need for associated RAM, a small block of RAM may be placed in the same area.

A last word on memory: Don't be too eager to fill up all the available memory space at once. You may later find that there is a need to use it for some other purpose, and — to be frank — the idea of keying in programs long enough to use 48k of RAM does not appeal. The challenge of squeezing as much as

possible into 1K seems far more attractive . . .

#### A Simple Input Port

An unwise lecturer on a computer course once tried to dismiss input/output systems by saying casually that they were really just the same as memory systems. He later had cause to regret that remark.

In a sense, what he said contained an element of truth. From the processor point of view, the only difference between memory and input/output accesses is that for one  $\overline{\text{MREQ}}$  is made low, while for the other the signal is  $\overline{\text{IORQ}}$ . An input port should come into action when it recognises its address, put out in combination with  $\overline{\text{IORQ}} = 0$  and  $\overline{\text{RD}} = 0$ . It should respond by placing data on the appropriate lines, probably by enabling tristate outputs.

That said, there is room for variation. The port may be of various kinds. It may contain a clocked latch buffer, or a transparent buffer, or — less probably — it may pass on an instantaneous picture of what it is receiving on its input lines. The clocked latch enables data to be frozen at a moment determined by a timing system. The transparent latch can freeze data at the moment when the port is read, so avoiding change during the read process, which may cause trouble if the third option is used, the chance snapshot.

Now, suppose that data is presented to the port: How does the computer know when to read it? Once again, there can be a number of possible answers. The computer may take a reading at regular intervals, relying on its own internal timing system to decide the right moment. The computer may perform an output as a request for an input to be got ready. In almost any computer but the ZX81, the input channel could raise an interrupt to request the computer to read its data, but interrupt is barred in this case.

This leaves us with the 'polling' system, which relies on the 'handshake'.

Polling means that the computer makes a periodic check of its

FIG 16 - INPUT PORT

input channels to see if any of them have data available. Instead of looking at the actual input ports, it will look at an extra input port which is driven by bistables, one bistable to each real input port. When data is sent to a port it is strobed into a latch, and the strobe also sets the associated bistable. This makes the extra port show a 1 in the bit position corresponding to the real input port which has been set. The computer checks the extra port now and then, and when a bit is set the data on the corresponding port is read in. This also resets the bistable.

To avoid losing data, the state of the bistable is signalled back to the data source, which is prevented from sending more data until the bistable is cleared. This is the 'handshake', an essential process in controlling computer data paths that handle only one byte at a time.

Although the system described could serve up to eight input ports, it is equally applicable with only one. The ultimate simplification is to limit the data to seven bits and use the eighth bit to show the state of the bistable. The data read is discarded if the eighth bit is not true. This method is convenient with 7-bit ASCII data, and is a basis for one form of the 'Centronics' interface.