Jonathan A. Titus David G. Larsen Christopher A. Titus

# Tecniche di interfacciamento dell'APPLE

ESEMPI DI CIRCUITI INTERFACCIA

GIÀ COLLAUDATI, PER IL CONTROLLO

DEI DISPOSITIVI ESTERNI

E LA COMUNICAZIONE CON ALTRI CALCOLATORI

DIVISIONE LIBRI

**EDIZIONE ITALIANA**

# Jonathan A. Titus David G. Larsen Christopher A. Titus

# Tecniche di interfacciamento dell'APPLE

GRUPPO EDITORIALE JACKSON Via Rosellini, 12 20124 Milano

| © Copyright per l'edizione originale: Jonathan A. Titus, Cristopher A. Titus e David G. Larsen                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| © Copyright per l'edizione italiana: Gruppo Editoriale Jackson S.p.A.                                                                                                                                                                                                                                  |

| Tutti i diritti sono riservati. Stampato in Italia. Nessuna parte di questo libro può essere riprodotta, memorizzati in sistemi di archivio, o trasmessa in qualsiasi forma o mezzo, elettronico, meccanico, fotocopia, registrazione o altri senza la preventiva autorizzazione scritta dell'editore. |

| Seconda edizione 1986                                                                                                                                                                                                                                                                                  |

| Fotocomposizione: Corponove s.n.c. — Bergamo<br>Stampa: S.p.A. Alberto Matarelli - Milano -                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                        |

# **SOMMARIO**

| PREFAZIONE                                             | Ш  |

|--------------------------------------------------------|----|

| CAPITOLO 1 — IL PROCESSORE 6502                        | 1  |

| La memoria                                             | 2  |

| I dispositivi d'ingresso/uscita (I/U)                  | 6  |

| Riepilogo                                              | 6  |

| Le istruzioni software per il controllo dell'I/U       | 7  |

| I comandi di I/U                                       | 7  |

| I comandi di I/U d'uso generale                        | 9  |

| Le mappe di memoria                                    | 11 |

| I comandi software ed i circuiti d'interfaccia         | 12 |

| I comandi software. Trasferimento e controllo dei dati | 15 |

| Linguaggio assemblatore e BASIC                        | 16 |

| Numerazione binaria e numerazione decimale             | 17 |

| CAPITOLO 2 — L'INTERFACCIAMENTO DELL'APPLE             | 19 |

| Decodifica degl'indirizzi dei dispositivi di $I/U$     | 19 |

| Indirizzamento dei dispositivi                         | 20 |

| Uso delle porte per la decodifica degl'indirizzi       | 20 |

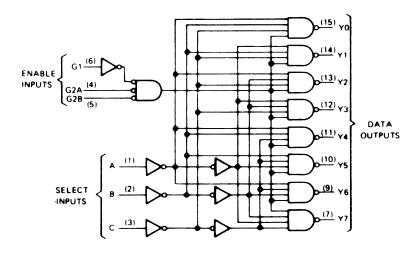

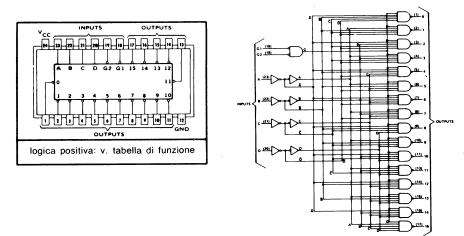

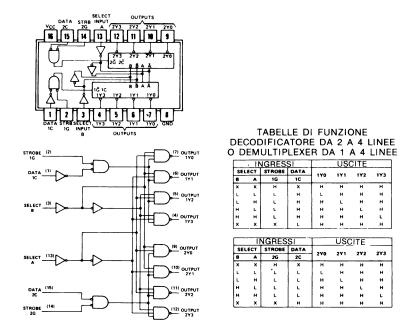

| Uso dei decodificatori                                 | 26 |

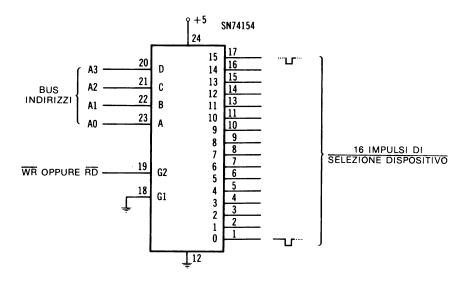

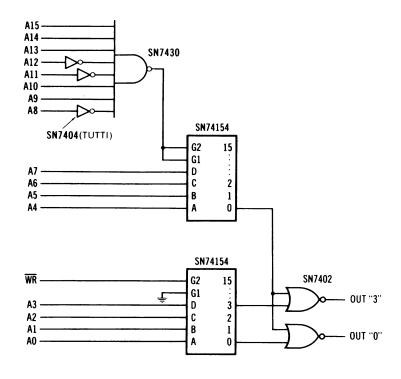

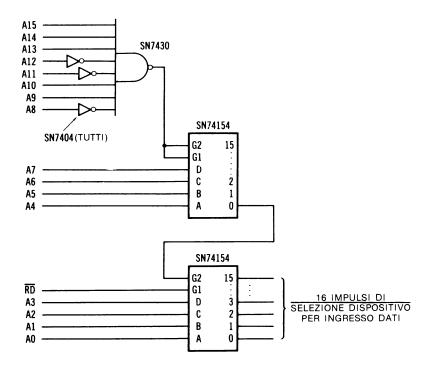

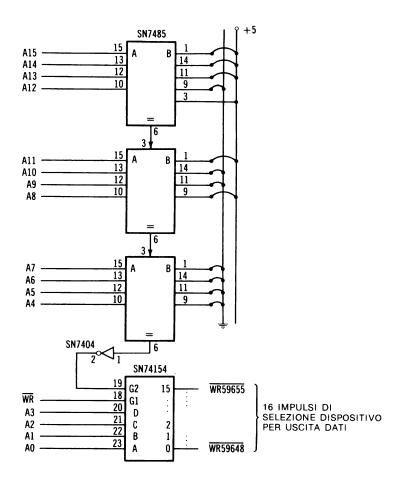

| I grossi decodificatori                                | 30 |

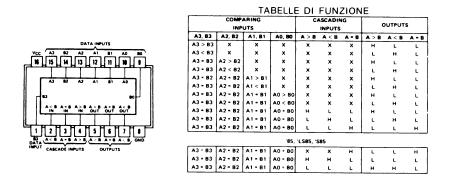

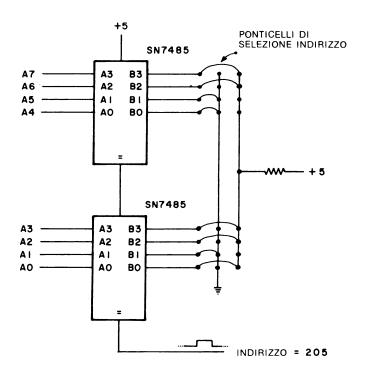

| Uso dei comparatori                                    | 35 |

| CAPITOLO 3 — L'INTERFACCIAMENTO DELL'I/U               | 39 |

| Le porte di uscita                                     | 39 |

| Le porte d'ingresso                                    | 45 |

| CAPITOLO 4 - FLAGS E DECISIONI                         | 53 |

| La sincronizzazione dei dispositivi di $I/U$           | 53 |

| Operazioni logiche e flags                             | 54 |

| Rilevazione dello stato dei flags                      | 55 |

| Le operazioni logiche in linguaggio assemblatore       | 56 |

| Flags complessi                                        | 59 |

| La circuiteria di flag                                 | 60 |

| Flags multipli                                         | 62 |

| Le interruzioni                                                      | 63  |

|----------------------------------------------------------------------|-----|

| Ancora qualche osservazione                                          | 64  |

| CAPITOLO 5 — LAVORIAMO CON LA SCHEDA DI PROVA                        | 65  |

| Configurazione base della scheda di prova                            | 66  |

| L'alimentazione                                                      | 66  |

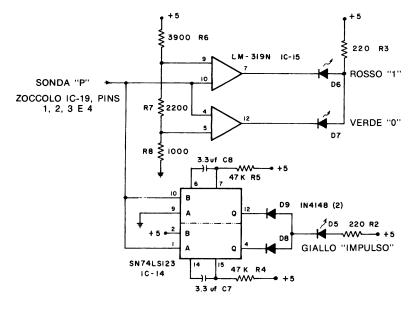

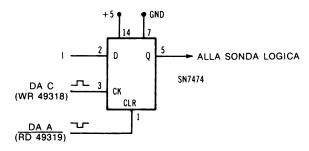

| La sonda logica                                                      | 67  |

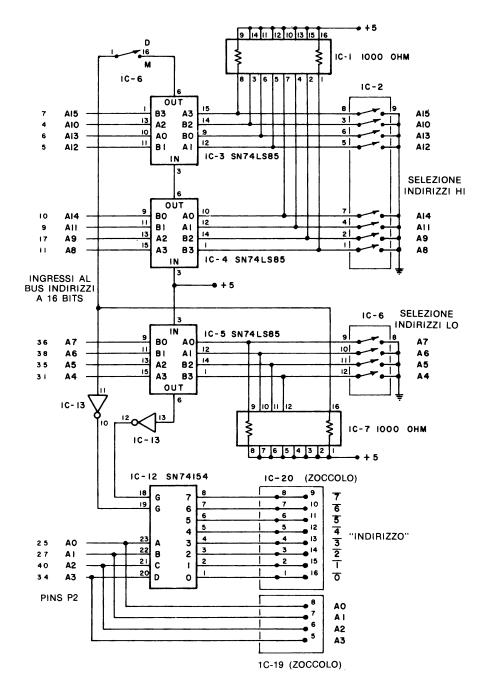

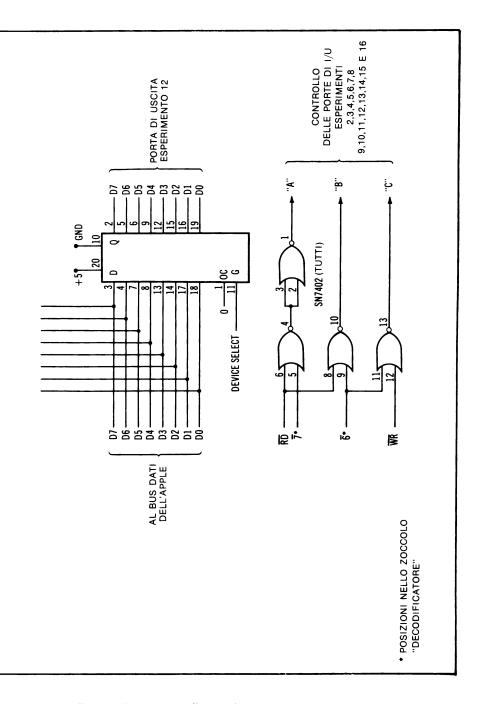

| Decodifica degl'indirizzi                                            | 68  |

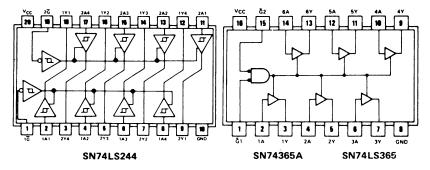

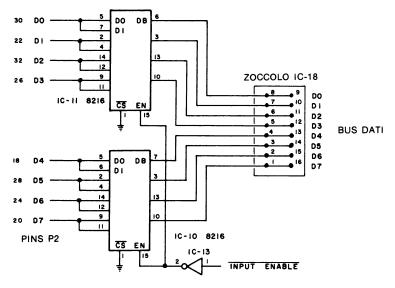

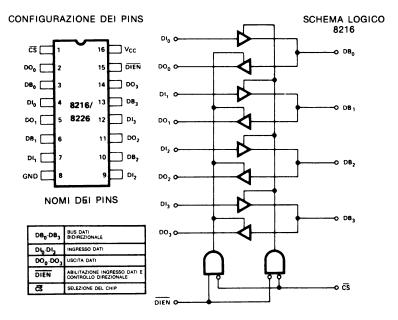

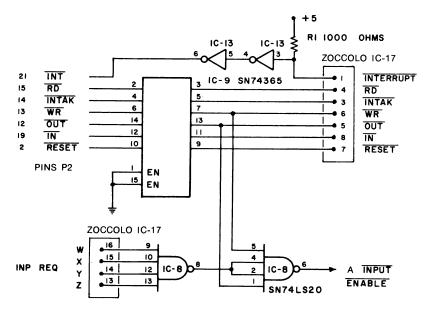

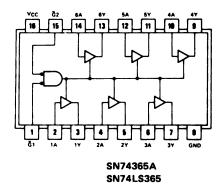

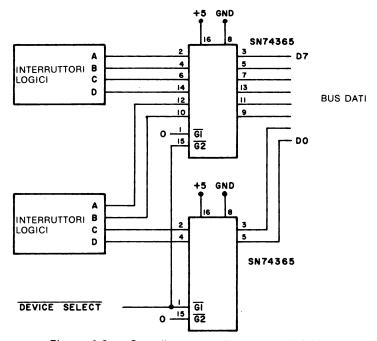

| I buffers bus                                                        | 71  |

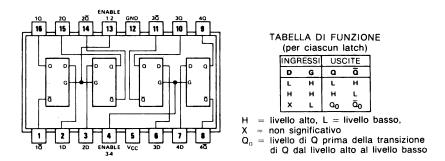

| La circuiteria di controllo                                          | 73  |

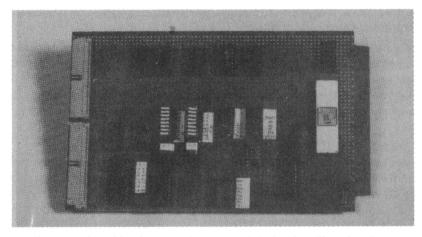

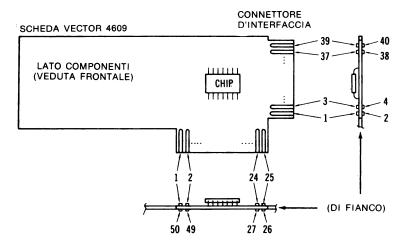

| Costruzione della scheda di prova                                    | 76  |

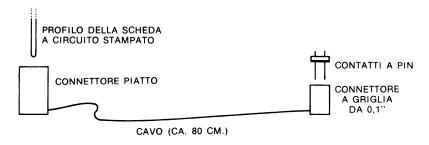

| Collegamento con l'Apple                                             | 77  |

| Qualche altra osservazione                                           | 80  |

| CAPITOLO 6 — ESPERIMENTI D'INTERFACCIAMENTO CON L'APPLE              | 83  |

| Osservazioni introduttive agli esperimenti                           | 83  |

| Esperimento n. 1. Uso della sonda logica                             | 86  |

| Esperimento n. 2. Uso del decodificatore d'indirizzo dispositivo     | 88  |

| Esperimento n. 3. Uso degl'impulsi di selezione dispositivo          | 92  |

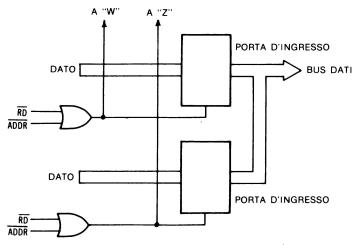

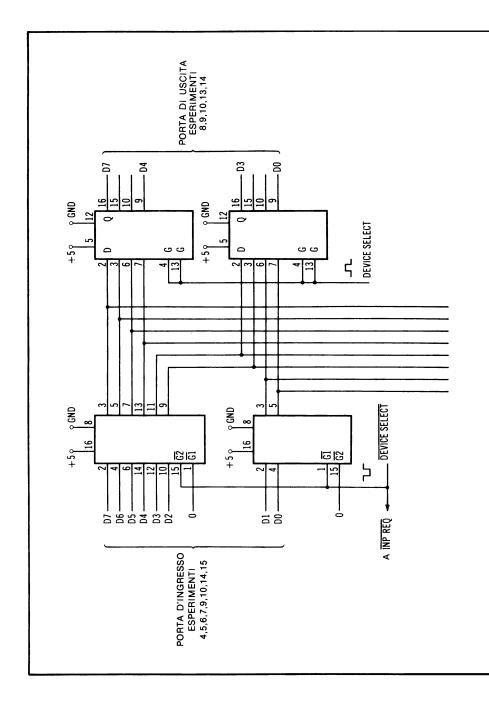

| Esperimento n. 4. Costruzione di una porta d'ingresso                | 96  |

| Esperimento n. 5. Porte d'ingresso multibyte                         | 99  |

| Esperimento n. 6. Applicazioni delle porte d'ingresso                | 102 |

| Esperimento n. 7. Applicazioni delle porte d'ingresso (2)            | 106 |

| Esperimento n. 8. Costruzione di una porta di uscita                 | 111 |

| Esperimento n. 9. Interazione fra porte d'ingresso e porte di uscita | 114 |

| Esperimento n. 10. Registrazione e visualizzazione dei dati          | 117 |

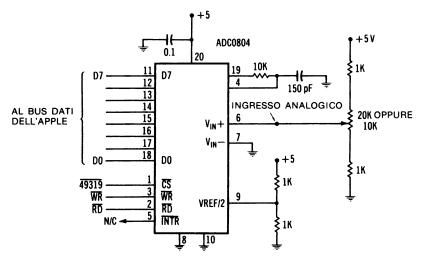

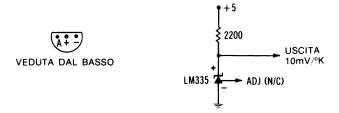

| Esperimento n. 11. Un elementare convertitore analogico-digitale     | 121 |

| Esperimento n. 12. Porte di uscita, BCD e codici binari              | 126 |

| Esperimento n. 13. Controllo di semafori con le porte di uscita      | 130 |

| Esperimento n. 14. Tester per dispositivi logici                     | 136 |

| Esperimento n. 15. Circuiti di flag elementari                       | 142 |

| Esperimento n. 16. Convertitore analogico-digitale elementare        | 147 |

| CAPITOLO 7 — IL BUS                                                  | 157 |

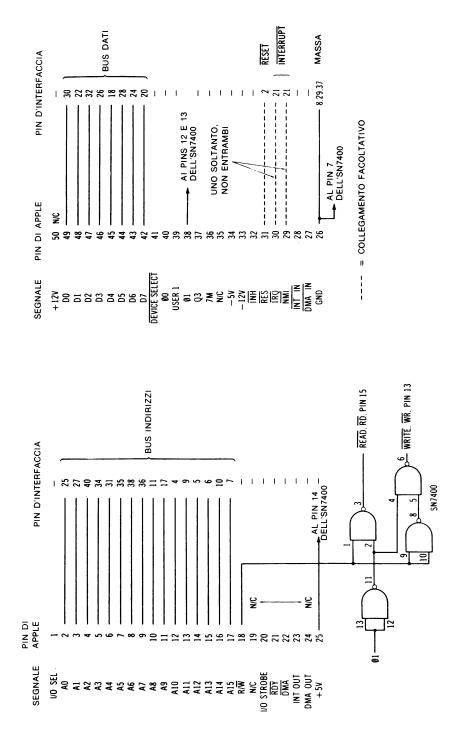

| I segnali di controllo dell'interfaccia                              | 159 |

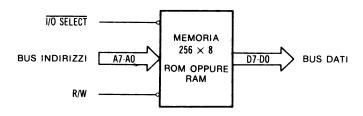

| 1/O SELECT                                                           | 159 |

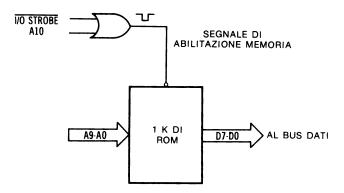

| 1/O STROBE                                                           | 161 |

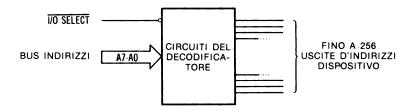

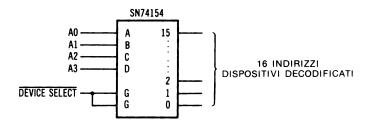

| DEVICE SELECT                                                        | 162 |

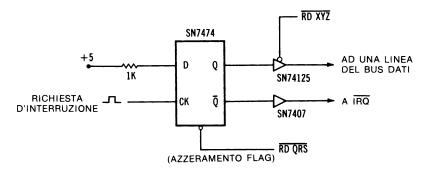

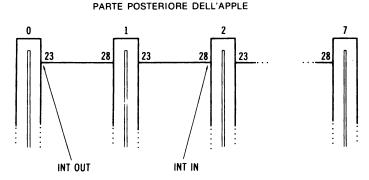

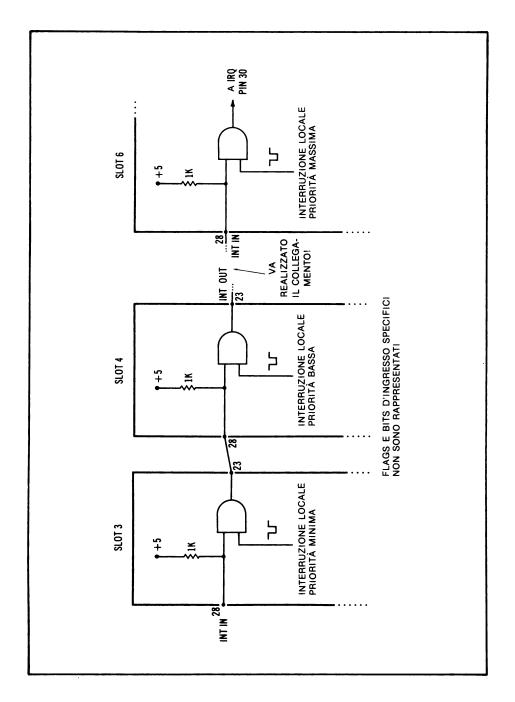

| IRQ ed NMI                                                           | 163 |

| DMA                                                                  | 166 |

| RES                                                                  | 166 |

| <del>ійн</del>                                                       | 166 |

| USER 1                                                               | 167 |

| RDY  I segnali di sincronizzazione                                                                         | 167<br>167<br>168 |

|------------------------------------------------------------------------------------------------------------|-------------------|

| Altre osservazioni                                                                                         | 169<br>169        |

| APPENDICE A — LE FUNZIONI LOGICHE                                                                          | 175               |

| APPENDICE B — COMPONENTI UTILIZZATI NEGLI ESPERIMENTI  APPENDICE C — DATI TECNICI SUL MICROPROCESSORE 6502 | -                 |

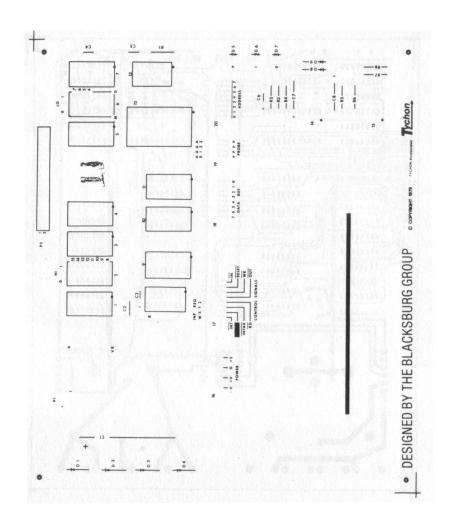

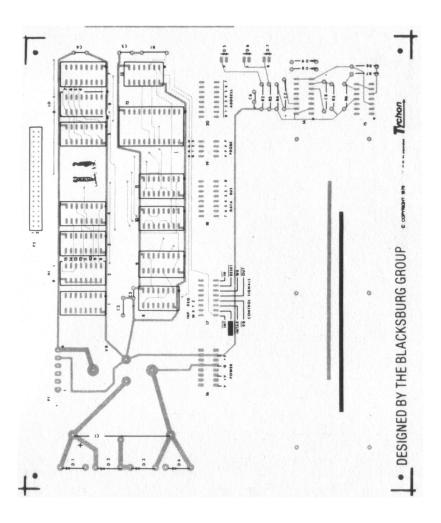

| APPENDICE D — PARTI DELLA SCHEDA DI PROVA PER L'INTERFACCIA-                                               | 101               |

| MENTO CON L'APPLE                                                                                          |                   |

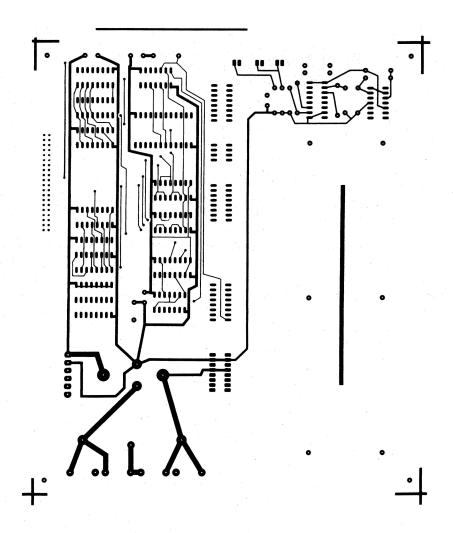

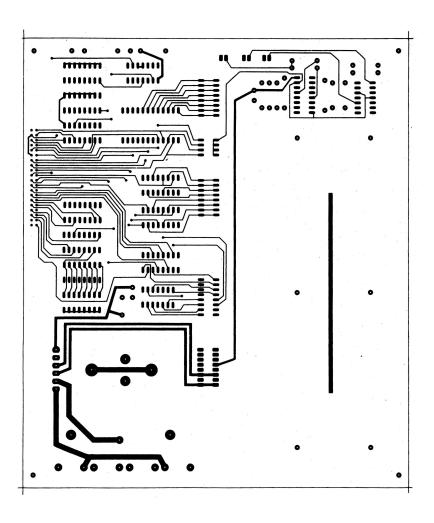

| APPENDICE E — DISEGNO DELLA SCHEDA A CIRCUITO STAMPATO                                                     | 193               |

# **PREFAZIONE**

Scopo di questo libro è farvi conoscere i segnali presenti nel calcolatore Apple II (¹) e mostrarvi come questi segnali possano essere utilizzati per controllare, mediante programmi scritti in linguaggio BASIC, dei dispositivi esterni. È stata sviluppata una scheda di prova (*breadboard*), interfacciabile con un qualunque calcolatore, allo scopo di rendere più rapida la vostra attività di progettazione e di verifica dei circuiti, in modo che possiate realizzare agevolmente i numerosi ed interessanti esperimenti che compaiono nel testo. Ricorrendo ad un metodo di progettazione come quello descritto in questo libro, potrete utilizzare il vostro tempo concentrandovi esclusivamente sui concetti esposti invece che ricercando gli errori dei vostri circuiti. Ciò non toglie che avrete ugualmente modo di costruire e provare molti circuiti digitali, come pure circuiti che utilizzano convertitori analogico-digitali e digitale-analogici.

Abbiamo optato per l'Apple II con una memoria RAM (cioè di lettura e scrittura) di 16 K e l'interprete BASIC Applesoft (²). Questo software garantisce un'elevata flessibilità, ed è notevolmente conveniente quando si usano circuiti esterni d'interfaccia. L'interprete BASIC Applesoft prevede due comandi d'uso generale con cui trasferire informazioni al e dal calcolatore. Queste istruzioni sono facilmente utilizzabili, anche senza una conoscenza particolareggiata del circuito integrato (CI) a microprocessore 6502, che costituisce il "cuore" dell'Apple.

Prima di tutto parleremo dei segnali di controllo che sono disponibili sul calcolatore Apple per l'interfacciamento, e ne illustreremo l'uso. Alcuni segnali non saranno descritti, in quanto generalmente non sono usati nei circuiti d'interfaccia, ma sono riservati a speciali schede d'interfaccia reperibili in commercio.

In secondo luogo illustreremo come l'Apple possa identificare o indirizzare dei dispositivi esterni mediante l'utilizzo di due istruzioni d'uso generale, PEEK e POKE. Questi comandi sono fondamentali per il controllo dei dispositivi esterni; pertanto ci soffermeremo abbastanza sulle loro modalità operative, e sull'uso di tutta una serie di circuiti che possono essere utilizzati per identificare specifici dispositivi d'ingresso/uscita (I/U). Si vedrà inoltre come l'Apple sia in grado di trasferire le informazioni a/da i dispositivi esterni attraverso il bus dati bidirezionale; i principali circuiti usati per le porte d'ingresso e le porte di uscita saranno descritti dettagliatamente. Presenteremo dei veri circuiti, in modo che il lettore possa in breve tempo utilizzare gli

<sup>(1)</sup> Apple e Apple II sono marchi di fabbrica registrati della Apple Computer, Inc.

<sup>(2)</sup> Applesoft è marchio di fabbrica della Apple Computer, Inc.

esempi, che sono numerosi, per progettare per conto proprio dei dispositivi d'interfaccia.

Si vedrà anche la potenza dei programmi scritti in linguaggio BASIC, e come i dati vengono elaborati all'interno del calcolatore al fine di fornire risultati significativi. Abbiamo introdotto dei semplici programmi di controllo, per mostrare come possano interagire i programmi in BASIC ed i dispositivi di I/U. Il lettore sarà messo in grado di scrivere semplici programmi di controllo e di elaborazione di dati, che potrà applicare alle porte e ai dispositivi di I/U di cui dispone.

Il calcolatore non è sempre sincronizzato con i dispositivi esterni; per questo motivo deve esistere una certa interazione fra il calcolatore stesso ed i dispositivi di I/U, affinché entrambi sappiano quando l'altro è pronto per una determinata operazione. E questo ci porta a parlare degl'indicatori (flags), e cioè di quei segnali utilizzati dal calcolatore e dai dispositivi esterni di I/U affinché le informazioni vengano trasferite secondo un certo ordine. Data l'importanza dei flags, dedicheremo loro un certo spazio, come pure ai circuiti corrispondenti usati in pratica nei dispositivi esterni. Tratteremo anche il software, perché i flags non hanno nessuna utilità se non sono rilevati da un programma di controllo.

Siamo partiti dal presupposto che chi legge conosca già sufficientemente i comandi del BASIC Applesoft. A chi prenda contatto solo adesso con il calcolatore Apple consigliamo di spendere un po' di tempo per rivedere i comandi elementari, come FOR, GOTO, IF... THEN, PRINT ed INPUT. Gli altri comandi saranno introdotti nel testo e negli esperimenti, con una spiegazione dettagliata della loro operatività. A lettura ultimata, l'uso di questi, e di altri comandi, dovrebbe essere del tutto automatico.

Nel Capitolo 6 troverete sedici esperimenti illustrati passo passo, che potrete eseguire allo scopo di suffragare i numerosi principi teorici sull'interfacciamento che sono stati sviluppati nel testo. I lettori vedranno altresì la potenza dei programmi scritti in linguaggio BASIC per il controllo dell'interfacciamento e per l'elaborazione delle informazioni trasferite a/da i dispositivi di I/U. Ci siamo sforzati d'illustrare una vasta gamma di applicazioni d'interfacciamento in qualche modo interessanti. Da questi esperimenti si vedrà che gli stessi principi di base valgono per tutti i circuiti d'interfaccia, dai più semplici ai più complessi.

Siamo coscienti della difficoltà di scrivere un libro che, come questo, sia destinato ad un pubblico estremamente differenziato sul piano delle conoscenze specifiche, un pubblico cioè che va dal principiante all'utente esperto; ed è per questo che abbiamo deciso di partire, diciamo così, a metà strada: quindi abbiamo saltato la numerazione binaria, la conversione decimale-binario, i principi fondamentali dell'elettronica digitale ed il montaggio della scheda di prova. Questi argomenti trovano ampia trattazione in altri testi, e sono probabilmente ben noti a quei lettori che si trovano a metà strada fra il principiante e l'esperto. In ogni caso abbiamo inserito qua e là dei brevi riepiloghi, proprio allo scopo di rinfrescare la memoria. Comunque in questa sede non siamo scesi eccessivamente nei particolari, ma solo quanto basta per permettere di proseguire la lettura.

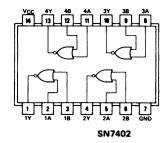

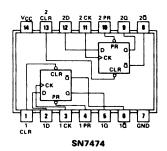

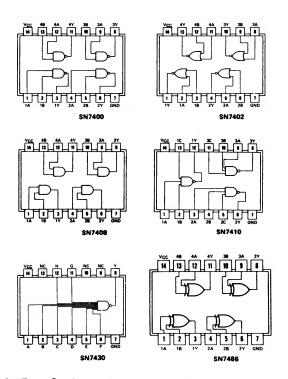

Abbiamo presupposto poi una certa familiarità con i circuiti integrati, o chips, della famiglia SN7400, come le quattro porte NOR SN7402 ed il chip a quattro latches SN7475. Saranno poi illustrati altri chips, abbastanza dettagliatamente perché il lettore possa utilizzarli così come è spiegato nel testo e negli esperimenti. A chi volesse impiegare questi dispositivi in altre applicazioni suggeriamo di richiedere ai costruttori i cataloghi relativi, che forniranno le informazioni necessarie per moltissimi usi; i cataloghi riportano inoltre tutti i cambiamenti o le modifiche eventualmente introdotti in un dispositivo "aggiornato", o in un dispositivo "migliorato" grazie a qualche caratteristica particolare.

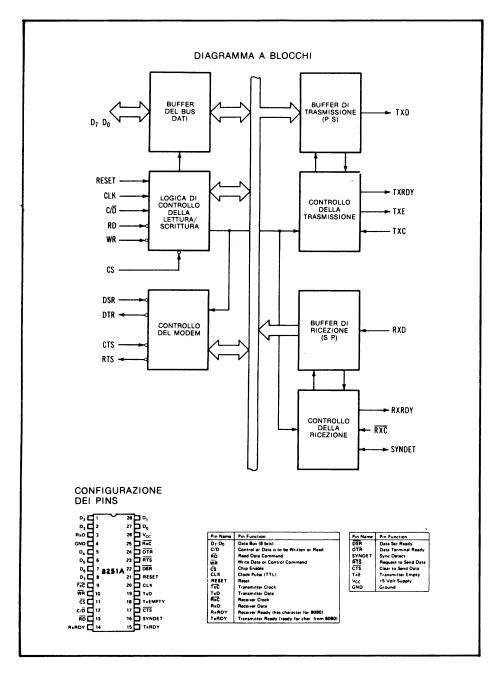

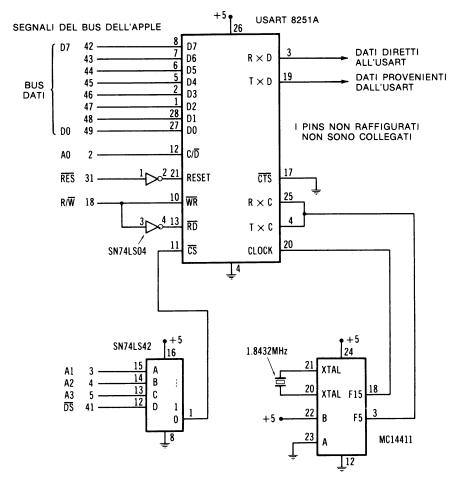

Il calcolatore Apple II ha otto connettori d'interfaccia a 50 conduttori, di uso generale. I segnali fondamentali di bus usati negli esperimenti sono derivati dai segnali relativi a tali connettori, in modo che, se qualcuno dei lettori vuol progettare e costruire per proprio conto dei circuiti d'interfaccia da inserire in uno di questi "slots", troverà che gli stessi segnali sono già pronti sui connettori. Comunque esistono anche dei segnali d'uso generale generati dall'Apple II allo scopo di facilitare il lavoro d'interfacciamento. Questi segnali, ed il modo di usarli, sono descritti dettagliatamente nel Capitolo 7. Ne parliamo per ultimi per il fatto che non sono di uso generale, ma specifici dell'Apple e, anzi, in molti casi di un particolare connettore. Per illustrarne l'uso abbiamo descritto un semplice circuito d'interfaccia per comunicazioni seriali asincrone, e abbiamo inoltre mostrato il listato del programma che lo controlla. Questo tipo d'interfaccia può servire per comunicare con altri calcolatori, stampanti seriali, modems ed altri dispositivi d'interfaccia che utilizzano per i dati il formato asincrono seriale.

Non descriviamo la programmazione fatta in linguaggio assemblatore, perché questo è un argomento specializzato che richiede un grosso bagaglio di conoscenze. Abbiamo comunque introdotto una semplice subroutine in linguaggio assemblatore, da utilizzare in più di un esperimento; l'abbiamo introdotta per un valido motivo: la funzione equivalente non è disponibile in Applesoft. Si tratta della funzione di AND logico fra bytes di 8 bits. In Applesoft l'AND logico non è altro che un'operazione che fornisce il valore "vero" o "falso", e come tale non è facilmente utilizzabile in un'operazione di AND fra bits. Oltre a ciò, la suddetta subroutine in linguaggio assemblatore fornisce un'idea del modo in cui tali routines sono accessibili da parte di un programma in BASIC. Abbiamo optato per il comando USR(X), più complicato, piuttosto che per il comando CALL, perché così imparerete qualcosa di più.

Abbiamo constatato che l'Apple ha alcuni limiti: ad esempio, manca un semplice comando di "arrotondamento" utilizzabile per arrotondare un numero ad un dato numero di cifre decimali, ad esempio 4.1986 a 4.20. Anche l'assenza di un comando di AND bit per bit è un limite, che viene superato, come si è già visto, con una routine in linguaggio assemblatore. Abbiamo poi constatato che il comando di WAIT, usato per verificare lo stato di singoli bits, pur essendo utile in potenza, "tiene in sospeso" il calcolatore se non è trovata la condizione richiesta: non incontrando la condizione, il calcolatore continua ad aspettare, e, per far riprendere l'esecuzione del programma, bisogna rimettere nello stato iniziale il calcolatore tramite il tasto RESET.

Sono disponibili una visualizzazione a colori ed una grafica gradevole; noi comunque, nel nostro sistema, ci siamo serviti di un monitor in bianco e nero.

Molti chips di uso specifico, come ad esempio i convertitori analogici, li abbiamo scelti per la loro semplicità, il costo contenuto e la facile disponibilità. Questo non vuol dire da parte nostra approvazione incondizionata per tali prodotti; aumentando il livello di sofisticazione dell'interfacciamento, troverete altri specifici dispositivi capaci di assolvere la stessa funzione, ma forse con delle caratteristiche aggiuntive, una più alta risoluzione, diverse alimentazioni, etc. Il nostro scopo è darvi degli strumenti per partire, non un repertorio di tutte le possibili interfacce al sistema Apple. Che sarebbe in ogni caso un'impresa impossibile.

A chi fosse interessato ad un ampliamento di quanto è detto in quest'opera consigliamo la lettura dei seguenti testi:

- 6502 Software Design (21656);

- Programming & Interfacing the 6502, With Experiments (21651);

- Microcomputer-Analog Converter Software and Hardware Interfacing (21540).

Si potrà leggere anche *TRS-80 Interfacing*, *Book 2*, che, pur avendo come argomento il calcolatore *TRS-80*, tratta dettagliatamente di alcuni aspetti più avanzati dell'interfacciamento, quali il pilotaggio di carichi ad alta corrente/alta tensione, le comunicazioni seriali, il controllo remoto, i convertitori analogici, il filtraggio, l'elaborazione dei dati ed altri interessanti argomenti. Noterete ben presto che le analogie fra il *TRS-80* e l'Apple sono molto maggiori delle differenze: ad esempio, i segnali di controllo ed i comandi in *BASIC* sono pressoché identici.

Tutti i testi che abbiamo citato sono disponibili presso la Howard W. Sams & Co., Inc., 4300 West 62nd Street, Indianapolis, IN 46268.

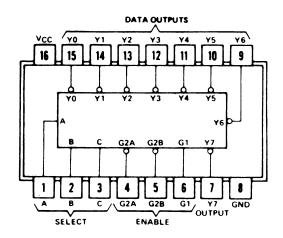

Le configurazioni dei pins che compaiono nella maggior parte delle figure, a meno di specifiche segnalazioni, ci sono state gentilmente fornite dalla Texas Instruments, Incorporated. I nomi Apple e Applesoft sono marchi di fabbrica della Apple Computer, Inc., Cupertino, CA. Il nome TRS-80 è un marchio di fabbrica registrato della Radio Shack.

Ci auguriamo che questo libro incontri la vostra approvazione, e che possa insegnarvi a progettare e costruire per conto vostro dei circuiti d'interfaccia.

Jonathan A. Titus, Christopher A. Titus, David G. Larsen "The Blacksburg Group"

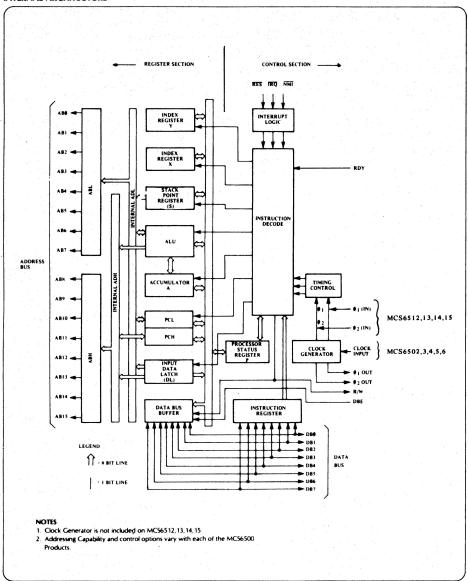

# CAPITOLO 1

# **IL PROCESSORE 6502**

II sistema Apple II® (Apple®), prodotto dalla Apple Computer, Inc., utilizza il circuito integrato a microprocessore 6502. Questo "chip" costituisce il cuore dell'unità centrale di elaborazione (CPU) del calcolatore, che è la sede dove effettivamente hanno luogo le operazioni matematiche, logiche, di decisione, e tutte le altre. Il microprocessore 6502 è prodotto dalla MOS Technology (Norristown, PA 19401), dalla Rockwell International (Anaheim, CA 92803) e dalla Synertek Corporation (Santa Clara, CA 95051).

Il 6502 è un processore ad 8 bits. Questo vuol dire che tutte le operazioni matematiche, logiche, di trasferimento di dati, d'ingresso e di uscita avvengono su otto bits binari alla volta. Chiaramente ciascun bit può essere o un uno logico o uno zero logico. Il 6502 utilizza un bus dati ad 8 bits per trasferire le informazioni fra lo stesso 6502 e le varie locazioni di memoria, e i dispositivi d'ingresso/uscita (I/U), quali tastiera, stampante, etc. Nei casi in cui il valore dell'informazione supera il limite degli otto bits, si utilizzano multipli delle parole-dato di 8 bits: ciascuna parola-dato di 8 bits prende il nome di byte.

Il massimo valore esprimibile con otto bits è 11111111<sub>2</sub>, ovvero 255<sub>10</sub>. Se, in un sistema ad 8 bits, si devono trattare valori superiori, si dovrà ricorrere ad operazioni multibyte. Generalmente, ciò significa operare sui bytes corrispondenti a due parole - dato; nel caso di parole-dato più lunghe, occorre gestire la corrispondente serie di bytes. In tal modo è possibile elaborare senza difficoltà valori elevati, superiori a 255. È comunque importante ricordare che la CPU dell'Apple è in grado di elaborare e trasferire non più di otto bits, ovvero un byte, per volta.

Il 6502 utilizza un'unica serie di otto pins per realizzare la connessione con il bus dati del calcolatore. Il bus dati serve per trasferire l'informazione al e dal calcolatore. Questo tipo di bus è detto *bidirezionale*, perché fa circolare l'informazione in due direzioni diverse. Possiamo paragonarlo ad un'autostrada, sulla quale le macchine possono viaggiare la mattina in una direzione, e la sera nella direzione opposta.

Il 6502 genera sul circuito integrato dei segnali di controllo, che vengono usati sia internamente che esternamente per controllare e gestire il flusso dell'informazione

sul bus, in una sola direzione per volta. Più avanti esamineremo il modo in cui questi segnali vengono generati ed utilizzati.

#### LA MEMORIA

Tutti i calcolatori sono dotati di memoria. La memoria generalmente serve per contenere tanto un programma destinato a controllare l'attività del calcolatore, quanto l'informazione da elaborare. In un calcolatore con il microprocessore 6502 in ciascuna locazione di memoria possono essere contenuti otto bits d'informazione, ovvero un byte di dati. La maggior parte delle memorie sono costituite da multipli di tali celle di memorizzazione da un byte, generalmente sotto forma di multipli di 1024, valore che viene detto in breve 1 K.

Le locazioni di memoria devono essere indirizzate in modo che il calcolatore sappia esattamente dove memorizzare i dati oppure dove ottenere le informazioni relative ad una data serie d'istruzioni del programma. Il microprocessore 6502 ha 16 uscite d'indirizzi, che gli consentono di specificare ciascuna delle  $2^{16}$ , ovvero 65.536, locazioni di memoria, ciascuna delle quali può contenere un byte. Questo spesso si abbrevia con 64 K, il che vuol dire che possono venir indirizzati 64 K *bytes* d'informazione. In quasi tutti i sistemi di memoria dei microcalcolatori, ogni locazione di memoria è indirizzata unicamente con un indirizzo a 16 bits.

Le linee del bus indirizzi sono indicate con sigle che vanno da A0 ad A15, corrispondenti rispettivamente al bit meno significativo (LSB) ed a quello più significativo (MSB). Tanto l'LSB quanto l'MSB possono essere sia un uno logico che uno zero logico, ma in rapporto alla posizione l'LSB ha valore zero o uno, mentre l'MSB ha valore zero o 32.768. Essendo il 6502 un processore ad 8 bits, spesso le linee degl'indirizzi sono ripartite in due gruppi di otto linee ciascuno, A7-A0 ed A15-A8. Le linee A7-A0 sono riferite alla parte bassa dell'indirizzo (LO), le linee A15-A8 alla parte alta dell'indirizzo (HI). In molti calcolatori basati sul 6502 l'indirizzo HI è detto anche indirizzo di pagina: la memoria infatti può essere divisa arbitrariamente in 256 pagine, con 256 bytes per pagina. Esamineremo gli usi del bus indirizzi più avanti, quando parleremo delle istruzioni software e quando svilupperemo i circuiti d'interfaccia. Contrariamente al bus dati, il bus indirizzi è monodirezionale, cioè l'informazione di un indirizzo fluisce in una sola direzione, dalla CPU alla memoria ed ai dispositivi esterni.

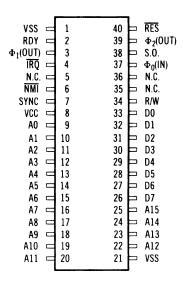

In Figura 1.1 compare la configurazione dei pins del 6502. Anche se probabilmente molti dei segnali non hanno per il momento per voi alcun senso, dovreste comunque essere in grado di riconoscere gli 8 pins d'ingresso/uscita del bus dati ed i 16 pins di uscita degl'indirizzi.

Dal momento che in questo paragrafo parliamo della memoria, aggiungiamo che nei microcalcolatori sono impiegati fondamentalmente due tipi di memoria, e cioè:

Memorie di lettura e scrittura (RAM): questo tipo di memoria serve a memorizzare i dati destinati ad essere modificati o aggiornati. Il calcolatore dev'essere in grado di collocare l'informazione in una locazione di memoria, e poi tornare a leggerla. Per lo stesso motivo nella memoria RAM sono memorizzati i programmi destinati ad essere cambiati. Il meno costoso dei calcolatori della linea Apple contiene 16.384, ovvero 16 K bytes, di memoria RAM.

2) Memorie di sola lettura (ROM): questo tipo di memoria si usa per i dati e le parti di programma destinate a restare invariate. Il programma interprete BASIC del vostro Apple risiede in chips di memoria di sola lettura, ed esattamente in 12 K di ROM.

Figura 1.1 — Configurazione dei pins del chip del microprocessore 6502.

Questi due tipi di memoria si suddividono poi a loro volta in vari sottotipi: le memorie RAM possono essere *statiche* o *dinamiche*. I chips di una memoria statica conservano i valori in essi memorizzati finquando questi non vengono modificati. Le memorie dinamiche invece devono essere continuamente "rinfrescate", mediante un hardware esterno, a intervalli di qualche millisecondo, altrimenti "dimenticano", o, in altre parole, perdono i dati memorizzati in esse. Le memorie RAM presenti nell'Apple sono dinamiche e, corredate dell'opportuna circuiteria di rinfresco, trovano posto sulla scheda a circuito stampato del calcolatore.

Esistono diversi tipi di memorie di sola lettura, generalmente tutte statiche, che differiscono nel modo in cui i valori di 8 bits vengono memorizzati nelle locazioni di memoria. I due tipi più importanti sono quello programmato a maschere e quello programmato a campi. Nelle memorie programmate a maschere i valori dei dati, i programmi, etc. vengono memorizzati nel corso delle varie fasi della costruzione:

queste memorie in genere vengono dette ROM. Invece le memorie programmate a campi richiedono una circuiteria di programmazione particolare per la memorizzazione degli uni e degli zeri logici nelle diverse locazioni. Alcune ROM programmabili a campi, o PROM, come vengono generalmente chiamate, possono venir cancellate da una luce ultravioletta di elevata intensità, e sono poi riprogrammabili. Questo è molto utile con programmi in fase di sviluppo destinati ad essere memorizzati in memorie di sola lettura: infatti non occorre sviluppare maschere e chips (che è un'operazione costosa) tutte le volte che si trova un errore nel programma o si effettua una modifica.

Ancora qualche parola sulle memorie a semiconduttore. Le memorie di lettura/scrittura (RAM) sono *volatili*, perché i dati (cioè il programma ed i valori) "si volatilizzano", ovvero scompaiono, non appena si stacca l'alimentazione dal calcolatore. Le memorie di sola lettura, invece, sono dette non volatili, perché conservano i dati e le istruzioni di un programma (l'interprete BASIC ad esempio) anche dopo che è stata tolta l'alimentazione.

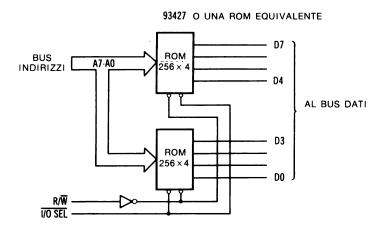

Nella maggior parte dei packages di memorie a circuito integrato, ovvero chips, non ci sono tutte le connessioni delle 16 linee d'indirizzi: i chips hanno solo le connessioni relative agl'indirizzi che bastano per indirizzare unicamente le celle di memoria contenute nel singolo chip. Quindi un chip a 64 bytes, piccolo rispetto agli standard attuali, avrà solo 6 ingressi per le linee d'indirizzo, mentre un chip di memoria di 1024 (1 K) bytes avrà 10 ingressi per le linee d'indirizzo. Chips di memoria di questo tipo dispongono di un ingresso aggiuntivo di controllo, ovvero di un ingresso di attivazione del chip (chip-enable), che consente di selezionare blocchi o gruppi di chips, uno per volta. Sono utilizzabili vari circuiti di decodifica e di selezione per costruire un blocco di memoria di 32 K partendo da chips di 64 bytes, o di 1 K byte, oppure dalla combinazione dei due tipi. Il punto più importante qui è che non è necessario collegare direttamente ai chips di memoria tutte le 16 linee d'indirizzo, anche se poi si userà una data combinazione di tutti i 16 bits d'indirizzo per selezionare univocamente un dato byte. Non ci si deve disorientare quando si prende in considerazione una memoria di 1 K 4 bits, che dispone soltanto di 10 ingressi per gl'indirizzi ed uno di attivazione del chip! Questo punto sarà comunque esaminato nei dettagli quando si parlerà dei trasferimenti di dati in ingresso/uscita.

II processore 6502 genera un segnale di controllo destinato a controllare il flusso dell'informazione lungo il bus dati. Questo segnale è indicato con READ $\overline{\text{WRITE}}$ , o, più semplicemente, con R $\overline{\text{W}}$ . Ogniqualvolta deve aver luogo un'operazione di lettura, o di scrittura, il 6502 deve specificare un indirizzo su 16 bits, che individui la "cella" di memoria che dev'essere interessata dal trasferimento. In questo caso la cella è costituita da una parola di 8 bits, vale a dire un byte.

La "sopralineatura" posta sopra una parte della notazione del segnale sta ad indicare che, quando il segnale è uno zero logico, è in corso un'operazione di scrittura, mentre, quando è nello stato logico uno, è in corso un'operazione di lettura. In tal modo un'unica linea controlla tutte le funzioni della memoria. In alcuni calcolatori e periferiche basati sul 6502, si può vedere una "separazione" del segnale, finalizzata

a fornire due segnali di controllo della memoria: lettura della memoria ( $\overline{\text{MEMR}}$  oppure  $\overline{\text{MR}}$ ) e scrittura della memoria ( $\overline{\text{MEMW}}$  oppure  $\overline{\text{MW}}$ ). In questo modo viene utilizzata qualche porta in più, e per questo in molti casi il segnale  $R/\overline{W}$  viene usato direttamente. Nel microprocessore 6502 questo segnale è disponibile sul pin 34.

Troverete anche la notazione RAM, usata in modo abbastanza diffuso per designare le memorie di lettura/scrittura. Infatti la sigla RAM sta per random-access memory (memoria ad accesso casuale): tutti gli attuali dispositivi di memorizzazione sono ad accesso casuale, nel senso che si può indirizzare una locazione, e poi un'altra locazione, senza dover scorrere in sequenza tutte le locazioni poste fra i due indirizzi.

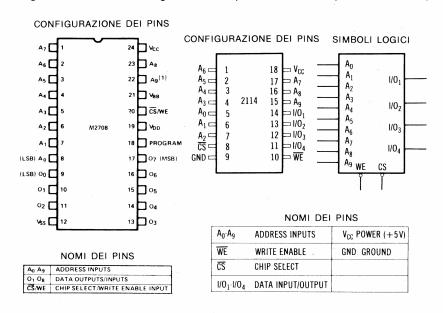

In figura 1.2 diamo le configurazioni dei pins relative a chips di memoria tipici.

Figura 1.2 — Configurazione dei pins della memoria PROM 2708 di 1 K x 8 e della memoria RAM 2114 di 1 K x 4.

Per ulteriori informazioni sulle memorie, rimandiamo a:

- Intel Memory Design Handbook, Intel Corporation, Santa Clara, CA 95051, 1975.

- The 8080A / 9080A MOS Microprocessor Handbook, Advanced Micro Devices, Inc., Sunnyvale, CA 94086, 1977.

- Mostek Memory Products Catalog, Mostek Corporation, Corollton, TX 75006, 1977.

- Bipolar and CMOS Memory Data Book, Harris Semiconductor Prod. Div., Melbourne, FL 32901, 1978.

# I DISPOSITIVI D'INGRESSO/USCITA (I/U)

La maggior parte dei sistemi basati su microcalcolatori è inutilizzabile senza dei dispositivi d'ingresso/uscita. Questi dispositivi possono essere delle periferiche standard, come lettori di schede, stampanti, visualizzatori, oppure sensori, unità di controllo, ed altri dispositivi che non si associano normalmente ad un calcolatore. L'Apple non fa eccezione: già prevede infatti il collegamento con un certo numero di dispositivi, che sono uno schermo televisivo, un registratore a cassette ed una tastiera.

Si possono poi aggiungere al calcolatore degli altri dispositivi di I/U, o progettati da voi stessi o disponibili in commercio, purché siano compatibili con l'Apple. Questi dispositivi di I/U sono assimilabili alle singole locazioni di memoria di cui si è parlato nel paragrafo precedente: i dispositivi di I/U sono collegati al bus dati, dal momento che è da essi o ad essi che i dati vengono trasferiti, e sono collegati pure con il bus indirizzi, in modo da poter essere indirizzati unicamente dal microprocessore 6502.

Un segnale di controllo, cioè READ/WRITE (o R/W), serve a sincronizzare il flusso dei dati verso e da i dispositivi di I/U. Nei calcolatori basati sul 6502 questo segnale serve anche a controllare il flusso delle informazioni verso e da i chips di memoria. Quindi nei calcolatori basati sul 6502 non c'è nessuna differenza fra gl'indirizzi di memoria e gl'indirizzi dei dispositivi di I/U. Invece nei calcolatori basati sui microprocessori 8085 o Z-80 esistono tecniche diverse per indirizzare in modo indipendente la memoria ed i dispositivi di I/U. Nel caso dell'Apple, visto che è usato un unico segnale di sincronizzazione per controllare tanto la memoria quanto i dispositivi di I/U, il processore 6502 sarà in qualunque momento o in lettura o in scrittura. Quando il segnale  $R/\overline{W}$  è un uno logico, il 6502 legge informazioni dal bus dati; quando invece è uno zero logico, il 6502 scrive dei dati su un dispositivo esterno di I/U oppure in una locazione di memoria. La "sopralineatura" posta sulla W significa semplicemente che l'operazione di scrittura ha luogo quando il segnale  $R/\overline{W}$  è uno zero logico. Vi capiterà certamente d'incontrare altri nomi di segnali con una sopralineatura: vorrà ancora dire semplicemente che quei segnali sono attivi nello stato logico zero.

Intendendo ora concentrare il discorso sull'uso dei dispositivi di I/U con l'Apple, rimandiamo gran parte della trattazione specifica ai prossimi paragrafi.

# Riepilogo

A questo punto dovrebbe esservi ormai chiaro che il 6502 effettua i trasferimenti e le operazioni su otto bits di dato per volta. Calcoli ed operazioni complessi spesso richiedono più gruppi di 8 bits, cioè di bytes. I bytes vengono trasferiti verso la e dalla CPU del 6502 attraverso un bus di 8 bits.

II 6502 utilizza un bus indirizzi a 16 bits per indirizzare le singole locazioni di memoria ed i dispositivi di I/U. Spesso il bus indirizzi è suddiviso in un bus d'indirizzi HI ed uno d'indirizzi LO, di otto bits ciascuno. Il singolo segnale di controllo  $R/\overline{W}$  controlla il flusso delle informazioni verso la e dalla CPU del 6502. In Tabella 1.1 compaiono i segnali e le loro denominazioni.

| Bus dati                | D7-D0  | Serie di linee bidirezionali ad 8 bits per tra-<br>sferire informazioni fra la CPU ed i dispositi-<br>vi di I/U. |

|-------------------------|--------|------------------------------------------------------------------------------------------------------------------|

| Bus indirizzi           | A15-A0 | Bus indirizzi monodirezionale a 16 bits per<br>indirizzare sia la memoria, sia i dispositivi di<br>I/U.          |

|                         | A15-A8 | Bus degl'indirizzi HI, cioè gli otto bits d'indi-<br>rizzi più significativi.                                    |

|                         | A7-A0  | Bus degl'indirizzi LO, cioè gli otto bits d'indi-<br>rizzi meno significativi.                                   |

| Segnale<br>di controllo | R/W    | Segnale di controllo della lettura/scrittura.                                                                    |

N.B.: La notazione con la "sopralineatura" (W) indica che lo zero logico è lo stato "attivó", lo stato cioè che fa si che l'azione corrispondente si verifichi.

Nel caso dei segnali numerati, il numero cresce in funzione del peso dei bits: ad esempio, A15 è il bit d'indirizzo più significativo (MSB).

Tabella 1.1 - Segnali di controllo usati per l'interfacciamento.

# LE ISTRUZIONI SOFTWARE PER IL CONTROLLO DELL'I/U

#### I comandi di I/U

Il calcolatore Apple prevede un certo numero d'istruzioni per il controllo dei dispositivi di I/U. Per lo più, comunque, queste istruzioni sono usate per controllare specifici dispositivi di I/U, o per svolgere funzioni specifiche. Per quanto probabilmente non abbiate realizzato ancora nulla, già conoscete abbastanza alcune, se non tutte, queste istruzioni. Comunque, per rinfrescarvi la memoria, abbiamo introdotto degli esempi particolari su queste istruzioni.

Probabilmente conoscete i comandi di INPUT e di PRINT. Il comando di INPUT fa sì che il programma in BASIC si arresti, e aspetti che vengano introdotti dei dati da tastiera. Il comando di PRINT fa "stampare" sullo schermo TV una risposta, o una stringa di caratteri.

ESEMPIO 1.1 - Semplice programma di I/U

10 INPUT "IL VALORE DI X ="; X

20 PRINT "IL VALORE INTRODOTTO ERA": X

Se si esegue il programma dell'Esempio 1.1, il valore associato alla variabile X dovrà venir introdotto nel calcolatore prima che il programma passi il controllo all'istruzione (statement) 20. Questi due tipi d'istruzioni d'ingresso/uscita si usano spesso allo scopo di permettere all'operatore d'introdurre un valore, e vederlo visualizzato. Per i comandi sia di INPUT che di PRINT esistono diverse varianti, ma l'esempio visto serve ad illustrare l'essenziale: certamente avrete già usato senza difficoltà le operazioni di I/U in programmi in BASIC.

È anche possibile che siate già al corrente dell'esistenza, in BASIC, di comandi di I/U di *visualizzazione grafica*: e cioè, ad esempio, HOME, PLOT X,Y e SCRN(X,Y). Il comando di HOME pulisce lo schermo e posiziona il cursore lampeggiante alla posizione di riposo, nell'angolo in alto a sinistra dello schermo TV. I comandi di PLOT e di SCRN richiedono l'impiego di "coordinate", indicanti dove un'operazione deve avvenire.

L'Esempio 1.2 mostra come dei semplici comandi di visualizzazione grafica vengano utilizzati in un breve programma. Il programma visualizza sullo schermo TV dei punti colorati, cangianti in modo casuale. Se si utilizza uno schermo TV in bianco e nero (b/n), i punti saranno di varie tonalità di grigio.

ESEMPIO 1.2 — Generatore di una combinazione casuale di colori mediante i comandi di I/U

```

10 GR

20 X = INT(40*RND(1)) + 1

30 Y = INT(40*RND(1)) + 1

40 COLOR = INT(15*RND(1)) + 1

50 PLOT X,Y

60 GOTO 20

```

Esistono poi altri due comandi, che forse non avete considerato come comandi di I/U: si tratta dei comandi di LOAD e di SAVE, che si usano per leggere e memorizzare programmi su cassetta. Entrambi fanno sì che abbia luogo una serie prefissata di operazioni di controllo del registratore a cassette. L'uso di questi comandi è immediato, per cui non ne diamo nessun esempio.

I rimanenti comandi di I/U sono costituiti dalle operazioni di IN # X e di PR # X, che sono associate a dispositivi di I/U particolari, coi quali si possono sostituire la tastiera e lo schermo TV. È importante non dimenticare che queste istruzioni di I/U sono proprie dell'Apple e del suo programma interprete in BASIC: saranno infatti prive di senso per altri calcolatori basati sul 6502, a meno che utilizzino il programma BASIC dell'Apple. Per di più, ogni istruzione è specificamente riferita ad un particolare dispositivo di I/U: ad esempio, il comando di HOME non avrà nessun effetto sul registratore a cassette, e su nessun altro dispositivo di I/U. Analogamente, il comando di INPUT controlla solo l'ingresso dei valori introdotti mediante la tastiera della console.

#### I comandi di I/U d'uso generale

Sebbene nel programma interprete di BASIC Integer dell'Apple esistano diversi comandi di I/U d'uso generale, abbiamo deciso, per questo libro, di usare il programma interprete di BASIC Applesoft, a nostro parere più flessibile. Chi volesse adattare il proprio Apple a questo programma potrà richiedere l'assistenza di un rivenditore di calcolatori Apple.

I due comandi per i dispositivi di I/U sono PEEK e POKE: POKE trasferisce i dati dal calcolatore ad un dispositivo esterno, PEEK da un dispositivo esterno al calcolatore. Per queste istruzioni esiste un formato specifico, che bisogna rispettare se si vuole che le istruzioni operino nel modo esatto.

Per i dispositivi d'ingresso e di uscita useremo il termine *porte*; quindi un dispositivo di uscita sarà una *porta di uscita*, un dispositivo d'ingresso sarà una *porta d'ingresso*. Questa è la terminologia standard in uso nell'industria dei microcalcolatori.

L'istruzione di uscita, POKE, deve specificare l'*indirizzo* del dispositivo di I/U interessato dal trasferimento di dati, ed il valore che dev'essere trasferito al dispositivo indirizzato. Il formato effettivo dell'istruzione di POKE è POKE x, y, dove il valore x rappresenta l'indirizzo decimale del dispositivo di uscita che deve ricevere il valore del dato, che è y. Anche il dato y dev'essere espresso da un numero decimale. Dal momento che il microprocessore 6502 può indirizzare 65536 locazioni di memoria, l'indirizzo dev'essere compreso fra 0 e 65535 incluso. Il valore del dato dev'essere compreso fra 0 e 255 incluso, perché il calcolatore utilizza un bus dati di 8 bits per tutti i trasferimenti, ed il numero massimo che può venir trasferito attraverso tale bus è appunto 255.

Così, ad esempio, nell'istruzione POKE 12684,215 il valore 215 è inviato alla porta di uscita 12684.

L'istruzione d'ingresso, PEEK, è analoga all'istruzione di POKE, solo che nel comando non compaiono valori di dati. Dal momento che c'interessa determinare il valore presente in uno specifico dispositivo d'ingresso, viene specificato soltanto l'indirizzo decimale di quel dispositivo d'ingresso: scriveremo quindi PEEK (x), ove x è l'indirizzo decimale del dispositivo d'ingresso.

Serve a ben poco introdurre un valore senza usarlo per qualcosa; perciò il comando d'ingresso è sempre inserito in uno statement completo, e non costituisce uno statement a sé: ad esempio,

Q = PEEK(34579)

Qui alla variabile Q è assegnato il valore decimale che è stato introdotto dal dispositivo 34579.

Importante: non dimenticate di mettere fra parentesi l'indirizzo del dispositivo d'ingresso.

Con il comando di PEEK, il valore introdotto dev'essere compreso fra 0 e 255 incluso, sempre per le limitazioni imposte dal trasferimento su 8 bits.

| POKE 45124,98 | L = PEEK(23109) |

|---------------|-----------------|

| POKE N,120    | L = PEEK(Q)     |

| POKE 45124,X  |                 |

| POKE X, M     |                 |

Tabella 1.2 - Comandi d'ingresso (PEEK) e di uscita (POKE) corretti.

Nei comandi d'ingresso e di uscita possono essere specificate delle variabili, invece di valori particolari, per indicare gl'indirizzi delle porte, ed i valori dei dati relativamente al comando di POKE. Quindi tutti i comandi di PEEK e di POKE che compaiono nella Tabella 1.2 sono leciti. È chiaro che abbiamo presupposto che i valori delle variabili N, M, X e Q siano già stati specificati in un punto del programma precedente all'esecuzione delle istruzioni riportate nella Tabella 1.2.

I comandi d'ingresso e di uscita in cui i valori degl'indirizzi superino 65535 genereranno da parte dell'Apple il messaggio ILLEGAL QUANTITY ERROR (cioè ERRO-RE PER QUANTITA' NON LECITA). Il medesimo messaggio viene generato se si cerca d'inviare in uscita un valore relativo ad un dato numerico superiore a 255.

Abbiamo dato qualche esempio d'uso dei comandi di PEEK e di POKE. Ma, anche se i programmi dell'Esempio 1.3 sono eseguibili, non faranno nulla di utile, visto che per il momento al vostro calcolatore non è collegata nessuna porta esterna di I/U.

ESEMPIO 1.3 — Semplici programmi di I/U con comandi di PEEK e di POKE

```

10 INPUT "PORTA DI USCITA # ="; P

```

- 20 INPUT "VALORE USCITO"; V

- 30 POKE P,V

- 40 GOTO 10

- 10 INPUT "PORTA DI INGRESSO # ="; M

- 20 PRINT "VALORE INTRODOTTO ="; PEEK(M)

- 30 GOTO 10

Dal momento che i calcolatori basati sul 6502 non sono in grado di distinguere fra le locazioni di memoria utilizzate per la memorizzazione temporanea di programmi e dati, e quelle utilizzate per le porte di I/U, spesso le istruzioni di PEEK e di POKE vengono usate per esaminare e modificare il contenuto di svariate locazioni di memoria dell'Apple. Se, con un'operazione di POKE, introducete delle informazioni nella memoria di lettura/scrittura in maniera indiscriminata, vi può capitare di "scrivere sopra" parti importanti del vostro programma, oppure su informazioni che sono state temporaneamente memorizzate dall'interprete BASIC. Ne deriva una "catastrofe" per il calcolatore, per cui i vostri programmi e dati andranno persi o saranno alterati in modo significativo. Certo non è opportuno scrivere a caso informazioni a diversi indirizzi mediante il comando di POKE, senza specifiche direttive. È chiaro che si può usare il comando di PEEK per esaminare il contenuto di una locazione di me-

moria ogni volta che si vuole, perché questo comando non altera il contenuto della locazione di memoria esaminata.

Da quanto si è detto a proposito dei dispositivi di memoria, avrete certamente capito che l'operazione di POKE non ha nessun effetto sulle memorie di sola lettura (ROM) dell'Apple.

#### Le mappe di memoria

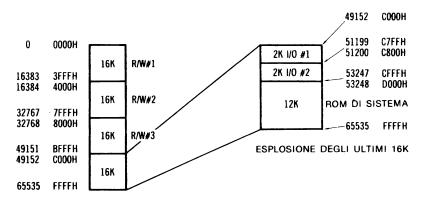

A questo punto è opportuno parlare brevemente delle "mappe" degl'indirizzi di memoria usati dall'Apple. In Figura 1.3 è rappresentata la mappa completa della memoria di 64 K. Per comodità gl'indirizzi di memoria sono riportati sia in notazione decimale (in base 10), sia in notazione esadecimale (in base 16). I numeri esadecimali hanno il suffisso H, per distinguerli dai numeri decimali.

Figura 1.3 - Mappa della memoria di 64 K del calcolatore Apple.

Nell'Apple lo spazio di memoria è diviso in blocchi di 16 K. Tre di questi blocchi sono riservati alla memoria RAM, e nella maggior parte degli Apple il primo blocco di RAM è "occupato" dai chips di memoria di lettura/scrittura. Gli altri blocchi di RAM possono essere utilizzati per espansioni future della memoria RAM eventualmente richieste da applicazioni particolari. Abbiamo verificato che nella maggior parte dei casi bastano 16 K di memoria RAM. Molti fornitori offrono kits di chips di memoria supplementare, e certamente la maggior parte degli utenti di Apple non avrà eccessive difficoltà a corredare il proprio sistema di ulteriori chips di memoria.

L'ultimo blocco di memoria di 16 K è riservato all'indirizzamento tanto della ROM quanto delle porte di I/U. 12 dei 16 K del blocco sono occupati dalle ROM di sistema dell'Apple, e comprendono l'interprete BASIC ed i programmi di monitor. I restanti 4 K sono suddivisi a loro volta in due spazi di 2 K ciascuno, l'uno per l'indirizzamento dell'I/U, l'altro per espansioni future dell'Apple. Il blocco di I/U, con indirizzi che vanno da C000H a C7FFH incluso, è uno dei più importanti ai fini dell'interfacciamento, in quanto specificatamente riservato a questo scopo, e non utilizzabile, nel-l'Apple, per nessun altro scopo. Alcuni indirizzi di questo blocco di 2 K sono utilizzati

dall'Apple per controllare ad esempio l'altoparlante, la tastiera ed il registratore a cassette. Le effettive assegnazioni d'indirizzo sono riportate nella Tabella 1.3. Per un discorso particolareggiato sull'utilizzo pratico di questi indirizzi di I/U rimandiamo al BASIC Programming Reference Manual ed all'Apple II Reference Manual, che vengono forniti insieme con l'Apple II, ma possono anche venire richiesti direttamente alla Apple Computer, Inc., 10260 Bandley Dr., Cupertino, CA 95014.

L'ultimo blocco di memoria di 2 K, C800H-CFFFH, è riservato alle espansioni future. Potete usare questo spazio per un'ulteriore memoria di sola lettura, nel caso di programmi lunghi che si desidera avere subito disponibili.

|                                | Indirizzo   |             |  |  |  |

|--------------------------------|-------------|-------------|--|--|--|

| Funzione                       | Decimale*   | Esadecimale |  |  |  |

| Dato da tastiera               | 49152       | C000        |  |  |  |

| Strobe di azzeramento tastiera | 49168       | C010        |  |  |  |

| Altoparlante                   | 49200       | C030        |  |  |  |

| Uscita di cassetta             | 49184       | C020        |  |  |  |

| Ingresso di cassetta           | 49256       | C060        |  |  |  |

| Ingressi di flag               | 49249-49251 | C061-C063   |  |  |  |

| Ingressi analogici             | 49252-49255 | C064-C067   |  |  |  |

| Azzeramento analogico          | 49264       | C070        |  |  |  |

| Strobe di utilità              | 49216       | C040        |  |  |  |

Diamo soltanto indirizzi positivi. Per calcolare gl'indirizzi negativi, sommare —65536 agl'indirizzi decimali riportati.

Tabella 1.3 – Indirizzi di I/U dell'Apple e loro uso.

Nei prossimi capitoli descriveremo in dettaglio l'uso concreto degl'indirizzi di I/U. Per ora è sufficiente sapere che uno specifico gruppo d'indirizzi di memoria è riservato alle vostre applicazioni particolari. Un'altra cosa da tener presente è che la mappa di memoria rappresentata in Figura 1.3 è propria del calcolatore Apple. Gli altri calcolatori basati sul 6502 potranno avere mappe di memoria diverse, nelle quali la memoria RAM, la memoria di sola lettura e gl'indirizzi dei dispositivi di I/U saranno collocati in aree differenti della mappa.

#### I comandi software ed i circuiti d'interfaccia

A questo punto avrete certamente capito che le istruzioni di PEEK e di POKE determinano il verificarsi di certe azioni, relative ai dispositivi di I/U ed alle locazioni di memoria, come diretto risultato del loro utilizzo. Istruzioni come A = 1.359 faranno sì che determinati valori siano memorizzati, ma non sappiamo quali locazioni di memoria l'Apple ha assegnato alla variabile "A", né in che modo il valore 1.359 è stato memorizzato. Le istruzioni di PEEK e di POKE determinano il verificarsi di una se-

quenza nota e ben definita di operazioni: trasferimento di bytes di dati, generazione di segnali di controllo, e trasferimento d'informazioni d'indirizzi sulle linee del bus indirizzi. Queste azioni, ben definite e riproducibili, ci permettono di utilizzare tali comandi per controllare i dispositivi di I/U. Vedremo ora quali azioni sono determinate da ciascuno di questi comandi software.

Le istruzioni di PEEK e di POKE operano in modo molto simile. Entrambe specificano un indirizzo che richiede 16 bits d'informazione. Durante la loro esecuzione l'informazione d'indirizzo contenuta nel comando viene trasferita ai dispositivi esterni attraverso le linee del bus indirizzi A15-A0. Così l'indirizzo del dispositivo di I/U è disponibile per tutti i dispositivi ed i circuiti connessi con queste linee d'indirizzi, cioè sia per la memoria, sia per i dispositivi di I/U.

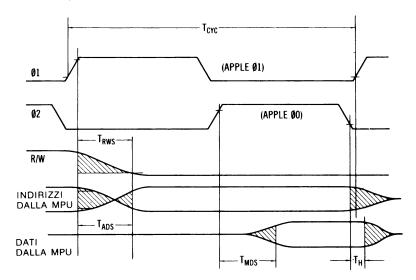

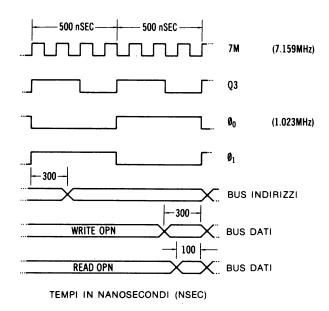

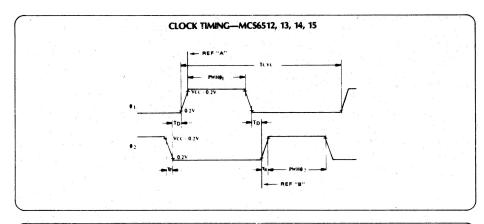

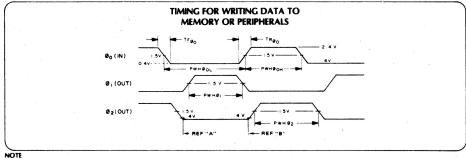

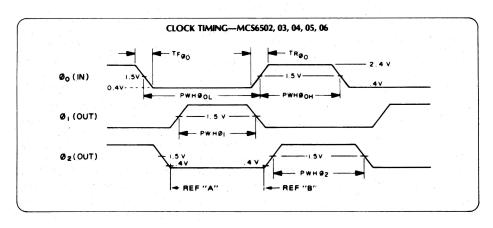

Quando in un programma si usa un'istruzione di POKE, anche il valore del dato viene fatto uscire dal chip del 6502, ma lungo le linee del bus dati D7-D0. Una volta che i bits dei dati ed i bits degl'indirizzi sono "stabili", ossia presenti sui loro rispettivi bus in una forma utilizzabile, il 6502 manda il segnale READ/WRITE sul bus di controllo: questo segnale sincronizza l'acquisizione del dato da parte del dispositivo di I/U che è stato indirizzato. Naturalmente è necessaria una circuiteria esterna che "catturi" il dato, identifichi il dispositivo di I/U selezionato e lo sincronizzi con il sistema basato sul 6502. In Figura 1.4 è rappresentato il diagramma di temporizzazione di questi segnali, così come si configurano in un sistema con 6502, in questo caso l'Apple. Ovviamente il comando di POKE implica molte istruzioni in linguaggio assemblatore, ed il diagramma di temporizzazione mostra soltanto quel che accade durante l'effettivo trasferimento dei dati. E fin qui abbiamo visto solo quel che il 6502 fa durante un'operazione di POKE.

Figura 1.4 — Relazioni fra i segnali durante un'operazione di scrittura (v. Appendice C).

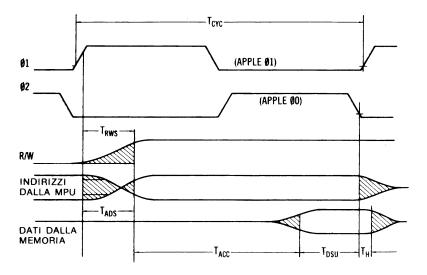

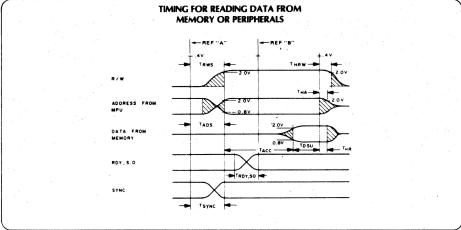

Quando viene eseguita un'istruzione di PEEK, i dati non compaiono in essa, ma vengono acquisiti da un dispositivo esterno di I/U: l'unico ad essere specificato è l'indirizzo. Al momento dell'esecuzione dell'istruzione di PEEK, l'indirizzo di 16 bits viene collocato sulle linee del bus indirizzi. Quando l'informazione d'indirizzo è presente, il dispositivo di I/U corrispondente collocherà il proprio dato sul bus dati, in modo che possa essere acquisito dal processore 6502. In un'operazione di lettura, il segnale  $R/\overline{W}$  proveniente dal 6502 è un uno logico. In questo caso sono anche richiesti degli ulteriori circuiti per la selezione del dispositivo di I/U e per condizionare l'invio dei propri dati sul bus dati. In Figura 1.5 compare un tipico diagramma di temporizzazione relativo al comando di PEEK.

Figura 1.5 — Relazioni fra i segnali durante un'operazione di lettura (v. Appendice C).

Fra poco descriveremo brevemente alcuni dei circuiti usati per le porte d'ingresso e di uscita. Certamente avrete capito che, anche se abbiamo descritto le *porte di I/U* come qualcosa che può tanto ricevere dati uscenti dal microcalcolatore, quanto trasmettere dati che vengono poi acquisiti dal microcalcolatore, alcuni *dispositivi di I/U* possono di fatto contenere un certo numero di porte di I/U particolari. Le unità di controllo, i dispositivi per la memorizzazione di dati (dischi, cassette), i convertitori analogici ed altri dispositivi di I/U possono avere un certo numero di porte di I/U, perché possono richiedere più di 8 bits d'informazione da parte del calcolatore, e possono anche aver bisogno di trasferire al calcolatore più di 8 bits d'informazione. In ogni caso, i trasferimenti di dati costituiti da più di 8 bits implicano sempre il trasferimento di più bytes verso/da il calcolatore, e porte di I/U di 8 bits particolari. Non dimenticate mai che *l'informazione* è sempre trasferita ad 8 bits per volta.

#### I comandi software. Trasferimento e controllo dei dati

Per lo più i comandi di PEEK e di POKE si usano per trasferire valori di dati di 8 bits fra i dispositivi di I/U o le locazioni di memoria ed il calcolatore 6502. Come si è già detto, alcuni trasferimenti di dati richiederanno più di 8 bits d'informazione, e allora saranno trasferiti più bytes, uno alla volta.

Ci sono anche dei casi in cui il *valore* reale del dato trasmesso non è significativo. I bits possono essere usati per rappresentare particolari condizioni a due stati, che non sono in rapporto con i valori posizionali dei bits. Ad esempio, l'Apple può essere collegato ad un certo numero di sensori indicanti condizioni come serbatoio vuoto o pieno, riscaldamento acceso o spento, valvola aperta o chiusa, e così via. Si potrà usare un comando di PEEK per introdurre lo stato di questi bits indicatori mediante una porta d'ingresso ad 8 bits. Allora il valore letto da questa porta d'ingresso potrà essere 100<sub>10</sub>, ma, dato che la porta *rileva* otto singoli stati di aperto o chiuso (cioè uno logico o zero logico), il valore 100<sub>10</sub> non è significativo: ciascun bit binario rappresenta lo stato di un singolo sensore. In questo caso

$$100_{10} = 01100100_2$$

Ciò vuol dire che tre sensori si trovano nello stato logico 1, e cinque nello stato logico zero.

I comandi di POKE e di PEEK si possono usare anche, in modo analogo, per attivare o disattivare un dispositivo, sulla base dello stato dei singoli bits rilevati in un altro punto del programma di controllo. Infatti molti degl'indirizzi di I/U usati nell'Apple sono associati a semplici dispositivi caratterizzati da un funzionamento di "aperto/chiuso", come gli altoparlanti. Quindi il semplice comando

$$A = PEEK(49200)$$

genererà un "blip" da parte dell'altoparlante dell'Apple. Capite bene che la variabile A è una variabile "fittizia", e che il suo valore finale non ha importanza, perché l'effetto di questo semplice statement BASIC è quello d'inviare all'altoparlante un impulso. Il comando di controllo dell'altoparlante può essere inserito in un ciclo, ottenendo così un debole ronzio da parte dell'altoparlante: v. Esempio 1.4.

ESEMPIO 1.4 - Semplice programma di controllo dell'altoparlante

10 A = PEEK(49200) 20 GOTO 10

Qui la cosa più importante da ricordare è che le istruzioni di PEEK e di POKE non si limitano semplicemente a controllare il trasferimento d'informazioni sul bus dati, ma si possono usare anche per funzioni di controllo specifiche, come l'invio d'impulsi ad un contatore, l'attivazione di una pompa, o l'inclinazione di un collettore solare.

#### Linguaggio assemblatore e BASIC

I programmi in linguaggio BASIC che voi scrivete sul vostro Apple hanno ben poco a che vedere con le istruzioni che il microprocessore 6502 è effettivamente in grado di eseguire. Ciascuno statement e comando del BASIC viene *interpretato* dall'*interprete* BASIC residente nel calcolatore Apple. Anche il manuale di programmazione del microprocessore 6502 avrà ben poco a che vedere con il manuale software dell'Apple: i comandi infatti sono molti diversi.

Il 6502 non ha un comando di PRINT, per cui non è in grado di eseguire l'operazione seguente:

#### PRINT "QUESTO SEMBRA UNO SCHERZO"

L'interprete BASIC stabilisce che deve aver luogo un'operazione di PRINT, e poi esegue una serie d'istruzioni di un programma in linguaggio assemblatore, che provvedono a collocare nella memoria associata allo schermo i codici dei caratteri alfabetici che formano le parole "QUESTO SEMBRA UNO SCHERZO". Le istruzioni del linguaggio assemblatore sono costituite da uni e zeri logici, che determinano il verificarsi delle operazioni del 6502, interne ed esterne, necessarie per il trasferimento della parte messaggio del comando di PRINT alla memoria associata allo schermo.

Anche se in tutto il libro non programmeremo mai in linguaggio assemblatore, è necessario sapere che è il linguaggio "base" del calcolatore quello che fa funzionare l'Apple così come funziona.

I comandi di PEEK e di POKE determinano l'esecuzione di moltissimi comandi in linguaggio assemblatore, al fine di ottenere come risultato il trasferimento dei dati. Visto che queste istruzioni in linguaggio BASIC devono essere interpretate, anche quando vengono usate l'una subito dopo l'altra, o all'interno di un ciclo, il processo software d'interpretazione sarà necessariamente lento. Nell'Esempio 1.5 presentiamo due programmi, entrambi di controllo dell'altoparlante dell'Apple; le due sequenze fanno la stessa cosa, e cioè generano un suono dell'altoparlante. Solo ascoltando le differenze fra i due suoni prodotti potrete apprezzare la diversa velocità di esecuzione dei due programmi.

ESEMPIO 1.5 — Confronto fra due programmi di controllo dell'altoparlante, l'uno in linguaggio assemblatore, l'altro in BASIC

| Programma in BASIC |                 | Programma in linguaggio assemblatore |            |  |

|--------------------|-----------------|--------------------------------------|------------|--|

| 10                 | A = PEEK(49200) | GO                                   | LDY # \$C0 |  |

| 20                 | GOTO 10         | LOOP                                 | LDA # \$0C |  |

|                    |                 |                                      | JSR WAIT   |  |

|                    |                 |                                      | LDA SPKR   |  |

|                    |                 |                                      | DEY        |  |

|                    |                 |                                      | BNE LOOP   |  |

|                    |                 |                                      | JMP GO     |  |

Il programma in linguaggio assemblatore genera un suono gradevole e uniforme, quello in BASIC invece un debole brontolio. Il programma in linguaggio assemblatore è simile a quello impiegato dal programma Monitor dell'Apple, ed inoltre usa la subroutine interna WAIT per produrre un ritardo.

In certi casi i programmi in linguaggio assemblatore sono più convenienti dei programmi in BASIC in una proporzione di *cinquecento contro uno*; i programmi in BASIC d'altra parte sono indubbiamente più facili da scrivere e mettere a punto. Generalmente la programmazione in linguaggio assemblatore non è consigliabile per i principianti.

Noi ci occuperemo molto poco di programmazione in linguaggio assemblatore, essendo il nostro discorso incentrato sulla programmazione in linguaggio BASIC. Per ulteriori informazioni sulla programmazione in linguaggio assemblatore con il 6502, consigliamo la lettura di 6502 Software Design, e di Programming & Interfacing the 6502, With Experiments, entrambi della Howard W. Sams & Co., Inc., Indianapolis, IN 46268.

#### Numerazione binaria e numerazione decimale

Il calcolatore Apple accetta, elabora e stampa numeri decimali (cioè in base 10). Questo fatto lo rende compatibile con il metodo di numerazione usato normalmente dalla gente, per la quale sarebbe complicato capire e convertire rapidamente valori di dati stampati in un formato diverso dal decimale. Le linee dei dati e degl'indirizzi sono collegate direttamente con il microprocessore 6502, per cui i dati relativi sono binari, avendo due soli stati: uno logico e zero logico. Quindi dobbiamo renderci conto che, quando specifichiamo l'indirizzo di una porta di I/U in un comando di PEEK o di POKE, l'indirizzo (0-65535) comparirà sul bus indirizzi nella sua forma binaria (000000000000000011111111111111111). Allora dovremmo essere capaci di eseguire nei due sensi la conversione decimale-binario!

Allo stesso modo, anche i valori dei dati trasferiti al e dal calcolatore tramite i comandi di PEEK e di POKE vengono indicati ed acquisiti sotto forma di valori binari di 8 bits, perché il bus dati ha una "larghezza" di soli 8 bits. Il bus dati da 8 bits dipende dalla capacità di elaborazione dei dati propria del 6502, non dall'Apple. Quindi dobbiamo limitarci a trasferire solo dati di 8 bits. È una grossa limitazione? In genere no. Infatti, malgrado ciò, l'Apple è in grado di elaborare grosse quantità d'informazioni, e, come si vedrà più avanti, questo fatto rende facile l'interfacciamento con i dispositivi di I/U.

Prima di chiudere il capitolo è necessaria un'ultima osservazione sugl'indirizzi. L'interprete BASIC del calcolatore Apple è stato concepito in modo che possa lavorare su indirizzi sia negativi che positivi. Questo non vuol dire che nel calcolatore ci siano realmente degl'indirizzi negativi! Riuscireste ad immaginare dei numeri civici negativi? I numeri negativi sono dovuti semplicemente al modo in cui nell'Apple sono memorizzati gli equivalenti binari degl'indirizzi. Così l'indirizzo 49200, relativo all'altoparlante, è equivalente a —16336. Per evitare confusioni, consigliamo decisamente di usare indirizzi positivi. Potrete attuare facilmente la conversione fra indiriz-

zi negativi e positivi semplicemente sommando 65536 ad un indirizzo negativo per ottenere il positivo equivalente, e sottraendo 65536 dall'indirizzo positivo per ottenere l'equivalente negativo. Entrambi gl'indirizzi, 49200 e —16336, generano lo stesso indirizzo di 16 bits, ma pensiamo che converrete sul fatto che gl'indirizzi negativi possono sembrare alquanto astratti e sconcertanti.

#### CAPITOLO 2

# L'INTERFACCIAMENTO DELL'APPLE

A questo punto probabilmente vi porrete delle domande, e cioè:

- Come, concretamente, l'Apple trasferisce le informazioni ai dispositivi di I/U?

- Come, concretamente, i dispositivi di I/U si sincronizzano con le operazioni del calcolatore?

- Come vengono selezionati, e identificati, i singoli dispositivi di I/U?

- Come i dispositivi di I/U collocano i loro dati sul bus dati, e come li ricevono dal bus dati?

Si tratta di domande fondamentali, perché le risposte a questi quesiti vi forniranno le basi per capire in che cosa consista l'interfacciamento con un microcalcolatore. A queste domande risponderemo in questo e negli altri capitoli. Introdurremo inoltre degli esperimenti, che daranno corpo ai principi teorici in forma sperimentale.

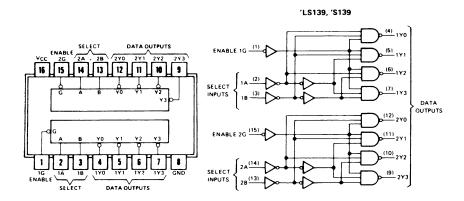

In questo capitolo daremo qualche esempio di circuiti digitali. Abbiamo dato per scontato che sappiate "leggere" ed interpretare lo schema di un circuito logico, e che conosciate i più comuni circuiti in logica TTL (transistor-transistor logic) della serie SN7400.

# DECODIFICA DEGL'INDIRIZZI DEI DISPOSITIVI DI I/U

Per poter parlare del trasferimento delle informazioni fra i dispositivi di I/U ed il calcolatore, dobbiamo prima conoscere la circuiteria ed i segnali usati per identificare e indirizzare i singoli dispositivi di I/U. Si possono usare molte tecniche, e ne esamineremo diverse; ma è impossibile illustrare tutti i possibili schemi d'interfacciamento dei dispositivi di I/U, per il fatto che molte modifiche si attuano per soddisfare necessità particolari.

Quando il calcolatore Apple viene programmato per eseguire un trasferimento di dati mediante uno dei due comandi di I/U di uso generale PEEK e POKE, il proces-

sore 6502 genera dei segnali destinati a sincronizzare il flusso dei dati. A questo punto quello che c'interessa di più è come si utilizzano le linee del bus indirizzi, che sono le 16 linee che indirizzano le singole locazioni di memoria ed i dispositivi di I/U. Ricorderete che le istruzioni di PEEK e di POKE contengono ciascuna l'informazione dell'indirizzo decimale, che serve ad identificare la locazione di memoria o il dispositivo di I/U indirizzato. Chiaramente, il calcolatore Apple non ha la facoltà di distinguere fra una locazione di memoria ed una porta di I/U.

#### INDIRIZZAMENTO DEI DISPOSITIVI

Tutti i dispositivi di I/U destinati ad essere utilizzati con il calcolatore devono essere in grado di riconoscere il proprio indirizzo. Dal momento che i comandi di PEEK e di POKE utilizzano indirizzi a 16 bits, i dispositivi di I/U devono "sorvegliare" queste 16 linee d'indirizzi, cioè le linee A15-A0, per l'evenienza dei propri indirizzi. I circuiti dei dispositivi di I/U possono rilevare la presenza di uno specifico indirizzo fondamentalmente secondo tre tecniche, che sono:

- condizionamento logico: rileva una particolare combinazione di segnali logici;

- decodifica: uno schema più flessibile del precedente, nel quale possono venir rilevati più indirizzi;

- confronto: un indirizzo assegnato o noto è paragonato con i segnali relativi al bus indirizzi, fino al verificarsi di un'uguaglianza.

Sono pure possibili delle combinazioni delle tre tecniche, ed anche diverse varianti. Noi daremo degli esempi per ciascuna delle tre tecniche di base.

#### Uso delle porte per la decodifica degl'indirizzi

Con la tecnica della decodifica degl'indirizzi dispositivo che prevede l'uso di porte specifiche, l'indirizzo dev'essere noto, affinché le porte possano essere configurate opportunamente. In quest'esempio supporremo che l'indirizzo del dispositivo sia 1010100011110111<sub>2</sub>, ovvero 43255<sub>10</sub>. La notazione binaria è lunga e abbastanza scomoda, e quindi vi sentirete certo più a vostro agio con l'equivalente esadecimale, A8F7H. Essendo le porte NAND/AND il tipo predominante attualmente disponibile per la realizzazione di condizioni logiche, nei nostri schemi logici utilizzeremo questi tipi di circuiti.

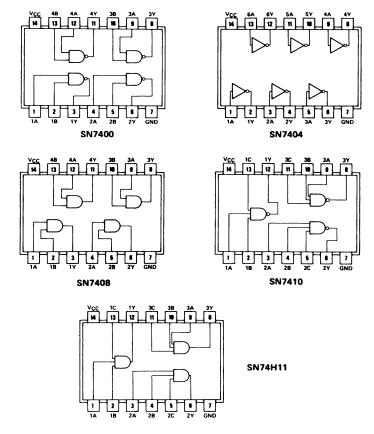

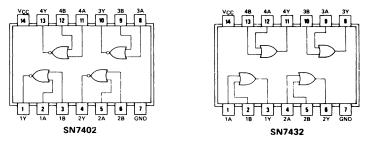

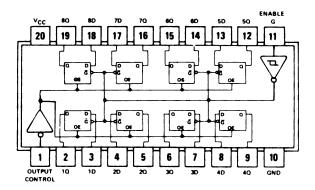

In Figura 2.1, al fine di rinfrescarvi la memoria, abbiamo evidenziato le configurazioni dei pins relative ad alcuni tipi di porte AND/NAND; nella Tabella 2.1 riportiamo la tabella della verità generalizzata relativa ad una porta di AND a due ingressi ed alla porta di NAND equivalente. Dal momento che spesso nei circuiti d'indirizzamento di un dispositivo si trovano inverters del tipo SN7404, in Figura 2.1 abbiamo inserito anche la configurazione dei pins relativa a questo chip. Anche le tabelle della verità riprodotte nella Tabella 2.1 mostrano la funzione di un inverter. *In tutti i casi lo stato*

Figura 2.1 — Configurazione dei pins relativi ad un inverter ed a varie porte AND/NAND.

logico uno corrisponde alla tensione più alta (da +2.8 a +5 volts), mentre lo stato logico zero corrisponde alla tensione più bassa (da 0.0 a 0.8 volts). Le funzioni della porta NAND sono disponibili con gl'ingressi 2, 3, 4 ed 8, quelle della porta AND con gl'ingressi 2, 3 e 4.

Dal momento che l'unico stato di uscita, che è un uno logico per le porte AND ed uno zero logico per le porte NAND, si ha soltanto quando *tutti* gl'ingressi di una porta AND o di una porta NAND sono degli uni logici, dovremo configurare l'indirizzo binario 1010100011110111<sub>2</sub> in modo che generi 16 uni logici all'ingresso di una porta AND o NAND, quando è presente sul bus indirizzi a 16 bits. Avete probabilmente capito che non si trovano in commercio porte AND e NAND a 16 ingressi, per cui al loro posto si dovrà utilizzare qualche altra configurazione: ad esempio, non sarà un problema usare una distinta porta NAND ad 8 ingressi per rilevare una configurazione di bits binari d'indirizzo sul bus d'indirizzo alto (A15-A8), ed un'altra porta NAND

|      | Porta | AND    | Porta NAND |      | Porta NAND Inverter |          | rter   |

|------|-------|--------|------------|------|---------------------|----------|--------|

| Ingr | essi  | Uscita | Ingr       | essi | Uscita              | Ingresso | Uscita |

| A    | В     | Q      | Α          | В    | Q                   | Α        | Q      |

| 0    | 0     | 0      | 0          | 0    | 1                   | 0        | 1      |

| 0    | 1     | 0      | 0          | 1    | 1                   | 1        | 0      |

| 1    | 0     | 0      | 1          | 0    | 1                   |          |        |

| 1    | 1     | 1:     | 1          | 1    | 0                   |          |        |

Tabella 2.1 — Tabelle della verità relative ad una porta AND a due ingressi, ad una porta NAND e ad un inverter.

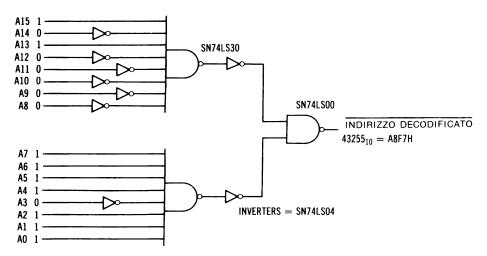

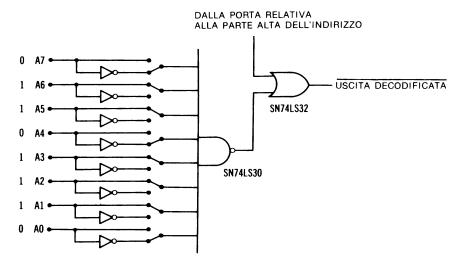

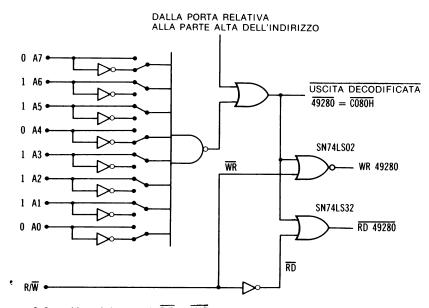

ad 8 ingressi per rilevare una configurazione di bits binari sul bus d'indirizzo basso (A7-A0). Semplici funzioni d'inverter sono usate per invertire i bits d'indirizzo posti a zero logico, affinché vengano applicati degli uni logici agl'ingressi della porta corrispondente, come si vede in Figura 2.2. In questo circuito sono stati usati due inverters ed una porta NAND, allo scopo di raggruppare le uscite di ciascuna porta ad 8 ingressi, in modo che l'uscita del circuito sarà uno zero logico soltanto quando *tutta* la configurazione di 16 bits 1010100011110111<sub>2</sub> viene rilevata sul bus indirizzi a 16 bits.

Figura 2.2 - Circuito logico di decodifica dell'indirizzo 43255, o A8F7H.

Uno dei principali inconvenienti di questo circuito è che alcuni segnali d'indirizzo devono passare attraverso quattro porte prima di uscire come indirizzo decodificato dalla porta NAND a 2 ingressi. E, dal momento che ciascuna porta carica il segnale di un leggero ritardo, questo fatto può provocare nel circuito qualche problema di temporizzazione. In realtà, i ritardi sono abbastanza trascurabili, e per il momento li ignoreremo. Comunque il ritardo può essere alquanto ridotto utilizzando nel circuito

una porta NOR o OR per raggruppare le uscite delle due porte NAND ad 8 ingressi: questa anzi è una buona regola di progettazione.

Le porte NOR ed OR sono facilmente procurabili, e sono largamente usate nell'interfacciamento dei calcolatori. Una tipica porta NOR ed una di OR sono rappresentate in Figura 2.3; nella Tabella 2.2 troverete le corrispondenti tabelle della verità.

Figura 2.3 — Configurazione dei pins di un tipico circuito integrato di porte NOR ed OR.

| Porta NOR |      |        |      | Po    | rta OR |

|-----------|------|--------|------|-------|--------|

| Ingi      | essi | Uscita | Ingi | ressi | Uscita |

| А         | В    | Q      | А    | В     | Q      |

| 0         | 0    | 1      | 0    | 0     | 0      |

| 0         | 1    | 0      | 0    | 1     | 1      |

| 1         | 0    | 0      | 1    | 0     | 1      |

| 1         | 1    | 0      | 1    | 1     | 1      |

Tabella 2.2 — Tabelle della verità relative ad una porta NOR e ad una porta OR a due ingressi.

La tecnica di condizionamento logico di Figura 2.2, pur essendo efficace nella decodifica di un singolo indirizzo e relativamente economica, è scarsamente flessibile. Un metodo più flessibile è rappresentato in Figura 2.4.

Figura 2.4 — Una semplice porta a quattro ingressi può venir programmata per ingressi logici 1 e 0.

In questo circuito è impiegata una tecnica di condizionamento logico nella quale gl'inverters possono essere usati per invertire, a seconda delle necessità, singoli bits d'indirizzo. Comunque i bits possono anche essere utilizzati non invertiti. I ponticelli permettono di assegnare l'indirizzo di dispositivo, come si vede in Figura 2.5, nella quale per chiarezza abbiamo rappresentato solo le condizioni logiche del bus relativamente alla parte bassa dell'indirizzo. Per le linee di bus relative alla parte alta dell'indirizzo è necessario un equivalente circuito logico. In questo tipo di circuito logico può essere selezionato uno qualunque dei 65536 possibili indirizzi, ma uno solo alla volta.

Figura 2.5 — Porta programmabile per la decodifica degl'indirizzi di dispositivo. (Il circuito relativo alla parte alta dell'indirizzo è equivalente.)

Il circuito con porte logiche programmabile assicura un'ampia flessibilità, in quanto gl'indirizzi possono venir facilmente cambiati al fine di soddisfare esigenze specifiche d'interfacciamento, ma d'altra parte un tale circuito può selezionare soltanto un unico indirizzo, e questa è una limitazione pesante. Quando si hanno più dispositivi di I/U posti sulla stessa scheda, ciascuno di essi richiede un proprio circuito per la decodifica dell'indirizzo. Ma questa limitazione è eliminabile con altre tecniche d'indirizzamento.

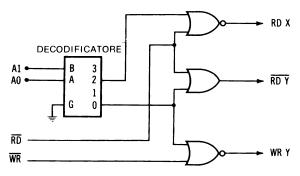

Purtroppo le tecniche di condizionamento logico che abbiamo illustrato non soddisfano tutte le necessità concernenti l'indirizzamento ed il controllo di un dispositivo di I/U. Ricorderete, da quanto si è detto nel Capitolo 1 sul segnale READ/WRITE (R/W), che questo segnale serve per sincronizzare il flusso d'informazione diretto al e proveniente dal calcolatore. Anche i dispositivi di I/U devono ricorrere a questo segnale di controllo, se si vuole che utilizzino correttamente il bus dati. In molte interfacce progettate per calcolatori basati sul 6502, la linea R/W è usata per fornire l'impulso negativo di scrittura, mentre il segnale R/W è invertito per generare un di-

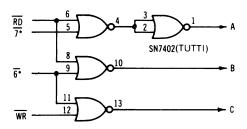

stinto impulso di lettura. I due segnali di controllo che ne risultano, WRITE (WR) e READ (R), sono di facile impiego nei circuiti d'interfaccia, perché sono attivi nello stato logico zero. L'uso di questi segnali è illustrato in Figura 2.6.

Figura 2.6 — Uso dei segnali RD e WR per generare impulsi di selezione dispositivo per la sincronizzazione delle relative operazioni.

In questo circuito l'uscita dal circuito che sente i 16 bits d'indirizzo è combinata con  $\overline{\text{RD}}$  e  $\overline{\text{WR}}$  allo scopo di fornire due segnali per il controllo delle porte di I/U. Questi due segnali di controllo sono una combinazione dell'indirizzo decodificato e dell'impulso  $\overline{\text{WRITE}}$ , ed una combinazione dell'indirizzo decodificato e dell'impulso  $\overline{\text{READ}}$ . L'impulso che ne risulta da ciascuna porta è detto *impulso di selezione indirizzo*, o *impulso di selezione dispositivo*. Più generalmente parlando, un *indirizzo decodificato* è condizionato da un *impulso di funzione* ( $\overline{\text{RD}}$  o  $\overline{\text{WR}}$ ), allo scopo di generare un *impulso di selezione dispositivo*. Nello schema del circuito di Figura 2.6, l'impulso  $\overline{\text{RD}}$  49280 potrebbe essere usato per controllare una porta d'ingresso dati, mentre l'impulso WR 49280 potrebbe essere usato per controllare una porta di uscita dati. Si osservi che la notazione WR 49280 dell'impulso non ha la riga soprascrita: questo vuol dire che l'impulso è attivo nello stato logico uno, mentre l'impulso  $\overline{\text{RD}}$  49280 è attivo nello stato logico zero. In quest'esempio è appropriato esprimere l'indirizzo relativo alle porte di I/U con un valore esadecimale, ad esempio  $\overline{\text{RD}}$  C080H.

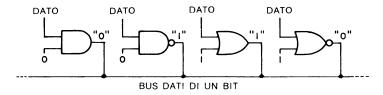

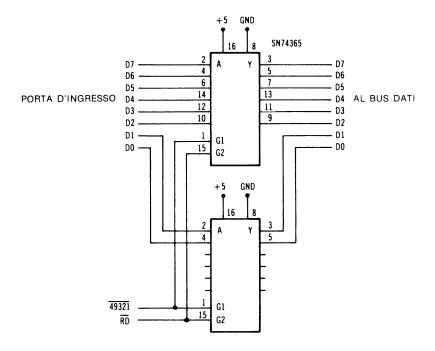

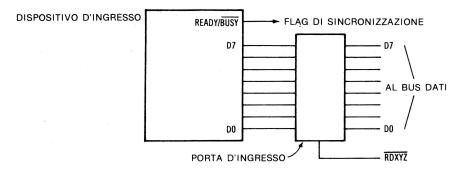

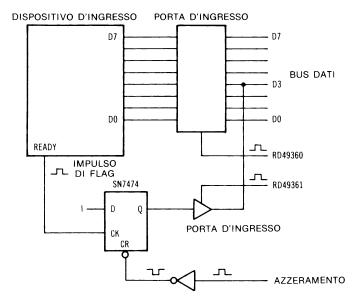

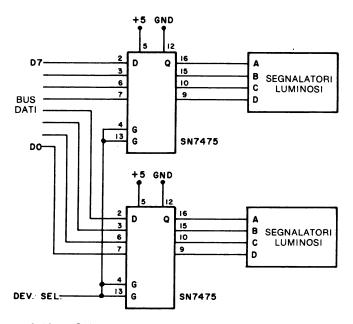

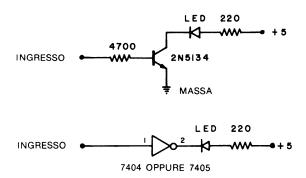

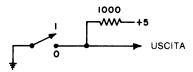

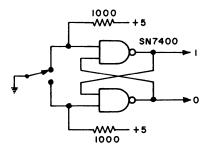

Prima di proseguire, è necessario avere ben capito che un'operazione di lettura comporta l'acquisizione dentro il calcolatore d'informazioni provenienti da una porta d'ingresso, mentre un'operazione di scrittura implica il trasferimento d'informazioni