# Spectrum +2 Machine Language for the Absolute Beginner

M

# Spectrum+2 Machine Language for the Absolute Beginner

**Joe Pritchard**

#### © 1986 Joe Pritchard

All rights reserved. This book is copyright and no part may be copied or stored by electromagnetic, electronic, photographic, mechanical or any other means whatsoever except as provided by national law. All enquiries should be addressed to the publishers:

Published in United Kingdom by Melbourne House (Publishers) Ltd 60 High Street, Hampton Wick Kingston-Upon-Thames Surrey KT1 4DB

Published in Australia by Melbourne House (Australia) Pty Ltd 96-100 Tope Street South Melbourne, Victoria 3205

ISBN 0 86161 209 4

Printed and bound in Great Britain by Short Run Press Ltd., Exeter.

# Contents

#### Chapter 1. Machine Code First Principles 1

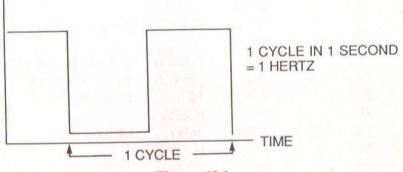

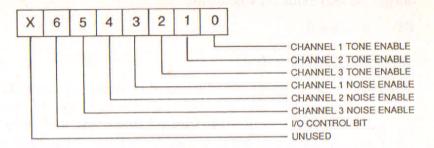

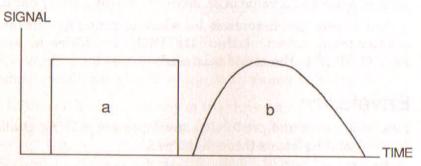

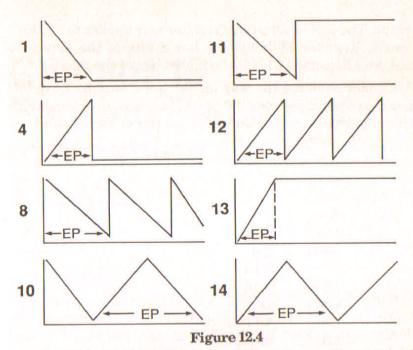

Why Bother? 2; What is Machine Code? 2; The BASIC Interpreter 3; Disadvantages of Machine Code 4; The Z80 CPU: What can it do? 6; The Stack 8; What the CPU is Capable of 9; Addresses 9; Spectrum 128 Hardware 10.

#### Chapter 2. How Computers Count 17

Bits and Bytes 21; Representation of Information 23; Summing Up 27.

#### Chapter 3. Machine Code and BASIC 29

Home for bytes 29; Screen Memory 33; Attributes 33; Printer Buffer 33; System Variables 33; Microdrive Maps 34; Channel Information 34; BASIC Program 34; The Calculator Stack 34; The Machine Stack 34; The GOSUB Stack 35; RAMTOP 35; POKE and PEEK 36; USR(address) 37; Saving Bytes on Tape 38; Loading Bytes from Tape 38; Entering Bytes 39.

#### Chapter 4. Registers at Work 41

Register Addressing 42; Immediate Addressing 43; Register Indirect Addressing 44; Extended Addressing 46; Labels in Machine Code 48; Indexed Addressing 49; Immediate Indexed Addressing 50.

#### Chapter 5.8 Bit Counting 53

The F Register 53; How are they used? 57; Counting with 8 Bits 57; 8 Bit Arithmetic 61; 8 Bit Addition 61; 8 Bit Subtraction 65; BCD Arithmetic 66; Arithmetic with BCD 66; Comparing Numbers 67; Logical Operations 70; Effect on Flags 74; Manipulating Bits within a Byte 75; Rotates and Shifts 76; Left Operations 77; Right Operations 78.

#### Chapter 6. 16 Bit Data Transfers 81

Manipulating the Stack 83; Warning! 85; Moving the Stack 86.

#### Chapter 7.16 Bit Arithmetic and Counting 89

INC and DEC 89; Addition and Subtraction 91; Effect on Flags 91; Add and Subtract with Carry 92.

#### Chapter 8. Jumps, Loops and Block Operations 95 Jumps 95; Relative Jumps 99; Register Indirect Jumps 102; CALL and RETURN 106; Conditional Subroutine Calls 109; Restarts 110; Block Operations 110; CPIR and CPDR 113; Block Moves 114.

Chapter 9. Ins and Outs and Odds and Ends 117 Input and Output Instructions 117; Odds and Ends 119; NOP 119; RRD and RLD 119; RLD 120; RRD 120; HALT 121; NEG 121.

Chapter 10. Interrupts on the Spectrum 123 EI and DI 124; The Spectrum and Interrupts 124; Interrupt Modes 125; Interrupt Vectors 126; Simple Interrupts 128.

Chapter 11. 48 and 128 Modes of Operation 133 New System Variables 134; Paging memory 135; Using the I/O Address 136.

#### Chapter 12. Sound 139

Software Sound Production 140; Hardware Sound Generation 144; Envelopes 153; Machine Code PLAY Commands 156.

Chapter 13. Passing Parameters to Machine Code Programs 157 VARS 157; Structure of the Variables 158; Find the Variable 160

Chapter 14. Keyboard Operations 165

Keyboard Repeats 166.

### Chapter 15. The Screen Display 169

Screen RAM Layout 169; The Attributes File 171; Printing Characters 172; Permanent Attributes 175; Extra Character sets 175; Simple Graphics 176.

#### Chapter 16. ROM Routines 177

The Error Restart 179; The 'Print a Character' Restart 179; The Tape Routines 179; Beep Routine 180; The Floating Point calculator 180.

Appendix 1. Instructions and Op-Codes 185

Appendix 2. Flag Operation Summary 189

Index 191

# Chapter 1 Machine Code First Principles

This book is designed to introduce the Spectrum 128/Plus 2 BASIC programmer to the 'mother tongue' of his or her computer. You may have previously heard of machine language, or it may be totally new to you. Whichever category you fall into, don't worry; we'll start our investigation of machine language, or **MACHINE CODE**, as it's sometimes called, by looking in this Chapter at the basic principles of the subject.

The first thing to do is to look at the way in which we normally program our computer. We type in a line of BASIC and then it is 'vetted' by the Spectrum ROM to see if it's legal; this is the same whether you're working in 48 or 128 BASIC. (As an aside, unless I otherwise mention it the machine will be running in 128 mode.) If the line is OK, it's entered into the program or executed, depending upon whether we gave it a line number or not.

When we're typing instructions into the computer in this way, we're not really communicating with the 'brain' of the computer, the **Central Processor Unit**, or the **CPU**. When we program the computer in BASIC, we never actually access the CPU directly; instead we go through a 'middle man' called the BASIC Interpreter, which directly accesses the CPU. The CPU used in the 128/Plus 2 is called the Z80, and is probably the most popular CPU around in home computers at the moment. It was used in the predecessors of the 128/Plus 2, the 48k Spectrum and the Spectrum+, and has also been used in the other popular Amstrad machines. The CPU is an electronic 'chip', and is the heart of all the activity of the computer. Other chips are to be found in the 128, but they are all under the direct or indirect control of the CPU. When we talk about programming the 128/Plus 2 in machine code, we're actually talking about programming the Z80 CPU of the computer in machine code.

## Why Bother?

Spectrum Plus 2 BASIC is a reasonably good version of BASIC; it's a little slow, but for many programs it is quite adequate. Why should we bother learning a new language? Well, there are three main advantages that machine code offers us over BASIC.

- 1. Faster programs.

- 2. Programs written in machine code can use less memory to do the same job.

- 3. Certain tasks can ONLY be done using machine code.

In addition, machine code allows us to free ourselves from the limitations of BASIC, and can also allow us to alter the way in which BASIC works! Thus, a knowledge of machine code can be a very useful thing. Having hopefully answered the question of 'Why?', let's now look at 'What?', and see exactly what machine code is.

## What is Machine Code?

The Z80 CPU, if you've never actually seen one, is a black 'chip', about 2" long, with 40 metal 'legs' on it which form electrical connections between the computer circuit and the silicon chip inside the black plastic case. Of these 'legs', or **PINS**, as they are called, 8 are particularly important. The CPU communicates with the rest of the computer via electrical signals and the CPU is designed to behave in different ways depending upon the combination of electrical signals on these 8 pins. Remembering that we're talking about electrical signals, let's represent the presence of an electrical signal on one of these pins by a '1' and the absence of an electrical signal as a '0'. As there are 8 pins of particular interest, a typical combination of electrical signals on these pins might be represented as:

00110010

This particular combination of signals will cause the CPU to behave in a particular fashion, and so we might say that this combination instructs the CPU to perform a particular job.

We call such a combination of signals a machine language instruction, just as 'LET a=0' is a BASIC instruction. This is essentially what machine code programming is all about; giving the CPU a sequence of combinations of electrical signals that tell it to do a sequence of tasks. The instructions that are understood by the CPU are collectively called the **Z80 INSTRUCTION SET**. Each different CPU has a different instruction set, and so programs written in machine language for one CPU will almost certainly *not* work on a different CPU, because the instruction sets are different.

## The BASIC Interpreter

This is a machine language program whose job it is to convert BASIC instructions typed in to the computer into machine language instructions that the CPU can understand. This is similar to the way in which we might use a dictionary to translate from English into a foreign language. Alternatively, if we could afford it, we might use a professional Interpreter.

Part of the BASIC Interpreter in the Spectrum 128 is a series of small programs, similar to BASIC subroutines, that tell the CPU how to communicate with the keyboard, screen, sound chip and tape recorder. In many machines, these routines are totally separate from the BASIC Interpreter, and are called the **OPERATING SYSTEM** (**OS**) of the computer. In the Spectrum, the BASIC Interpreter and Operating System programs are rather mixed up; I tend to treat all the Operating System machine code programs as being part of the BASIC Interpreter. However, these 'OS' routines of the BASIC Interpreter are called whenever the Interpreter needs to put something on the screen, read the keyboard or send information to tape.

The fact that we have to translate BASIC Instructions to machine code before they can be used is the principle reason for the slowness of BASIC in comparison to machine code programs. The translation process takes time, and also the machine code routines that finally do the required tasks are not as efficient as they could be.

## **Disadvantages of Machine Code**

There are a few disadvantages to using machine code. Just to balance things up a little, let's have a look at them.

- 1. Machine language programs are difficult to read and find errors in.

- 2. They are difficult to transfer from one type of computer to another. Usually this transfer involves re-writing parts of the program, if not all of it!

- 3. Complex arithmetic, such as trigonometry, is difficult using machine code.

You can thus see that 'You pays your money and takes your choice' with regard to whether machine code or BASIC is used to write a particular program. Speed can be provided by machine code, and good mathematical abilities are more easily provided from BASIC. Thus you'd be best to write your epic arcade game in machine code, but that Accounts Program for the office might be easier to write in BASIC.

So far, we've seen that we can represent machine code instructions as a series of 1's and 0's. If we had to write machine code programs like this, then only the masochists of the computing world would bother! It would simply be too time consuming to write big machine code programs in this way. To us humans, such strings of 1's and 0's can represent a **BINARY NUMBER**, and we can then translate this into decimal. This would be a much more convenient representation of the instructions for us, although the CPU would still see the instruction as a series of electrical signals on those 8 pins. However, we could now write a machine code program as a series of decimal numbers. While this is more intelligible to us than a string of binary numbers, it still doesn't give us any idea of what a particular CPU instruction does. We could have a list of these numbers and the jobs they perform, but this would soon get to be more like doing the yearly accounts than programming a computer! No, what would be useful would be a method of representing machine code instructions in some sort of English. We can, in fact, do this.

We use a form of representation called ASSEMBLY LANGUAGE. Each machine code instruction is given a short 'name' which indicates its function to us. This name is called a MNEMONIC. (The first 'm' is silent, and the word is pronounced 'nemonic'). An alternative name is an ASSEMBLER INSTRUCTION. We now have three different ways of representing instructions to the CPU: binary, decimal or mnemonic. For a particular instruction, let's look at each method.

| Binary   | 01110110 |

|----------|----------|

| Decimal  | 118      |

| Mnemonic | HALT     |

From the mnemonic, you might even be able to guess what this instruction does. Yes, it tells the CPU to stop, or HALT, until further notice.

Of course, such mnemonics are totally incomprehensible to the CPU. We thus require a method of converting mnemonics back into 1s and 0s for the CPU. There are two ways of doing this, known as 'the hard way' and 'the easy way'! The first is to use tables like those in the back of the book to to convert the mnemonics into numbers. This technique is called **HAND ASSEMBLY**, and although it's possible to hand assemble small programs it's not feasible for larger ones. Though good for the soul, it takes a long time, is prone to errors, and can be very frustrating. The second method is to get a computer program to do the job for you. Much easier!

Such a program is called an ASSEMBLER, and it ASSEMBLES a machine code program from the mnemonics of the Assembly language program. There are a variety of such programs available for the Spectrum 48 and Spectrum+ and you should be able to find one that works with the Spectrum 128.

# The Z80 CPU: What can it do?

The CPU is responsible for virtually everything that goes on in the computer; as soon as you turn the computer on, the CPU begins running, or **EXECUTING**, the machine code program that initialises the computer and puts the 'main menu' on the screen. This, and all the other jobs done by the CPU may appear to be incredibly complicated, but, in fact, the CPU is only capable of doing very simple tasks, such as addition and moving numbers from one part of the computer to another. However, these operations are carried out very quickly, and it is the speed of operation that gives the CPU its power.

With such simple tasks, the CPU uses what might be called its 'fingers' to carry them out, just as a child might when performing simple sums. It can make use of 'pencil and paper', in order to temporarily remember the result of a task, when necessary, though. These partial results are stored in 'boxes' in the computer memory. Three points become obvious from the fact that the computer uses 'fingers' for its operations.

- Only whole numbers can be represented directly by the CPU. As you may know, these whole numbers are called INTEGERS. The reason for this is that the CPU cannot work in 'half fingers'!

- 2. The size of the numbers that can be represented on the CPU fingers is limited by the number of fingers that the CPU has.

3. The limitation of point (2) above can be partially overcome by allowing the CPU to use its 'toes' as well as its fingers for its counting operations.

However, whereas we're stuck with two hands and two feet, the CPU has several more hands and feet and each 'hand' has 8 fingers and each 'foot' has 16 toes! In addition, by a clever coding system the CPU can count up to 255 on each of its hands and up to 65535 on each of its feet! This is clearly much more efficient than our usual way of counting on our fingers, and we'll take a look at how this coding system works in Chapter 2.

So, how might the CPU do a simple job, like add together 2 small numbers. Let's see how the sum '3+4' would be dealt with. First of all, let's give one of the CPU hands a name; we'll call it 'A'. Also, we'll let the CPU use some of the 'boxes' in the computer memory. The steps that the CPU might take to add the two numbers could be:

- LD A,3

- LD (BOX#1),A

- LD A.4

ADD A,(BOX#1)

LD (BOX#2),A

'LD' is a mnemonic for a machine code instruction called LOAD; this simply tells the CPU, in the first instruction, to count '3' on to its 'A' hand. In the second instruction, we tell the CPU to count the contents of 'A', which is 3, onto the 'fingers' of the memory box BOX#1. 4 is then counted onto A, and the value on A is added to the value in BOX#1. Finally, the result is stored in BOX#2.

The second instruction introduces us to a quite important concept of machine code programming. The brackets around the word 'BOX#1' indicate that we're interested in the *contents* of this box. In the first instruction, we were interested in the actual number '3', so we didn't need the brackets. The use of brackets in this way to refer to the contents of a memory 'box' is a bit like the idea of BASIC variables. If it helps at all, think of the second instruction as LET BOX#1=A, where A can be thought of as another 'variable', in this case holding 3. The ADD instruction, by the way, leaves the result of the addition on the fingers of 'A'; this is very common in machine code programming. The results of CPU operations are always left on the fingers of various CPU hands. As you can see, it's a lot more long winded than the BASIC equivalent of LET A=3+4!

## The Stack

Despite the apparent excess of hands and feet possessed by the CPU, it's often desirable for the CPU to be able to store results of CPU operations elsewhere. As we've seen above, the CPU can use memory 'boxes', but the CPU can also use a special form of storage called a STACK. Years ago, before in-trays, out-trays and computer filing systems were invented many desks would be occupied by a piece of wood with a metal spike stuck in it. Pieces of paper entering the office were stuck on this spike until they could be dealt with. The last piece of paper placed on the stack would thus be the most easily accessible of all the pieces of paper on the spike. The computer equivalent of the spike, the Stack, is useful to the CPU precisely because of this fact; if a piece of information has been stacked, the CPU knows where to find it. The CPU PUSHES information onto the stack, usually two hands worth of information at a time. A typical use is where the CPU has some information on a hand, but needs to use the hand for something else. PUSHing the hand on to the stack will save it, and once the hand is free again the CPU can POP the information back off of the stack onto the desired hand. Information can be stored from as many of the hands and feet of the CPU as you like, each store operation needing a separate PUSH. However, like the office spike, the only piece of information that is readily available is the last item PUSHed on. The office spike grew upwards in size whenever a piece of paper was pushed on to it. The stack also grows, but in the computer the stack is arranged so that it's upside down. Thus, the stack grows downwards in the computer as more information is PUSHed on to it.

# What the CPU is Capable of

As we mentioned earlier in the Chapter, the CPU is really only capable of performing simple tasks. Due to the limitations set by the number of its fingers and toes, it is limited to using numbers in the following ranges:

- 1.8 fingered numbers in the range 0 to 255.

- 2.16 fingered numbers in the range 0 to 65535.

I use the phrase 8 and 16 fingered numbers deliberately here; this is because the CPU can use two of its 'hands' as an extra 'foot' if it wants to, thus effectively giving us an extra 16 fingered foot to put larger numbers on. The basic operations that the CPU can perform on these numbers are as follows:

- 1. Counting on one hand.

- 2. Counting on two hands.

- 3. Addition and Subtraction on one hand.

- 4. Addition and Subtraction on two hands.

- 5. Various manipulations of one handed numbers, such as making a number negative.

- 6. Causing the CPU to jump from one place in a machine code program to another.

- 7. Causing the CPU to transfer numbers from one part of the computer to another.

Before we leave this introductory Chapter, let's look at two last topics; the concept of **ADDRESSES** and the hardware of the Spectrum 128/Plus 2.

# Addresses

In normal usage, an address refers to where abouts a particular building can be found in a town or city full of them. In computing terms, an address refers to where in the computer a particular 'box', used for the storage of numbers, can be found. The number in this box could be a machine code instruction or a piece of data. Whatever it is, it will be stored in the box as an 8 fingered number; this is the largest value number that one of the boxes can hold. In the Spectrum 128, some of the boxes are used to store the BASIC Interpreter program, others store our BASIC program and still others are used to store the information that makes up the screen image.

## Spectrum 128 Hardware

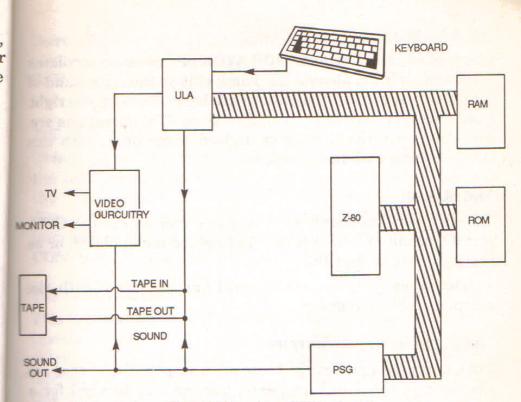

Let's now take a detour and look at the hardware of the Spectrum 128/Plus 2. **Hardware** is the term applied to the various electronic components that make up the computer system. I once read that hardware was the bit you could kick; this is, in some ways, true, but don't take it literally! **Software** is the term given to the programs that are run on computers. Figure 1.2 indicates how the various components of the system are arranged. Let's now look at the function of each part of the system.

## The Z80 CPU

There are 8 hands in the CPU, and they've all been given names. They're called **A,B,C,D,E,F,H** and **L**. In addition, there are two feet, called **IX** and **IY**. These hands and feet are often represented diagramatically as shown in Figure 1.1.

| A    | F |

|------|---|

| В    | С |

| DAGE | E |

| н    | L |

| IX   |   |

| IY   |   |

Figure 1.1 The Z80 Register Set.

Figure 1.2 Spectrum 128 Hardware.

All of the hands except for 'F' can be used for counting on. Hand F has a special function, as each finger of this hand is used to indicate whether or not a particular event has happened within the CPU. We'll look at this hand in a later Chapter.

We can team up hands to form some new feet. The hands involved are B,C,D,E,H and L. The new feet formed are BC, DE and HL. Note that we can't just combine hands as we want; these are the only allowable combinations. A CE or BL pair is not possible. Each of these new 'feet' can hold a sixteen finger number, just like the IY or IX feet.

The hands and feet of the CPU are really called **CPU REGISTERS**. Thus the A hand is usually called the A Register. The feet produced by pairing up two hands, such as BC, DE or HL are called **REGISTER PAIRS**. The IX and IY feet are also given a special name; they are called **INDEX REGISTERS**. Don't worry about the Index Registers, as we'll be looking at these registers later.

#### THE A REGISTER

This is often called the **ACCUMULATOR** because it accumulates the results of CPU operations. Think of it as the right hand of the CPU; just as many operations are best done with the right hand (for right handed people), then some CPU operations are best done with the A register. Indeed, some operations can ONLY be done with the A register.

#### THE HL PAIR

This is a very commonly used Register Pair within the CPU, and it's useful to look at it as a 16 fingered accumulator, or as the 'right foot' of the CPU.

The other registers are 'general purpose' ones, with the exception of the F register.

#### THE ALTERNATIVE REGISTERS

Not a name for a pop group! These are a set of registers that are the same as the A to L registers, but can only be used for a limited range of tasks. They are called the ALTERNATIVE **REGISTER SET** and are called A',B',C',D',E',F',H' and L'. There are no alternative IX or IY registers. The only thing that we can do with these registers is to copy the contents of the main register set (Registers A to L) into them for safe keeping whilst we use the main registers for something else. When we do this, the contents of the Alternative Registers are copied into the main registers. When writing machine language programs on the Spectrum 128/Plus 2 it's a good idea not to use these Alternative Registers until you gain some experience. This is because the BASIC Interpreter makes frequent use of the Alternative Registers, and would get rather confused if you altered their contents and didn't change them back!

#### THE STACK POINTER

This is a special Register Pair that we don't directly use very much. It's used by the CPU to indicate the address of the position in memory of the last entry on the Stack. As the Stack grows downwards into memory, the number in this register decreases with each PUSH and increases with each POP. The contents of the Stack Pointer (SP) is thus altered whenever the CPU uses the Stack. This is done automatically, so we needn't worry too much about it.

#### THE PROGRAM COUNTER

This Register Pair tells the CPU where in memory it can find the next machine code instruction so that the CPU can fetch the instruction and act on it. The Program Counter isn't directly altered by our programming. The collection of the instructions is dealt with by another part of the CPU called the **CONTROL UNIT** of the CPU.

#### THE CONTROL UNIT

This is the supervisor of the CPU. It coordinates and times the various operations of the Z80 and is responsible for fetching a machine code instruction from memory. The instruction is fetched from the address held in the Program Counter, and this instruction is then passed over to a special register in the CPU called the **Instruction Register**.

#### THE INSTRUCTION REGISTER

This register holds an 8 finger number representing an instruction while the CPU works out what the instruction is. One the task to be done is known, the Control Unit acts upon it.

### THE ARITHMETIC AND LOGIC UNIT

This is often called the ALU, and is the 'pocket calculator' of the CPU, being responsible for all the arithmetic operations that the Z80 can perform. It's very simple in its function, being able to add and subtract but not being able to do multiplication or division. It can also perform what are called **LOGICAL** operations on the contents of CPU registers, such as comparing the contents of two registers, and raising (setting to '1') or lowering (setting to '0') fingers within a hand. As a byproduct of the activities of the ALU, the fingers in the F register are affected. Despite the fact that the Z80 is a very smart device, it would be useless without the other chips in the 128. Let's now take a quick 'Cook''s Tour' around them to see what they do.

## Memory

Because of its 16 fingered Program Counter, the Z80 can gain access to 65536 different 'boxes' in memory. However, as we'll soon see, by a clever feat of engineering the 128 uses some of these locations 'twice', thus allowing us to gain access to more memory. This is used by the 'Silicon Disc' facillity of the 128, but we can also use it for storage if we like. However, we won't go into it in too much detail; this is, after all, a beginner's book.

The Spectrum 128 has two types of memory, called **Read Only Memory** and **Random Access Memory**. Let's now look at what these names mean.

#### **READ ONLY MEMORY**

This type of memory is used in the Spectrum 128 to hold the BASIC Interpreter. ROM, as this type of memory is also known, has a useful ability; it retains its contents when you turn the power off. Thus, the BASIC Interpreter is always in your machine. However, we cannot alter the contents of ROM, except by putting new memory chips into the machine! We can still copy numbers held in this type of memory into CPU registers, and the CPU can run programs made up of instructions held in ROM. However, we cannot write any new information from registers into ROM. Hence the name, Read Only memory.

Well, ROM is alright for programs or information that we don't want to alter. But what about the programs we write? We can type them in and the computer remembers them. But, as you know, when we turn off the power to the 128 our BASIC programs disappear from the computer memory, hence the need for SAVEing them to tape or Microdrive. There must, therefore, be another type of memory apart from ROM.

14

#### **RANDOM ACCESS MEMORY**

For this type of memory, I prefer to use the unofficial but much more descriptive name of Read and Alter Memory. This describes exactly what RAM is; a type of memory which we can alter at will. We can read number from it, then alter it, as often as we want. Thus for situations where we frequently need to change the contents of memory, such as BASIC or machine code programming, we use RAM for our memory.

We've already mentioned the big drawback with RAM; turn off the power, and the contents are lost forever. Just as with ROM, a 'box' in RAM can store 8 finger numbers – between 0 and 255. Later in the book we'll see how we can use two of these locations to hold a 16 finger number, but for now let's just stick to 8 finger numbers in memory locations.

Before leaving memory for a while (we'll return to it in Chapter 3), how does the CPU tell the memory, whether ROM or RAM, which 'box', or LOCATION, it wants to use? Well, the CPU is connected to memory by the 8 pins that we mentioned at the beginning of this Chapter, called the DATA pins of the CPU because they carry information, or data, and 16 other pins called the ADDRESS pins. These tell the rest of the computer what value is in the Program Counter at any time. When the address of a memory location is put into the Program Counter, therefore, the memory knows about it, and the correct memory location will 'know' that the CPU wants to access it and so will make itself available to the CPU. Other pins of the CPU tell the memory whether a read or write operation is needed. Remember that reading takes information FROM memory TO the CPU registers and a write takes information from the CPU registers TO the memory. The collection of Address pins is called, in technical jargon, the Address Bus, and the collection of Data pins is called the Data Bus. The 'bus', in this case, carries numbers around the computer circuit rather than people around a town or city! Remember that although the CPU can only access, or ADDRESS, 65536 memory locations at once the Spectrum 128/Plus 2 has about twice this many memory locations. Exactly how the 128 gets around this problem will be discussed later.

## The Programmable Sound Generator

This chip, also called the PSG, is responsible for the sounds produced with the PLAY command. BEEP uses a different technique to produce sounds. In addition, the PSG is responsible for the MIDI interface, which allows the Spectrum 128 to control suitable electronic musical instruments such as synthesisers, and the RS232 Serial Interface, which allows the 128 to communicate with suitable printers, other computers or telecommunications equipment. We'll look at the PSG in considerable detail in Chapter 12.

## Video Circuitry

This collection of electronic components is responsible for producing the image that you see on the Television or monitor screen. The Plus 2 can drive a standard television, an RGB monitor for colour displays or a green screen monitor for cases where a steady display is more useful, such as might be required for long periods of programming. There's nothing here that we can program.

## Uncommitted Logic Array

This is a 'black box' amongst the chips in the 128. Suffice to say that it helps the CPU out with many of the housekeeping activities, such as screen display and keyboard reading. It occasionally causes us some problems, especially if we're putting machine code programs in the lower half of memory. However, these problems are quite rare and I'll mention them when we come to them. The ULA is probably the second most important chip in the computer after the Z80.

All these devices are under CPU control to some extent, with the exception of the Video Circuitry. If we want to alter their behaviour, we have to program the CPU accordingly. However, this isn't as difficult as it sounds, and we'll see later in the book how we can use machine code to get the best out of the 128 hardware. Now that we've discussed the cast list of the Spectrum 128/Plus 2, let's go on to look at something that is rather fundamental to computers; the subject of counting.

# Chapter 2 How Computers Count

I mentioned in Chapter 1 that the CPU can represent numbers between 0 and 255 on its 8 fingered hands. How can this be, when we can only count to 10 on our fingers? Well, the answer is that the way in which we count on our fingers is rather inefficient, and the computer is simply more efficient in its counting than we are.

When we count on our fingers we let each finger have the same value; i.e. a raised first finger represents the same value as a raised second finger. There's no reason why this should be. We could let each finger represent a different value. For example, a raised first finger could indicate a value of 1, a raised second finger 2 and so on. In this scheme, the number 3 could be represented on just two fingers by raising the first and second finger (1+2). When either finger is lowered, it has a value of zero. Thus to represent the number 2, we'd just raise the second finger and keep the first finger lowered. This method is clearly more efficient than our usual means of counting on fingers, as the usual method of counting on our fingers would need 3 fingers to represent the number 3, and this new method needs only 2 fingers. The counting method used by the CPU is based upon this idea, and appreciates the below facts:

- 1. Whether a finger is lowered or raised is important to the overall number being represented on the fingers.

- 2. The position of a finger within the hand is important to the value represented on that finger, which in turn is important to the number represented on the hand as a whole.

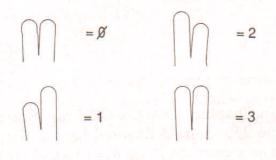

Let's now take a look at our new method of representing numbers using two fingers.

#### Figure 2.1

We might represent a raised finger by the digit '1' and a lowered finger by the digit '0'. This is much easier than drawing pictures of hands all over the place. Thus we could rewrite the above as:

| 00 | = | 0 |

|----|---|---|

| 01 | = | 1 |

| 10 | - | 2 |

| 11 | = | 3 |

This should look vaguely familiar; remember our way of representing the presence of an electrical signal. We used 1s and 0s there as well.

Such a method of representing numbers in which there are only two different states (raised or lowered fingers, 1 or 0) is called a **BINARY** method of representing numbers. If we add another finger to the two that we've considered so far, then we have 8 different combinations of three fingers, thus allowing us to represent 8 different numbers. If you don't believe this then try it with your own fingers. We can represent the numbers 0 to 7 on these three fingers. Let's use our 0 and 1 notation to represent lowered and raised fingers.

| 000 | =     | 0 |

|-----|-------|---|

| 001 | =     | 1 |

| 010 | =     | 2 |

| 011 | =     | 3 |

| 100 | •=    | 4 |

| 101 | =     | 5 |

| 110 | =     | 6 |

| 111 | ·<br> | 7 |

The addition of a fourth finger allows us to represent numbers between 0 and 15. In computing circles, the numbers 10 to 15 are often represented by the letters A to F rather than the two digit numbers 10 to 15. Thus,

| 10 | = | Α |

|----|---|---|

| 11 | - | В |

| 12 | = | С |

| 13 | = | D |

| 14 | = | E |

| 15 | = | F |

This method of representing numbers is called **HEXADECIMAL NOTATION.** In this way of representing numbers the number 0 to 15 are represented as 0,1,2,3,4,5,6, 7,8,9,A,B,C,D,E and F. 16 is represented as 10 in hexadecimal, 17 as 11 and so on. A four finger number can be represented by a single hexadecimal digit, and an 8 finger number can be represented by 2 hexadecimal numbers. We indicate that a number is in hexadecimal by prefixing it with '&' or '#' or following it with 'H'. Although the Spectrum doesn't understand hexadecimal numbers directly, there are advantages to be had in using them. Obviously, hexadecimal numbers can be converted in to decimal, and vice-versa. We'll soon see how we can do this. The advtantages offered by using hexadecimal notation are:

- We can easily convert hexadecimal numbers into binary numbers and so we can see which fingers within a hand are raised or lowered.

- 2. By the number of hexadecimal digits used to represent the number, we can tell if the number will fit into one or two hands; a one handed number has two digits and a two handed number has four digits.

How can we work out what value a number has if we know which of the fingers are raised or lowered? Well, look at Figure 2.2.

We've got 4 fingers raised here, and we've assigned each finger a value. When any finger is raised it has the value given, and if it's lowered it has the value 0. Thus with all 4 fingers raised, as above, the fingers will be representing the number:

8+4+2+1 = 15

We simply add up the values that have been assigned to each raised finger. Thus if the left most finger was lowered, the value represented would be:

0+4+2+1=7

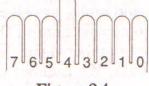

If you're mathematically inclined you'll probably note that the value represented by each finger is multiplied by two as we go from right to left. If we number the fingers in the below fashion:

then the values assigned to each finger is 2 to the power of N, where N is the finger number. 2 to the power of 0, for example, is 1. So far, we've seen how we can represent numbers up to 15. You should be able to see what to do to enable us to represent larger numbers; just add more fingers. For example, the number 16 is represented on an 8 fingered hand in the below fashion, with finger number 4 raised.

#### Figure 2.4

This can be written in hexadecimal, as we've already seen, as =10. We arrive at this by splitting the 8 finger number into two 4 finger numbers, and we then give each 4 finger number a separate hexadecimal digit. Thus in this case, the right 4 fingers are lowered, thus we can represent them by a '0'. Of the left 4 fingers, the rightmost of them is raised, so we can represent these four fingers with a '1'. The significance of these 4 finger handlets' is not the same to the total value of the number; the left 4 fingers represent 16 times the value of the right 4 fingers. As a further example, consider the situation where all 8 fingers are raised. Each hand is represented by the hexadecimal digit F (#F=1111), and the value contributed to the total value of the number by the left hand 'F' is 16\*15 (remember that =F=15). The value contributed by the rightmost 'F' is just 15, so the total is 15\*16+15, or 255. Thus, we can see how we can represent 255 on 8 fingers. An extension of this will allow us to represent 65535 on 16 fingers.

## **Bits and Bytes**

It's now time to introduce the proper names of the hands and fingers that are used in computer counting. In common English, an alternative name for a finger is a digit, and it's the same in computing. Each finger, or binary number, is thus called a digit, and there are 8 such digits in our 8 fingered numbers. There is a special name for a Binary Digit – we call it a **BIT**. This is simply a shortened version of BInary digiT. We can thus call the 8 finger numbers 8 bit numbers. These collections of 8 bits are also given a special name; they're called **BYTES**. A byte is thus a number that can be represented on 8 fingers or a CPU hand. The 4 finger 'handlets' are called NIBBLES, a nibble, after all, being a small byte.

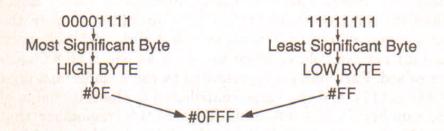

The terms bit, byte and nibble are all common in computing circles, and you'll come across them in this book and in other books as well. Just as we numbered our fingers, we give the bits within the byte a number. We number the bits from right to left, 0 to 7. Bit 0 is given a special name, the **LEAST SIGNIFICANT BIT**, or LSB. This is because the value contributed to the byte by this bit, 1, contributes the least to the value represented by the byte. For a similar reason, bit 7 is called the **MOST SIGNIFICANT BIT**, or **MSB** of the byte. In the same way, we also label the two bytes that make up a 16 bit number of the type that can fit into a register pair.

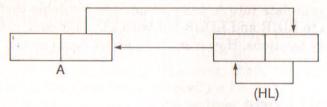

Here the high byte has a significance to the total value of the 16 bit number of 256 times the low byte. Thus the total value of a 16 bit number is given by:

TOTAL = 256\*HIGH + LOW

where low is the value of the low byte and high the value of the high byte. In the same way, a Register pair in the CPU is said to be made up of a High Register and a Low Register. When you write down a Register pair's name, the name of the High Register is written first. Thus in the BC register pair, B is the high register and C is the low register. This fact isn't too difficult to remember if you think about the HL register pair.H holds the High byte and L the Low byte. This might be why the name 'G' wasn't applied to a register; a GH register pair might be a little confusing.

# **Representation of Information**

e

e

3

Human beings deal with information mainly as numbers and etters. Computers can only deal with numbers. Therefore, because the computer has to tell us the results of its operations, is clear that the computer must have a way of representing other forms of information. There are two main types of information represented by numbers in a computer:

- 1. Machine language programs. These could be the BASIC Interpreter or a program written by the user.

- 2. Data for a machine language program. This can either be numeric, or might include some textual information. A BASIC program, for example, could be treated as data for the BASIC Interpreter program.

Let's now look at how different types of information are represented in the memory of the computer.

## **Program Representation**

A machine language program, as we've already said, is a sequence of bytes that represent machine code instructions to the CPU of the computer. They are stored in the memory of the omputer, and Z80 instructions can be between 1 and 4 bytes in length. For example, the HALT instruction is only one byte in length. Once the number representing the instruction, 118, has been read from memory and acted upon the CPU is able to go on and get the next instruction. However, with the more 'long winded' instructions the CPU cannot do anything until it has read the rest of the instruction from memory. The Control Unit of the CPU automatically knows how many bytes are needed to make up a given instruction. It should be obvious that a single byte instruction will probably be acted upon more quickly than one of these 'multi byte' instructions.

### Data

In BASIC we are able to use various types of variable to hold information on which our programs are to work. These include whole numbers, such as 1,2 or 4000, Real Numbers, such as 1.23, 0.34 or 0.000001 or strings of characters, such as "Hello" or "Don't Panic". In machine code, we don't have this sort of versatility; the only numbers that the CPU can handle directly are those in the range 0 to 65535. To represent Real Numbers, or numbers outside the range above, we have to program the CPU to do so. Character strings are available with a little programming, and letters are stored as numbers in the memory. Programming the CPU to handle real numbers is quite a job.

### Integers

Integers, or whole numbers, are easily dealt with by the CPU provided that they're in the range 0 to 65535.

### Signed Integers

These are integers which can be negative. Thus -1 is a signed integer. Like all numbers in the computer, the CPU sees the numbers as collections of 1s and 0s. We need a means of telling the CPU whether a number is negative or positive, just as we use '+' or '-' in normal arithmetic. The most commonly used method of representing the sign of a number is where we use the most significant bit of the number to represent the sign. If such a number is negative, then the MSB is set to 1 and if it's positive then the MSB is set to 0. Thus for an 8 bit number. we've got bits 0 to 6 in which to represent the value of the number and bit 7 to represent the sign of the number. Bit 7 is often thus called the SIGN BIT of an 8 bit number. The resultant 7 bits don't hold values in the range 0 to 255 any more. Instead, half the numbers represented will be below 0 (sign bit set to 1) and half above 0 (sign bit set to 0). The new range of numbers represented will be -128 to +127. This gives us a problem; for any 8 bit number, how do we tell whether an 8 bit number is a negative number or a large positive number?

The answer is that we don't. It depends purely upon what interpretation the programmer puts on the numbers at any time. The machine code instructions don't care what interpretation we put on them, but the interpretation we put on the result of such operations depends upon the representation used. Producing a negative number is not, however, just a matter of setting bit 7 to 1. We must also alter the way in which the lower 7 bits of the byte hold the value of the number. The fundamental thing to remember about a negative number is that if you add it to the corresponding positive number you get zero. E.g.

(+1) + (-1) = 0

d

e

S

r

y

9

e

Thus the binary representation of -1 must be such that when it's added to +1 the result is zero.

#### 0000001

+ 1???????

#### 00000000 desired result

If we represented -1 by 10000001, then by binary addition we'd set bit 0 of the answer to 0 (1+1=0 carry 1 in binary) but what about the other bits?

00000001

+ 10000001

#### 10000010 actual result

Well, this isn't the correct result. We really need to take the carry that was generated by the addition of 1+1 and use it to somehow set all the other bits in the result to zero. This requires that all the bits in the binary representation of -1 be set to 1.

0000001

+ 11111111

00000000

Well, this is the correct answer for -1, but we must really try to work out some general rule that allows up to work out the representation of a negative number. Well, let's start with -1. The representation of -1 above was obtained in two stages:

1. Replace all the 0s in the the positive number with 1s and all the 1s in the postive number with 0s. The number is thus:

#### 00000001 goes to 11111110

This process is called COMPLEMENTING a number. the complement of 1 is 0 and the complement of 0 is 1.

2. Add 1 to the result of complementing.

#### 11111110 + 00000001 = 11111111

The only way to see if this method gives us a true binary representation of a negative number is to try applying it to other numbers. Let's see if it works on the number -2.

1. Complement the number +2. This gives us:

00000010 goes to 11111101

2. Now add 1 to this:

#### 11111101 + 00000001 = 11111110

This should be the correct representation of -2. To see if we're right, let's add this representation to +2:

- 00000010

- + 11111110

#### 00000000

Yes, that's correct, as we get the result zero. This method of representing a negative number in binary is called the **TWOS COMPLEMENT** representation. It's the most common form of representation of negative numbers. If you apply the methods to a negative representation, then you'll get the positive number back. This isn't really surprising once we remember that two minuses make a plus. So far, we've only applied this to 8 bit numbers. However, it works just as well with 16 bit numbers When we use twos complement notation to represent negative 16 bit numbers, the MSB of the high byte is the sign bit rather than bit 7. The complementing operation is just the same. When we use a 16 bit number in this way, the range of numbers that can be represented is -32768 to +32767 instead of the usual 0 to 65535.

### Characters and Strings

We rely on textual information a great deal, and so it's important that we should be able to represent letters in the computer as well as numbers. Well, all that we do is allow each character, which is a letter, number or anything else that we can display on the screen of the 128 with a PRINT command, to be represented in the computer by a number. Again, it's a case of what the programmer wants a particular number to be. The limit of 255 different characters available to the Spectrum 128 is due to the fact that the characters are stored as single byte numbers in memory. To ensure that we all maintain our sanity, the numbers used to represent particular characters have been standardised, so that in different computers we use the same numbers to represent the same characters. The most popular code used is called ASCII, which stands for 'American Standard Code for Information Interchange' - quite a mouthful. As an example, the code for 'A' is 65 and that for 'a' is 97. To find out the code for a particular character, just type in PRINT CODE a\$, where a\$ holds the character of interest.

## Summing Up

You can thus see that to a large extent the meaning of a particular number in a memory location in the computer depends upon what the programmer wants it to represent. A byte can be:

- 1. A machine language instruction.

- 2. A number in the range 0 to 255.

- 3. A number in the range -128 to 127.

- 4. Part of a 16 bit number or a multi byte instruction.

- 5. A character code.

It is thus important for the programmer to keep an eye on what he uses different parts of the computer memory for. For example, the CPU might try and treat the bytes making up the message 'Hello There!' as a program! This would result in a very confused CPU.

Well, having seen what machine code instructions are, and how computers count, it's about time we looked at the memory of the Spectrum 128 in more detail and find out exactly how we can enter machine code programs into memory.

all paintenes

# Chapter 3 Machine Code and BASIC

In this Chapter we'll look at how we can enter machine code programs into the computer, and see where in the machine we can store the programs that we write.

When we turn the Spectrum on, the BASIC interpreter begins running and expects us to enter BASIC commands or programs. Therefore, whenever we type in machine code, somewhere along the way is going to be at least 1 BASIC command, even if it's just the instruction to tell BASIC to run our machine code program rather than the BASIC Interpreter.

## **Homes for Bytes**

The machine code programs that we'll deal with are all made up of sequences of bytes representing machine language instructions. Therefore, one of the first things to do is to find a place in the computer memory where these bytes can be stored without them being altered in any way.

For programs that we are writing, it's clear that this has got to be in RAM; remember that we cannot affect the values held in ROM. Although there's a good bit of RAM in the Spectrum, some of it is used by the Spectrum BASIC Interpreter and are unsuitable for our machine code programs. Such areas are

those used for the storage of your BASIC programs or variables. the screen image, or areas used by the Z80 as 'scrap paper' while it executes the BASIC Interpreter program. Any machine code programs placed in these areas are thus prone to being overwritten by the BASIC program as you add more lines or create more variables, by the images we put on the screen or by the Z80 as it executes the OS programs. These areas of memory that are used by the CPU to perform its normal tasks are collectively called WORKSPACE. If we alter workspace locations, there is a good chance that we could alter some of the information that is required by the CPU to execute the programs properly. The Z80 would then, not surprisingly, lose track of what it was doing and 'crash'. This is as unpleasant as it sounds, the CPU going out of control. The results of a crash are usually the computer resetting itself, with the subsequent loss of anything in the machine. Alternatively, it might just sit there, keyboard not operating, screen not changing, until you put it out of its misery by pulling the power plug. This, by the way, is often called the 'Sinclair RESET'!

The moral of all this is that when we're playing with machine code, it's a good idea to save programs to tape or microdrive before running them. That way, if we crash we can get back the material that was in the machine and correct the problem without us having to retype the whole lot in.

When you start programming in machine code, you will have a few of these crashes as you get used to programming. This is because, compared to BASIC, machine code is very unforgiving with mistakes. You can't enter a 'dud' line of BASIC into the Spectrum, but machine code offers you no such 'Syntax Checks'. In addition, whereas errors such as 'No such variable' in BASIC are indicated to the programmer who can then correct the problem, no such niceties exist in machine code. If you are lucky, then the unexpected will happen when you make a mistake in your programming; if you're unlucky, then a crash can be the result.

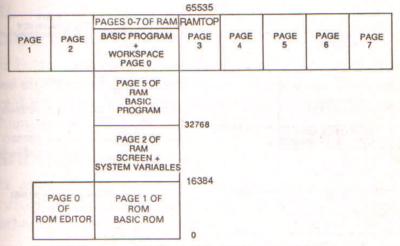

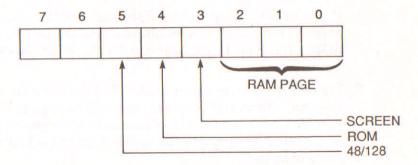

Anyway, let's get back to the problem of finding somewhere to put our machine code programs. The parts of memory that are used by the Spectrum BASIC Interpreter are shown in Figures 3.1 and 3.2. These MEMORY MAPS simply show which bytes in the computer memory are used for what purpose. As you can see, some addresses in the memory, such as those between 0 and 16384, are occupied by two different pieces of memory! This is how we can fit the computing 'quart' of 128k of memory, into the 'pint pot' of the Z80, which should only be able address 65536 different locations in memory (addresses 0 to 5535). This sharing of address space is called PAGING, because it's similar to the pages in a book; the pages occupy the same space on the desk but you can look at many different pages simply by turning them over.

Figure 3.1 Simplified Memory Map.

We'll take a closer look at this in a later Chapter. All that we need to know at the moment is that when we are running a BASIC program, or in 48k mode, the BASIC Interpreter ROM is 'paged in' and is used by the CPU. When we are editing a program in 128 mode then the Editor ROM is in use. However, when a BASIC program is being run in 128 mode the BASIC ROM is active again.

RAM is also paged in the Spectrum 128; there are 8 'pages' of RAM, all of which contain 16384 bytes of memory. They are all paged in to the top 16384 bytes of the memory map, as can be seen from Figure 3.1. Just to complicate matters a little, two of these pages, Page 2 and Page 5, are also 'paged in' to other places in the memory map, as can be seen. They are used for the screen and BASIC program storage. Again, we'll look at RAM paging in a later Chapter. For now, just be aware that normally we are using pages 0,2 and 5 of RAM, page 0 occupying the top 16384 bytes of memory and the others being used where indicated in Fig. 3.1. However, when we're using the BASIC Editor in 128 mode, page 7 of RAM is used instead of Page 0. We also use the paged RAM when we use the SAVE !, LOAD ! etc. commands to use the 'silicon disc' facility of the computer.

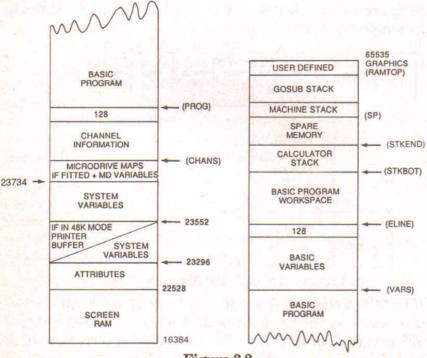

Let's examine the maps in a little more detail. The addresses are in decimal, or are indicated as **LABELS**. These are such things as (PROG) or (VARS). These names refer to places in the memory that hold the actual address of the start of the BASIC program (PROG) or of the start of the area of memory that is used to store the BASIC variables in (VARS). The reason why these values need to be stored in the workspace is simply that the exact position in memory where, for example, the variable storage starts depends on the length of the program, amongst other things. So, the CPU keeps an eye on how things are going and updates the stored addresses when it needs to. Thus, if we add another line of BASIC to a program, the value held in the the memory locations used to store VARS will be changed. All these 'labels' are stored in the area of memory called 'System Variables' in Figure 3.2. There are many of these, some of which we can make good use of in our programs. The more useful of these we'll look at later in the book. For now, just treat the system variables as 16 bit numbers that represent a particular address in the computer memory map, or represent certain facts about the BASIC Interpreter to the CPU.

## Screen Memory

This is the area of memory used to hold the bytes that tell the video circuitry of the computer what to put on the screen. It's over 6000 bytes long, and is arranged in a slightly peculiar fashion, as we'll later see.

## Attributes

This area of memory holds the information for the video circuitry about the colour of different things on the screen, whether they are flashing, and so on.

## **Printer Buffer**

In 48k mode, this is used by the Operating System to allow information to be sent to the ZX Printer. A line at a time of text is formed here and it's then sent to the printer. In 128 mode this area is used to provide space for the extra system variables needed to run the keypad, handle the serial interface and so on. In 48k mode, if you're not using a printer, therefore, you can use the printer buffer space for short machine code programs.

## **System Variables**

This area of memory holds the System Variables and is totally OFF LIMITS for the storage of machine code programs!

## **Microdrive Maps**

This area of memory doesn't always exist, depending upon whether you've got Interface 1 fitted and microdrives in use. When it does exist, it's used to give the Operating System an idea of the way in which different parts of the microdrive tape have been used.

## **Channel Information**

This area of memory holds the information necessary for the BASIC Interpreter to use the screen, keyboard, and, where possible, the ZX printer. This finishes with a byte holding the value 128.

## **BASIC Program**

This is stored from the address in (PROG) onwards. After the program we have the area of memory devoted to the BASIC variables, and the start of the variable area of memory is held in System Variable VARS. A useful application of these two system variables is to get the length of the program. This is done by subtracting the value of PROG from that or VARS. PROG is held in bytes 25635 and 23636, low byte first. VARS is stored in addresses 23627 and 23628, again low byte first. The end of the variables area is marked by a byte containing 128, and this is followed by the BASIC program workspace.

## **The Calculator Stack**

The Spectrum ROM contains a lengthy program called the **Floating Point Calculator.** This is used when the CPU needs to do complex arithmetic, such as multiplication, doing sines and cosines, etc. This 'stack' is used for temporary storage of results calculated by the Floating Point Calculator.

## **The Machine Stack**

This is the stack pointed to by the Stack Pointer.

## The GOSUB Stack

This stack is used to store the return addresses for BASIC GOSUBs. The information held on this stack tells the BASIC interpreter where to go when a RETURN instruction is encountered in a BASIC program.

## RAMTOP

This is the last byte of memory available to BASIC. Anything above this isn't affected by the BASIC program. We can 'move' this address around in memory, though we must use care. Setting RAMTOP too low, for example, will lead to a 'memory full' error, even though there will be many k of memory above RAMTOP. Usually, the only thing above RAMTOP are the definitions of the User Defined Graphics characters, accessed by USR("a") and so on. However, if we move RAMTOP down, we have some 'spare space' between RAMTOP and the definition of the User Defined Graphics. This space is protected from incursions from BASIC, and so would make a great place in which to put our machine code. That is in fact what we do. This is the 'official' method of generating space in the Plus2/128 for machine code. To set RAMTOP to a particular value, we issue a special form of the CLEAR command:

CLEAR nn

where nn is a 16 bit address which specifies the last available byte to BASIC. Thus the command:

#### CLEAR 39999

will set RAMTOP to address 39999 and the first protected byte is one after this; i.e. 40000. Thus all the memory from 40000 to the start of the UDG definitions would be available for machine code. This command should be one of the first you issue when programming, and it stays in force until you issue another CLEAR nn command, or until you reset the machine or change from 48k to 128k mode or vice versa.

While we're talking about memory, let's introduce a little more jargon that you may encounter. It's a problem with memory that we tend to end up talking about long strings of numbers when describing the quantity of memory possessed by computers. For example, the Z80 can address 65536 different locations of memory. To cut the numbers down, we say we've got 64k of memory, where a 'k' is 1024 bytes of memory. So, 2048 bytes are 2k, and 1/2k is 512 bytes of memory. The reason why a computer 'k' is 1024 and not 1000 is that 1024 is a whole number power of 2; 1000 isn't.

So, now we've seen how we can store our bytes in memory, safely above RAMTOP, can we put them there in the first place? Also, can we look at the contents of memory locations from BASIC? The answer to these questions is 'yes' in both cases.

## **POKE and PEEK**

When we want to put a byte into a particular memory location we use the rather descriptively named POKE command. This is exactly what it does; it POKEs, or puts, a value into a particular memory location. It's used in the following fashion:

POKE address, value

The address must be in the range 0 to 65535, and the value must be in the range -255 to +255. If this isn't so, then an error will be reported. 'address' is the address of the memory location into which we want to put the 'value'. If the address isn't a RAM location, then the value will obviously NOT be inserted; you can't alter ROM! Take care with POKE, though; don't alter the System Variables unless you're very sure you know what you're doing. Thus the command:

### POKE 40000,201

will put the value 201 into address 40000. So, we can use POKE to put the bytes that represent our machine code program into memory. What about looking at the bytes once they're there? This is done by using the PEEK command, which allows us to look into a memory location, whether it's ROM or RAM. As PEEK is a function, we can PRINT its value out or assign its value to a variable.

#### PRINT PEEK(address)

will print to the screen the value held in the byte at address 'address'. Similarly,

LET a=PEEK(address)

will put the value in byte 'address' into variable 'a'.

Thus if we're in BASIC these two commnds will form the very heart of our attempts to input machine language routines in to the Spectrum memory.

## **USR(address)**

Of course, once we've got the bytes into memory, we really want to be able to run the program that they represent. This is done by using another function called USR(address), which stands for USer Routine. When we use it, by, for example,

### PRINT USR(address)

### RANDOMIZE USR(address)

then the machine code routine represented by the bytes starting at address 'address' will be executed by the Z80. USR tells the CPU to leave the BASIC Interpreter and execute another program. When we are in a program called like this, we're 'on our own'; there is no error trapping and no break key. Thus:

### PRINT USR(0)

will run the machine code routine that starts at address 0. This will reset the computer.

What about swapping information between BASIC and machine code? Well, there's no immediately obvious method of transferring information from BASIC variables to machine code routines, but on returning from a USR routine the BC register contents are passed back to BASIC. Thus in a statement such as PRINT USR(40000), the value printed to the screen would be the value that was in the 16 bit BC register pair when the machine code routine finished. Thus it is easy to pass back some information to BASIC in the BC register pair. As to other methods of making BASIC variables available to machine code, or passing information back to BASIC programs in the variables, see Chapter 13.

The simplest method of passing numbers to and from BASIC, though, is to use POKE and PEEK in the following way. POKE is used to load bytes of memory with values to be accessed by a machine code program. The machine code program can then load registers with these values, and use them in the program. The result can then be stored in the memory locations for PEEK to recover after the routine has been executed. Alternatively, we can use the BC register pair to return values to BASIC.

## Saving Bytes on Tape

You will occasionally want to store the bytes that represent a machine code program on tape; the easiest way to do this is to use the SAVE "filename" CODE address, length command from BASIC. 'address' is the start address of the area of memory to be saved and 'length' is the number of bytes to be saved. For example:

### SAVE "fred" CODE 40000,100

will save the area of memory between 40000 and 40099. (100 bytes, including the byte at address 40000).

## Loading Bytes from Tape

We use the LOAD "filename" CODE address, length command from BASIC to do this. 'address' is the address to which we want the bytes to be saved, and 'length' is the number of bytes that are to be loaded in from tape. The 'length' parameter isn't compulsory, but is useful if you have a number of files with the same name but different lengths on the same tape (very bad practice!!!).

## **Entering Bytes**

0

0

3

There are three main methods by which we can enter bytes representing machine code programs in to the program:

- 1. Use an assembler program, which will allow you to type in the machine code programs in their mnemonic form.

- 2. Use a MONITOR program, which is a program in either BASIC or machine code that allows you to enter the bytes into memory in decimal or hexadecimal, and allows easy listing and editing of bytes in memory. Complex monitors also allow 'single stepping' of your machine code programs; here, the computer stops after executing each instruction in the program and displays the contents of the registers after that instruction.

- 3. Put the bytes into a DATA statement and then write a short BASIC program to POKE the bytes into memory. This is quite useful for the routines in this book, as the bytes can be entered, the BASIC program saved on tape and then the program run to enter the bytes into memory. USR can then be used to test the program.

The program to deal with (3) above can be quite simple:

- 10 CLEAR 39999

- 20 LET address=40000

- 30 READ byte

- 40 IF byte=999 THEN STOP

- 50 POKE address, byte

- 60 LET address=address+1

- 70 GOTO 30

- 80 DATA data representing the program.

The bytes are entered into the DATA statement just like any other data, each number being typed in followed by a ','. After the last byte of the machine code program type in the value '999' as the last item in the data statement to tell the program where the end of the machine code is.

Well, we're now ready to look at some instructions that the Z80 can understand. Before we do so, though, a look at an instruction that's probably the most useful you'll use; it allows you to get back to BASIC from your machine code program. The instruction is called:

#### RET

which is short for RETURN. This is the equivalent of the BASIC RETURN command, which we use to finish subroutines off. Whereas forgetting a RETURN in BASIC will usually generate an error message, forgetting a RET in machine code will often result in a crash!

# Chapter 4. Registers at Work

Well, we're now ready to look at some machine code instructions. It's probably clear to you by now that we can't do much programming of the CPU until we can get some numbers into the CPU registers, and transfer these numbers between the CPU registers and the memory of the computer. So, in this chapter we'll look at the instructions that are available to us to allow us to move 8 bit numbers between different CPU registers and the memory of the computer. We'll look at how to deal with 16 bit numbers in a later chapter.

There's a little jargon to deal with here. When we are transferring data from one register to another register, or between memory and registers, the register which originally held the data is called the **SOURCE REGISTER**. That to which the data is going is called the **DESTINATION REGISTER**. Similar terms are used when we're transferring data between registers and memory. It's common to say that we LOAD a register from memory, or LOAD memory from a register. Indeed, the mnemonic that is used for these data transfer instructions, LD, is short for LoaD.

At this stage, it's important to realise that on the whole we COPY data from one register to another; after any of these operations, the destination AND the source registers hold the contents of the source register before the operation. The designers of the CPU gave us a variety of different ways in which we can use the CPU. This isn't meant to confuse machine code programmers, but is intended to provide us with methods of solving problems that are both fast and convenient, as we'll later see. The ways in which the CPU is able to transfer data are known as the **ADDRESSING MODES** of the CPU, and virtually all the instructions in the Z80 instruction set can operate in at least one of these addressing modes.

I'll look at the addressing modes with respect to the LD instructions, although they're applicable to other instructions, as we'll later see. From now on we'll write our machine code programs down in the form of mnemonics. If you're using an assembler, then you'll be able to type in the programs as you see them. Otherwise, you'll have to hand assemble them, using the tables in the back of the book. To help you out, some of the first programs in this book will have the listings of machine code instructions ready assembled for you to enter into memory, as we saw in Chapter 3. So, let's get on with Addressing Modes.

## **Register Addressing**

This is probably the simplest mode of all; it is used for operations involving two registers. With LD operations, therefore, this mode is used when data is being copied between two CPU registers. An example of this addressing mode is:

### LD A,B load A from B

which simply copies the contents of the B register (source) into the A register (destination). The contents of the B register are totally unaffected by the transfer operation, but whatever was originally in A is lost forever as they are overwritten by the contents of the B register. There is a 'general way' of writing down such Register Addressing mode instructions. This is:

LD r1,r2 load r1 from r2

where r1 is the destination register and r2 the source. They can be any 8 bit register except for F. Each of these instructions is represented to the CPU by a single, 8 bit, number. For example, the instruction:

#### LD A,C load A from C

is represented by the number 121. There are many such transfer commands, as you'll see if you look at the tables in the back of the book. These Register Addressing mode transfers are similar to BASIC commands of the form:

#### LET A=B

They are clearly very useful, but only if we've been able to get something into the source register in the first place!

### Immediate Addressing

This mode solves that problem. It allows us to carry out an operation on an 8 bit number specified as part of the instruction. In this case, the mode allows us to load a register with a given 8 bit number. This type of instruction will thus need two bytes to represent it; one for the instruction, and a second byte to represent the number in use. The first byte, as well as indicating the fact that it's an immediate mode instruction, also lets the CPU know what register is needed. The general format of these instructions is:

LD r,n load register r with value n where 'r' is an 8 bit register, with the exception of F, and 'n' is

the number to put in that register. A more specific example is:

LD A,23

which will put the value 23 into the A register. This is represented by the two bytes:

#### 62 23

The 'LD A,n' instruction is represented by the number 62, and goes in to the computer memory first, followed by the data byte, which in this case is 23. These two bytes are given special names; the instruction byte is called the **OP CODE** or **INSTRUCTION CODE**. OP CODE is short for OPeration Code. The second byte is called the **OPERAND**, which simply indicates that it is the number to be operated on by an instruction. Thus, Immediate Addressing allows us to load the CPU registers with particular values. So far we've only looked at addressing modes that allow us to access the CPU registers. What about memory? We'll now look at addressing modes that permit us to use memory in our transfers.

## **Register Indirect Addressing**

Things now begin to get a little more complicated, but the instructions using this addressing mode are very powerful indeed. Data is transferred between the CPU registers and memory, using the BC, DE and HL register pairs to hold the address of the place in memory which is to be involved in the data transfer. We'll look at how we can set up the 16 bit register pairs to hold the address later in the book, but for now we'll just look at the transfers possible with them. The general way of writing these instructions is:

| LD | A,(rr) |

|----|--------|

| LD | (rr),A |

| LD | (HL),n |

Here, 'rr' indicates one of the register pairs and 'n' is an 8 bit number. There are a couple of points to note with regard to these instructions.

- 1. The brackets surrounding the register pair indicate that we are interested in the CONTENTS of the register pair. This is true in all Z80 operations. Whenever we see the brackets, we must remember that we're interested in the contents of the register pair or memory address that is in the brackets.

- 2. The HL pair is already showing its versatility over the other 16 bit register pairs. We can load a memory location whose address is in the HL register pair directly with an 8 bit number. To do the same job with the other register pairs it's necessary to put the number in to the A register first.

This method of using the HL register to directly load a memory location with a number is given a special name. It's an addressing mode called, wait for it...'Register Indirect Immediate Addressing'. You can probably see that the Immediate part of the name comes from the use of a number in the instruction ('n'), and the Register Indirect part comes from the fact that the address is held in the HL pair.

The Register Indirect Addressing instructions just seen need a single byte to represent them, with the exception of LD (HL),n, where a second byte is required to hold the value of 'n'.

Using the instructions we've seen so far, let's write a piece of machine code to transfer the contents of memory location 40000 to location 40001. Before we start, the only thing to note is that when we're using the Register Indirect Addressing instructions the high byte of the address is held in the high register of the pair (B, D or H) and the low byte of the address is held in the low register of the pair (C,E or L). The low and high bytes of the address can be worked out in the following way:

- 1. Calculate INT(address/256). This is the high byte of the address.

- 2. Calculate address 256\* (INT(address/256)). This is the low byte of the address.

Listing 4.1 shows the program to transfer the data from 40000 to 40001. In addition to the mnemonics, the decimal numbers representing the instructions are listed.

| LD  | H,156  | 38,156 |

|-----|--------|--------|

| LD  | L,64   | 46,64  |

| LD  | A,(HL) | 126    |

| LD  | H,156  | 38,156 |

| LD  | L,65   | 46,65  |

| LD  | (HL),A | 119    |

| RET |        | 201    |

#### Listing 4.1

Let's look at what each instruction does. The first two load the address 40000 into the HL register pair. The low byte of the register is loaded into L and the high byte into H. Then A is loaded from the address held in the HL register pair, in this case 40000. The HL pair is then set up to hold 40001, which is the address we want to transfer the data to. The contents of A are then written into address 40001. The final instruction, RET, brings us back to BASIC. The below BASIC program will enter the bytes into memory at address 40002. Line 10 reserves the memory, and the program is run by POKEing a number into address 40000, RANDOMIZE USR 40002, then PRINT PEEK 40001 to see if the value has been transferred. This might seem a rather trivial example, but demonstrates the basic principles of entering a small machine code program into the Spectrum 128/Plus 2.

- 10 CLEAR 39999

- 15 RESTORE 100

- 20 FOR i=0 TO 10

- 30 READ a

- 40 POKE (40002+i),a

- 50 NEXTI

- 60 STOP

- 100 DATA 38,156,46,64,126,38,156,46,65,119,201

It's clear that things would be a little easier if we could have loaded the A register from a memory location without having to put the address of the memory location of interest into the HL pair. Well, the CPU does provide us with an addressing mode to do this.

## Extended Addressing

These commands are of the form:

| LD | A,(nn) |

|----|--------|

| LD | (nn),A |

where 'nn' is a 16 bit number that represents the address of a location within the computer memory. Typical instructions using this addressing mode might be:

LD A,(40000) LD (40001),A

These two instructions could obviously be use in listing 4.1 to transfer the data from 40000 to 40001. As you'll probably remember, the 16 bit numbers are stored in two bytes in the memory. The instruction also needs a byte to represent it, so these instructions are three bytes long. The command:

LD A,(40000)

is represented by the three numbers:

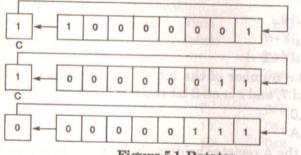

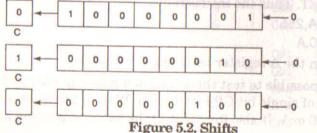

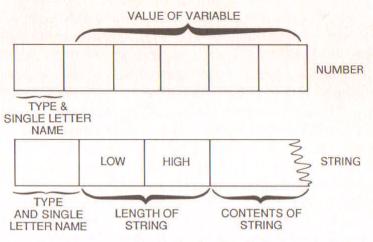

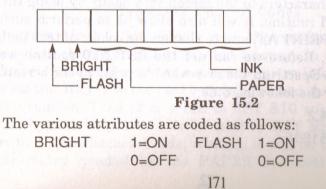

58, 64, 156