# Programming the 8086 8088 JAMES W. COFFRON

# PROGRAMMING THE 8086/8088

Cover art by Jean Francois Penichoux Design and layout by Ingrid Owen

8086 and 8088 are trademarks of, and all mnemonics are copyright by, Intel Corporation. IBM PC is a registered trademark of International Business Machines, Inc. Sybex is not affiliated with any manufacturer.

Every effort has been made to supply complete and accurate information. However, Sybex assumes no responsibility for its use, nor for any infringements of patents of other rights or third parties which would result.

©1983 SYBEX Inc. 2344 Sixth Street, Berkeley, CA 94710. World rights reserved. No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including but not limited to photocopy, photograph, magnetic or other record, without the prior agreement and written permission of the publisher.

Library of Congress Card Number: 83-50228 ISBN 0-89588-120-9 First Edition 1983 Printed in the United States of America 10 9 8 7 6 5 4 3 2 1 To Bill Long

# **CONTENTS**

| Ackr  | nowledgements                                                                                                                                                                                                                                                                                                                                            | х  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Intro | duction                                                                                                                                                                                                                                                                                                                                                  | xi |

| 1     | <b>BASIC CONCEPTS</b><br>What Is Programming? 2<br>Flowcharting 3<br>Information Representation 4                                                                                                                                                                                                                                                        | 1  |

| 2     | INSIDE THE 8086/8088<br>General Microprocessor System Architecture 28<br>Inside a Microprocessor 30<br>The General Instruction Cycle 34<br>Internal Organization of the 8086/8088 37<br>8086/8088 General Registers 39<br>Additional Control Flags 42<br>Summary 43                                                                                      | 27 |

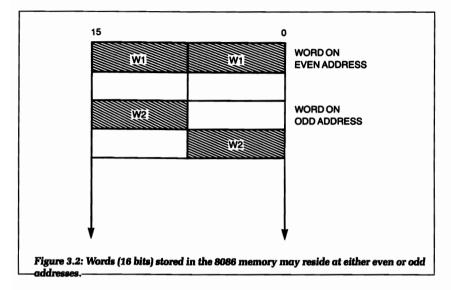

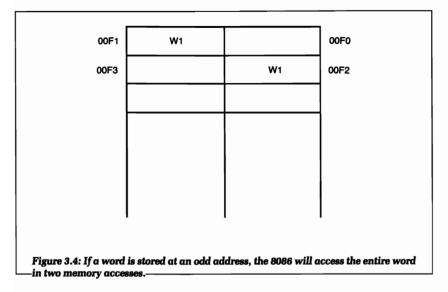

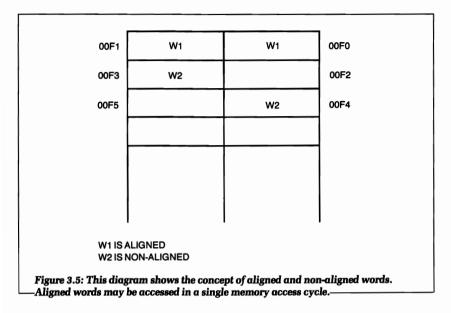

| 3     | 8086/8088 MEMORY ORGANIZATION<br>AND ADDRESSING MODES<br>System Memory Organization of the 8086 48<br>Aligned and Non-Aligned Words 51<br>System Memory Organization of the 8088 52<br>Address Generation with the 8086/8088 52<br>8086/8088 Object Code 58<br>Object Code for Indexing and Base Register Use 62<br>Object Code Summary 62<br>Summary 63 | 47 |

| 4 | THE INSTRUCTION SET:<br>INDIVIDUAL DESCRIPTIONS                                                                                                                                                                                                                                                                      | 65  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5 | BASIC PROGRAMMING TECHNIQUES<br>Arithmetic Programs 176<br>BCD Arithmetic 180<br>Subroutines 188<br>CALL-RETURN Mismatch 191<br>Summary 193                                                                                                                                                                          | 175 |

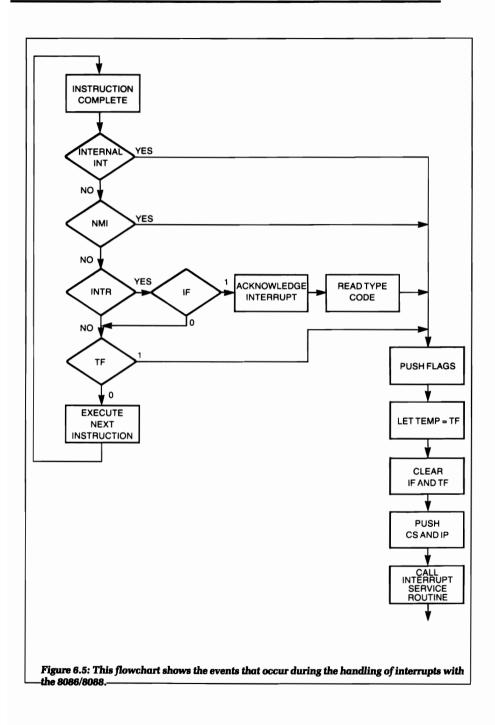

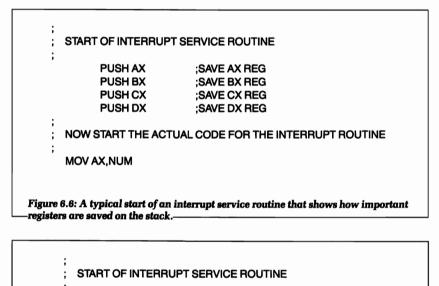

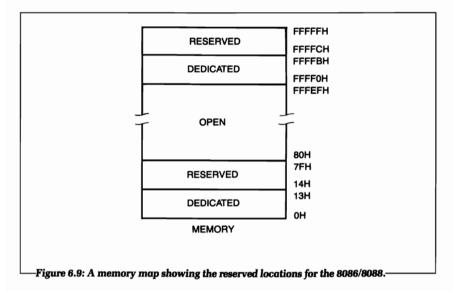

| 6 | INTERRUPTS FOR THE 8086/8088<br>What is an Interrupt? 196<br>CPU Activity During the NMI Request 198<br>The Interrupt Table 199<br>INTR Input 202<br>Internal Interrupts 203<br>Resetting the 8086/8088 206<br>Summary 208                                                                                           | 195 |

| 7 | INPUT/OUTPUT FOR THE 8086/8088<br>What is Input and Output? 212<br>I/O Addressing 213<br>Input Instruction 216<br>Output Instruction 218<br>8086 Input and Output Ports 219<br>8088 Input and Output Ports 219<br>Using an 8255 PIO Device with the 8086/8088 224<br>Example of Keyboard Scanning 232<br>Summary 238 | 211 |

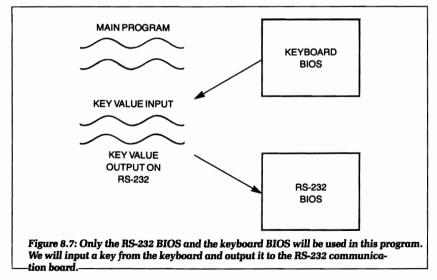

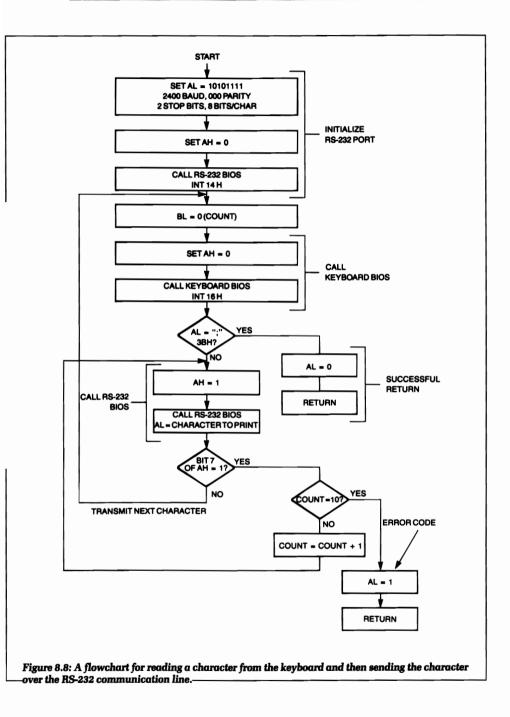

| 8 | MORE APPLICATIONS USING THE IBM<br>PERSONAL COMPUTER<br>BIOS (Basic I/O System) 242<br>BIOS Advantage 242<br>Accessing Peripherals Using the BIOS 243<br>Preamble for the Printer I/O 246<br>Keyboard Preamble 253<br>RS-232 Preamble 256                                                                            | 241 |

vii

Program Definition 258 Summary 261

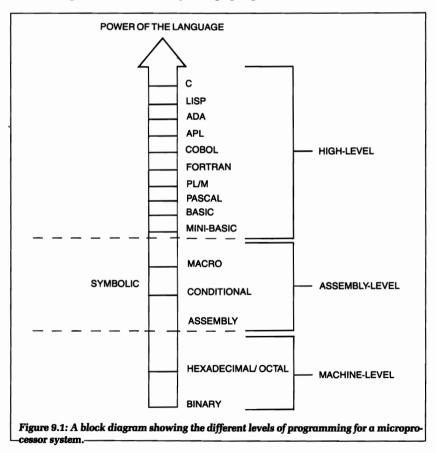

# **9 PROGRAM DEVELOPMENT**

263

Programming Choices 264 The Software Development Sequence 268 Hardware Alternatives 269 Summary of Hardware Resources 271 The Assembler 271 The Assembly Language 275 Summary 279 Conclusion 279

Index

306

# **ACKNOWLEDGEMENTS**

I wish to thank Bob Schuchard and Richard King, for their review and helpful suggestions; and my wife Carol, for preparing the original diagrams. Finally, a hearty thanks to the entire staff at Sybex for their splendid efforts.

# INTRODUCTION

Welcome to the exciting world of 16-bit microprocessors. Imagine yourself programming, controlling, and using one of the most powerful and versatile 16-bit microprocessors: the 8086. This microprocessor can access over ONE MILLION memory locations—a far cry from the 64 thousand available in the majority of 8-bit microprocessors.

The 8086 is one of the most widely-used, 16-bit microprocessors in industry today. It has an extremely powerful instruction set that allows you to make your own software application a reality. In fact, the 8086 has two instructions that allow you to directly multiply and divide numbers; thus lengthy algorithms are no longer required to perform these tasks.

As you learn how to program the 8086, you will also be learning how to program the 8088 microprocessor. These two processors have identical instruction sets, and software written for one can be run on the other with no changes.

Both the 8086 and 8088 are well suited for communication with I/O devices and I/O ports. In fact, their architecture can support over 64,000 unique input and output ports. These ports can be any combination of 8 or 16 bits wide!

In addition, the 8086 and 8088 offer a powerful interrupt scheme, which allows you to vector to any system address for service routines. There are special interrupt vectors for single stepping and for internal errors, such as division by zero. Further, any of the interrupt service routines can be evoked via hardware or software.

The 8086 and 8088 are designed for ease of use in multiprocessor system applications. In light of this, Intel Corporation has designed several co-processors for use with the 8086/8088.

The preceding topics and more will be covered in this text. You will learn to program the 8086/8088 inside and out. From the internal microprocessor architecture to the advanced addressing modes, you will be shown how it all works. Each instruction will be described and several examples of actual programs will be given. To add more "real world" explanation, we will actually present examples of programs written for the IBM® PC, that use the 8088 microprocessor.

So, whether you are a beginner in microprocessor assembly-language programming or an advanced programmer, there is something for you in this text. After reading this book, you should be able to program the 8086/ 8088 for any application. In addition you should find that the text will serve as a valuable reference later on. So let's get going! Let's start down the path that will lead you to an understanding of the power contained in one of the most advanced 16-bit microprocessors in use today.

### CHAPTER BREAKDOWN

**Chapter 1** starts off with a review of the basic concepts of microprocessor programming. It covers number representation, the addition and subtraction of binary and BCD numbers, and the use of flags.

**Chapter 2** describes in general, the internal structure of a microprocessor; and discusses, in particular, the internal registers of the 8086/8088. An in-depth discussion focuses on the differences and similarities between the 8086 and 8088, and microprocessors in general.

**Chapter 3** details the physical memory organizations of the 8086 and 8088 microprocessors—and shows that they are completely different. In addition, this chapter examines the different addressing modes for the various instructions.

**Chapter 4** is a big one. It gives a complete listing of each instruction for the 8086/8088 and provides the relevant information pertaining to each instruction.

**Chapter 5** discusses the basic programming techniques for microprocessors—addition, subtraction, multiplication, and division—and shows how these techniques are accomplished using the 8086/8088 instructions.

**Chapter 6** discusses the general topic of interrupts for a microprocessor system and describes the complete interrupt structure for the 8086/8088. By the end of this chapter you will have a good understanding of how interrupts are used with these CPUs.

**Chapter 7** covers the input and output techniques for the 8086/8088. Various input and output instructions are discussed and their uses examined. Included are programs for controlling an 8255 PIO and an 8253 counter timer LSI device.

**Chapter 8** gets into "real world" applications. It shows you how to use the information on the 8088 to control the IBM PC. Two different application programs are given. Each uses the IBM BIOS to control the printer, the keyboard, and the RS-232 port.

**Chapter 9** explores various program development techniques. Development hardware is evaluated and trade-offs are discussed. The chapter concludes with a discussion of assembly language details which you will be needing to write programs for the 8086/8088 CPU.

Also included are four useful appendices. **Appendix A** is a hexadecimal conversion table. **Appendix B** is an ASCII conversion table. **Appendix C** is a decimal-to-BCP conversion table. **Appendix D** is an 8086/8088 instruction set summary.

**BASIC CONCEPTS**

# INTRODUCTION

1

We shall begin with a discussion of the basic concepts and definitions used in computer programming. If you are already familiar with these concepts, you may only want to glance quickly at the contents of this chapter and then move on to Chapter 2. We do suggest, however, that even if you are an experienced programmer, you read through this chapter in order to familiarize yourself with the approach used throughout this book.

### WHAT IS PROGRAMMING?

Given a problem, one normally tries to devise a solution. When this solution is expressed as a step-by-step procedure, it is called an *algorithm*. An algorithm may be expressed in any language or symbolism. It must terminate in a finite number of steps. Here is a simple example of an algorithm for unlocking and opening a door:

- 1. Insert key in the keyhole

- 2. Turn key one full turn to the left

- 3. Grasp doorknob

- 4. Turn doorknob, and push on the door

At this point, if the algorithm is correct for the type of lock involved, the door will open.

Once a solution to a problem has been expressed in the form of an algorithm, the next step is to translate it into a language that is understood by the computer.

At this point in time, only a well-defined subset of a natural language called a programming language—is "understood" by computers. The conversion of an algorithm into a sequence of instructions comprising a programming language is called programming. The actual translation phase of the algorithm into the programming language is called *coding*. Programming refers not just to the coding, but also to the overall design of the programs and "data structures" that will implement the algorithm.

Effective programming requires not only an understanding of the possible implementation techniques for standard algorithms, but also the skillful use of computer hardware resources (such as internal registers, memory, and peripheral devices) and a creative use of appropriate data structures. (Note: We will examine these techniques in the chapters that follow.)

Programming also requires a strict documentation discipline. Welldocumented programs are understandable not only to the author later on, but also to other users. Documentation must be both internal and external. *Internal program documentation* refers to the comments used in the body of a program to explain its operation. *External documentation* refers to the design documents that are separate from the program, including written explanations, manuals, and flowcharts.

An intermediate step is almost always taken between the design of the algorithm and the creation of the program. This step is called *flowcharting*.

## FLOWCHARTING

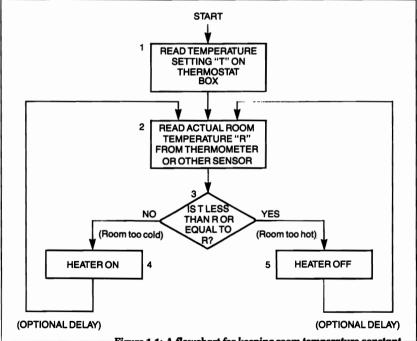

A flowchart is simply a symbolic representation of an algorithm, usually expressed as a sequence of rectangles and diamonds. On a flowchart, rectangles are used to represent *commands*, (or executable statements), and diamonds are used for *tests* such as: If information X is true, then take action A; if not, take action B. Figure 1.1 shows an example of a flowchart. We will not give a formal definition for flowcharts at this point; we will discuss flowcharting in more detail in Chapter 3.

Flowcharting is a highly recommended intermediate step between the specification of an algorithm and the actual coding of a solution. Remarkably, it has been observed that perhaps 10% of the programming population can write a program successfully without having to prepare a flowchart. Unfortunately, it has also been observed that 90% of the population believes it belongs to this 10%! The result, then, is that, on the average, 80% of the programs fail the first time they are run on a computer. (These percentages are naturally not meant to be accurate.) In short, most novice programmers seldom see the necessity for drawing a flowchart. Ignoring

-Figure 1.1: A flowchart for keeping room temperature constant.-

the flowcharting step usually results in an erroneous program, and the programmer must then spend a long time testing and correcting his or her program. (This is known as the *debugging* phase.) The discipline of flowcharting is, therefore, highly recommended in all cases. Flowcharting generally requires a small amount of additional time prior to the coding, and usually results in a clear program that executes correctly within a short period of time. Once the procedure of flowcharting is wellunderstood, a small percentage of programmers can perform this step mentally, without using paper. Unfortunately, in such cases, the programs they write are usually difficult for others to understand, since the documentation normally provided with a flowchart is not available. It is universally recommended that flowcharting be used as a strict discipline for any program more than ten or fifteen instructions long. Many examples of flowcharting are provided throughout this book.

### INFORMATION REPRESENTATION

All computers manipulate information in the form of numbers or characters. We will now examine the external and internal representations of information on a computer.

#### INTERNAL REPRESENTATION OF INFORMATION

Information in a computer is stored as groups of bits. A bit stands for binary digit. Because of the limitations of conventional electronics, the most practical representation of information uses two-state logic. The two states of the circuits used in digital electronics are generally "on" and "off." These states are represented logically by the symbols "0" and "1". Because these circuits are used to implement logical functions, they are called binary logic circuits. As a result, virtually all information processing today is performed in binary format. A group of eight bits is called a byte. A group of four bits is called a nibble.

Let us now see how information is represented internally in this binary format. Two entities must be represented inside the computer: the program (which is a sequence of instructions), and the data on which the program operates. The data may include numbers or alphanumeric text. Let's now discuss the representation of instructions, numbers, and alphanumerics in binary format.

Many of the examples that follow use eight bits. This makes it easier to explain the concept being discussed. The examples can easily be expanded to more than eight bits. **Representing Numeric Data** The representation of numbers in binary is not a straightforward task: several cases must be distinguished. We must be able to represent whole numbers, such as signed numbers (i.e., positive and negative numbers or integers) and numbers with decimal points. Let us now address these requirements and possible solutions.

Integers may be represented using a *direct binary* representation. The direct binary representation is simply the representation of the decimal value of a number in the binary system. In the binary system, the right-most bit represents 2 to the power 0. The next bit to the left represents 2 to the power 1; the next, 2 to the power 2; and the left-most bit, 2 to the power 7, which equals 128. For example,

$$b_7 b_6 b_5 b_4 b_3 b_2 b_1 b_0$$

represents

$$b_7 2^7 + b_6 2^6 + b_5 2^5 + b_4 2^4 + b_3 2^3 + b_2 2^2 + b_1 2^1 + b_0 2^0$$

The powers of 2 are:

$$2^7 = 128, 2^6 = 64, 2^5 = 32, 2^4 = 16, 2^3 = 8, 2^2 = 4, 2^1 = 2, 2^0 = 1$$

The binary representation is analogous to the decimal representation of numbers. For example, 123 represents:

$$1 \times 100 = 100 + 2 \times 10 = 20 + 3 \times 1 = 3$$

Note that  $100 = 10^2$ ,  $10 = 10^1$ ,  $1 = 10^0$ . In this positional notation, each digit represents a power of 10. In the binary system, each binary digit or bit represents a power of 2, instead of a power of 10 as in the decimal system. Let's look at an example of binary. 00001001 in binary represents:

| 1 ×        | 1 = 1   | (2 <sup>0</sup> ) |

|------------|---------|-------------------|

| $0 \times$ | 2 = 0   | (2¹)              |

| $0 \times$ | 4 = 0   | (2²)              |

| $1 \times$ | 8 = 8   | (2 <sup>3</sup> ) |

| 0 ×        | 16 = 0  | (24)              |

| 0 ×        | 32 = 0  | (2 <sup>5</sup> ) |

| 0 ×        | 64 = 0  | (2 <sup>6</sup> ) |

| 0 ×        | 128 = 0 | (2 <sup>7</sup> ) |

|            | or 9    | in decimal        |

Let's look at some other examples. 10000001 represents:

1 x 1 = 1  $0 \times$ 2 =0 4 = 0 x 0  $0 \times 8 =$ 0  $0 \times 16 =$ 0  $0 \times 32 =$ 0  $0 \times 64 =$ n  $1 \times 128 = 128$ or 129 in decimal

Therefore, 10000001 represents the decimal number 129. Examining the binary representation of numbers makes it easy to understand why bits are numbered from 0 to 7, going from right to left. Bit 0 is  $b_0$  and corresponds to  $2^0$ . Bit 1 is  $b_1$  and corresponds to  $2^1$ , and so on. The binary equivalents of the numbers from 0 to 255 are shown in Figure 1.2.

**Decimal to Binary** Conversely, we can compute the binary equivalent of 11 decimal:

$\begin{array}{ll} 11 \div 2 = 5 \text{ remains } 1 > 1 & (lowest \ bit) \\ 5 \div 2 = 2 \ remains \ 1 > 1 \\ 2 \div 2 = 1 \ remains \ 0 > 0 \\ 1 \div 2 = 0 \ remains \ 1 > 1 & (highest \ bit) \end{array}$

The binary equivalent is 1011 (read the right-most column from bottom to top). The binary equivalent of a decimal number can be obtained by continually dividing by 2, until a quotient of 0 is obtained.

**Operating on Binary Data** The arithmetic rules for binary numbers are straightforward. The rules for addition are:

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = (1) 0$$

where (1) denotes a "carry" of 1 (note that 10 is the binary equivalent of 2 decimal). Binary subtraction can be performed by "adding the complement." We will discuss binary subtraction once we learn how to represent negative numbers. Let's consider the following example involving

addition:

| (2)  | 10  |

|------|-----|

| +(1) | +01 |

| (3)  | 11  |

Addition is performed just as in decimal, by adding the columns, from

| DECIMAL | BINARY   | DECIMAL | BINARY   |

|---------|----------|---------|----------|

| 0       | 00000000 | 32      | 00100000 |

| 1       | 00000001 | 33      | 00100001 |

| 2       | 00000010 | •       |          |

| 3       | 00000011 | •       |          |

| 4       | 00000100 | •       |          |

| 5       | 00000101 | 63      | 0011111  |

| 6       | 00000110 | 64      | 0100000  |

| 7       | 00000111 | 65      | 0100001  |

| 8       | 00001000 | •       |          |

| 9       | 00001001 | •       |          |

| 10      | 00001010 | •       |          |

| 11      | 00001011 | 127     | 01111111 |

| 12      | 00001100 | 128     | 1000000  |

| 13      | 00001101 | 129     | 10000001 |

| 14      | 00001110 |         |          |

| 15      | 00001111 | •       |          |

| 16      | 00010000 | •       |          |

| 17      | 00010001 | •       |          |

| •       |          |         |          |

| •       |          |         |          |

| •       |          | 254     | 1111110  |

| 31      | 00011111 | 255     | 1111111  |

|         |          |         |          |

|         |          |         |          |

|         |          |         |          |

– Figure 1.2: Decimal-Binary Table. ——

right to left. First you add the right-most column:

Then the next column:

Let us now look at other examples of binary addition:

| 0010   | (2) | 0011  | (3) |

|--------|-----|-------|-----|

| + 0001 | (1) | +0001 | (1) |

| 0011   | (3) | 0100  | (4) |

The last example illustrates the role of the carry. Looking at the right-most bits: 1 + 1 = (1) 0. A carry of 1 is generated, which must be added to the next bits:

001 (column 0 has just been added) + 000 + 1 (carry) =(1)0 (where (1) indicates a new carry into column 2)

The final result is 0100.

Let's consider another example:

| 0111   | (7)   |

|--------|-------|

| + 0011 | + (3) |

| 1010   | (10)  |

In this example, a carry is again generated, up to the left-most column.

With eight bits, it is, therefore, possible to directly represent the numbers 00000000 to 11111111 (i.e., 0 to 255). Two limitations, however, should be immediately visible. First, we are only representing positive numbers. Second, the magnitude of these numbers is limited to 255, if we use only eight bits. Let's now address these limitations in turn.

**Signed Binary** In a signed binary representation, the left-most bit is used to indicate the sign of the number. Traditionally, 0 is used to denote a *positive* number and 1 is used to denote a *negative* number. For example, 1111111 represents – 127, while 01111111 represents + 127. We can now

represent positive and negative numbers, but we have reduced the maximum magnitude of these numbers to 127. As another example, 00000001 represents +1 (the leading 0 is "+", followed by 0000001 = 1) and 10000001 is -1 (the leading 1 is "-").

Let us now address the *magnitude* problem. In order to represent larger numbers, it is necessary to use a larger number of bits. For example, if we use sixteen bits (two bytes) to represent numbers, we will be able to represent numbers from -32K to +32K in signed binary. (1K in computer jargon represents 1,024.) Bit 15 is used for the sign, and the remaining 15 bits (bit 14 through bit 0) are used for the magnitude:  $2^{15} = 32$ K.

If we wish to represent large integers, it is necessary to use a larger number of bytes internally. This is why most simple BASICs, and other languages, provide only a limited precision for integers. This way, they can use a shorter internal format for the numbers they manipulate. Better versions of BASIC and some other languages provide a larger number of significant decimal digits at the expense of a large number of bytes for each number.

Let us now solve another problem: speed efficiency. Let's perform an addition in the signed binary representation we have just introduced. We want to add +7 and -5.

+ 7 is represented by 00000111 - 5 is represented by 10000101 The binary sum is: 10001100, or - 12

This is not the correct result. The correct result is +2. We have neglected the fact that in order to use this representation, special actions must be taken, depending on the sign. This results in increased complexity and reduced performance. In other words, the binary addition of signed numbers does not "work correctly." This is annoying. Clearly, the computer must not only represent information, but it must also perform arithmetic on it.

The solution to this problem is called the *two's complement* representation. We will use the two's complement representation, instead of the signed binary representation. Before we introduce two's complement, we will first introduce an intermediate step: *one's complement*.

**One's Complement** In the one's complement representation, all positive integers are represented in their correct binary format. For example +3 is represented as usual by 00000011. However, its complement, -3, is obtained by complementing every bit in the original representation. Each

0 is transformed into a 1 and each 1 into a 0. In our example, the one's complement representation of - 3 is 1111100.

Let's look at another example:

+2 is 00000010 -2 is 11111101

Note that, in this representation, positive numbers start with a 0 on the left, and negative numbers start with a 1 on the left. As a test, let's add -4and +6:

> – 4 is 11111011 +6 is 00000110 The sum is: (1) 00000001

where (1) indicates a carry. The correct result should be 2 or 00000010. Let's try again:

| – 3 is          | 11111100 |

|-----------------|----------|

| – 2 is          | 11111101 |

| The sum is: (1) | 11111001 |

or -6, plus a carry. The correct result is -5. The representation of -5 is 11111010. It did not work.

This representation does represent positive and negative numbers; however, the result of an ordinary addition does not always come out correctly. We will now use another representation. It is evolved from the one's complement and is called the two's complement representation.

Two's Complement Representation In the two's complement representation, positive numbers are represented, as usual, in signed binary, just like in one's complement. The difference lies in the representation of negative numbers. A negative number represented in two's complement is obtained by first computing the one's complement and then adding one. Let's examine an example:

**Example:** +3 is represented in signed binary by 00000011. Its one's complement representation is 11111100. The two's complement is obtained by adding one. It is 1111101.

Let's try an addition:

| (3)   | 00000011   |

|-------|------------|

| + (5) | + 00000101 |

| (8)   | 00001000   |

The result is correct.

Let's try a subtraction:

$\begin{array}{ccc} (3) & 00000011\\ (-5) & + 1111011\\ & 1111110 \end{array}$

Now, let's identify the result by computing the two's complement:

(The one's complement of 1111110 is)

00000001

(Adding 1)

+

1

(Therefore, the two's complement is)

00000010 (or +2)

The result + 11111110 represents - 2. It is correct.

We have now tried addition and subtraction, and the results have been correct (ignoring the carry). It seems that two's complement works!

We will now add +4 and -3 (the subtraction is performed by adding the two's complement):

| +4 is              | 00000100 |

|--------------------|----------|

| 3 is               | 11111101 |

| The result is: (1) | 0000001  |

If we ignore the carry, the result is 00000001 (i.e., 1 in decimal). This is the correct result. Without giving the complete mathematical proof, we will simply state that this representation does work. In two's complement, it is possible to add or subtract signed numbers, regardless of the sign. Using the usual rules of binary addition, the result comes out correct, including the sign. The carry is ignored. This is a very significant advantage. If this were not the case, we would have to correct the result for sign every time, causing a much slower addition or subtraction time.

For the sake of completeness, let us state that two's complement is simply the most convenient representation to use for simpler processors, such as microprocessors. On more complex processors, other representations may be used. For example, one's complement may be used, but if one's complement is used, special circuity is required to "correct the result."

From this point on, all signed integers will be implicitly represented internally in two's complement notation. See Figure 1.3 for a table of two's complement numbers.

We will now offer examples that demonstrate the rules of two's complement. In particular, C denotes a possible carry (or borrow) condition. (It is bit 8 of the result.) V denotes a two's complement overflow; that is, it indicates when the sign of the result is changed "accidentally," because the

| +     | TWO'S COMPLEMENT CODE | _         | TWO'S COMPLEMENT CODE |

|-------|-----------------------|-----------|-----------------------|

| + 127 | 0111111               | - 128     | 1000000               |

| + 126 | 01111110              | - 127     | 10000001              |

| + 125 | 01111101              | - 126     | 10000010              |

|       | UTTTO                 |           | 10000010              |

|       |                       | - 125<br> | 1000011               |

| + 65  | 01000001              | - 65      | 10111111              |

| + 64  | 01000000              | - 64      | 11000000              |

| + 63  | 00111111              | - 63      | 11000001              |

|       |                       |           |                       |

| + 33  | 00100001              | - 33      | 11011111              |

| + 32  | 00100000              | - 32      | 11100000              |

| + 31  | 00011111              | - 31      | 11100001              |

|       |                       |           |                       |

| + 17  | 00010001              | - 17      | 11101111              |

| + 16  | 00010000              | - 16      | 11110000              |

| + 15  | 00001111              | - 15      | 11110001              |

| + 14  | 00001110              | - 14      | 11110010              |

| + 13  | 00001101              | - 13      | 11110011              |

| + 12  | 00001100              | - 12      | 11110100              |

| + 11  | 00001011              | - 11      | 11110101              |

| + 10  | 00001010              | - 10      | 11110110              |

| + 9   | 00001001              | - 9       | 11110111              |

| + 8   | 00001000              | - 8       | 11111000              |

| + 7   | 00000111              | - 7       | 11111001              |

| + 6   | 00000110              | - 6       | 11111010              |

| + 5   | 00000101              | - 5       | 11111011              |

| + 4   | 00000100              | - 4       | 11111100              |

| + 3   | 00000011              | - 3       | 1111101               |

| + 2   | 00000010              | - 2       | 1111110               |

| + 1   | 0000001               | - 1       | 1111111               |

| + 0   | 0000000               |           |                       |

numbers are too large. It is an essentially internal carry from bit 6 to bit 7 (the sign bit). This will be clarified below.

Let us now demonstrate the role of the carry C and the overflow V.

**The Carry C** Here is an example of a carry:

| (128)       | 10000000  |

|-------------|-----------|

| + (129)     | + 1000001 |

| (257) = (1) | 00000001  |

where (1) indicates a carry. The result requires a ninth bit (bit 8, since the right-most bit is 0). It is the carry bit.

If we assume that the carry is the ninth bit of the result, we recognize the result as binary 10000001 = 257. However, the carry must be recognized and handled with care. Inside the microprocessor, the registers used to hold information are generally only eight bits wide. When storing the result, only bits 0 to 7 will be preserved.

A carry, therefore, always requires special action. It must be detected by special instructions, then processed. Processing the carry means either storing it somewhere (with a special instruction), ignoring it, or deciding that it is an error (if the largest authorized result is 1111111).

**Overflow V** Here's an example of overflow:

| bit 6 –     |        |

|-------------|--------|

| bit 7-1     |        |

| VV          |        |

| 01000000    | (64)   |

| (+)01000001 | + (65) |

| 1000001     | (-127) |

An internal carry has been generated from bit 6 into bit 7. This is called an *overflow*. The result is now negative, "by accident." This situation must be detected, so that it can be corrected.

Let us examine another situation:

| 11111111     | ( – 1) |

|--------------|--------|

| + 11111111   | + (-1) |

| (1) 11111110 | (-2)   |

| ¥            |        |

| carry        |        |

In this case, an internal carry has been generated from bit 6 into bit 7, and also from bit 7 into C. The rules of two's complement arithmetic specify

that this carry should be ignored. The result is then correct. This is because the carry from bit 6 to bit 7 did not change the sign bit.

The carry from bit 6 into bit 7 is not an *overflow* condition. When operating on negative numbers, the overflow is not simply a carry from bit 6 into bit 7. Let's examine one more example:

| 11000000     | (–64)  |

|--------------|--------|

| + 10111111   | (–65)  |

| (1) 01111111 | (+127) |

| ↓            |        |

| carry        |        |

This time, there has been no internal carry from bit 6 into bit 7, but there has been an external carry. The result is incorrect, as bit 7 has been changed. An overflow condition should be indicated.

Overflow will occur in four situations, including:

- 1. the addition of large positive numbers

- 2. the addition of large negative numbers

- 3. the subtraction of a large positive number from a large negative number

- 4. the subtraction of a large negative number from a large positive number.

Let us now improve our definition of the overflow.

Technically, the overflow indicator, a special bit reserved for this purpose, and called a condition code, will be set when there is a carry from bit 6 into bit 7, and there is no external carry. It will also be set when there is no carry from bit 6 into bit 7, but there is an external carry. This indicates that bit 7—the sign of the result—has been accidentally changed. For the technically-minded reader, the overflow flag is set by Exclusive ORing the carry-in and carry-out of bit 7 (the sign bit). Practically every microprocessor is supplied with a special overflow flag to automatically detect this condition—a condition that requires corrective action.

Overflow indicates that the result of an addition or subtraction requires more bits than are available in the standard 8-bit register used to contain the result.

**The Carry and the Overflow** The carry and the overflow bits are called *condition codes*. They are provided in every microprocessor. We will learn to use them for effective programming in Chapter 2. These two indicators

are located in a special register called the flags or "status" register. This register also contains additional indicators (as described in Chapter 4).

**Examples** We will now look at actual examples that illustrate the operation of the carry and the overflow. In each example, the symbol V denotes the overflow, and C denotes the carry. If there has been no overflow, V will equal 0. If there has been an overflow, V will equal 1 (the same is true for the carry C). Remember that the rules of two's complement specify that the carry be ignored. (The mathematical proof is not supplied here.) Let's examine the following examples:

| <b>Positive-Positive</b> |             |         |

|--------------------------|-------------|---------|

| 00000110                 | (+ 6)       |         |

| + 00001000               | (+8)        |         |

| 00001110                 | (+14)       | V:0 C:0 |

| (CORRECT)                |             |         |

| Positive-Positive wi     | th Overflow |         |

| 01111111                 | (+127)      |         |

| + 0000001                | (+1)        |         |

| 1000000                  | (-128)      | V:1 C:0 |

| (ERROR)                  |             |         |

The above is invalid because an overflow has occurred.

| Positive-Negative (result | positive) |                     |

|---------------------------|-----------|---------------------|

| 00000100                  | (+4)      |                     |

| + 11111110                | (-2)      |                     |

| (1)0000010                | (+2)      | V:0 C:1 (disregard) |

| (CORRECT)                 |           |                     |

| Positive-Negative (result | negative) |                     |

| 0000010                   | (+2)      |                     |

| + 11111100                | (-4)      |                     |

| 11111110                  | (-2)      | V:0 C:0             |

| (CORRECT)                 |           |                     |

| Negative-Negative         |           |                     |

| 1111110                   | ( – 2)    |                     |

| + 11111100                | (-4)      |                     |

| (1)11111010               | (-6)      | V:0 C:1 (disregard) |

| (CORRECT)                 |           |                     |

| Negative-Negative      | with Overflow |         |

|------------------------|---------------|---------|

| 1000001                | ( – 127)      |         |

| + 11000010             | (-62)         |         |

| (1)01000011<br>(ERROR) | (+67)         | V:1 C:1 |

In the last examples, an "underflow" has occurred, by adding two large negative numbers. The result is -189, which is too large to reside in eight bits.

**Fixed Format Representation** We now know how to represent signed integers; however, we have not yet resolved the problem of magnitude. If we want to represent larger integers, we will need several bytes. In order to perform arithmetic operations efficiently, it is necessary to use a fixed number of bytes, rather than a variable number. Therefore, once the number of bytes is chosen, the maximum magnitude of the number that can be represented is fixed.

#### THE MAGNITUDE PROBLEM

Let us consider the following important point: the number of bits, n, chosen for the two's complement representation is usually fixed for that program. If any result or intermediate computation should generate a number that requires more than n bits, some bits will be lost. The program normally retains the n left-most bits (the most significant) and drops the low-order ones. This is called *truncating* the result.

Let's look at an example in the decimal system, using a six-digit representation:

|   | 123456   |

|---|----------|

| × | 1.2      |

|   | 246912   |

|   | 123456   |

|   | 148147.2 |

The result requires seven digits. The 2 after the decimal point will be dropped, and the final result will be 148147. It has been truncated. Usually, as long as the position of the decimal point is not lost, this method is used to extend the range of the operations that can be performed, at the expense of precision. The problem is the same in binary. This fixed-format representation may cause a loss of precision, but it may be sufficient for usual computations or mathematical operations.

Unfortunately, in the case of accounting, no loss of precision is tolerable.

For example, if a customer rings up a large total on a cash register, it would not be acceptable to have a five-figure total that would be approximated to the dollar. Thus, another representation must be used whenever precision in the result is essential. The solution normally used is *BCD*, or binarycoded decimal.

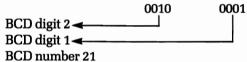

**BCD Representation** The principle used in representing numbers in BCD is to encode each decimal digit separately and to use as many bits as necessary to represent the complete number exactly. To encode each of the digits from 0 through 9, four bits are necessary. (Three bits supply only eight combinations and, therefore, cannot encode the ten digits.) Four bits allow sixteen combinations and are, therefore, sufficient to encode the digits 0 through 9. It should also be noted that six of the possible codes will not be used in the BCD representation (see Figure 1.4). This will result later on in a potential problem, when performing additions and subtractions. Since only four bits are needed to encode a BCD digit, two BCD digits may be encoded in every byte. This is called *packed BCD*. As an example, 00000000 is 00 in BCD. 10011001 is 99.

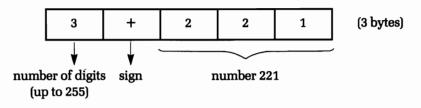

A BCD code is read as follows:

As many bytes as necessary will be used to represent all BCD digits. Typically, one or more nibbles will be used at the beginning of the representation to indicate the total number of nibbles (i.e., the total number of BCD digits used). Another nibble or byte will be used to denote the position

| BCD SYMBOL | CODE                       | BCD SYMBOL                                                                                                                                                           |

|------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 1000                       | 8                                                                                                                                                                    |

| 1          | 1001                       | 9                                                                                                                                                                    |

| 2          | 1010                       | UNUSED                                                                                                                                                               |

| 3          | 1011                       | UNUSED                                                                                                                                                               |

| 4          | 1100                       | UNUSED                                                                                                                                                               |

| 5          | 1101                       | UNUSED                                                                                                                                                               |

| 6          | 1110                       | UNUSED                                                                                                                                                               |

| 7          | 1111                       | UNUSED                                                                                                                                                               |

|            | 0<br>1<br>2<br>3<br>4<br>5 | 0         1000           1         1001           2         1010           3         1011           4         1100           5         1101           6         1110 |

-Figure 1.4: A BCD Table.—

of the decimal point. However, conventions may vary. Here is an example of a representation for multibyte BCD integers:

This example represents +221. (The sign may be represented by 0000 for +, and 0001 for -, for example.)

The BCD representation can easily accommodate decimal numbers. For example, +2.21 may be represented by:

The advantage of BCD is that it yields absolutely correct results. Its disadvantage is that it uses a large amount of memory and results in slow arithmetic operations. This is acceptable only in an accounting environment, but BCD is normally not used in other cases.

We have now solved the problems associated with the representation of integers, signed integers, and large integers. We have even presented one possible method of representing decimal numbers, with BCD representation. Let us now examine the problem of representing decimal numbers in fixed length format.

**Floating-Point Representation** The basic principle of floating point representation is that decimal numbers are represented with a fixed length format. In order not to waste bits, the representation will *normalize* all the numbers. For example, 0.000123 wastes three zeroes on the left before non-zero digits. These zeroes have no meaning except to indicate the position of the decimal point. Normalizing this number results in .123 ×  $10^{-3}$ . .123 is the normalized mantissa; -3 is the exponent. We have normalized this number by eliminating all the meaningless zeroes to the left of the first non-zero digit and by adjusting the exponent. Let's consider another

example:

**Example:** 22.1 is normalized as  $.221 \times 10^2$ . The general form of floatingpoint representation is M  $\times 10^E$ , where M is the mantissa, and E is the exponent.

It can be readily seen that a normalized number is characterized by a mantissa less than 1 and greater than or equal to .1 in all cases where the number is not zero. In other words, it can be represented mathematically by:

$.1 \le M \le 1 \text{ or } 10^{-1} \le M \le 10^{0}$

Similarly, in the binary representation:

$2^{-1} \le M < 2^{\circ} (\text{or } .5 \le M < 1)$

where M is the absolute value of the mantissa (disregarding the sign). For example:

111.01 is normalized as: .11101 × 2<sup>3</sup>.

The mantissa is 11101. The exponent is 3.

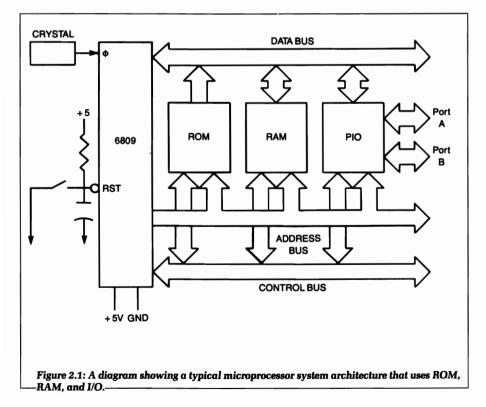

Now that we have defined the principle of the representation, let us examine the actual format. A typical floating-point representation appears in Figure 1.5.

In the representation in Figure 1.5, four bytes are used for a total of 32 bits. The first byte on the left of the illustration is used to represent the exponent. Both the exponent and the mantissa will be represented in two's complement. As a result, the maximum exponent will be -128. "S" in Figure 1.5 denotes the sign bit.

Three bytes are used to represent the mantissa. Since the first bit in the two's complement representation indicates the sign, this leaves 23 bits for the representation of the magnitude of the mantissa.

This is only one example of a floating point representation. It is possible to use only three bytes, or it is possible to use more. The 4-byte representation proposed above is a common one that represents a reasonable compromise in terms of accuracy, magnitude of numbers, storage utilization, and efficiency in arithmetic operation.

We have now explored the problems associated with the representation of numbers and have learned how to represent them in integer form with a

| 31 | 24  | 23 | 16 | 15 |   |   |   | 8 | 7 |   | 0 |

|----|-----|----|----|----|---|---|---|---|---|---|---|

| s  | EXP | s  | м  | A  | N | т | I | s | S | Α |   |

Figure 1.5: Typical Floating-Point Representation.—

sign, or in decimal form. Let's now go on to examine how alphanumeric data is represented internally.

**Representing Alphanumeric Data** The representation of alphanumeric data (i.e., characters) is completely straightforward: all characters are encoded in an 8-bit code. Only two codes are in general use in the computer world, the ASCII Code and the EBCDIC Code. ASCII stands for "American Standard Code for Information Interchange," and is universally used in the world of microprocessors. EBCDIC is a variation of ASCII used by IBM, and is, therefore, not used in the microcomputer world unless one interfaces to an IBM terminal.

Let us briefly examine the ASCII encoding. We encode 26 letters of the alphabet for both upper and lower case, plus 10 numeric symbols, and perhaps 20 additional special symbols. This can be easily accomplished with 7 bits, which allow 128 possible codes. (See Figure 1.6) All characters are, therefore, encoded in 7 bits. The 8th bit, when it is used, is the parity bit.

| HEX | MSD  | 0   | 1   | 2     | 3   | 4   | 5   | 6   | 7      |

|-----|------|-----|-----|-------|-----|-----|-----|-----|--------|

| LSD | BITS | 000 | 001 | 010   | 011 | 100 | 101 | 110 | 111    |

| 0   | 0000 | NUL | DLE | SPACE | 0   | Ø   | Р   | _   | р      |

| 1   | 0001 | SOH | DC1 | !     | 1   | Α   | Q   | а   | q      |

| 2   | 0010 | STX | DC2 | "     | 2   | в   | R   | b   | r      |

| 3   | 0011 | ETX | DC3 | #     | 3   | С   | S   | с   | s      |

| 4   | 0100 | EOT | DC4 | \$    | 4   | D   | т   | d   | t      |

| 5   | 0101 | ENQ | NAK | %     | 5   | Е   | U   | е   | u      |

| 6   | 0110 | ACK | SYN | &     | 6   | F   | v   | f   | v      |

| 7   | 0111 | BEL | ETB | ,     | 7   | G   | w   | g   | w      |

| 8   | 1000 | BS  | CAN | (     | 8   | н   | х   | h   | x      |

| 9   | 1001 | нт  | EM  | )     | 9   | I.  | Y   | i   | у      |

| A   | 1010 | LF  | SUB | *     | ~   | J   | z   | j   | z      |

| В   | 1011 | VT  | ESC | +     | ;   | к   | I   | k   | {      |

| С   | 1100 | FF  | FS  | ,     | <   | L   | ١   | I   |        |

| D   | 1101 | CR  | GS  | -     | =   | м   | 1   | m   | }      |

| Е   | 1110 | SO  | RS  |       | >   | Ν   | ^   | n   | $\sim$ |

| F   | 1111 | SI  | US  | /     | ?   | ο   |     | ο   | DEL    |

|     |      |     |     |       |     |     |     |     |        |

-Figure 1.6: ASCII Conversion Table (See Appendix B for Abbreviations.)-

Parity is a technique for verifying that the contents of a byte have not been accidentally changed. The number of 1's in the byte are counted and the 8th bit is set to one if the count was odd, thus making the total even. This is called *even parity*. Odd parity (i.e., writing the 8th bit [the left-most bit] so that the total number of 1's in the byte is odd) can also be used.

As an example, let us compute the parity bit for 0010011 using even parity. The number of 1's is 3. The parity bit must, therefore, be a 1, so that the total number of bits is 4, or even. The result is 10010011, where the leading 1 is the parity bit and 0010011 identifies the character.

The table of 7-bit ASCII codes is shown in Figure 1.6. In practice, it is used "as is," without parity, by adding a 0 in the left-most position, or else with parity, by adding the appropriate extra bit on the left.

In specialized situations, such as telecommunications, other codings, such as error-correcting codes, may be used. However, descriptions of these codings are beyond the scope of this book.

Now that we have examined the usual representations for both program and data inside the computer, let us examine the possible external representations.

### **EXTERNAL REPRESENTATION OF INFORMATION**

The external representation of information refers to the way information is presented to the user, i.e., generally to the programmer. Information may be presented externally in essentially three formats: binary, octal or hexadecimal, and symbolic. Let's examine these formats.

We have seen that information is stored internally in bytes, 1. Binary which are sequences of eight bits (0's or 1's). It is sometimes desirable to display this internal information directly in its binary format-this is known as binary representation. A simple example is provided by lightemitting diodes (LEDs) which are essentially miniature lights on the front panel of a microcomputer. In the case of an 8-bit microprocessor, a front panel will typically be equipped with eight LEDs to display the contents of any internal register. A lighted LED indicates a 1. An unlighted LED indicates a 0. Such a binary representation may be used for the fine debugging of a complex program, especially if it involves input/output, but is naturally impractical at the human level. This is because in most cases, it is easier to look at information in symbolic form. For example, 9 is much easier to understand and to remember than 1001. More convenient representations have been devised, which improve the interface between people and machines.

**2.** Octal and Hexadecimal Octal and hexadecimal encode three and four binary bits, respectively, into a unique symbol. Octal is a format using three bits, where each combination of three bits is represented by a symbol between 0 and 7. (See Figure 1.7)

For example, 00 100 100 binary is represented by:

$\begin{array}{c|c} \downarrow & \downarrow & \downarrow \\ 0 & 4 & 4 \end{array}$

or 044 in octal.

As another example: 11 111 111 is:

**3** 7 7

or 377 in octal.

Conversely, the octal 211 represents

010 001 001

or 10001001 binary.

Octal has traditionally been used on older computers that employ various numbers of bits, ranging from 8 to, perhaps, 64. More recently, with the dominance of 8-bit microprocessors, the 8-bit format has become the standard, and another, more practical, representation is used hexadecimal representation.

In the hexadecimal representation, a group of four bits is encoded as one hexadecimal digit. Hexadecimal digits are represented by the symbols

| 0 |

|---|

|   |

| 1 |

| 2 |

| 3 |

| 4 |

| 5 |

| 6 |

| 7 |

|   |

from 0 to 9, and by the letters A, B, C, D, E, F. For example, 0000 is represented by 0; 0001 is represented by 1; and 1111 is represented by the letter F (see Figure 1.8). For example, 1010 0001 in binary is represented by

in hexadecimal.

Hexadecimal offers the advantage of encoding eight bits into only two digits. This is easier to visualize or memorize and faster to type into a computer than its binary equivalent. Therefore, on most new microcomputers, hexadecimal is the preferred method of representation for groups of bits.

Naturally, whenever the information present in the memory has a meaning, such as representing text or numbers, hexadecimal is not convenient for representing the meaning of this information for a human user.

**Symbolic Representation** Symbolic representation refers to the external representation of information in actual symbolic form. For example,

| DECIMAL | BINARY | HEX | OCTAL |

|---------|--------|-----|-------|

| 0       | 0000   | 0   | 0     |

| 1       | 0001   | 1   | 1     |

| 2       | 0010   | 2   | 2     |

| 3       | 0011   | 3   | 3     |

| 4       | 0100   | 4   | 4     |

| 5       | 0101   | 5   | 5     |

| 6       | 0110   | 6   | 6     |

| 7       | 0111   | 7   | 7     |

| 8       | 1000   | 8   | 10    |

| 9       | 1001   | 9   | 11    |

| 10      | 1010   | А   | 12    |

| 11      | 1011   | В   | 13    |

| 12      | 1100   | С   | 14    |

| 13      | 1101   | D   | 15    |

| 14      | 1110   | E   | 16    |

| 15      | 1111   | F   | 17    |

Figure 1.8: Hexadecimal Codes—

decimal numbers are represented as decimal numbers, and not as sequences of hexadecimal symbols or bits. Similarly, text is represented as such. Naturally, symbolic representation is most practical to the user. It is used whenever an appropriate display device is available, such as a CRT display or a printer. (A CRT display is a television-type screen used to display text or graphics.) Unfortunately, in smaller systems, such as oneboard microcomputers, it is uneconomical to provide such displays, and the user is restricted to hexadecimal communication with the computer.

**Summary of External Representations** Symbolic representation of information is the most desirable, since it is the most natural for a human user. However, it requires an expensive interface in the form of an alphanumeric keyboard, plus a printer or a CRT display. For this reason, it may not be available on the less expensive systems. An alternative type of representation is then used and in such a case, hexadecimal is the dominant representation. Only in rare cases, relating to fine debugging at the hardware or software level, is the binary representation used. *Binary* directly displays the contents of the registers of memory in binary format.

Now that we have seen how information is represented internally and externally, let's go on to examine the actual microprocessor that manipulates this information.

# 2 INSIDE THE 8086/8088

# INTRODUCTION

In this chapter we will discuss the internal architecture of the 8086/8088 microprocessor. We will begin with a broad discussion of the architecture of a microprocessor in general. We will then discuss important concepts common to most single-chip microprocessors.

Next, we will examine the instruction cycle of a typical microprocessor. By the end of this discussion you should have a good general understanding of the internal organization of a microprocessor and the execution of instructions.

We will then go on to examine the internal organizations of the 8086/8088. We will look closely at the many features provided by these two processors and contrast them with features typical of other microprocessors. When comparing processors, it can be clearly seen that the designers of the 8086/ 8088 have implemented new solutions to old problems, and this has resulted in an easyto-use, extremely powerful microprocessor.

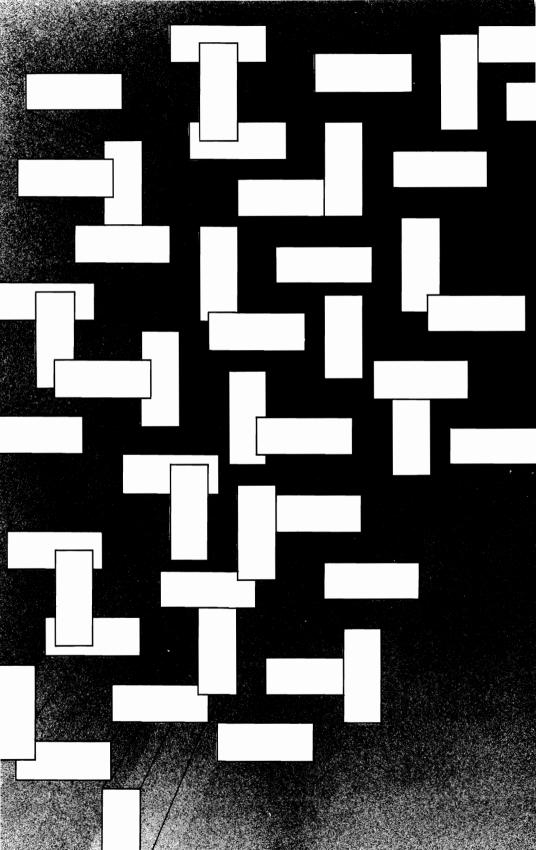

## GENERAL MICROPROCESSOR SYSTEM ARCHITECTURE

Let's begin our discussion by examining the general hardware architecture of a typical microprocessor-based system. Although we will not take the time now to explain how this architecture is realized with the 8086/ 8088, we will show how a microprocessor fits into a system environment and thereby help you to better understand the internal organization of a CPU.

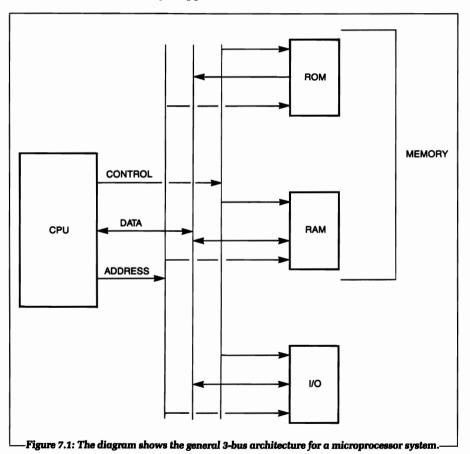

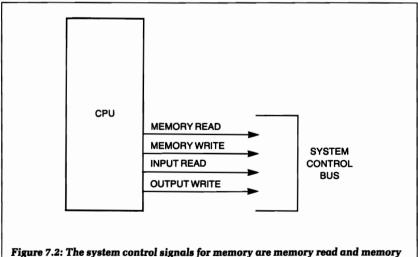

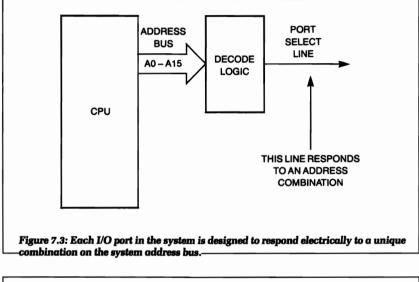

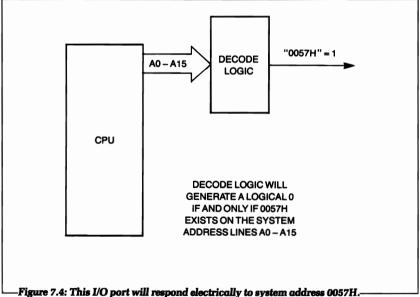

Figure 2.1 displays a block diagram of a typical microprocessorcontrolled system. Appearing on the left of the diagram is the microprocessor unit (the MPU)—in this case the 8086/8088—which implements the functions of the central-processing unit (the CPU) on a single chip. The CPU includes an arithmetic-logical unit (the ALU), plus its internal registers, and a control unit (the CU), which decodes and internally sequences instructions. (We will learn more about the CPU later in this chapter.) The MPU has three buses: an address bus, a data bus, and a control bus. A bus

is a collection of electronic signals that originate at a common source and perform a common function.

We can see in Figure 2.1 that alongside the CPU are the ROM, RAM, and I/O. These are the main blocks of a microprocessor system. No matter how complex a system is or what its function is, the block diagram of Figure 2.1 accurately depicts it.

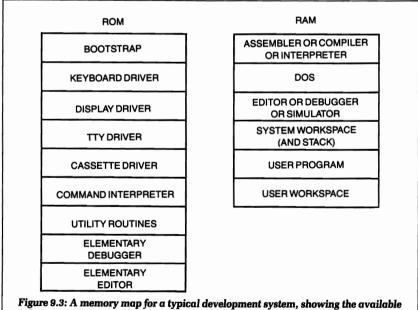

Let us examine briefly each of the main blocks, labeled ROM, RAM, and I/O. The ROM (or read-only memory) stores the program of the system. The advantage of ROM memory is that its contents are permanent; they do not disappear when the system is turned off. For this reason, ROM usually contains the "bootstrap" or monitor program that permits initial system operation. In a process-control environment, nearly all programs reside in ROM. This is because they are seldom changed and must be protected against power failures.

RAM (or random access memory) is the read/write memory of the system. In a hobbyist or program-development environment, most of the programs reside in RAM, so they can be easily changed. Such programs can be kept in RAM or transferred into ROM, if desired. RAM is volatile. Information in RAM is lost when power is turned off. In a control system, the amount of RAM is typically small (for data only); however, in a program-development environment, the amount of RAM is generally large, as it contains programs, plus the development software. Prior to use, the contents of RAM must be loaded from an external device.

Finally, the system also contains one or more interface chips. An interface chip allows communication between the system and the external world. The PIO is a frequently-used interface chip. PIO stands for parallel input/output. PIOs, like the other chips in the system, connect to all three buses and provide data paths for communication with the outside world.

Let's now study the function of the buses.

#### THE THREE BUSES

As we mentioned previously, the system in Figure 2.1 has a 3-bus architecture. The address bus has the "job" of enabling the path for the communication between the CPU and ROM, RAM, or I/O. The data bus passes the actual information between the CPU and the enabled system block (see Figure 2.1). Finally, the control bus performs the dual task of 1) electrically defining the type of communication, and 2) beginning and ending the transfer.

In most applications the CPU controls each bus. It is the function of the CPU to correctly time each bus so that reliable communication can occur.

You, as the programmer, need not concern yourself with this activity, as it is done by the system hardware. However, you must provide the correct instructions to the CPU so that it can generate the right addresses and data to the system hardware. (As a programmer you can only assume that the hardware is functioning correctly.)

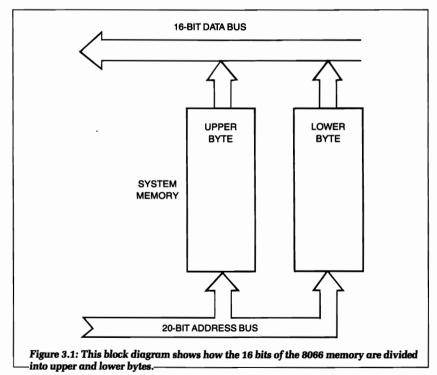

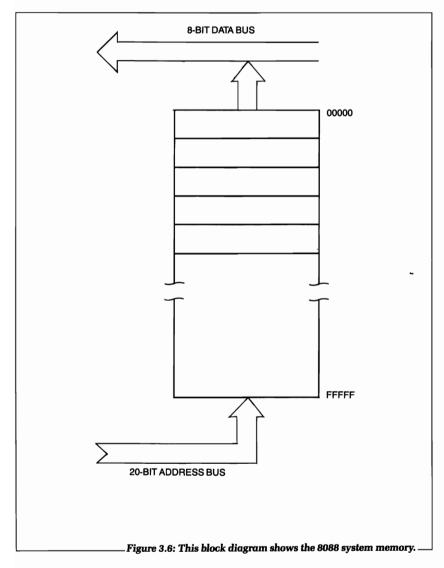

The width of a bus determines the number of signal lines contained in the group comprising the bus. For the 8086/8088 the address bus can be up to 20 bits wide. The width of the data bus is 16 bits and the width of the control bus varies, but it has a nominal value of 5 bits. The width of each bus differs from CPU to CPU, and from system to system.

## **INSIDE A MICROPROCESSOR**

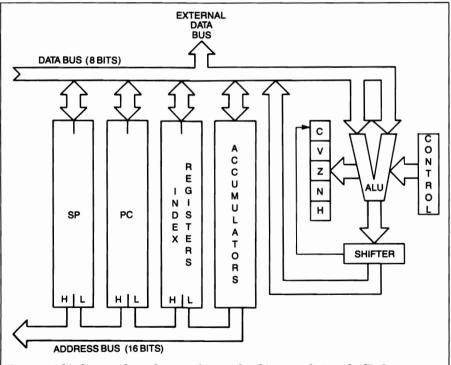

Let us now examine Figure 2.2 and discuss the general internal architecture of a microprocessor. In addition, we will show you how the 8086 and 8088 implement their specific internal architectures, and we will point out the similarities and differences to the general case (shown in Figure 2.2).

Figure 2.2: This diagram shows the general internal architecture of a "standard" microprocessor.  $^{

m J}$

Figure 2.2 shows a diagram of a standard architecture of a general microprocessor. Let's examine the different modules in this figure. The control box (on the right of the illustration) represents the control unit that synchronizes the system hardware and timing.

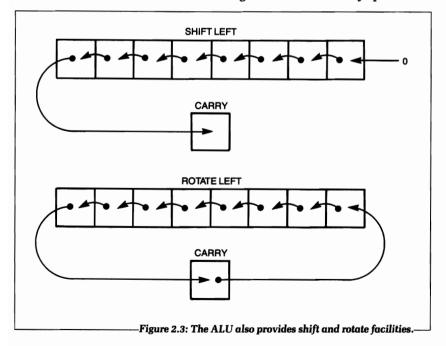

To the left of the control box is the ALU. The ALU performs all arithmetic and logical operations. Special registers, called accumulators, are usually connected to the output of the ALU. They contain the results of arithmetic operations. In addition to the arithmetic and logical operations, the ALU also provides *shift* and *rotate* facilities. As illustrated in Figure 2.3, a shift moves the contents of the accumulator to the left or right by one or more positions. In this illustration, each bit has been moved to the left by one position.

Referring back to Figure 2.2, the status or condition code register appears to the left of the ALU. The job of this register is to store the internal conditions of the microprocessor in codes. The condition codes are sometimes referred to as condition flags. An example of this is a bit that indicates when the result of an operation performed by the ALU leaves all accumulator bits equal to 0. When this occurs, the condition flag called the zero flag is set to true.

The contents of the condition code register can be tested by specialized

instructions. The CPU alters its execution path based on the logical values of these codes. We will discuss this subject in further detail when we present the instruction set and give program examples for the 8086/8088. (*Note:* most of the instructions executed by the microprocessor will modify some or all of the condition flags. The instruction set for the 8086/8088 [presented in Chapter 4] clearly indicates which instructions modify which condition flags.]

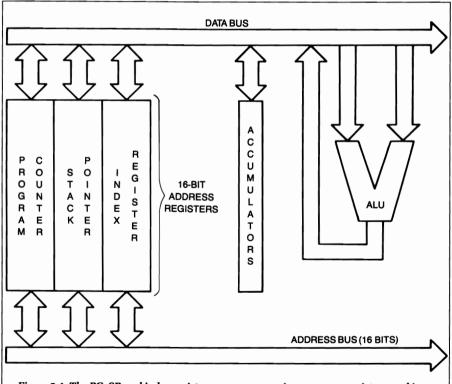

Moving to the left in Figure 2.2, we find the address registers. These registers are used for the storage of addresses. They are connected to the system address bus. Whenever the CPU executes a program, the address registers are combined logically to form a complete system address. Some of the power of a microprocessor comes from its ability to combine the address registers in special ways to form the system address present on the address bus. Chapter 3 describes in detail how the address registers of the 8086/ 8088 can be logically combined to form a single address. Figure 2.4 shows

Figure 2.4: The PC, SP, and index registers are common microprocessor registers used in forming a complete system address.

three common address registers contained in a microprocessor: the program counter, the stack pointer, and the index register. Note that the registers also appear in Figure 2.2. Let's discuss them.

#### THE PROGRAM COUNTER (or PC)

The program counter (or PC) must be present in all microprocessors, as it is fundamental to program execution. It contains the address of the next instruction to be executed.

A program normally executes in a sequential fashion. To access the next instruction, it is necessary to "fetch" it from the system memory and read the instruction into the microprocessor. The contents of the PC are deposited on the address bus and input to the memory address line. The memory then reads the contents specified by the address and sends the corresponding instruction back to the CPU.

#### THE STACK POINTER (or SP)

The stack pointer (or SP) implements the system stack. (The stack is described in detail in a following section. The stack is often used for handling interrupts and subroutines, and for saving temporary data.) The stack pointer contains the memory address of the top of the stack.

#### THE INDEX REGISTER

Indexing is a memory-addressing facility used to access blocks of data in the memory, using only a single instruction. This facility is not available in all microprocessors. It is, however, available with the 8086/8088. An index register typically contains a displacement, which is automatically added to a base value when forming an address. In short, indexing is used to access a word within a block of data. Now that we have discussed all the elements in Figure 2.2, let's move on and discuss the stack.

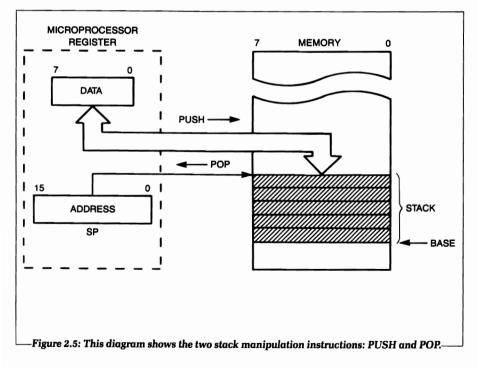

## THE STACK

A stack, formally called a LIFO (last-in, first-out) structure, is a set of memory locations, allocated to the stack data structure. The essential characteristic of the stack is that the first element introduced in the stack is always at the bottom, and the element most recently deposited is always on top. An analogy can be drawn with plates stacked on a restaurant counter assuming that there is a hole in the counter with a spring at the bottom, and that the plates are piled up in the hole. With this organization, it is guaranteed that the plate that was placed first in the stack is always at the bottom, and the most-recent placement is on top.

In normal use, a stack is only accessible via two operations or instructions: PUSH and POP. These two instructions are illustrated in Figure 2.5. The PUSH operation deposits elements on the top of the stack. A POP transfers the top element of the stack into the internal register specified by the instruction.

# THE GENERAL INSTRUCTION CYCLE

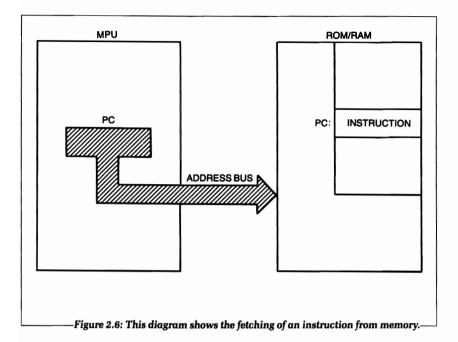

Let's now examine Figure 2.6. This diagram illustrates the role of the program counter, which fetches an instruction from the memory. The microprocessor unit appears on the left of the illustration, and the memory appears on the right. The memory stores instructions and data. The memory chip can be either ROM, RAM, or any other chip that happens to contain memory.

Viewing Figure 2.6, we will assume that the program counter holds an address, which is the address of the next instruction to be fetched from the memory.

Every microprocessor proceeds in three cycles, which involve:

- 1. fetching the next instruction

- 2. decoding the instruction

- 3. executing the instruction.

Let us now discuss each cycle.

## FETCHING

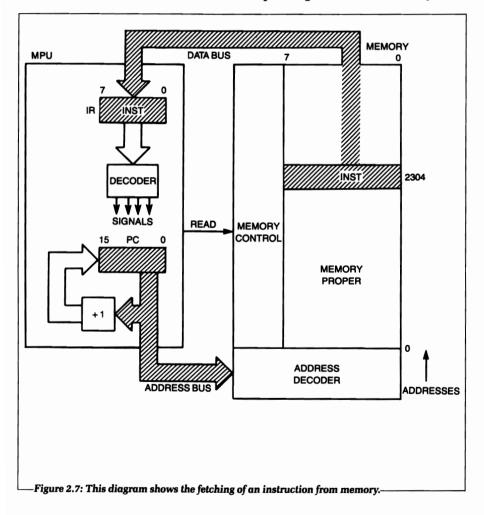

In the first cycle, the contents of the program counter are placed on the system address bus and input to memory at the correct time. The control bus then generates a memory read signal. When the memory reaches the read signal, data stored in memory at the specified address is placed on the system data bus. The microprocessor then reads the information on the data bus into an internal register called the *instruction* register (or IR). The information read into the CPU is the instruction. We can say that the

instruction has been fetched from memory. Figure 2.7 is a block diagram showing the fetching of an instruction from memory.

## DECODING AND EXECUTING

Once the instruction is in the IR, the control unit of the microprocessor decodes it and generates the correct sequence of internal and external signals for its execution. Some time, typically one clock period, is necessary for the CPU to decode an instruction and logically decide what action to take. We will see later on that the 8086/8088 puts to good use this normally

"idle" time (i.e., the time waiting for the CPU to decode the instruction).

Once the CPU has decoded the instruction, it then performs a series of events, dictated by the instruction. Some instructions require simple tasks and thus take little time to execute; others require several events to occur and thus take longer. The speed of execution for an instruction is usually expressed in the total number of clock cycles required for completion.

#### FETCHING THE NEXT INSTRUCTION

We have just described how an instruction is fetched from memory, using the program counter. During the execution of a program, instructions are fetched in sequence. It is, therefore, necessary for an automatic mechanism, called an *incrementer*, to be provided to fetch instructions in sequence. The incrementer is attached to the program counter, as shown in Figure 2.7.

It must be stressed that the preceding descriptions are simplified. In reality, some instructions may be two, three, or six bytes long and, in such cases, the PC must logically decide how many bytes are contained in each instruction, before the next instruction starts. We will be discussing more about the function of the PC as we detail the internal architecture of the 8086/8088.

## **INTERNAL ORGANIZATION OF THE 8086/8088**

So far, we have discussed (in general terms) how a microprocessor system is organized, and we have examined the internal architecture of a CPU. Let us now build on this information and detail the actual internal architecture of the 8086/8088. Once you understand this program, it is much easier to understand the topic of addressing modes (presented in the following chapter).

The internal architectures of the 8086 and 8088 are virtually identical from a programming point of view. Software written for the 8086 will run on the 8088 with no modifications. The reverse is also true. (*Note:* It is important to note that the hardware implementation of each microprocessor is quite unique, but this is of little concern to us here, since we are concentrating on programming in this text.)

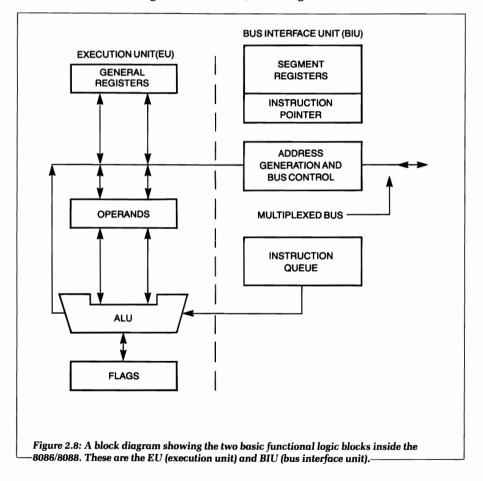

Figure 2.8 shows a functional block diagram of the 8086/8088. This diagram shows that there are two main functional logic blocks in the device: the BIU (bus interface unit) and the EU (execution unit). In the general block diagram back in Figure 2.2, both of these functions were grouped into a single control block. Let us examine what they do. The major function of the BIU in the 8086/8088 is to provide the physical interface between the 8086/8088 and the "outside" world. The BIU controls the system address, data, and control buses. It can operate in parallel with the EU. One of the unique features of the BIU is its "instruction prefetch" capability. To understand what this means, consider the following.

When the PCU executes instructions, it first fetches the instruction from memory and then decodes it. During the decoding time the external buses of the CPU are idle. In other words, there is no activity on the buses because the CPU does not electrically know what to do, as the instruction has not yet been decoded.

In the 8086/8088, the BIU fetches an instruction from memory and then while the EU is decoding that instruction, the BIU gets the next instruction

from memory. In this way, the next instruction is "prefetched" and waiting to be executed by the CPU. As a matter of fact, the 8086 can have up to six bytes of information in the instruction queue, while the 8088 can have up to four.

Some instructions on the 8086/8088 are executed completely internally in the CPU, and can require many clock cycles. An example of this type of instruction would be the DIVIDE instruction. During the time that the CPU is performing the division, the BIU is prefetching data from memory, up to the maximum number of bytes that can be held in the queue.

Prefetching data from memory reduces the overall instruction execution time. This is because the instruction fetch time does not have to be counted in the overall execution time. This statement is not always true, however, because there will be times when an entire instruction must be obtained without a prefetch. This occurs whenever the queue is flushed or reset. For example, whenever the 8086/8088 executes a jump instruction, the queue is flushed and must be filled again. If you are not familiar with the jump instruction, you may not understand why the queue must be flushed. This will be made clear when the instruction set is given in Chapter 4.

The other functional hardware section of the 8086/8088 shown in Figure 2.8 is the execution unit. This unit contains a 16-bit arithmetic logic unit. It maintains the condition flags of the CPU. The EU also manipulates the general registers of the CPU. All registers in the EU are 16 bits wide. This is true of both the 8086 and 8088.

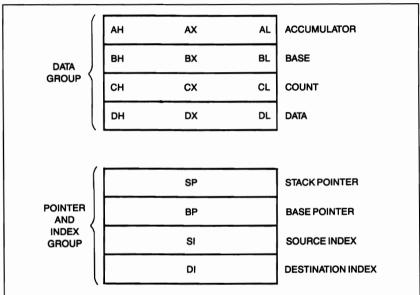

## 8086/8088 GENERAL REGISTERS

Figure 2.9 shows the general registers of the 8086/8088. We can seen in this figure that there are two main groups: the data group, and the pointer and index group. Each register is 16 bits wide. The data group is labeled AX, BX, CX and DX. They can be used as a single 16-bit register or as two 8-bit registers. When used as two 8-bit registers, they are divided into an upper (H) and lower (L) half, labeled AH, AL, BH, BL, CH, CL, and DH, DL.

The pointer and index group of registers (shown in Figure 2.9) are used only as 16-bit registers. These registers are labeled SP (stack pointer), BP (base pointer), SI (source index), and DI (destination index). The reasoning behind these names will become clear later on in the text when we discuss the various addressing modes and show programming examples for the 8086/8088. For now, it is only important to know that these registers exist, and how they are organized.

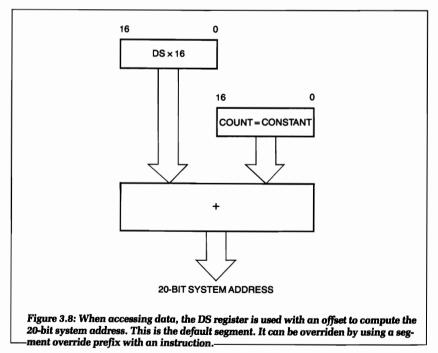

## SEGMENT REGISTERS

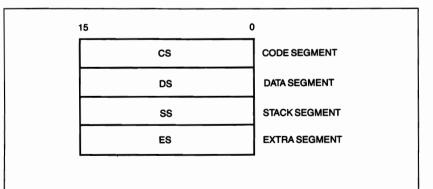

There are four segment registers in the 8086/8088, as shown in Figure 2.10. We will give a brief description of the segment registers now and a more detailed description in Chapter 3. Each segment register is 16 bits in length and each has a particular name: code segment (CS), data segment

-Figure 2.9: This diagram shows the general internal registers of the 8086/8088.-

Figure 2.10: This diagram shows the four segment registers of the 8086/8088. These reg--isters are logically combined with the general registers to form a 20-bit system address. (DS), stack segment (SS) and extra segment (ES). The names are useful for understanding how the segment registers are used during program execution.

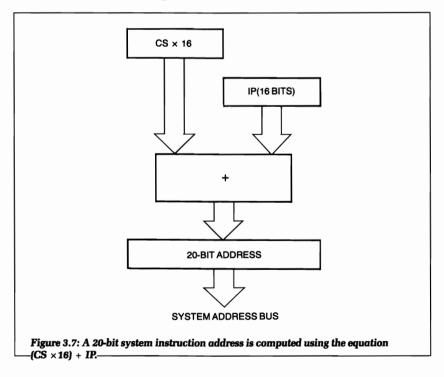

These registers are combined with other internal registers during program execution to form a complete 20-bit system address for the CPU external address bus. For example, when performing a PUSH or POP operation with the stack, the SS register is combined logically with other registers to form the memory address at points to the top of the stack. We will expand on this in the addressing mode discussion in Chapter 3.

#### **INSTRUCTION POINTER**

In the description of the general block diagram of a microprocessor shown in Figure 2.2, we discussed the operation of the program counter. In the 8086/8088 the program counter is replaced by the instruction pointer (IP) register. The IP register is updated by the BIU to point to the address of the next instruction. Programs do not have direct access to the instruction pointer; but, during execution of a program, the IP can be modified or saved and restored from the stack.

## FLAGS

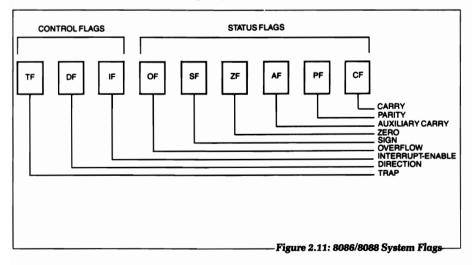

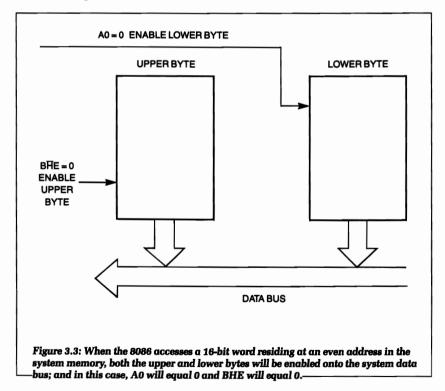

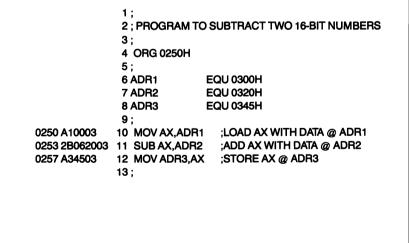

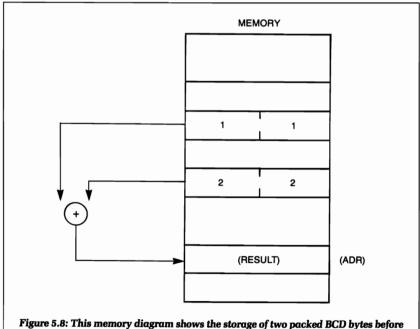

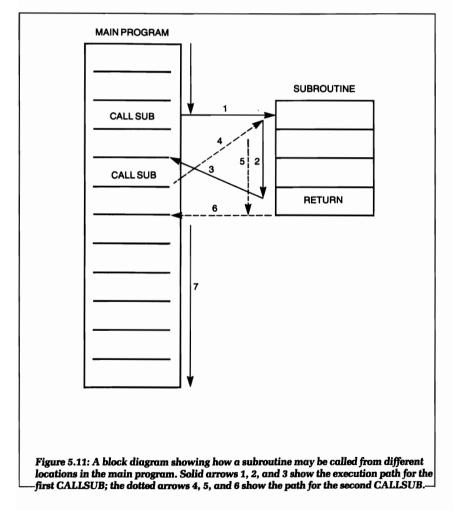

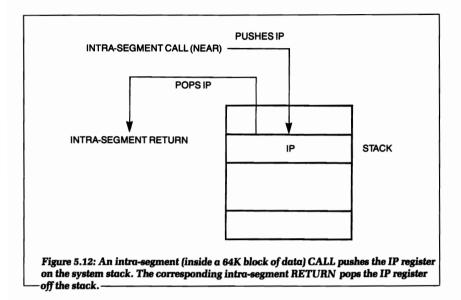

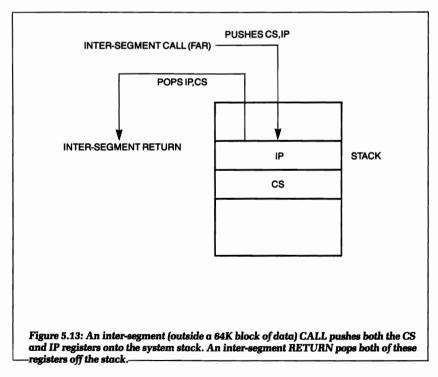

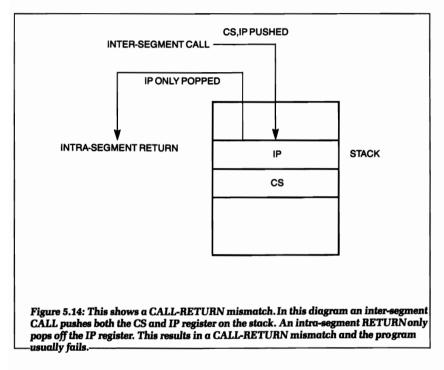

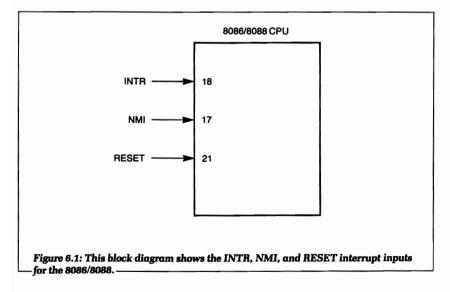

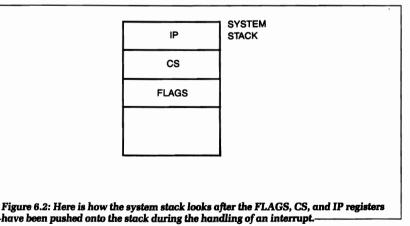

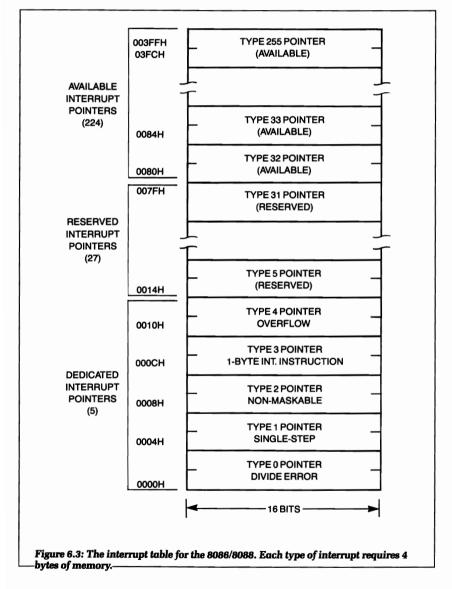

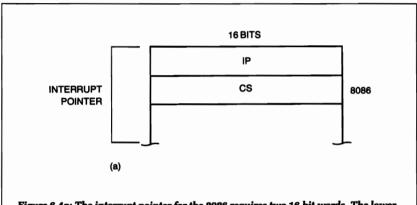

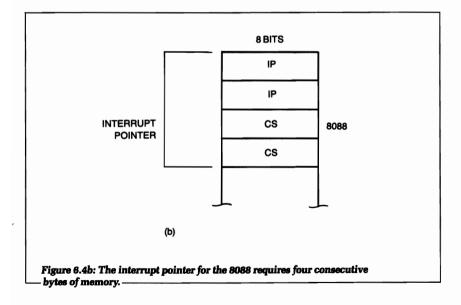

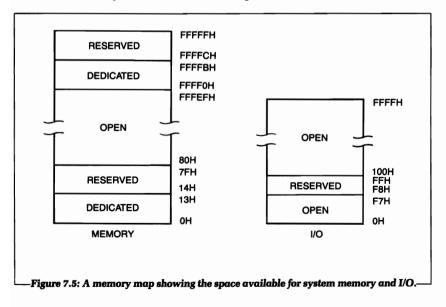

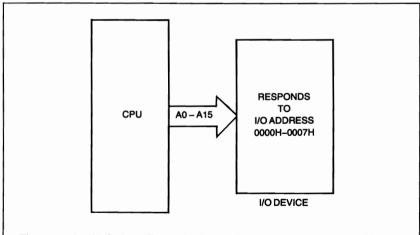

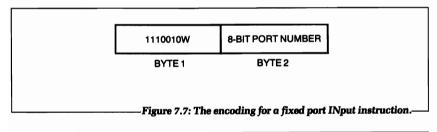

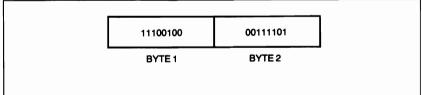

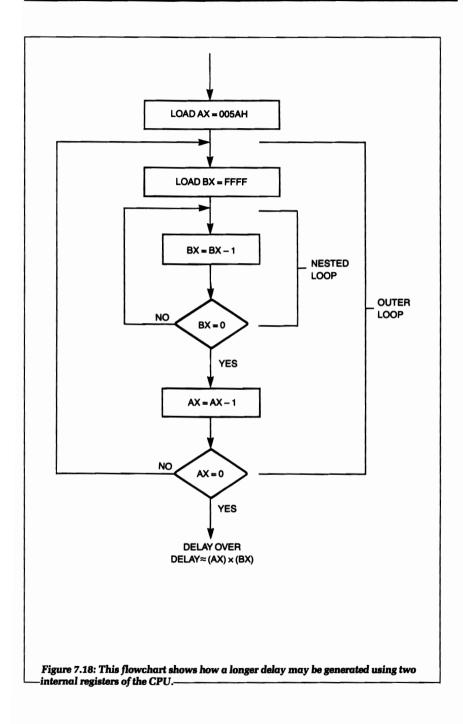

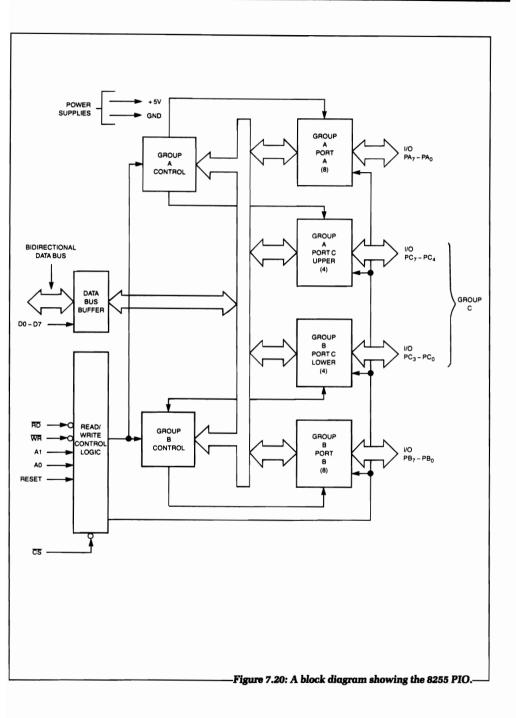

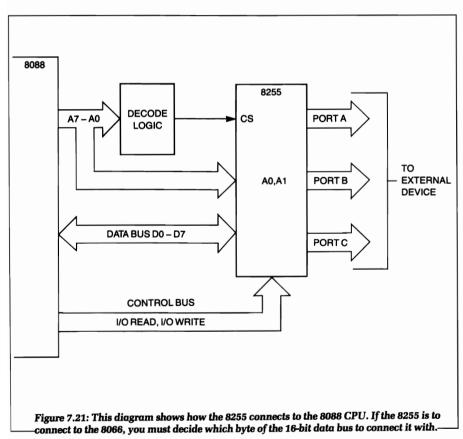

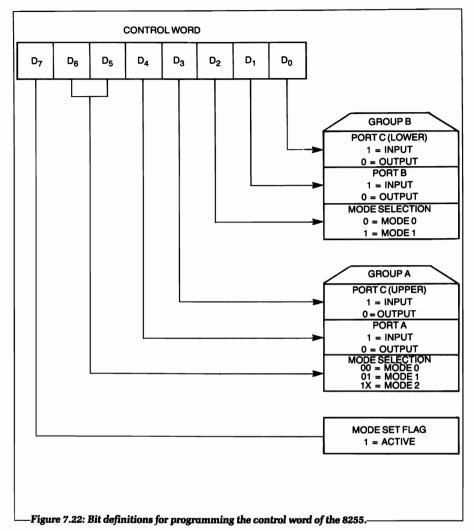

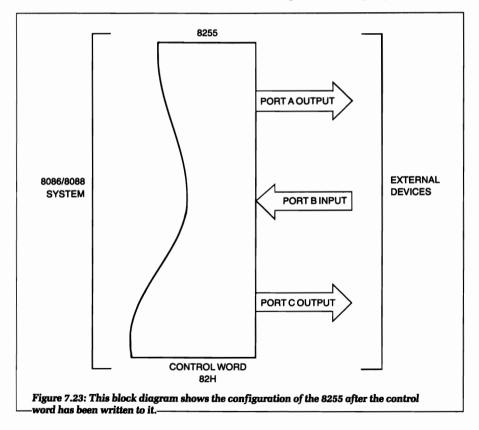

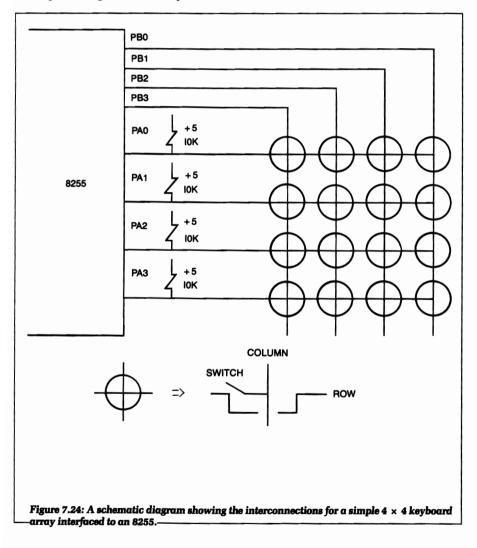

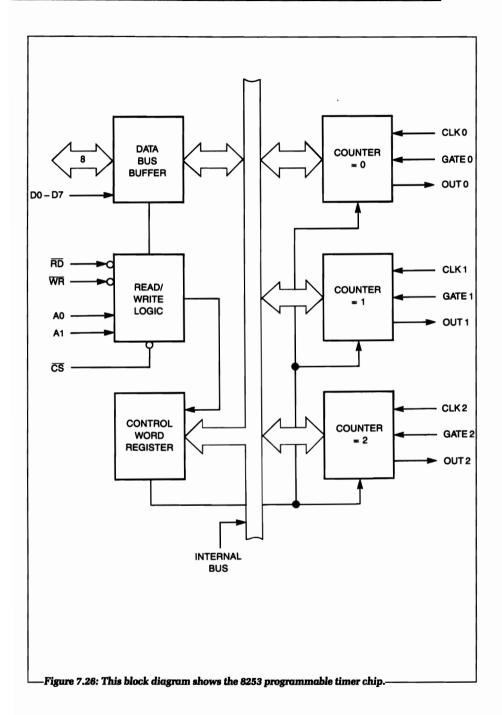

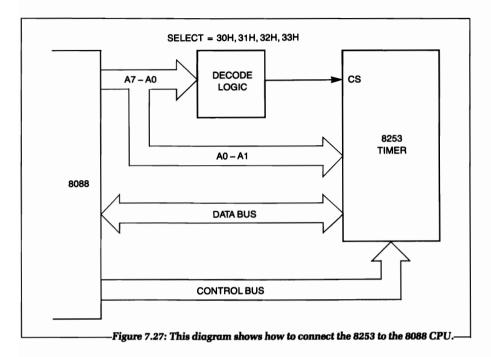

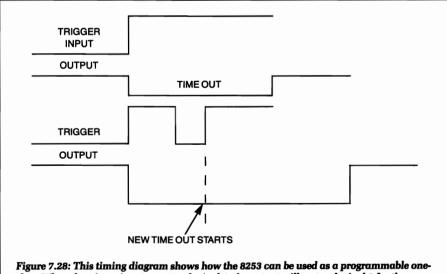

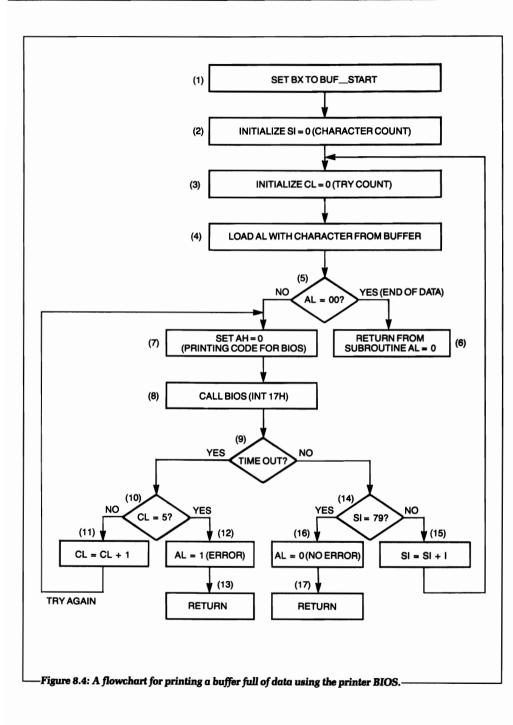

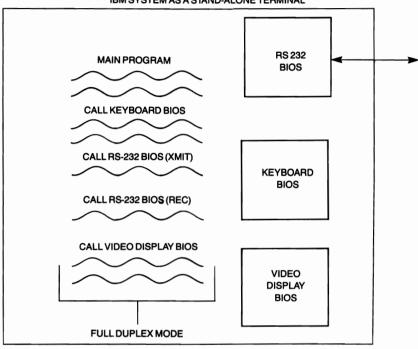

The 8086/8088 have six 1-bit status or condition flags that are updated by the EU. These flags, shown Figure 2.11, represent the condition of the result of an arithmetic or logic operation that has just occurred. In Chapter