**Achtung:**

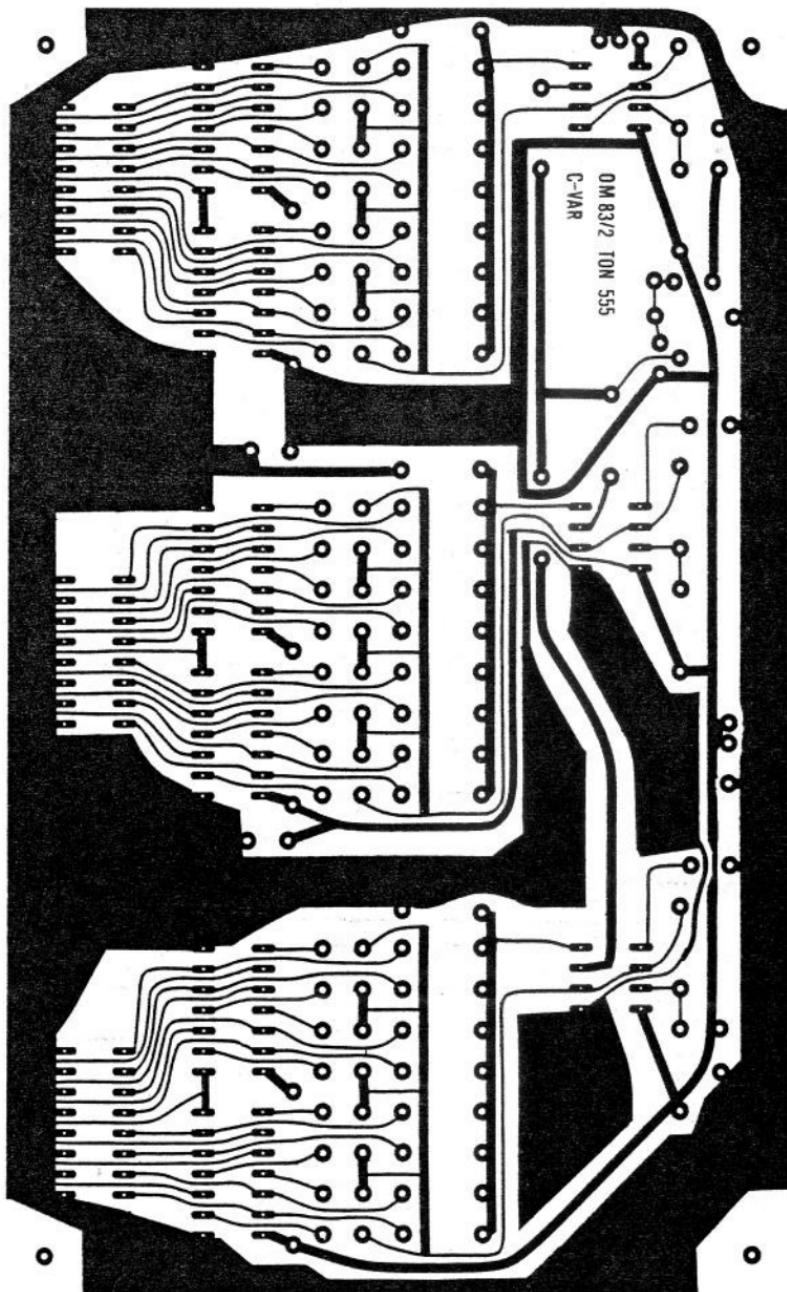

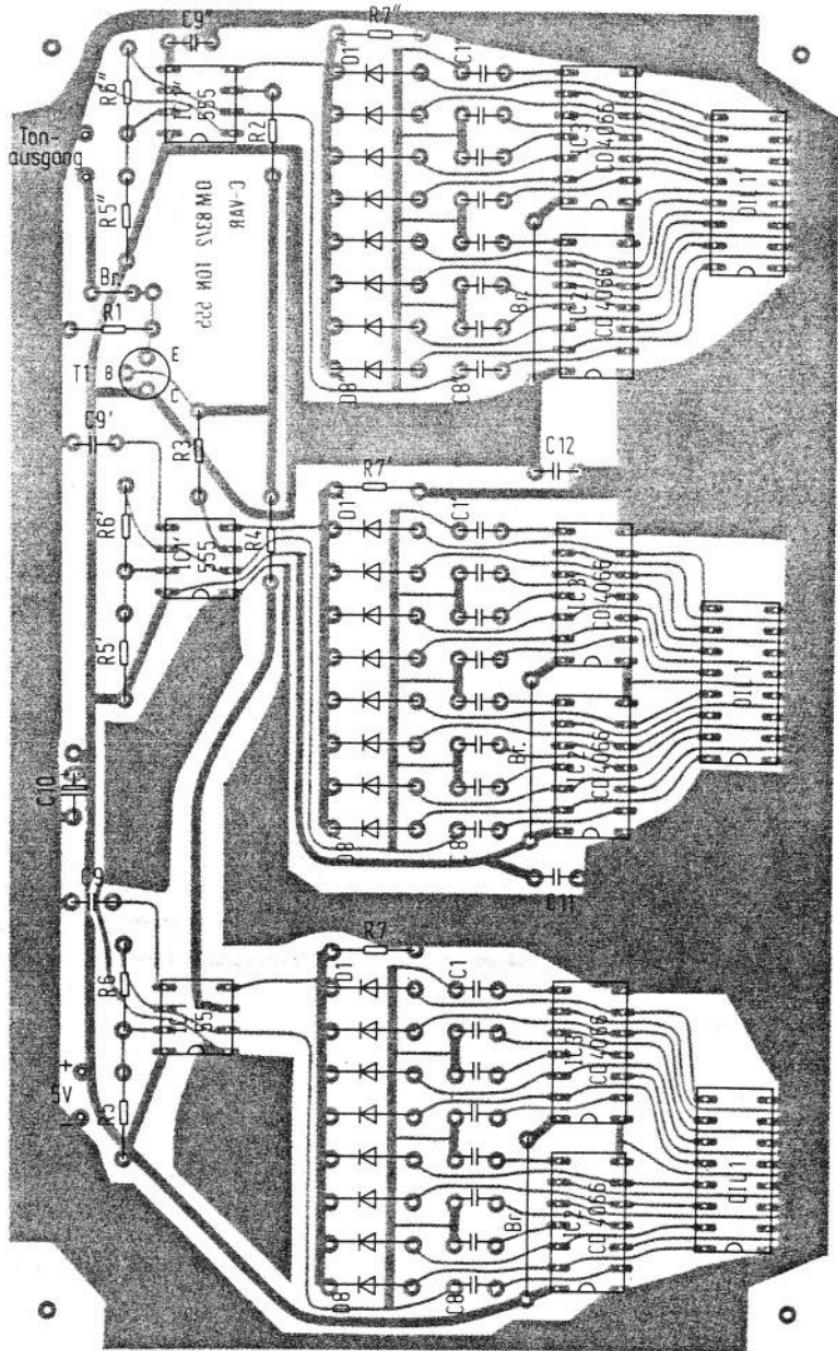

**Textseiten mit 300 dpi gescannt,

Platinenseiten und Layoutseiten

mit 600 dpi gescannt !**

**Beim Ausdrucken der

Platinenseiten aus Photoshop

oder Adobe Reader heraus -

unbedingt 100% wählen bzw.

unter keinen Umständen

“an Seite anpassen” benutzen,

da sonst die Löcherabstände

nicht mehr stimmen. Im

Zweifelsfall Probeausdruck

fertigen und IC-Fassung

( möglichst lang ) an Ausdruck

halten und Abstände vergleichen!**

# Merkel

# Hardware-Erweiterungen

# für den ZX 81

Der nachträgliche Einbau von Schnittstellen zum Messen, Steuern und Regeln

- Wie funktioniert ein Computer?

- Daten und Befehle

- Die Z-80-CPU

- Der Mikrocomputer ZX 81

- I/O-Ports

- Language Card

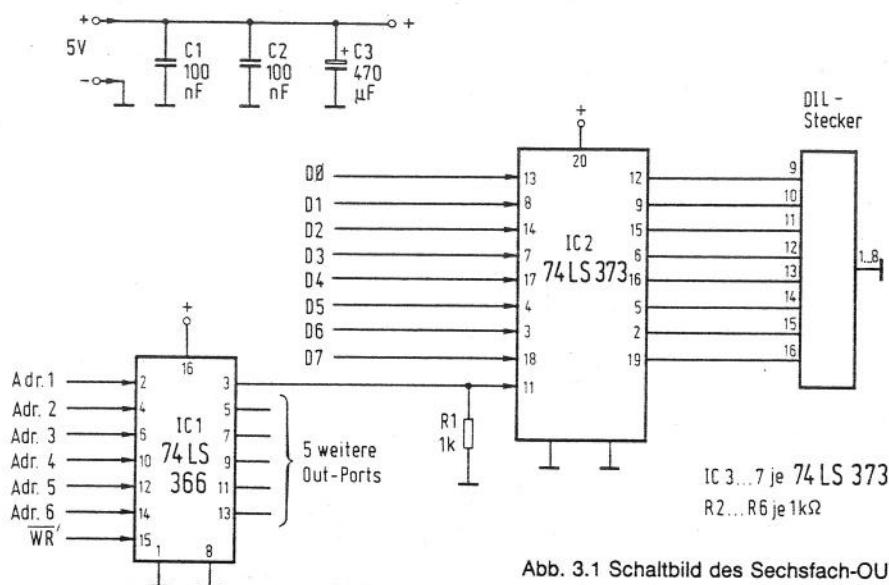

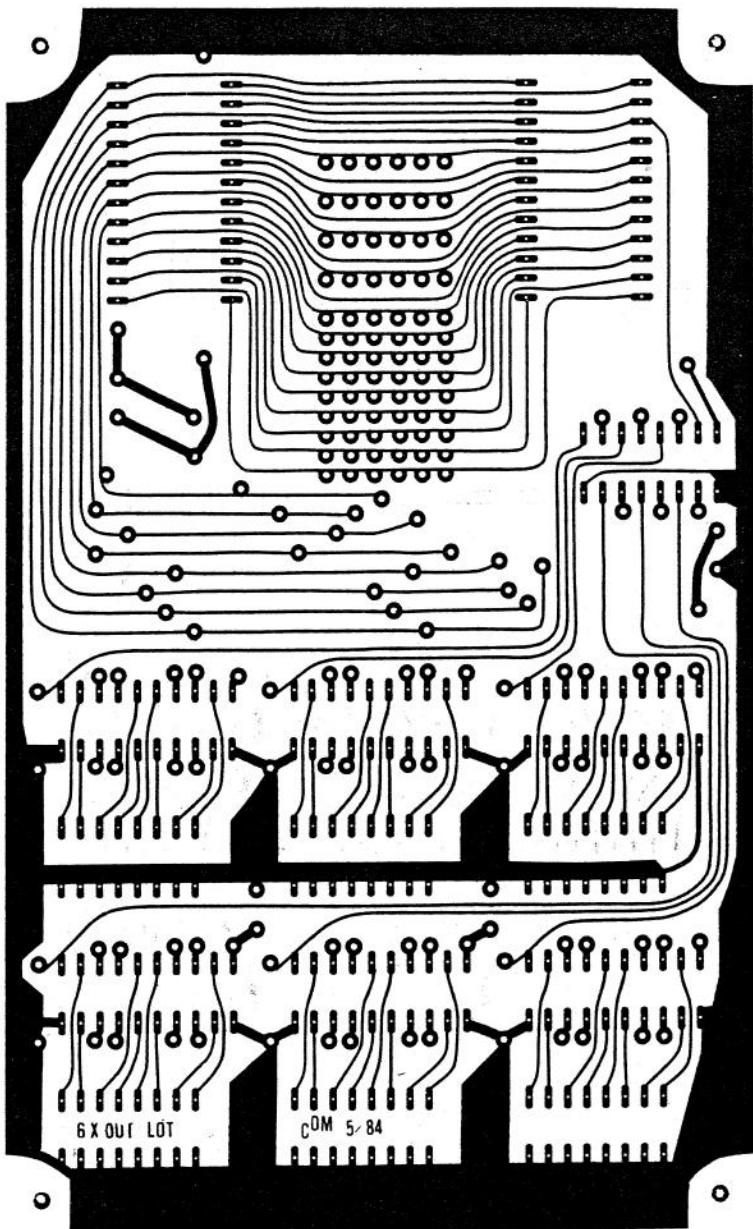

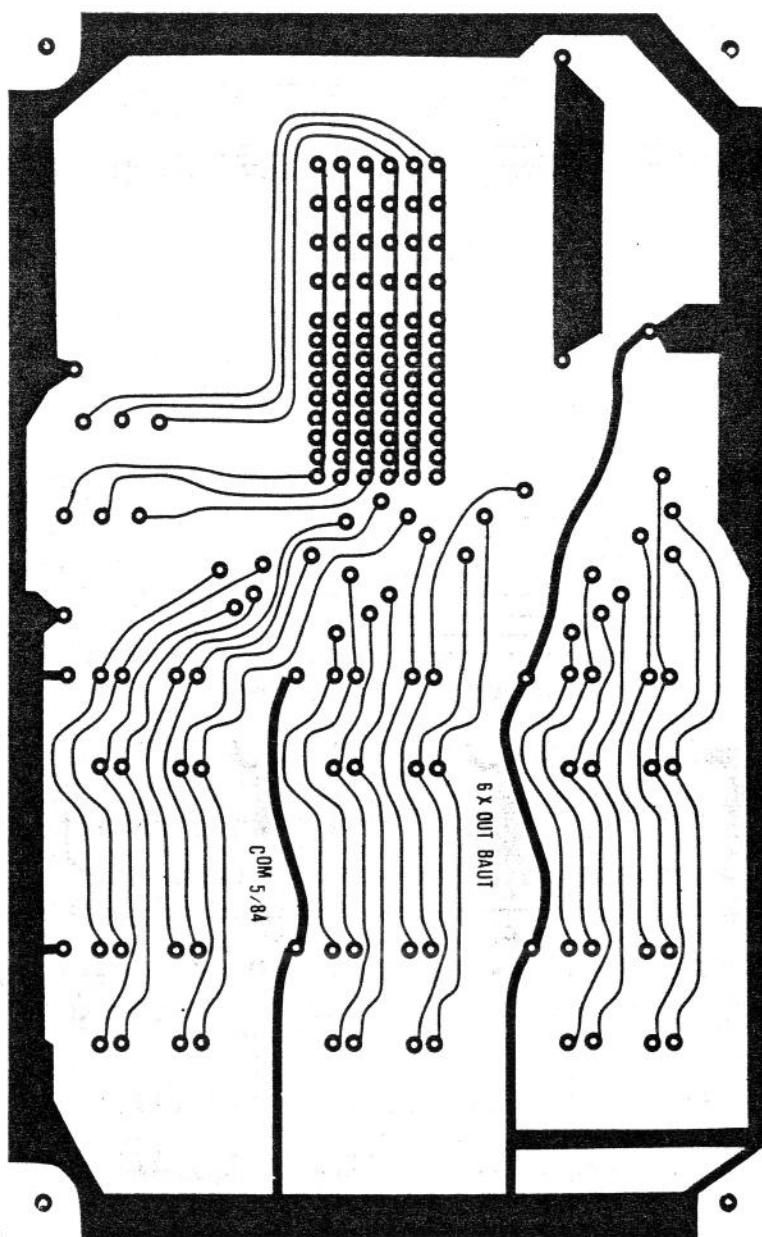

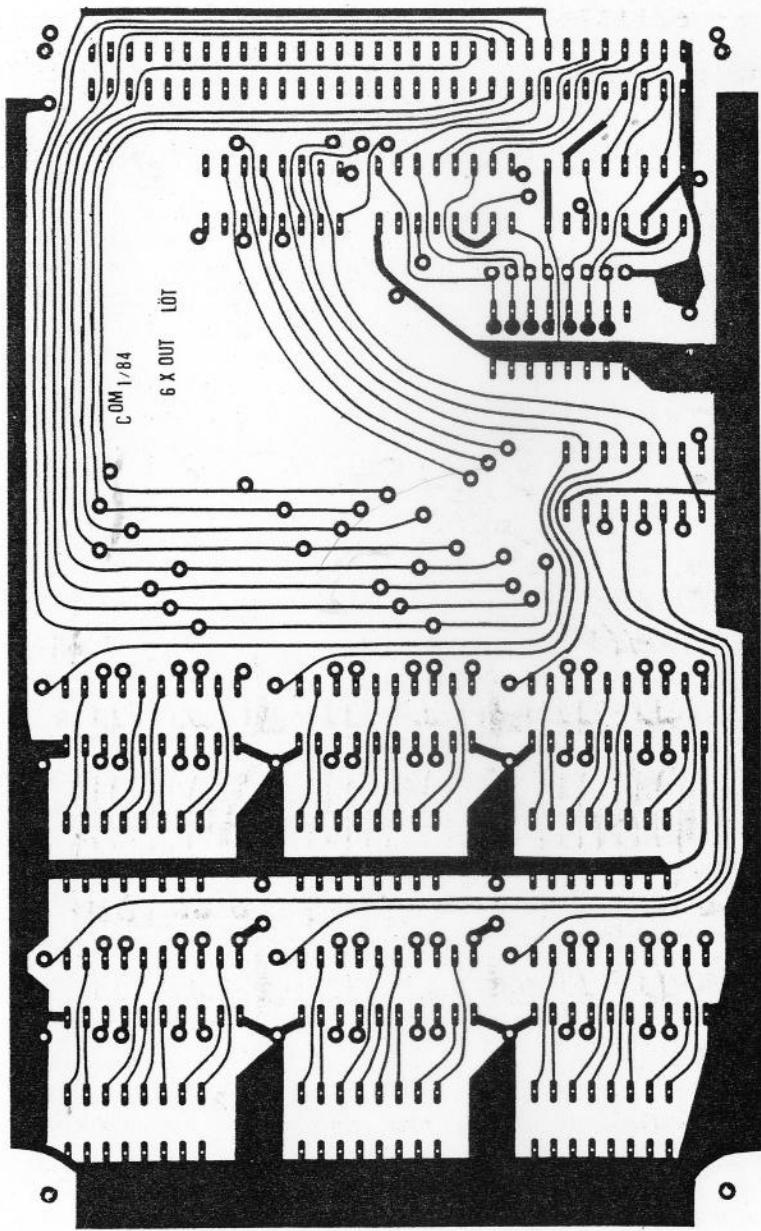

- Sachsfach OUT-Port

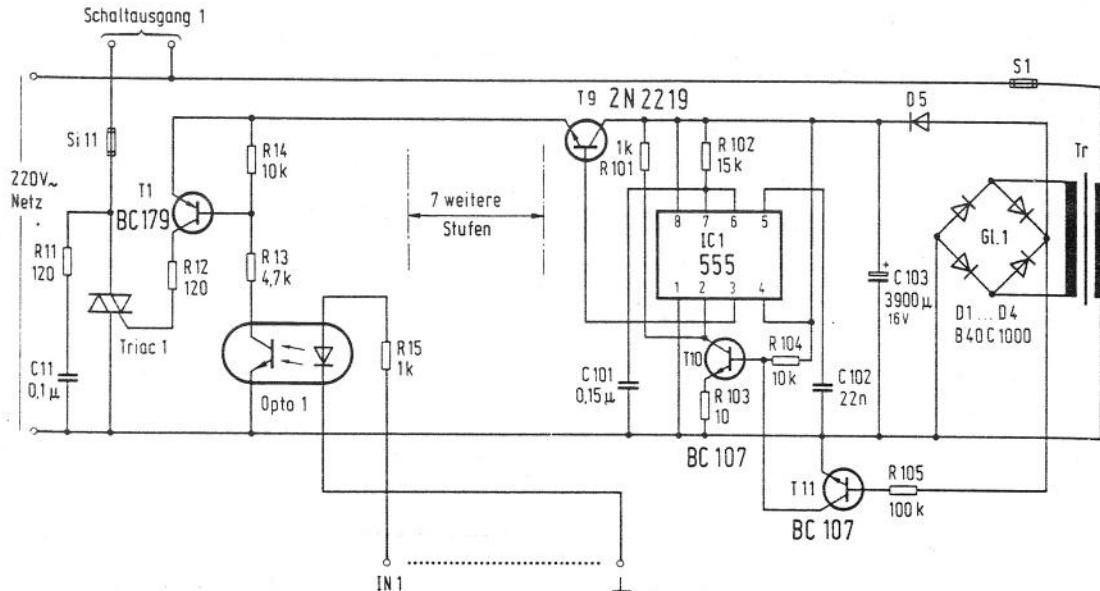

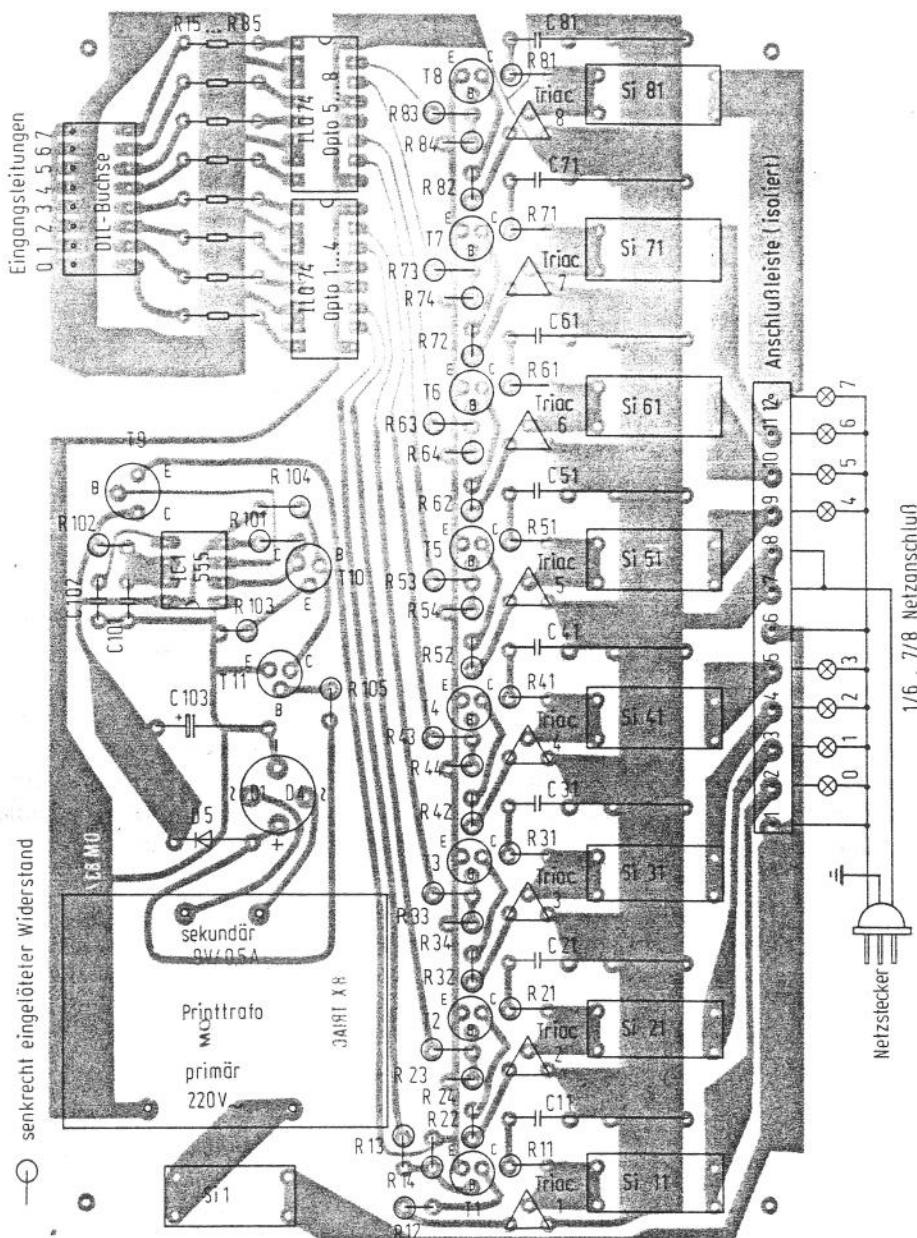

- Schaltung des Thrac Interface

- Set/Reset IN-Port

- Padline-Speicherung

- AVD-Harddisk

- Schaltung zur Hardware Dekodierung

- Über Anschlüsse

- Sound-ROM

- Steuerkopplung

- Spezialanwendungen

- Brennanzewen

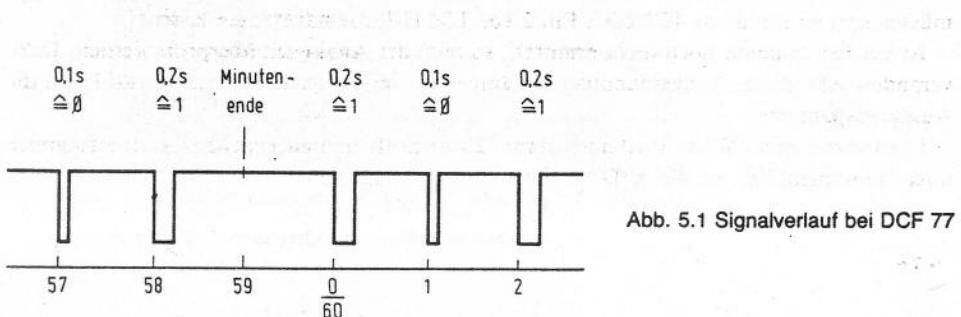

- Dekodierung des Zeitzeichensenders DCE

chert ist. Nach Abarbeitung dieses Programms kehrt sie wieder zum ursprünglichen Programm zurück.

Die Interrupt-Bearbeitung kann softwaremäßig unterdrückt („maskiert“) werden, so daß trotz Signal auf Leitung 16 keine Programmunterbrechung stattfindet.

Diese Leitung (Pin 17) hat dieselbe Funktion wie die INT-Leitung, mit dem einzigen Unterschied, daß dieses Signal nicht blockiert werden kann.

*l) WAIT (wait, Warten)*

Es kann vorkommen, daß die CPU zu schnell für die angeschlossenen Speicher oder Peripheriebausteine ist. Dies können die Bausteine der CPU über ein L-Signal an Pin 24 signalisieren. Die CPU führt dann WAIT-Zyklen durch, bis die Bausteine soweit sind.

*m) RESET (reset, Zurücksetzen)*

Nach Einschalten der Betriebsspannung muß der Prozessor in einen definierten Ausgangszustand gebracht werden. Dies wird erreicht, indem der RESET-Eingang (Pin 26) kurzzeitig auf L-Pegel gelegt wird. Anschließend beginnt die CPU mit der Programmabarbeitung ab Adresse 0000.

*n) BUSRQ (bus request, Busanforderung)*

In gewissen Fällen kann es notwendig werden, daß die CPU die Kontrolle über die Adress-, Daten- und Steuerbusleitungen aufgibt. Dies ist zum Beispiel der Fall, wenn Peripheriebausteine schnell große Datenmengen in den Speicher einlesen oder aus ihm heraus transferieren sollen (DMA: direct memory access, direkter Speicherzugriff).

Um dies zu erreichen, wird ein L-Signal an den BUSRQ-Eingang (Pin 25) gegeben. Dadurch werden alle Tristate-Ausgänge der CPU hochohmig, so daß sie diese Leitungen nicht mehr beeinflußt.

*o) BUSAK (bus acknowledgement, Bus-Anforderungsbestätigung)*

Wenn eine Busanforderung von der CPU akzeptiert wird, signalisiert sie das durch L-Pegel auf Leitung 23. Jetzt kann die Peripherie auf die Leitungen zugreifen.

### 1.3.2 Programmabarbeitung durch die Z-80-CPU

Etwas vereinfacht betrachtet besteht die CPU aus einer Anzahl von Registern (d. h. Speichern) und einer Logik- und Verarbeitungseinheit. In Abb. I.4 ist diese Registerstruktur der Z-80-CPU gezeigt. Um zu verstehen, wie ein Maschinenprogramm abläuft und wie Speicherbausteine bzw. Erweiterungsschaltungen angesprochen werden, ist es notwendig, sich damit vertraut zu machen.

Die Register A,B,C,D,E,H und L sind jeweils 8 Bit breite Speicher, die in einem Programm mit Daten geladen werden bzw. solche Daten auch ausgeben können. Das Register A (Akku) besitzt eine gewisse Sonderstellung, da es auch eine Reihe logischer Verknüpfungen durchzuführen gestattet.

Das F-Register (Flag, d. h. „Flagge“ oder besser Anzeigeregister) gibt Auskunft über den Status des Prozessors und kann über verschiedene Befehle beeinflußt und auch auf seinen Inhalt hin abgefragt werden.

|                                     |            |                       |             |

|-------------------------------------|------------|-----------------------|-------------|

| Akkumulator<br>A                    | Flags<br>F | Akkumulator<br>A'     | Flags<br>F' |

| B                                   | C          | B'                    | C'          |

| D                                   | E          | D'                    | E'          |

| H                                   | L          | H'                    | L'          |

| Interrupt Register<br>I             |            | Refresh Register<br>R |             |

| Index Register                      |            | IX                    |             |

| Index Register                      |            | IY                    |             |

| Stack Pointer<br>(Stapelzeiger)     |            | SP                    |             |

| Programm Counter<br>(Befehlszähler) |            | PC                    |             |

Abb. 1.4 Innerer Aufbau und Register der Z-80-CPU

Für viele Anwendungszwecke ist es von Bedeutung, daß die Registerpaare BC, DE und HL zu 16-Bit-Registern zusammengefaßt werden können und damit Zahlenwerte zwischen 0 und 65535 darstellbar sind. Auf diese Weise ist es sehr einfach möglich, einen Adressenwert zu speichern.

Der gesamte Registersatz ist in der CPU doppelt vorhanden. Durch Befehle ist ein Umsteigen auf den Zweitregistersatz möglich, wobei die bisherigen Registerinhalte nun „versteckt“ im Hintergrundregistersatz erhalten bleiben.

Das Interrupt-Register I kann mit Daten geladen werden, die beim Aufruf eines Interrupts (zur Erinnerung: dabei wird die INT-Leitung der CPU auf L-Pegel gezogen) wichtig sind. Der ZX 81 benützt dieses Register zum Auffinden seines Zeichensatzes bei der Bildschirmausgabe von Texten.

Das Refresh-Register R ist wichtig bei der Verwendung von dynamischen Speicher-ICs. Diese Bausteine verlieren ihre eingeschriebenen Daten, wenn nicht innerhalb bestimmter Zeitabstände eine „Auffrischung“ stattfindet. Dabei merkt sich das R-Register, welche Speicherzellen als letztes aufgefrischt wurden. Beim ZX 81 wird dieses Register im Zusammenhang mit der Bildschirmausgabe „zweckentfremdet“.

Die Index-Register IX und IY sind für Adressierungen relativ zu bestimmten Werten von Bedeutung.

## 1 Wie funktioniert ein Computer?

Das PC-Register (program-counter - Befehlszähler) führt eine 16-Bit-Adresse, die auf die Speicherstelle zeigt, die den momentan ausgeführten Befehl enthält. Zu Beginn, d. h. nach einem Reset, beginnt der Befehlszähler bei Adresse 0. Mit jedem abgearbeiteten Befehl wird der Befehlszähler um eins bzw. mehr inkrementiert (erhöht), je nachdem wie lang der jeweilige Befehl war. Falls die CPU dabei auf einen Sprungbefehl oder Unterprogrammaufruf trifft, wird die Adresse, bei der das Programm fortgesetzt werden soll, in den Befehlszähler übernommen.

Das SP-Register (stack pointer - Stapelzeiger) zeigt auf die Speicheradresse, bei der der „Stapel“ beginnt. Dieser Stapel beinhaltet (u.a.) Adressen, die beim Aufruf von Unterprogrammen dort abgelegt wurden. Es handelt sich dabei um die Adreßwerte, die der Befehlszähler beim Sprung in ein Unterprogramm besitzt. Auf diese Weise ist nach dem Abarbeiten des Unterprogramms ein Rücksprung in die richtige Adresse des Hauptprogramms möglich.

Anhand eines kleinen Beispielprogramms soll die Arbeitsweise verdeutlicht werden (alle Zahlenangaben sind dabei hexadezimal):

| Speicheradresse | Befehl | Mnemonik    |

|-----------------|--------|-------------|

| 0000            | 31     | LD SP, FFFF |

| 0001            | FF     |             |

| 0002            | FF     |             |

| 0003            | 21     | LD HL, FF00 |

| 0004            | 00     |             |

| 0005            | FF     |             |

| 0006            | 01     | LD BC, F000 |

| 0007            | 00     |             |

| 0008            | F0     |             |

| 0009            | CD     | CALL 0011   |

| 000A            | 00     |             |

| 000B            | 11     |             |

| 000C            | C3     | JP 0003     |

| 000D            | 00     |             |

| 000E            | 03     |             |

| 000F            | XX     |             |

| 0010            | XX     |             |

| 0011            | 7E     | LD A, (HL)  |

| 0012            | 02     | LD (BC), A  |

| 0013            | C9     | RET         |

| 0014            | XX     |             |

| 0015            | XX     |             |

| 0016            | XX     |             |

Nach einem Reset besitzt der Befehlszähler den Wert 0000. Dadurch wird die Speicherstelle 0000 adressiert und der dort (z. B. in einem ROM) gespeicherte Wert 31h (=49d) von der CPU gelesen. Sie weiß darauf hin, daß ein Ladebefehl für das SP-Registerpaar vorliegt und lädt es mit dem Wert 65535d. Auf Adresse 3 findet die CPU einen Ladebefehl (21h = 33d)

für das HL-Registerpaar. Daraufhin erhält das H-Register (high: höherwertiges Byte) FFh (= 255d), L (low: niederwertiges Byte) 00. Damit zeigt das HL-Register auf den Wert 65280d ( $255 \times 256 + 0 \times 1$ ).

Nun besitzt das PC-Register den Wert 6 und liest in entsprechender Weise den Ladebefehl für das BC-Register. Dort wird dadurch der Wert 61440 eingeschrieben.

Mit dem PC-Wert 9 wird der Befehl zum Aufruf eines Unterprogramms, das auf der Adresse 17d beginnt, gefunden. Daraufhin erhält PC den Inhalt 17d, gleichzeitig wird in die Speicheradresse, auf die (SP-2) zeigt (nämlich 65533) 12d (= 0Ch) geladen, die Speicherstelle 65534 (SP-1) erhält 00. Auf diese Weise wird für den Rücksprung nach dem Abarbeiten des Unterprogramms die Adresse des nächsten Befehls gespeichert. Der Stack Pointer besitzt nun den Wert 65533. Der Stapelbereich erstreckt sich also von höheren Adressen zu niedrigeren.

Das Unterprogramm lädt den Akku mit dem Inhalt der Adresse, auf die HL zeigt (65280d). Dabei kann es sich um Daten in einer Speicherstelle handeln oder auch um Informationen, die eine eventuell auf dieser Adresse angeschlossene Peripherie (z. B. ein Eingabeport) liefert. Diesen Zahlenwert schreibt der Befehl in die Speicherstelle ein, die das BC-Register adressiert (61440). Auch hier kann es sich sowohl um eine Speicherstelle (RAM) als auch um einen Peripherie-Baustein, z. B. ein Ausgabeport handeln.

Beim PC-Wert 19d (13h) wird der Befehl zum Rücksprung aus dem Unterprogramm gefunden. Daraufhin erhält PC den Inhalt 12d (0Ch) aus dem Stapel, der Stack Pointer zeigt wieder auf 65535. Es wird also wieder im normalen Programmablauf weitergearbeitet, wo ein Rücksprungbefehl zur Adresse 3 auftritt. Dadurch wird der Befehlszähler auf 3 gesetzt und der Programmdurchlauf beginnt wieder von vorne.

## 1.4 Der Mikrocomputer ZX 81

### 1.4.1 Struktur und Besonderheiten

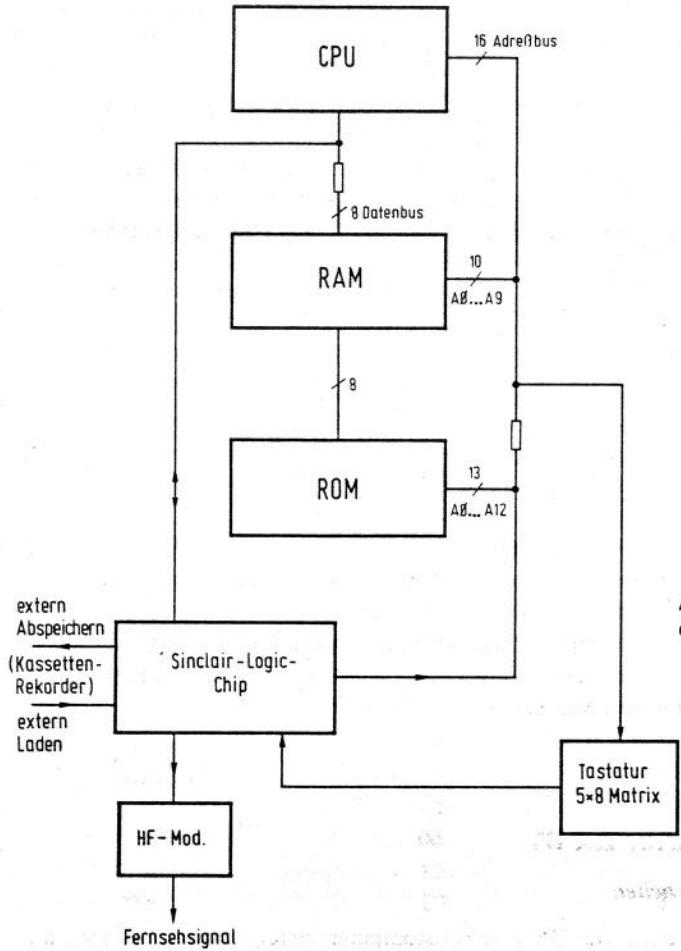

In Abb. 1.5 ist die Blockstruktur des ZX-81-Mikrocomputers gezeigt. Vergleicht man mit Abb. 1.1, so ist eine weitgehende Übereinstimmung zu erkennen. Im Detail weist die Schaltung allerdings einige Besonderheiten auf.

Die wichtigste Besonderheit stellt der Sinclair-Logic-Chip dar, ein kundenspezifischer Schaltkreis, der eine Reihe von Aufgaben ausführt, für die sonst ein mittleres „TTL-Grab“ nötig wäre. Der Vorgänger des ZX 81, der ZX 80, war noch in dieser Technik aufgebaut und enthielt über 20 integrierte Schaltungen. Dieses Sonder-ICwickelt unter anderem die Save/Load-Prozeduren für den Kassettenrekorder, die Tastaturerkennung in Zusammenarbeit mit der CPU und die Signalausgabe an das Fernsehgerät ab.

Eine weitere spezielle Eigenheit des ZX 81 ist die Tatsache, daß sich die CPU neben der eigentlichen Programmbehandlung um eine Menge zusätzlicher Dinge kümmert. So ist sie direkt an der Tastaturabfrage beteiligt, erstellt das Fernsehbild und steuert den Sinclair-Logic-Chip. Daraus resultiert allerdings eine gewisse Überbeschäftigung, wodurch die Zeit zum Abarbeiten eines Programms verlängert wird. Aus diesem Grund besitzt der ZX 81 einen FAST-Modus, während dem kein Fernsehbild ausgegeben wird, so daß die Rechengeschwindigkeit ansteigt.

## 1 Wie funktioniert ein Computer?

Abb. 1.5 Struktur des ZX-81-Mikrocomputers

Das 8-KByte-ROM enthält den BASIC-Interpreter und alle Steuerroutinen für Bildschirmausgabe, Tastaturabfrage und weitere Hilfsfunktionen. Das RAM umfaßt in der Grundversion 1-KByte, kann allerdings mit käuflichen Zusatzspeichern oder mit einer in diesem Buch vorgestellten Erweiterungsplatine vergrößert werden.

### 1.4.2 Tastaturbedienung

Der ZX 81 besitzt zur Programm- und Dateneingabe eine Folientastatur. Sie besteht aus zwei übereinandergeklebten Folien, die zueinander kreuzweise verlaufende Leiterbahnen enthält. Zwischen diesen beiden Folien befindet sich eine Isolierschicht, die an den Kreuzungspunkten Unterbrechungen aufweist. Die dort normalerweise isolierende Luftschicht wird bei Tastendruck überbrückt und schließt damit einen Schaltkontakt.

Abb. 1.6 Tastaturmatrix des ZX 81

Die Tastatur stellt also eine  $8 \times 5$ -Matrix dar (Abb. 1.6). Durch die Angabe von Zeilen- und Spaltennummer ist damit jede einzelne Taste eindeutig bestimmt. Die acht Zeilenleitungen sind über Dioden mit den Adreßleitungen A8 ... A15 der CPU direkt verbunden. Die fünf Spaltenleitungen werden über Widerstände an + 5 V gelegt. Sie erhalten dadurch den Signalpegel logisch 1. Diese Leitungen (KBD 0 ... 4) gelangen an die entsprechenden Eingänge des Sinclair-Logic-Chips (Pin 25, 27, 29, 31, 33). Betätigt man also beispielsweise die Taste „E“, so wird die Adreßleitung A10 mit der Leitung KBD 2 verbunden. Dies bleibt ohne Auswirkung auf den Zustand von KBD 2, solange A10 H-Pegel führt. Lag im Augenblick der Tastenbetätigung an A10 jedoch L-Pegel, so wird KBD 2 ebenfalls auf L-Pegel gezogen.

Die jeweils gedrückte Taste ist also durch L-Pegel auf Adreß- und Keyboard-Leitung (KBD) bestimmt. Um die gesamte Tastatur abzufragen, werden demnach alle Adreßleitungen nacheinander auf L-Pegel gelegt. Zu jeder angesprochenen Adreßleitung müssen dann die Keyboard-Leitungen auf L-Pegel getestet werden.

Die Abfrage erfolgt durch die CPU. Dabei wird die Tatsache ausgenutzt, daß etwa bei der Ausführung des Maschinenbefehls

IN A, (n)

## 1 Wie funktioniert ein Computer?

die untere Adreßbushälfte (A0 ... A7) durch die CPU mit dem Operanden n belegt wird (der Operand n wählt die Adresse des gewünschten Eingabekanals aus), während gleichzeitig auf der oberen Adreßbushälfte (A8 ... A15) der Inhalt des Akkus erscheint.

Ein Beispiel soll das Ganze verdeutlichen:

Mit dem Maschinenbefehl

LD A, 127d

wird in den Akku das Bitmuster 0111 1111 geladen. Anschließend erfolgt der Befehl

IN A, (254d).

Dadurch erscheint auf der Adreßleitung A15 eine logische 0. Wird nun gleichzeitig eine der Tasten unten rechts gedrückt (B/N/M/.Space), so erhält auch die entsprechende Keyboard-Leitung einen L-Pegel. Das Bitmuster auf den fünf Leitungen KBD 0 ... KBD 4 stellt also eine Binärzahl dar, deren Zahlenwert der gedrückten Taste entspricht.

Der Sinclair-Logic-Chip registriert diesen Zahlenwert und führt ihn dem Datenbus zu, so daß er in den Akku geladen wird. In Abb. 1.7 sind die über A8 ... A15 ausgegebenen Bitmuster (Zeilenauswahl) und die über den Datenbus eingelesenen Bitmuster (Spaltenauswahl) zusammengestellt. Damit kann jede einzelne Taste der Tastaturmatrix angesprochen werden. Dabei ist zu beachten, daß die ersten drei Bit der eingelesenen Bitmuster vom Sinclair-Logic-Chip bestimmt werden und unter Umständen nicht die Werte 0,1,1 haben. In Maschinensprache können diese Bits durch Undieren mit einem geeigneten Bitmuster maskiert werden. So liefert der nachgeschaltete Maschinenbefehl

AND 31d (31d = 0001 1111)

### Ausgegebenes Bitmuster und Zahlenwert

| Aktivierte Leitung | Bitmuster | Hex | Dez |

|--------------------|-----------|-----|-----|

| A15                | 0111 1111 | 7F  | 127 |

| A14                | 1011 1111 | BF  | 191 |

| A13                | 1101 1111 | DF  | 223 |

| A12                | 1110 1111 | EF  | 239 |

| A11                | 1111 0111 | F7  | 247 |

| A10                | 1111 1011 | FB  | 251 |

| A9                 | 1111 1101 | FD  | 253 |

| A8                 | 1111 1110 | FE  | 254 |

### Eingelesenes Bitmuster und Zahlenwert

| Aktivierte Leitung | Bitmuster | Hex | Dez      |

|--------------------|-----------|-----|----------|

| keine              | 0111 1111 | 7F  | 127 (31) |

| KBD 0              | 0111 1110 | 7E  | 126 (30) |

| KBD 1              | 0111 1101 | 7D  | 125 (29) |

| KBD 2              | 0111 1011 | 7B  | 123 (27) |

| KBD 3              | 0111 0111 | 77  | 119 (23) |

| KBD 4              | 0110 1111 | 6F  | 111 (15) |

Abb. 1.7 Bitmuster zur Tastaturabfrage

den reinen Tastencode. Die zugehörigen dezimalen Zahlenwerte sind in der Abb. 1.7 in Klammern gesetzt.

Möchte man in einem Maschinenprogramm z. B. testen, ob die BREAK(Space)-Taste gedrückt wurde, so fügt man an das oben begonnene Maschinenprogramm noch an:

```

AND 31d

CP30d

JP Z, nn.

```

Dabei stellt nn ein Sprungziel dar, wo die für den BREAK-Fall gewünschte Routine beginnt.

Soll die gesamte Tastaturmatrix abgefragt werden, so muß anschließend die Leitung A14 auf 0 gelegt werden, dann A13 usw. Das bedeutet, daß das im Akku enthaltene Bitmuster nach rechts rotieren muß (0111 1111, 1011 1111, 1101 1111, usw.). Hierfür kann der Maschinenbefehl RRCA (rotate right circular akku, 0Fh) verwendet werden. Damit kann diese Tastaturabfrage in einer Programmschleife integriert werden.

#### 1.4.3 Der Bildschirm

Der ZX 81 kann 22 Zeilen mit je 32 Zeichen darstellen, dazu kommt noch eine Kommando- und Anzeigenzeile im unteren Teil des Bildschirms. Da im Grafikmodus der Raum eines Zeichens in eine obere oder untere bzw. linke und rechte Hälfte aufgeteilt wird, ergibt das 44 vertikale und 64 horizontale Druckpositionen.

Nachdem Bildaufbau und -ausgabe im wesentlichen von der CPU bewerkstelligt werden, muß hierfür Rechenzeit aufgebracht werden. Daher ist der ZX 81 zwischen den beiden Betriebsarten „SLOW“ und „FAST“ umschaltbar. Im SLOW-Modus ist der Rechner relativ langsam, da ein Fernsehbild ausgegeben wird. Für das Rechnen steht dadurch nur die Zeit zwischen zwei Fernsehbildern, also in der Austastlücke, zur Verfügung. Wird der FAST-Modus eingeschaltet, so erfolgt keine Bildausgabe, so daß die Rechengeschwindigkeit wesentlich ansteigt.

Das Bild, das auf dem Fernsehschirm erscheint, benötigt im RAM-Speicher  $24 \times (32 + 1) + 1$  Plätze. Dies sind ein Byte für jedes Zeichen, dazu kommt noch je ein Byte für das Zeilenende (Wert 118: Symbol NEWLINE) sowie zu Beginn ein Symbol NEWLINE. Das ergibt 793 Byte Speicherbedarf. Damit wäre in der Grundversion des ZX 81 (Speicherinhalt 1 KByte) schon fast der gesamte RAM-Speicher belegt. Deshalb wird bei einem verfügbaren RAM-Speicher von weniger als  $3^{1/4}$  KByte nur ein Minimal-Bildschirm aufgebaut, der keine Leerzeichen enthält. Ein leerer Bildschirm besteht dann also aus 25 Speicherstellen, die alle den Wert 118 enthalten. Je mehr Bildinhalt dargestellt wird, desto größer wird der benötigte Speicherplatz, so daß man in der Grundversion sehr schnell an Speichergrenzen stößt. Daher wird in diesem Buch auch eine Speichererweiterung (zusätzliche 6 KByte RAM) beschrieben.

Die Größe des Bildschirmspeichers läßt sich durch Peeken der entsprechenden Systemvariablen berechnen: D-File (PRINT PEEK 16396 + 256 × PEEK 16397) zeigt auf den Beginn des Bildschirmspeichers, VARS (PRINT PEEK 16400 + 256 × PEEK 16401) auf den Beginn des Variablenbereichs, der sich unmittelbar an das Ende des Bildspeichers anschließt (vergleiche hierzu auch das ZX-81-Handbuch). Die Differenz dieser beiden Zahlenwerte ergibt die Größe des Bildspeichers.

## 1 Wie funktioniert ein Computer?

| Adresse | Bitmuster | Dezimal |  |  |  |  |  |  |  |  |  |

|---------|-----------|---------|--|--|--|--|--|--|--|--|--|

| 7984    | 00000000  | 0       |  |  |  |  |  |  |  |  |  |

| 7985    | 00111100  | 60      |  |  |  |  |  |  |  |  |  |

| 7986    | 01000010  | 66      |  |  |  |  |  |  |  |  |  |

| 7987    | 01000010  | 66      |  |  |  |  |  |  |  |  |  |

| 7988    | 01111110  | 126     |  |  |  |  |  |  |  |  |  |

| 7989    | 01000010  | 66      |  |  |  |  |  |  |  |  |  |

| 7990    | 01000010  | 66      |  |  |  |  |  |  |  |  |  |

| 7991    | 00000000  | 0       |  |  |  |  |  |  |  |  |  |

Abb. 1.8 Zeichen-darstellung im ROM

So ist es auch möglich, direkt Zeichen auf dem Bildschirm auszugeben, was vor allem beim Programmieren in Maschinensprache von Bedeutung ist. Der Einfachheit halber kann man es auch in BASIC probieren:

**POKE (PEEK 16396 + 256 × PEEK 16397 + 1), 38**

setzt den Buchstaben „A“ an die erste Printposition in Zeile 1. Entsprechend sind natürlich auch die anderen Stellen des Bildschirms erreichbar, auch die beiden Zeilen am unteren Rand des Bildschirms, die sonst für die normale Bildschirmausgabe nicht zur Verfügung stehen. Wird dabei eine Speicherstelle erwischt, die „118“ (Zeilende) enthält, gibt es Überraschungen. Aber keine Angst, kaputtgehen kann nichts, nach erneutem Einschalten funktioniert der Rechner wieder wie gewohnt.

Da an der Druckposition des Bildschirms lediglich der Zeichencode gespeichert ist, muß der Computer anhand des Codes noch das auszugebende Zeichen ermitteln. Hierzu ist im ROM ein Zeichengenerator enthalten. Der Zeichensatz ist gespeichert ab Adresse 7680d (1E00h) und umfaßt 512 Byte. Jedes einzelne Zeichen ist in einer 8 × 8-Matrix dargestellt.

Abb. 1.8 zeigt dies am Beispiel des Buchstabens „A“. Die Matrix-Positionen, die auf dem Bildschirm dunkel erscheinen, enthalten eine logische 1, die hellen Punkte eine logische 0. Daraus resultieren die dezimalen Zahlenwerte, die in Abb. 1.8 eingetragen sind.

Das nachfolgend aufgelistete Programm liest den Zeichengenerator ab Adresse 7680 aus und stellt die Zeichen in Großschrift auf dem Bildschirm dar.

```

1 REM AUSLESEN DES ZEICHEN-

2 REM GENERATORS - GROSSDARST

3 REM

4 REM

200 LET E=7680

300 LET Q=0

400 FOR J=E TO E+7

401 LET Z=PEEK J

410 POKE 16442,24-Q

420 LET I=PEEK 16442

430 IF 24-I<20 THEN GOTO 450

432 LET I=24

```

```

434 LET Q=0

436 CLS

450 PRINT AT 24-I,0;J

455 LET Q=Q+1

460 FOR K=1 TO 8

500 LET B=Z/2

600 IF Z-2*INT B=1 THEN PRINT A

T (24-I),24-K;"*";

601 IF Z-2*INT B=0 THEN PRINT A

T (24-I),24-K;" ";

650 LET Z=INT B

700 NEXT K

800 NEXT J

900 PAUSE 500

1000 CLS

1100 LET E=E+8

1101 POKE 16442,24

1102 LET Q=0

1200 GOTO 400

```

PROG 1

Interessant ist, wie der ZX 81 seinen Zeichengenerator findet. Dies geschieht über das Interrupt-Register I. Normalerweise enthält I den Wert 1Eh (30d). Dies sind die beiden führenden Ziffern einer 4stelligen Hex-Zahl. In dezimaler Schreibweise ist das also  $1 \times 4096 + 14 \times 256 = 7680$ , die Anfangsadresse des Zeichengenerators. Die beiden niederwertigen Stellen der Hex-Zahl werden durch den jeweiligen Zifferncode gebildet.

Beispiel: Der Buchstabe „A“ hat den Code 38d (26h). Also enthält der Zeichengenerator den Buchstaben „A“ ab der Adresse 7984 (7680 + 38 × 8, da jedes Zeichen 8 Byte umfaßt).

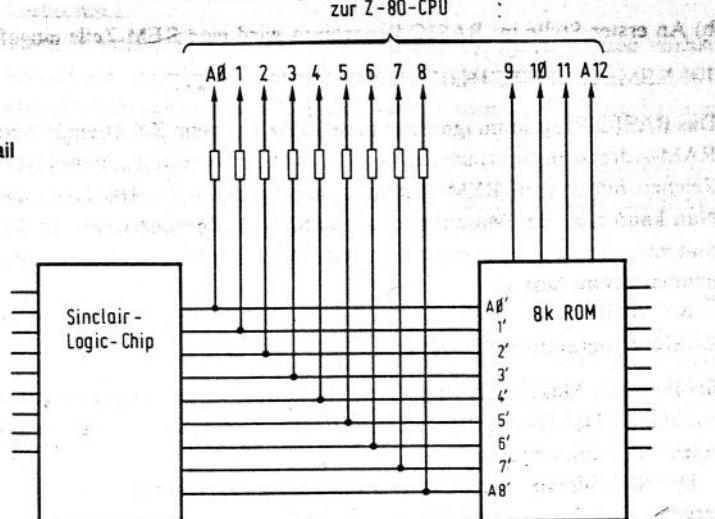

Man könnte auf die Idee kommen, einen eigenen Zeichensatz zu definieren, indem man das Interrupt-Register beispielsweise mit 65d lädt und ab Adresse 16640 die Bitmuster dieses Zeichensatzes einschreibt. Leider funktioniert das aber nicht. Den Grund erkennt man aus Abb.1.9: Der Zeichengenerator wird über die Leitungen A9 ... A12 von der CPU her adres-

Abb. 1.9 Schaltungsdetail zum Zeichengenerator

## 1 Wie funktioniert ein Computer?

siert. Das betreffende Zeichen wird ausgewählt, indem der Sinclair-Logic-Chip den Code-Wert des Zeichens auf A0 ... A8 ausgibt. Damit dies ungestört von den gerade ablaufenden sonstigen Aktivitäten der CPU geschehen kann, sind diese Adreßleitungen über Widerstände vom CPU-Bus entkoppelt. Es wird hier also eine spezielle Art von DMA (direct memory access - direkter Speicherzugriff) realisiert. Das bedeutet andererseits aber, daß der Zeichen-generator vom ZX 81 nur gefunden wird, wenn er sich am Steckplatz des Original-ROMs befindet.

### 1.4.4 Maschinenprogramme

Die in diesem Buch beschriebenen Hardware-Erweiterungen sind alle von BASIC aus bedienbar. Trotzdem ist in einigen Fällen eine sinnvolle Ausnützung aller Möglichkeiten erst durch ein Maschinenprogramm möglich.

Maschinenprogramme können beim ZX 81 mit

**LET A = USR (NN)**

aufgerufen werden. Dabei bedeutet NN die Speicherstelle, in der der erste Befehl des Maschinenprogramms steht. Allerdings müssen einige Vorkehrungen getroffen werden, damit das Maschinenprogramm nicht zerstört werden kann, z. B. durch das Eintippen weiterer BASIC-Programmzeilen. Hierzu gibt es im wesentlichen zwei Methoden:

a) RAMTOP wird herabgesetzt. Dazu müssen in die Speicherstellen 16388 und 16389 die entsprechenden Werte gepoket werden. Anschließend wird NEW eingegeben. Der Speicherplatz ab RAMTOP bis zur tatsächlichen Speichergrenze steht für Maschinenprogramme zur Verfügung.

Nachteilig ist, daß diese Maschinenprogramme bei SAVE nicht mit abgespeichert werden, da der Computer wegen des herabgesetzten RAMTOP-Wertes ja nichts von diesem Speicherbereich „weiß“. Deshalb ist Methode b) empfehlenswerter.

b) An erster Stelle im BASIC-Programm wird eine REM-Zeile eingefügt, z. B.:

**100 REM ABCDEFGHIJKLMNOPQRSTUVWXYZ.**

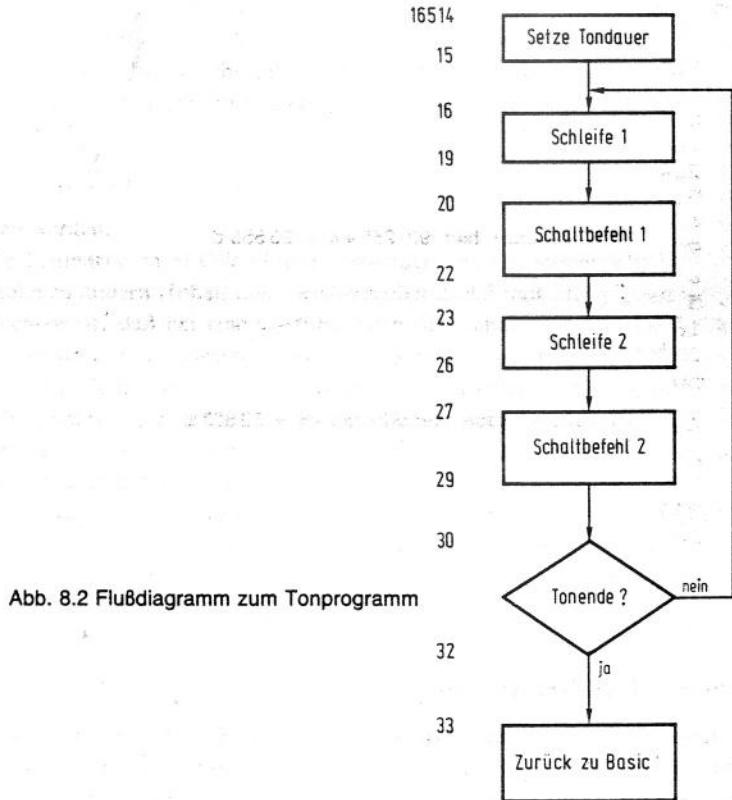

Das BASIC-Programm ignoriert diese Zeile. Da beim ZX 81 ein Programm stets ab derselben RAM-Adresse beginnt, nämlich 16509, läßt sich berechnen, in welcher Speicherstelle das erste Zeichen hinter dem REM-Statement steht (vergleiche Abb. I.10). Diese Adresse ist 16514. Nun kann man das Maschinenprogramm in die Speicherstellen ab 16514 poken. Das REM-Statement muß also zuvor mindestens soviele (beliebige) Zeichen enthalten, wie das Maschinenprogramm lang ist.

NN ist in diesem Fall also 16514. Mit SAVE wird das Programm zusammen mit dem BASIC-Programm aufgezeichnet.

Bei längeren Maschinenprogrammen ist das Eintippen der entsprechenden REM-Zeile recht ermüdend. Das folgende Programm schafft hier Abhilfe. Es besteht aus einem BASIC- und einem Maschinenprogrammteil.

Das Maschinenprogramm wird zunächst in einer (kurzen) REM-Zeile ab Adresse 16514 untergebracht. Während des Programmablaufs wird interaktiv die endgültige Startadresse für

Programmzeile :

1 REM ABCDE

Speicherung :

| 16509                        | 16510                                                 | 16511 | 16512 | 16513 | 16514 | 16515 | 16516 | 16517 | 16518   | 16519 |

|------------------------------|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|---------|-------|

| 0                            | 1                                                     | 7     | 0     | 234   | 38    | 39    | 40    | 41    | 42      | 118   |

| A1                           | A2                                                    | B1    | B2    |       |       |       |       |       |         |       |

| Zeilennummer<br>=256*A1 + A2 | Länge des<br>Textes einschl.<br>NEWLINE<br>=B1+256*B2 | REM   | A     | B     | C     | D     | E     |       | NEWLINE |       |

Abb. 1.10 Speicherung einer REM-Zeile

das Maschinenprogramm erfragt. Solange noch keine der später beschriebenen Speichererweiterungen vorhanden ist, empfieilt es sich, dieses Programm, wie vorhin erläutert, in einen Bereich oberhalb RAMTOP zu kopieren.

Des weiteren kann die Anzahl der Zeichen im REM-Statement eingegeben werden. Diese Werte fügt das BASIC-Programm in das Maschinenprogramm ein, kopiert anschließend das Maschinenprogramm in den gewünschten Speicherbereich, ergänzt die gewünschte Anzahl von „Dummy-Zeichen“ (Zeichen mit Code 8) und fügt als Zeilenende „118“ (NEWLINE) an. Dann löscht es sich selbst. Nun kann mit

LET A = USR (NN)

die REM-Zeile erstellt werden. Hierbei wird die vom BASIC-Programm vorher oberhalb RAMTOP erstellte REM-Zeile als erste Programmzeile ab Adresse 16509 gespeichert. NN ist dabei die eingegebene Startadresse.

Das Maschinenprogramm benützt den Blocktransferbefehl LDIR. Hierzu müssen vorher die Register HL (Startadresse der umzukopierenden REM-Zeile), DE (Zieladresse) und BC (Anzahl der umzukopierenden Zeichen) geladen werden. Anschließend erfolgt ein Sprung nach 1027d (0403h) in die Initialisierungsroutine des ROMs.

Zu beachten ist, daß das Maschinenprogramm oberhalb RAMTOP um die Anzahl der „Dummyzeichen“ (sowie eine Byte für Zeilenende) länger ist als das Programm in der ursprünglichen REM-Zeile (genügend Speicherplatz reservieren).

|       |      |     |

|-------|------|-----|

| 16514 | ---> | 33  |

| 16515 | ---> | 0   |

| 16516 | ---> | 0   |

| 16517 | ---> | 17  |

| 16518 | ---> | 125 |

| 16519 | ---> | 64  |

| 16520 | ---> | 1   |

| 16521 | ---> | 0   |

| 16522 | ---> | 0   |

| 16523 | ---> | 237 |

|               |      |         |

|---------------|------|---------|

| 4082:21 00 00 | LD   | HL,0000 |

| 4085:11 7D 40 | LD   | DE,407D |

| 4088:01 00 00 | LD   | BC,0000 |

| 408B:ED B0    | LDIR |         |

| 408D:EB       | EX   | DE,HL   |

| 408E:C3 03 04 | JP   | 0403    |

## 1 Wie funktioniert ein Computer?

|       |      |     |  |       |      |     |

|-------|------|-----|--|-------|------|-----|

| 16524 | ---> | 176 |  | 16529 | ---> | 0   |

| 16525 | ---> | 235 |  | 16530 | ---> | 1   |

| 16526 | ---> | 195 |  | 16531 | ---> | 0   |

| 16527 | ---> | 3   |  | 16532 | ---> | 0   |

| 16528 | ---> | 4   |  | 16533 | ---> | 234 |

```

100 REM 5 )?RND# GOSUB k FOR    900 POKE 16521,A+6-256*INT ((A-

?■ ■ REM                               6)/256)

150 SLOW                                1000 POKE 16522,INT ((A+6)/256)

200 PRINT "STARTADRESSE FUER"          1100 POKE 16531,A+2-256*INT ((A-

300 PRINT "MASCHINENPROGRAMM --      2)/256)

-> ";                                1200 POKE 16532,INT ((A+2)/256)

400 INPUT S                               1300 LET X=16514-S

450 PRINT S                               1400 FOR N=16514 TO 16533

500 PRINT "ANZAHL LEERZEICHEN -      1500 POKE (N-X),PEEK N

-> ";                                1600 NEXT N

600 INPUT A                               1700 FOR..N=1 TO A

650 PRINT A                               1800 POKE (S+19+N),8

660 FAST                                 1900 NEXT N

700 POKE 16515,S+15-256*INT ((S     2000 POKE (N+S+19),118

+15)/256)                               2100 NEW

800 POKE 16516,INT ((S+15)/256)

```

## PROG 2

Um Maschinenprogramme bequem eingeben zu können, empfiehlt sich ein Hilfsprogramm. Das nachfolgend aufgelistete Programm erfüllt drei Funktionen:

- a) RUN 1900: zeigt Speicherinhalt zwischen S und E

- b) RUN 2900: schreibt ein Maschinenprogramm in den Speicher zwischen S und E

- c) RUN 4000: füllt den Speicher zwischen S und E mit dem Code des gewünschten Symbols SY.

```

2000 FOR N=S TO E

2200 PRINT N; " - "; PEEK N

2300 NEXT N

2400 STOP

2450 REM ****

2460 REM ■ S-E: PROGRAMM POKE ■

2470 REM ****

2900 PRINT "START: ";

2910 INPUT S

2920 PRINT S; " ENDE: ";

2930 INPUT E

2940 PRINT E

2950 PRINT "

3000 FOR N=S TO E

3100 PRINT N;

3200 INPUT K

3300 POKE N,K

3400 PRINT " - "; PEEK N

3410 IF PEEK 16442<=3 THEN GOSUB

3620

3500 NEXT N

3600 STOP

3620 PRINT " V O R S I C H T "

```

3630 PAUSE 500

3650 CLS

3660 POKE 16442,24

3670 RETURN

3980 STOP

3990 REM \*\*\*\*

3991 REM ■ S-E: RAM MIT SY FUELLEN

3992 REM \*\*\*\*

4000 PRINT "START = "

4100 INPUT S

4200 PRINT S

4300 PRINT "ENDE = "

4400 INPUT E

4500 PRINT E

4600 PRINT "CODE DES SYMBOLS = "

;

4700 INPUT SY

4800 PRINT SY; " --- "; CHR\$ SY

4900 PAUSE 200

5000 FOR N=S TO E

5100 POKE N,SY

5200 NEXT N

5300 STOP

PROG 3

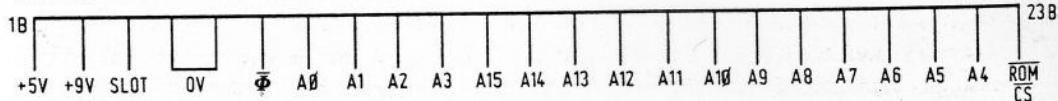

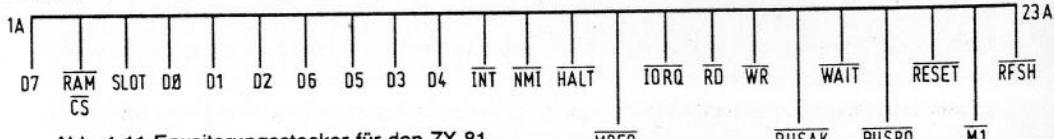

#### 1.4.5 Steckleiste für Erweiterungsschaltungen

Der ZX 81 besitzt an seiner Rückseite eine Kontakteiste, die normalerweise für die käuflichen Speichererweiterungen und den Druckeranschluß vorgesehen ist. Wie ein Blick auf die Anschlußbelegung der Kontakteiste zeigt (Abb. 1.11), sind tatsächlich alle für Hardware-Erweiterungen wichtigen Signale herausgeführt. Neben den schon in Kap. 1.3 besprochenen BUS-Signalen sind dies die Betriebsspannungen +9 V und +5 V sowie die Leitungen ROM CS/ RAM CS.

Während eines CPU-Zugriffs auf die internen Speicher gehen diese CS-Signale (chip select — Bausteinwahl) auf logisch 0. Da die beiden Leitungen durch Widerstände von den Ausgängen des Sinclair-Logic-Chips entkoppelt sind, kann durch ein von außen zugeführtes H-Signal der jeweilige Speicherbereich abgeschaltet werden, ohne daß dieses IC Schaden nimmt.

#### Unterseite

#### Oberseite

Abb. 1.11 Erweiterungsstecker für den ZX 81

## 1 Wie funktioniert ein Computer?

Die 9-V-Leitung liefert als Ausgang die Gleichspannung des Rechnernetzteils. Falls die Belastung nicht zu groß wird, läßt sich diese Spannung auch extern verwenden. Bei umfangreicheren Erweiterungen allerdings sollte ein leistungsfähigeres Netzteil verwendet werden. Dabei kann über diese Leitung die Stromversorgung des Rechners erfolgen. Dabei wird der im Rechner eingegebauter Spannungsregler mitverwendet. Der stabilisierte 5-V-Ausgang ist für externe Schaltungen nur bedingt geeignet, da bei zu hoher Belastung der Spannungsregler im Rechner zu heiß wird. Bei Verwendung der BUS-Signale ist zu beachten, daß einige Leitungen vom Betriebssystem des Rechners in einer Weise benutzt werden, die ihre externe Verwendung problematisch, wenn nicht gar unmöglich werden läßt. Dies gilt für die Signale INT, NMI, HALT, BUSRQ und BUSAK.

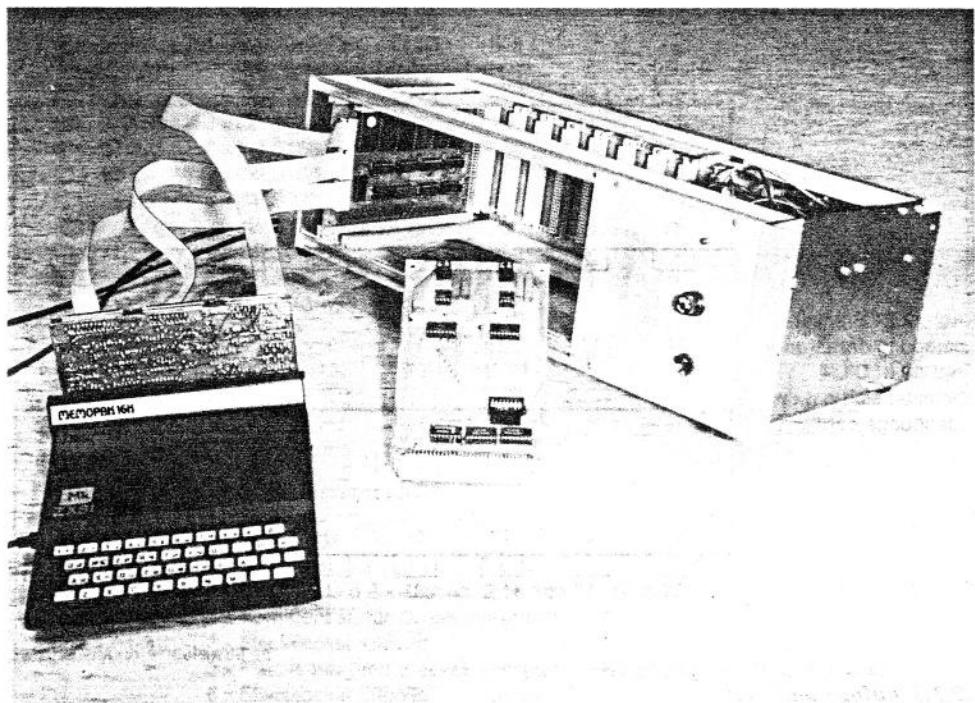

## 2 Grundplatinen

### 2.1 Systemüberlegungen und Platinenherstellung

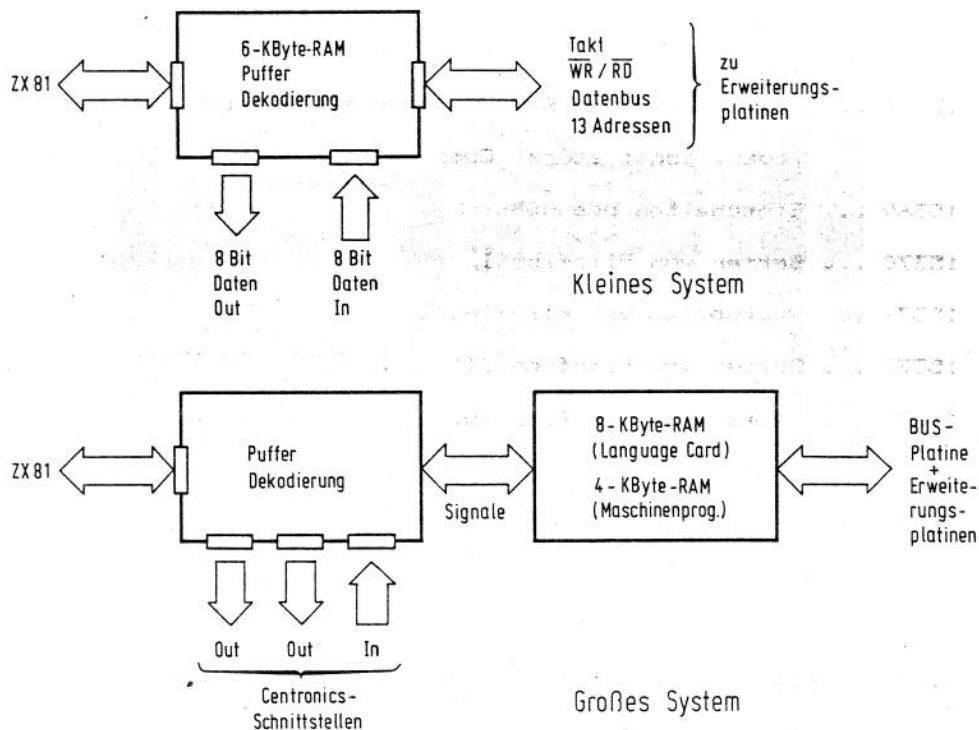

Damit Hardware-Erweiterungen an die jeweiligen Wünsche und Notwendigkeiten angepaßt werden können, werden zwei verschiedene Systeme vorgestellt. Beide besitzen eine Grundplatine, die für eine Bus-Entkopplung zwischen Rechner und Peripherie sorgt und einige Grundfunktionen, wie beispielsweise Adressendekodierung, bereitstellt. An diese Grundplatine können die gewünschten Funktionsplatinen, wie z. B. OUT-Ports, AD-Wandler und ähnliches angeschlossen werden.

Das „kleine“ System enthält auf der Grundplatine neben den Bustreibern 6-KByte-RAM (CMOS), einen IN/OUT-Port, einen Software-Schalter sowie die Dekodierung für 13 weitere Adressen.

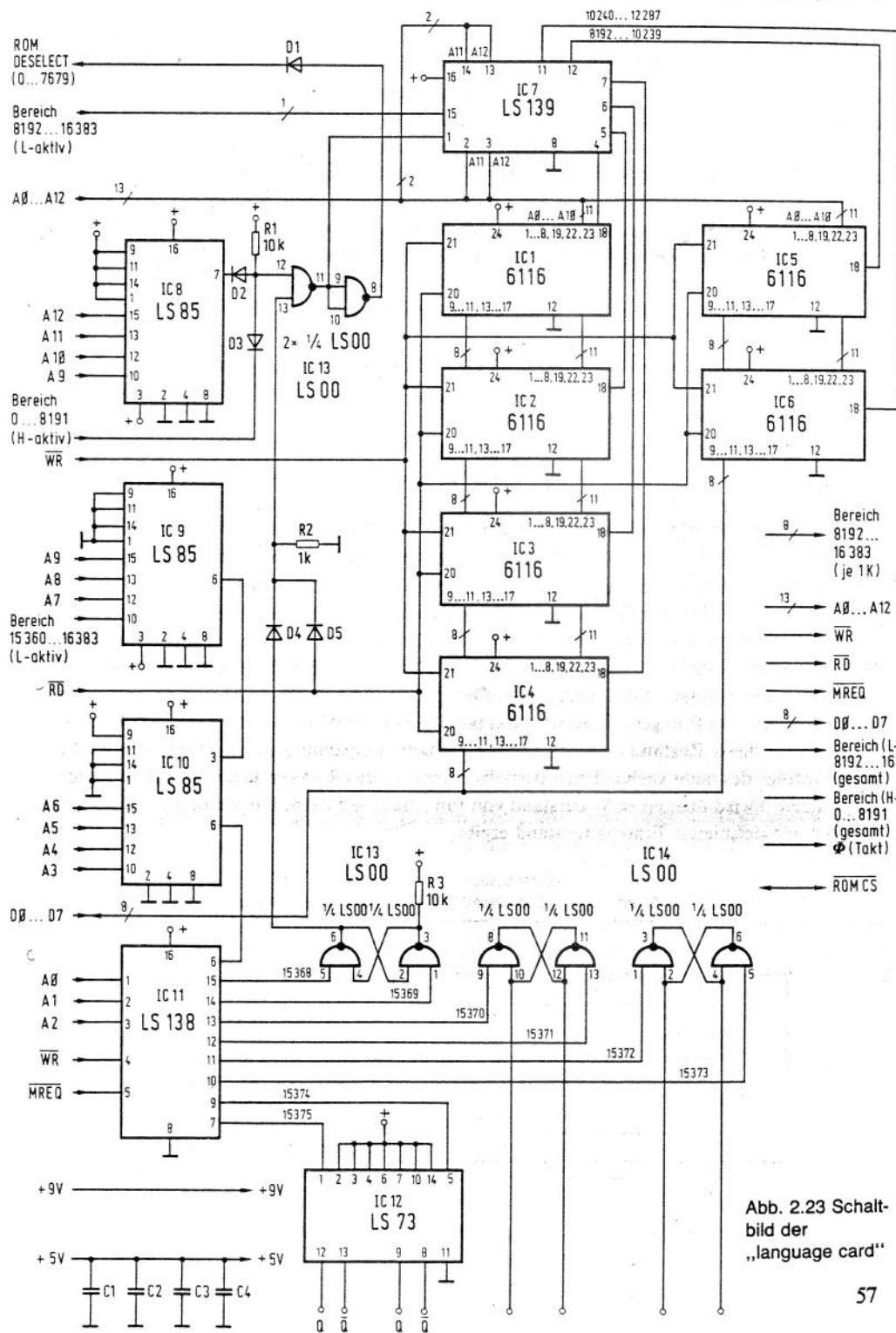

Beim „großen“ System sind statt dessen zwei Centronics-Ausgänge und ein Centronics-Eingang vorhanden. Über eine Interface-Platine, die insgesamt 12-KByte-RAM enthält, geht es auf eine Bus-Platine, an der die gewünschten Zusatzkarten angeschlossen werden (19-Zoll-Einschubtechnik). Der RAM-Speicher auf der Interface-Karte ist allerdings nicht für BASIC-Programme gedacht, sondern dient besonderen Anwendungszwecken. 8-KByte dieses Speichers liegen als eine Art „language card“ („Sprachenkarte“) parallel zum ZX-81-ROM. Der Name „language card“ röhrt daher, daß eine Sprache (z. B. BASIC) ins RAM geladen werden kann. Da diese Programmiersprache nicht mehr unveränderlich im ROM vorliegt, kann sie nach Bedarf geändert, ergänzt oder durch eine andere (z. B. FORTH, PASCAL o. ä.) ersetzt werden. Für den ZX 81 wäre mit dem Ersatz durch eine andere Sprache allerdings ein unverhältnismäßig großer Aufwand verbunden, da Teile des Betriebssystems (Tastaturbedienung, Bildschirmerstellung usw.) ebenfalls im ROM untergebracht sind. Damit bleibt die Möglichkeit zur Veränderung des Interpreters sowie des Betriebssystems, was immer noch hochinteressant ist.

Auf diese Weise ergibt sich eine ungeahnte Zahl von Möglichkeiten. So kann der ZX 81 beispielsweise einen normalen Centronics-Drucker bedienen, es lassen sich die Keyboard-Tasten umbelegen, eigene Funktionen können definiert werden usw. Der Centronics-Eingang kann benutzt werden, um Druckerdaten eines anderen Computers einzulesen. Durch entsprechende Programmierung läßt sich der ZX 81 für diesen Computer als Druckerpuffer verwenden. Als zusätzlicher BASIC-Speicher kann das 6-KByte-RAM der Grundplatine aus dem kleinen System verwendet werden.

Für I/O-Zwecke besitzt die Z-80-CPU spezielle Befehle. Dabei wird hardwaremäßig die IORQ-Leitung der CPU verwendet (vergl. Kap. 1.3.1). Allerdings stehen diese Befehle nicht in BASIC zur Verfügung. Bei Anwendung dieser I/O-Technik können die jeweiligen Peripherieschaltungen also nur durch Maschinenprogramme angesprochen werden. Darüber hinaus verwendet der ZX 81 diese IN/OUT-Befehle für die Bedienung von Bildschirm, Tastatur,

## 2 Grundplatinen

Kassettenrecorder usw. Dadurch ergeben sich bei Verwendung der IORQ-Leitung unter Umständen größere Probleme.

Diese Gründe waren maßgeblich dafür, daß hier zum Ansprechen der Peripherie-Schaltungen auf die speziellen I/O-Möglichkeiten der Z-80-CPU verzichtet wurde und statt dessen die I/O-Leitungen „memory mapped“ betrieben werden. Das bedeutet, daß sie wie Speicherstellen angesprochen werden. Die Datenausgabe erfolgt also mit

POKE Adresse, Zahl

während eine Dateneingabe z. B. mit

A = PEEK Adresse

durchgeführt wird. Selbstverständlich können auch Maschinenprogramme unter Verwendung der entsprechenden Ladebefehle eingesetzt werden.

Einiger Nachteil dieser Methode ist die Tatsache, daß die von den I/O-Bausteinen belegten Adressen für Speicherzwecke nicht zur Verfügung stehen. Es muß also ein geeigneter Adreßbereich für die Bausteine reserviert werden.

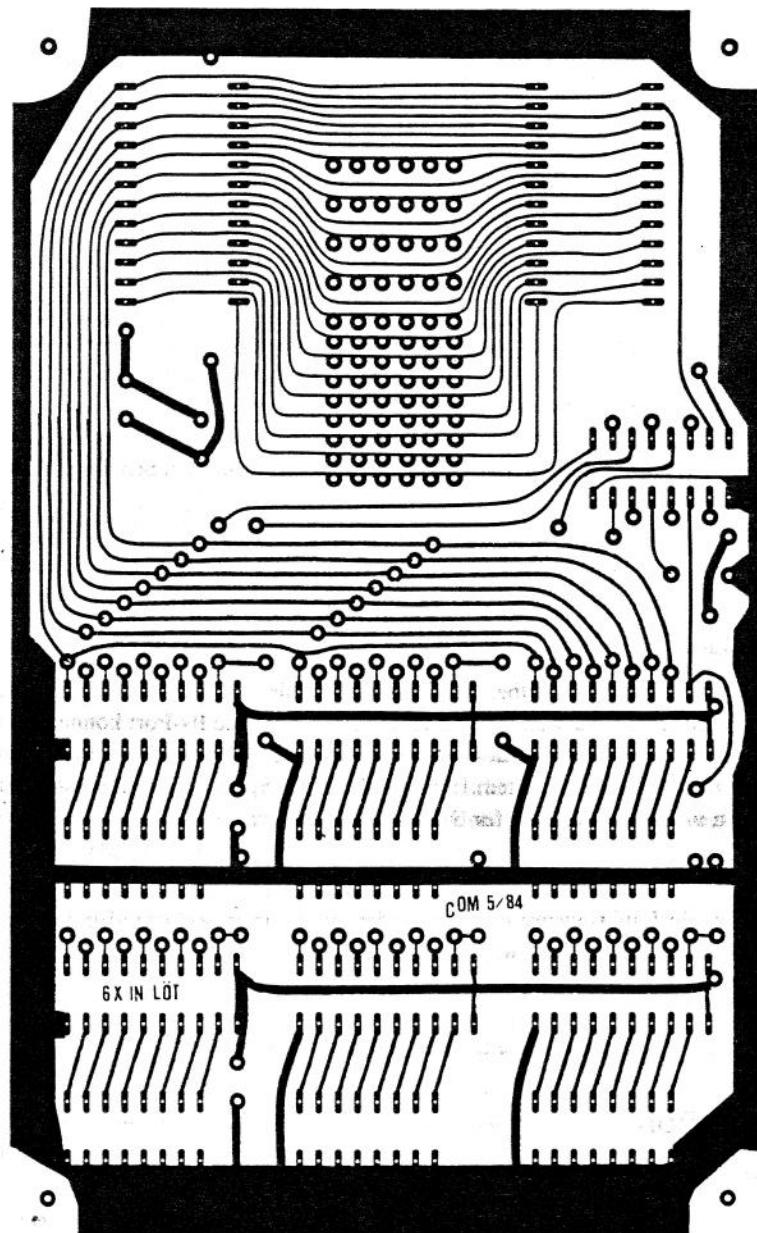

Aufgebaut werden die Schaltungen auf Platinen im Europaformat. Bei der Vielzahl an Leitungen, die bei Computerschaltungen nötig sind, ist eine zweiseitig kupferkaschierte Platine im Regelfall nicht zu umgehen. Dabei ist vor allen Dingen auf eine exakte Passung zwischen Vorder- und Rückseite der Platine zu achten, da sonst Kurzschlüsse entstehen können. Um diese Passung zu gewährleisten, besitzen die Platinenvorlagen stets an den vier Ecken Lötaugen als Markierungen, die jeweils 5 mm vom Rand entfernt sind. Diese Markierungen werden durchgestochen. Die Europakarte erhält vor der Belichtung ebenfalls vier Bohrungen (1mm Durchmesser), jeweils 5 mm von den Kanten entfernt. Auf einem Holzbrett werden vier Stifte in einem Rechteck (9 cm × 15 cm) angeordnet. Auf das Holzbrett steckt man nun die Platine und die Vorlage. Nach dem Belichten der Vorderseite wird die Rückseite in derselben Weise hergestellt. Dabei ist nur darauf zu achten, daß die Vorlage richtig herum aufgelegt wird. Bei einigermaßen sorgfältigem Vorgehen können auch mit Amateurmitteln sehr brauchbare Resultate erzielt werden.

Nach dem Ätzen ist die fertige Platine sehr sorgfältig auf eventuelle Leiterbahnunterbrechungen und Kurzschlüsse zu untersuchen. Bohrungen werden im Regelfall mit 0,8 mm Durchmesser ausgeführt. Lediglich bei Bauteilen mit dickeren Anschlußdrähten wie Steckerleisten, Siebkonsensatoren u. ä. müssen 1,0 oder 1,2 mm verwendet werden.

Für das Durchkontaktieren sind die Platinen so ausgelegt, daß im Regelfall alle von der Be stückungsseite aus sichtbaren Bohrungen durchkontakteert werden. Hierzu wird ein dünner Draht (z. B. abgeschnittener Anschlußdraht der einzulötenden Bauelemente) durch das Loch hindurchgesteckt und auf beiden Seiten verlötet. Es wird also nicht, wie bei kommerziellen Platinen üblich, eine Durchkontaktierstelle auch zum Verlöten von Bauelementen benutzt. Auf diese Weise läßt sich zwar keine ganz so große Packungsdichte erreichen, dafür ist aber das Verlöten wesentlich erleichtert.

Ein direktes Einlöten der ICs ist auf gar keinen Fall zu empfehlen, da sich eine eventuelle Fehlersuche und Beseitigung sonst äußerst schwierig gestaltet. Statt dessen sollten (gute) Stecksockel verwendet werden, die ein dichtes Anreihen der ICs gestatten.

## 2.2 Grundplatine I (kleines System)

### 2.2.1 Speichererweiterung

In der Grundversion besitzt der ZX 81 nur eine geringe Speicherkapazität von 1-KByte-RAM. Dies ist eigentlich von vornherein viel zu wenig, da bereits ein vollständig aufgebauter Bildschirm diesen Speicher schon nahezu belegt. Mit zusätzlichen 6-KByte-RAM ist man für viele Anwendungsfälle gerüstet, soweit nicht größere Programme eingetippt werden sollen (wozu die Tastatur des ZX 81 auch nicht unbedingt animiert) oder umfangreiche Datenmengen bearbeitet werden müssen. Durch Verwendung von Speicher-ICs des Typs HM 6116 ( $2K \times 8$ ) kann dieser Speicher auch in Einzelschritten von jeweils 2 KByte ausgebaut werden. Außerdem besteht die Möglichkeit, pinkompatible Eproms (2516 bzw. 2716, je nach Hersteller) zu verwenden, und dadurch häufig benötigte Maschinenprogramme permanent im Speicher zu haben.

Damit der Computer die Speichererweiterung für BASIC-Programme auch nützen kann, muß sich der externe RAM-Bereich nahtlos an den internen Bereich anschließen. Dazu ist es nötig, sich die Speicherorganisation des ZX 81 klarzumachen (Abb. 2.1). Eine Eigentümlichkeit dieses Computers ist die dezimale Angabe von Adressen und Speicherinhalt. Daher sind in der Abbildung die Adressen sowohl decimal als auch hexadezimal aufgeführt. Die vierte Spalte zeigt die dazugehörigen logischen Pegel auf den Adreßleitungen.

| HEX  | DEZ   | Y  | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Adreßbereich für I/O |

|------|-------|----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----------------------|

| 5FFF | 24575 | Y7 | 0   | 1   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 6116 III             |

| 5C00 | 23552 |    | 0   | 1   | 0   | 1   | 1   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 5BFF | 23551 | Y6 | 0   | 1   | 0   | 1   | 1   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 6116 II              |

| 5800 | 22528 |    | 0   | 1   | 0   | 1   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 57FF | 22527 | Y5 | 0   | 1   | 0   | 1   | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 6116 II              |

| 5400 | 21504 |    | 0   | 1   | 0   | 1   | 0   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 53FF | 21503 | Y4 | 0   | 1   | 0   | 1   | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 6116 II              |

| 5000 | 20480 |    | 0   | 1   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 4FFF | 20479 | Y3 | 0   | 1   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 6116                 |

| 4C00 | 19456 |    | 0   | 1   | 0   | 0   | 1   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 4BFF | 19455 | Y2 | 0   | 1   | 0   | 0   | 1   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1K internes RAM      |

| 4800 | 18432 |    | 0   | 1   | 0   | 0   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 47FF | 18431 | Y1 | 0   | 1   | 0   | 0   | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | ROM Doppel           |

| 4400 | 17408 |    | 0   | 1   | 0   | 0   | 0   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 43FF | 17407 | Y0 | 0   | 1   | 0   | 0   | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | ROM                  |

| 4000 | 16384 |    | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 3FFF | 16383 |    | 0   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |                      |

| 2000 | 8192  |    | 0   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

| 1FFF | 8191  |    | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |                      |

| 0000 | 0     |    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                      |

Abb. 2.1 Speicherorganisation des ZX 81

## 2 Grundplatinen

Da die Z-80-CPU bei Reset den ersten (Maschinen-)Programmbefehl auf Adresse 0 erwartet, liegt das ROM für Betriebssystem und BASIC-Interpreter (8 KByte) zwischen 0 und 8191. Überraschenderweise erscheint es nochmals zwischen 8192 und 16383. Der Grund dafür ist in einer unvollständigen Adreßdekodierung zu suchen, d. h. für die Zuordnung der Speicheradressen im ROM zu den von der CPU ausgegebenen Adreßsignalen werden nur die Leitungen A0 ... A12 verwendet. Dadurch „sieht“ die CPU 0 und 8192 als dieselbe Adresse.

Man kann sich diesen Effekt an den dezimalen Zahlen 1293 und 7293 klarmachen. Betrachtet man nur die letzten drei Ziffern, so erhält man beide Male dieselbe Zahl.

Von 16384 bis 17407 schließt sich das interne RAM an. Die RAM-Obergrenze wird beim Einschalten vom Computer mit einem Testprogramm ermittelt und als Systemvariable RAM-TOP gespeichert. Dabei enthält die Speicherstelle 16388 die unteren 8 Bit, die Speicherstelle 16389 die oberen 8 Bit der entsprechenden 16-Bit-Zahl. Durch die Befehlseingabe

PRINT PEEK 16388 + 256 × PEEK 16389

erhält man diesen Zahlenwert in dezimaler Schreibweise. Er stellt die Adresse des ersten nicht existierenden Bytes dar, ohne Speichererweiterung ergibt sich also die Zahl 17408.

Käufliche Speichererweiterungen benützen in der Regel das interne RAM nicht und schalten es über die Leitung RAM-CS (H-Pegel) ab. Dadurch erhält man eine bequemere Organisation des Zusatzspeichers (z. B.  $8 \times 2$  KByte Speicher-ICs ergeben 16 KByte) und kann die Adreßdekodierung einfacher vornehmen. Für den Selbstbau besitzt diese Methode aber ein ernstzunehmendes Problem: funktioniert die Speichererweiterung nach dem Zusammenbau aus irgendeinem Grund nicht (und nach dem Gesetz von Murphy ist sogar sicher damit zu rechnen), stürzt der Computer unweigerlich ab, da er zu seinem Betrieb auf jeden Fall RAM-Bereich benötigt. Dann aber ist eine Fehlersuche praktisch unmöglich, da ja keinerlei Testprogramme zum Einkreisen der Fehlerstelle eingegeben werden können. Das heißt, entweder findet man den Fehler durch Zufall, oder eben nie.

In Abb. 2.2 ist das Anschlußschema und die Funktionstabelle des Speicherbausteins HM 6116 gezeigt. Wie man erkennt, besitzt dieser Speicher 11 Adreßleitungen (A0 ... A10).

|      |    |    |      |    |    |    |                    |

|------|----|----|------|----|----|----|--------------------|

| A7   | 1  | 24 | +UB  | CS | OE | WE | Betriebsart        |

| A6   | 2  | 23 | A8   | 1  | X  | X  | nicht angesprochen |

| A5   | 3  | 22 | A9   | 0  | 0  | 1  | Lesen              |

| A4   | 4  | 21 | WE   | 0  | 1  | 0  | Schreiben          |

| A3   | 5  | 20 | OE   | 0  | 0  | 0  | Schreiben          |

| A2   | 6  | 19 | A10  |    |    |    |                    |

| A1   | 7  | 18 | CS   |    |    |    |                    |

| A0   | 8  | 17 | I/O8 |    |    |    |                    |

| I/O1 | 9  | 16 | I/O7 |    |    |    |                    |

| I/O2 | 10 | 15 | I/O6 |    |    |    |                    |

| I/O3 | 11 | 14 | I/O5 |    |    |    |                    |

| GND  | 12 | 13 | I/O4 |    |    |    |                    |

Abb. 2.2 Anschlußbelegung

und Funktionstabelle des HM 6116

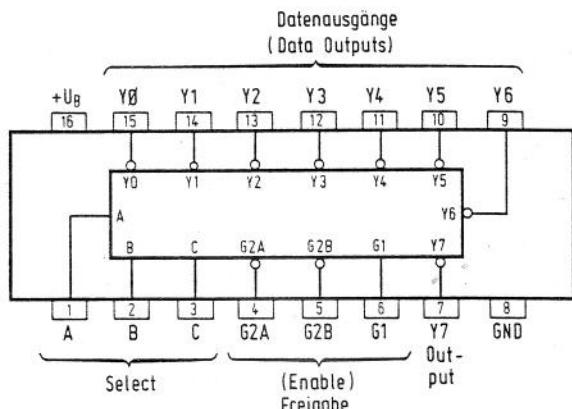

Abb. 2.3 Anschlußbelegung und Funktionstabelle des 74LS138

| Eingänge/Inputs |    |        | Ausgänge |   |    |    |    |    |    |    |    |    |

|-----------------|----|--------|----------|---|----|----|----|----|----|----|----|----|

| Freigabe        |    | Select |          |   | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| G1              | G2 | C      | B        | A |    |    |    |    |    |    |    |    |

| X               | 1  | X      | X        | X | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 0               | X  | X      | X        | X | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1               | 0  | 0      | 0        | 0 | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1               | 0  | 0      | 0        | 1 | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1               | 0  | 0      | 1        | 0 | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  |

| 1               | 0  | 0      | 1        | 1 | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  |

| 1               | 0  | 1      | 0        | 0 | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  |

| 1               | 0  | 1      | 0        | 1 | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  |

| 1               | 0  | 1      | 1        | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| 1               | 0  | 1      | 1        | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

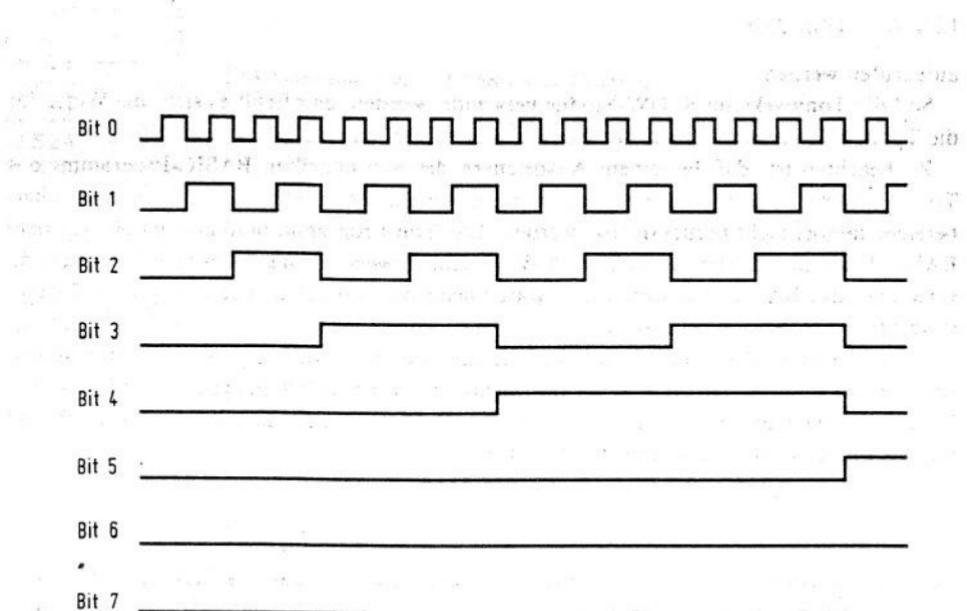

Würde man ihn direkt mit den entsprechenden Leistungen des Adressbusses verbinden, so würde er gemeinsam mit dem internen ROM zwischen Adresse 0 und 2047 angesprochen. Erwünscht ist er allerdings zwischen 17408 und 19455. Erreichen läßt sich das, indem man die Adreßleitungen A11 ... A14 zur Unterscheidung heranzieht. Im Bereich von 16384 bis 24575 ist stets A14 = 1 und A13 = 0. Betrachtet man A12, A11 und A10 als dreistellige Binärzahl, so entspricht jeder solchen Zahl ein 1 KByte großer RAM-Bereich.

Ein 3-zu-8-Dekoder 74LS138 kann in Abhängigkeit von dieser Zahl (CBA in Abb.2.3) jeweils einen der Ausgänge Y0 ... Y7 auf logisch 0 schalten (Spalte 3 in Abb.2.3). Führt man seinem Enable-Eingang G1 (H-aktiv) das Signal A14, den Eingängen G2A und G2B (L-aktiv) die Signale MREQ und A13 zu, so ist gewährleistet, daß der Dekoder nur während eines Speicherzugriffs auf die Adressen 16384 bis 24575 angesprochen wird.

A15 wird nicht benutzt. Das hat zur Folge, daß sich die gesamte Specheraufteilung zwischen 32768 und 65535 wiederholt (unvollständige Adressendekodierung).

Da der 3-zu-8-Dekoder jeweils 1-KByte-Blöcke auswählt, die Speicher-ICs aber 2 KByte umfassen, müssen jeweils zwei Ausgangsleitungen über eine ODER-Verknüpfung zusammengefaßt werden, um den betreffenden Speicher anzusprechen. Das bedeutet, Y1 oder Y2 aktiviert den CS-Eingang (vergl. Abb. 2.3) des ersten Speicher-ICs. Y3 oder Y4 bzw. Y5 oder Y6 bewirken dasselbe für die anderen Speicher.

Wenn  $Y_0 = 0$  ist, ist das interne RAM an der Reihe. Das bedeutet umgekehrt, daß während  $Y_0 = 1$  externe Bausteine angesprochen werden. Daher ist dieses Signal zur Abschaltung des internen RAMs geeignet. Diese Abschaltung ist nötig, da infolge unvollständiger Adreßdekodierung dieses RAM mehrfach erscheint und dadurch mit externen Speichern kollidieren würde.

### 2.2.2 I/O-Ports

Mit  $Y_7 = 0$  wird der Bereich von 23552 bis 24575 erfaßt. Dieser Bereich wird nun nicht für einen weiteren 2-KByte-Speicher genutzt (obwohl das natürlich genauso möglich wäre), sondern für Ein-/Ausgabeleitungen (I/O). Streng genommen besitzt der ZX 81 bereits solche I/O-Ports: Die Tastatur zur Daten- und Befehlseingabe (I-Port) und den Bildschirm zur Informationsausgabe (O-Port). Darüber hinaus steht mit dem Kassettenrekorder-Anschluß ein bidirektonaler I/O-Port für das Laden und Speichern von Programmen zur Verfügung. Hierbei handelt es sich um einen seriellen Port mit einer Datenbreite von 1 Bit. Wer sich einen Drucker zulegt, besitzt eine weitere Ausgabemöglichkeit.

Nachteil all dieser Schnittstellen ist aber, daß kein direkter Kontakt zur Umwelt besteht, stets muß der Mensch als Vermittler zusätzlich in Aktion treten. Wünschenswert ist also eine direkte Verbindung, um etwa ein Gerät direkt durch den Computer ein- oder ausschalten zu können. Umgekehrt kann auf diesem Weg eine unmittelbare Datenerfassung, z. B. der Zimmertemperatur, Raumhelligkeit o. ä. erfolgen.

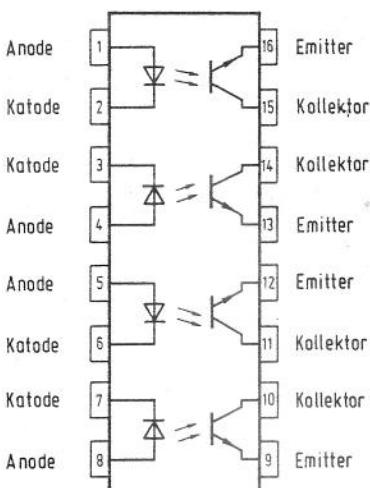

Für diesen Zweck stehen eine Reihe spezieller ICs zur Verfügung, z. B. die Z-80-PIO (*Parallel In/Out*). Vor allem für den Anfänger von Nachteil ist die Notwendigkeit einer Programmierung dieses Bausteins für seine verschiedenen Betriebsarten, was zu einer gewissen Unübersichtlichkeit führt. Zudem kann es durch falsche Programmierung u. U. zu Hardware-Schäden kommen. Dies geschieht beispielsweise dann, wenn eine fälschlicherweise als Ausgang programmierte Leitung gegen eine andere Ausgangsleitung treibt. Führt in einem solchen Fall der eine Ausgang H-Pegel, der andere L-Pegel, fließt ein hoher Strom, der zur Zerstörung der Ausgangstransistoren führen kann. Daneben liefern die Ausgänge der PIO relativ geringe Ströme, so daß z. B. Leuchtdioden zur Pegelanzeige nicht direkt angeschlossen werden können, sondern einen zusätzlichen Leistungstreiber benötigen. Daher wurde im folgenden ein anderes Konzept verwendet.

Speicherstellen können in BASIC mit dem Befehl

PRINT PEEK Adresse

gelesen werden, mit

POKE Adresse, Zahl

geladen werden. Ersetzt man das Speicher-IC durch ein geeignetes Port-IC, kann auf gleiche Weise eine Ein- oder Ausgabe realisiert werden. Daher schließt sich der I/O-Bereich an den Adressenbereich der Speichererweiterung an.

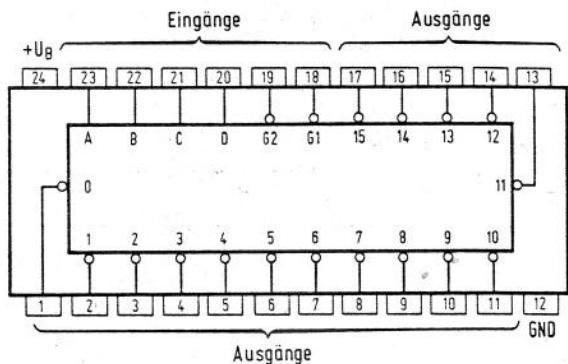

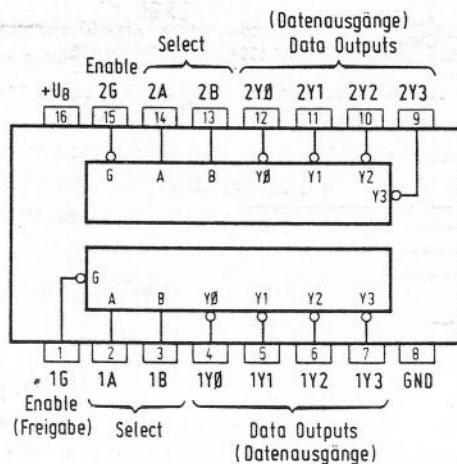

Zu diesem Zweck steht vom Adreßdekoder 74LS138 (IC4 der Speichererweiterung) das Signal  $Y_7$  zur Verfügung, das im Adreßbereich 23552 ... 24575 logisch 0 ist. Mit diesem Signal läßt sich ein 4-zu16-Dekoder 74LS154 über die Strobe-Eingänge G1/G2 aktivieren (Abb.2.4). Werden an seine Eingänge A, B, C und D die Adreßleitungen A0, A1, A2 und A3 angelegt, so

| Eingänge |    |   |   |   |   | Ausgänge |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|----------|----|---|---|---|---|----------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| G1       | G2 | D | C | B | A | 0        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 0        | 0  | 0 | 0 | 0 | 0 | 0        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 0 | 0 | 1 | 1        | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 0 | 1 | 0 | 1        | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 0 | 1 | 1 | 1        | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 1 | 0 | 0 | 1        | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 1 | 0 | 1 | 1        | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 1 | 1 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 0 | 1 | 1 | 1 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 1 | 0 | 0 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 1 | 0 | 0 | 1 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 1 | 0 | 1 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1  | 1  | 1  | 1  | 1  |

| 0        | 0  | 1 | 0 | 1 | 1 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 0  | 1  | 1  | 1  |

| 0        | 0  | 1 | 1 | 0 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 0  | 1  | 1  |

| 0        | 0  | 1 | 1 | 0 | 1 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 0  | 1  |

| 0        | 0  | 1 | 1 | 1 | 0 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 0  |

| 0        | 0  | 1 | 1 | 1 | 1 | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 0        | 1  | X | X | X | X | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 1        | 0  | X | X | X | X | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 1        | 1  | X | X | X | X | 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

Abb. 2.4 4-zu-16 Dekoder 74LS154: Anschlußbild und Funktionstabelle

wählt er in Abhängigkeit von der entsprechenden Adressenkombination eine der 16 Ausgangsleitungen an (L-aktiv). Auf diese Weise können die Adressen 23552 ... 23567 einzeln angesprochen werden. Wegen unvollständiger Adreßdekodierung wiederholen sich diese Adressen 64mal bis zu Adresse 24575, was aber nicht weiter stört.

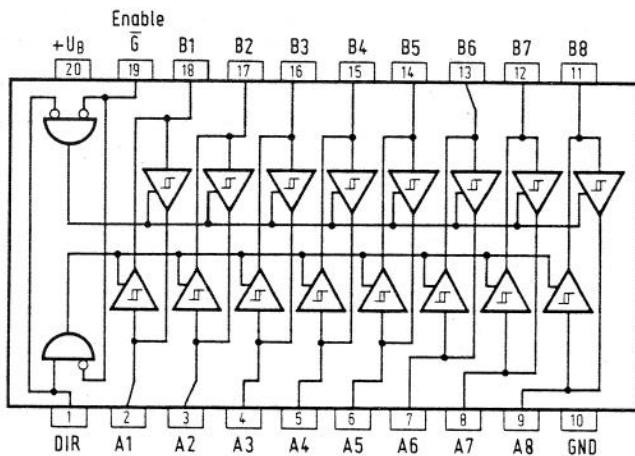

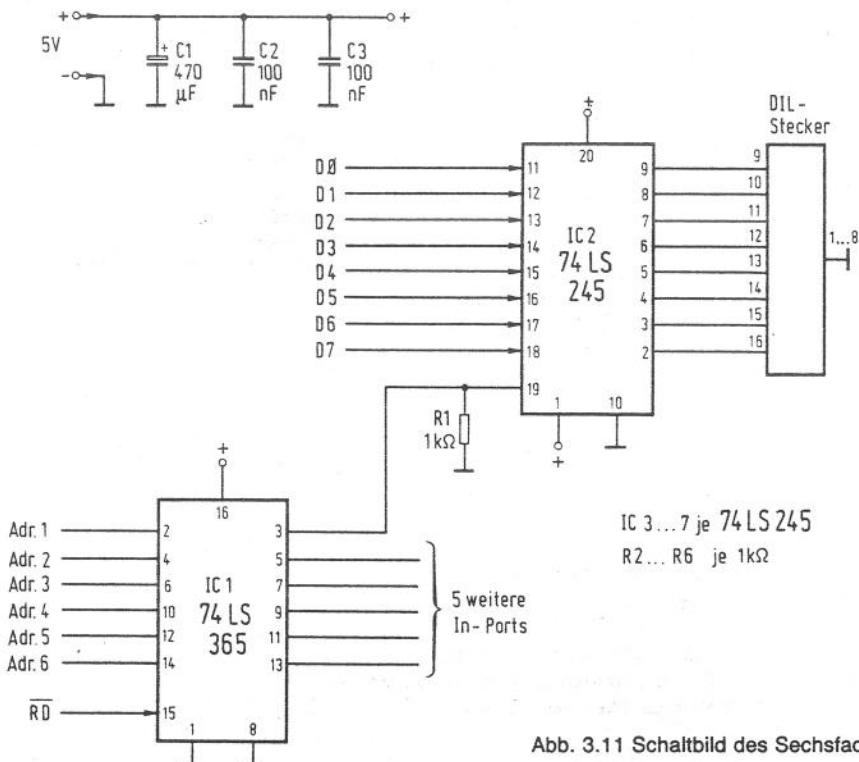

Im Falle eines Eingabe-Ports müssen beim Ansprechen der gewünschten Adresse die von außen kommenden Daten auf den Datenbus gelegt werden. Hierfür läßt sich sehr gut der Bustreiber 74LS245 „zweckentfremden“ (Abb. 2.5). Legt man seinen Anschluß 1 an Masse, so ist eine Datenübertragung von B (Außenwelt) nach A (Datenbus) möglich. Dies geschieht allerdings nur, wenn an Pin 19 (Enable) ein L-Signal anliegt. Ist das Signal an Pin 19 logisch 1, so sind die IC-Ausgänge im hochohmigen Zustand (Tristate) und belasten den Datenbus 1, so sind die IC-Ausgänge im hochohmigen Zustand (Tristate) und belasten den Datenbus

| Pin 19                  | Pin 1                          |              |

|-------------------------|--------------------------------|--------------|

| Freigabe<br>Enable<br>G | Richtungs-<br>steuerung<br>DIR | Datenfluß    |

| 0                       | 0                              | von B nach A |

| 0                       | 1                              | von A nach B |

| 1                       | X                              | hochohmig    |

Abb. 2.5 Bustreiber 74LS245:

Anschlußbild und Funktionstabelle

nicht. Die Eingabedaten müssen vorhanden sein, wenn die Port-Adresse angesprochen wird, eine Zwischenspeicherung erfolgt also nicht. Dies ist in den meisten Anwendungsfällen allerdings kein Nachteil.

Da die Ausgabedaten von der CPU nur sehr kurze Zeit auf den Datenbus gebracht werden (einige  $\mu$ s lang), ist für die Ausgabe-Ports eine Zwischenspeicherung erforderlich.

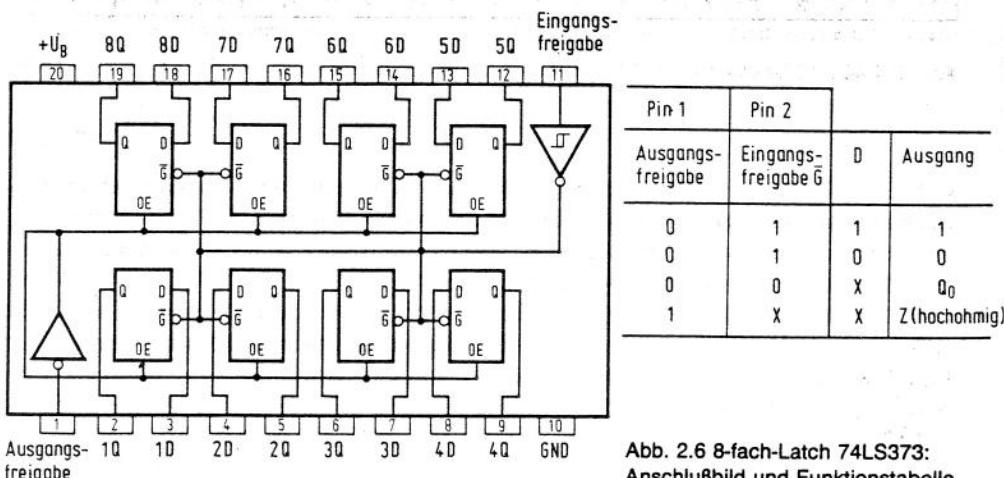

Abb. 2.6 8-fach-Latch 74LS373:

Anschlußbild und Funktionstabelle

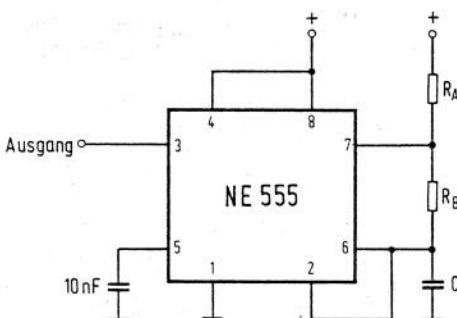

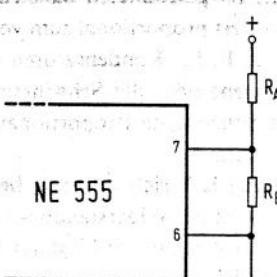

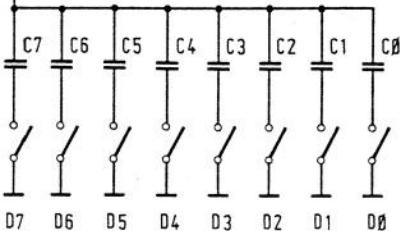

Diese Speicherung kann ein 8fach-Latch 74LS373 übernehmen (Abb. 2.6). Seine Ausgänge werden durch ein L-Signal an Pin 1 (output control) aktiviert, ein H-Signal schaltet die Ausgänge in den hochohmigen Zustand. Ein H-Signal an Pin 11 (enable) veranlaßt das IC, die an den Eingängen anliegenden Daten zu übernehmen und zu speichern. Dieses Signal muß also vom Computer geliefert werden, sobald die Ausgabe-Daten auf dem Datenbus vorhanden sind.

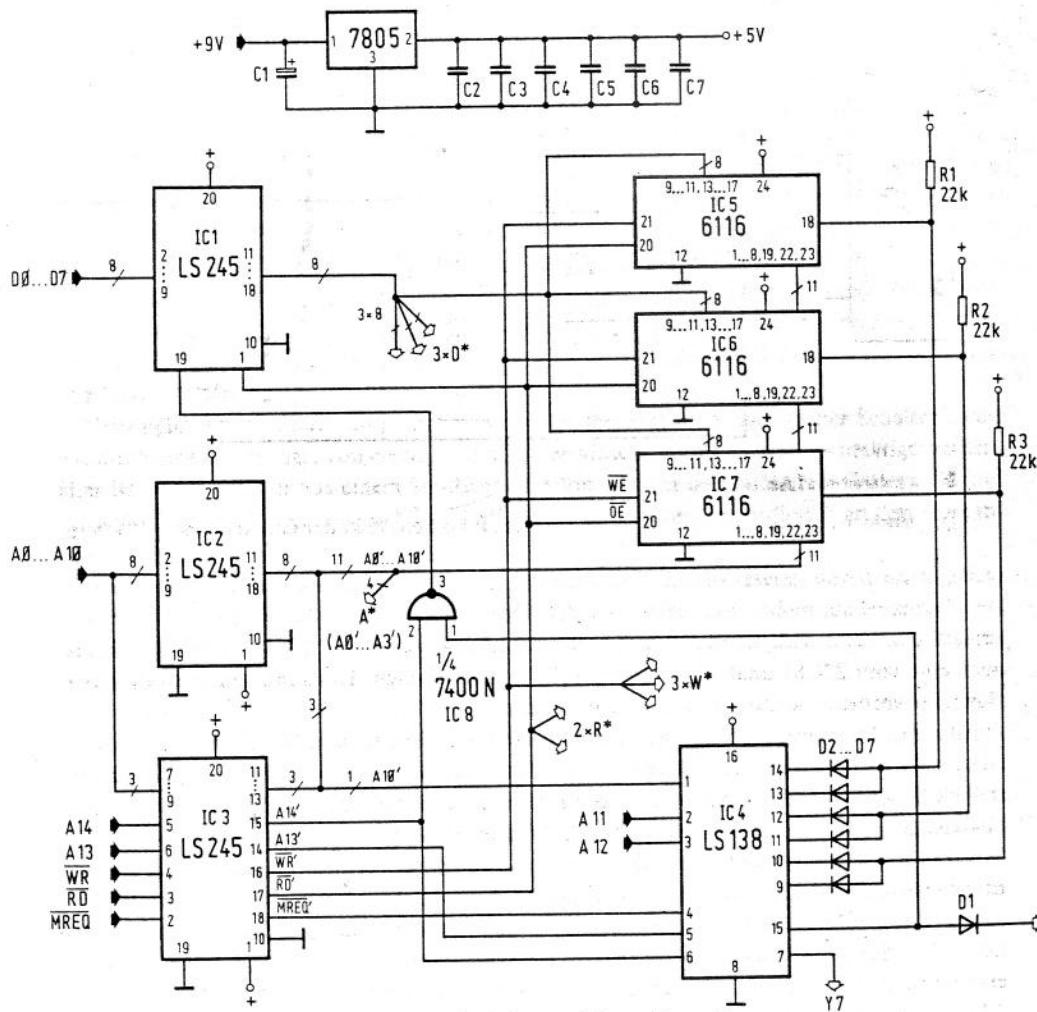

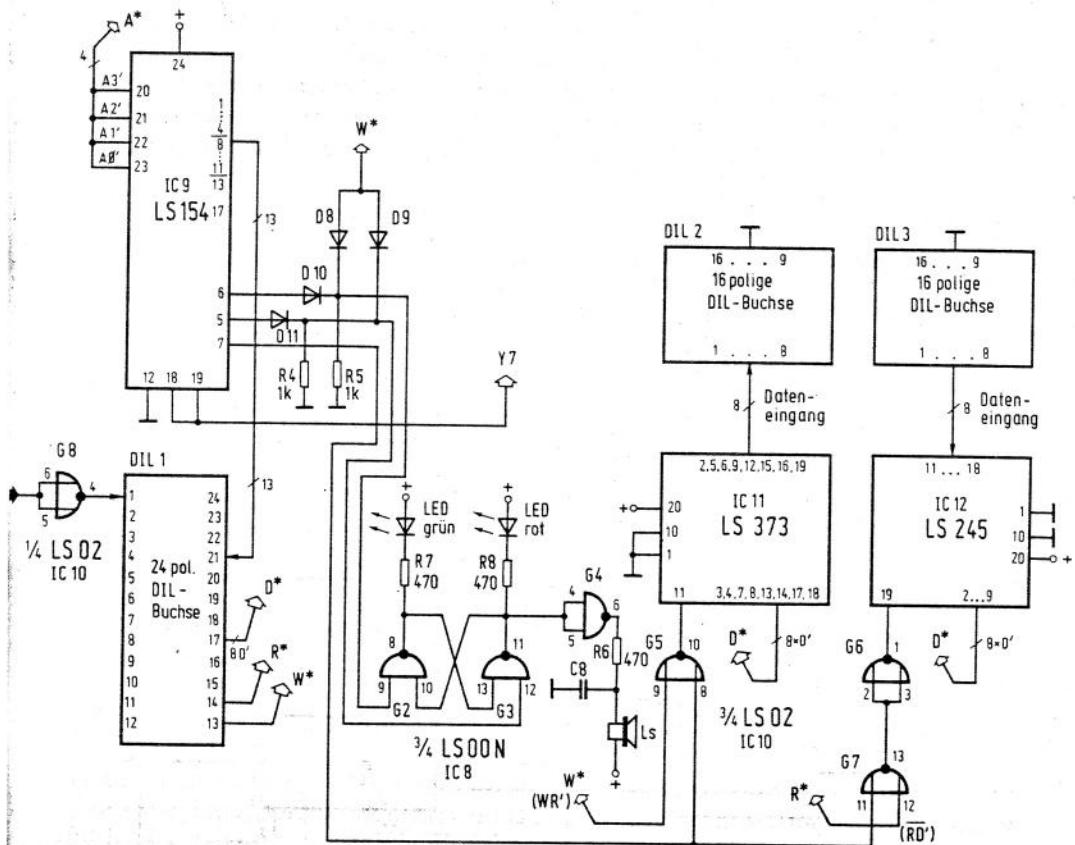

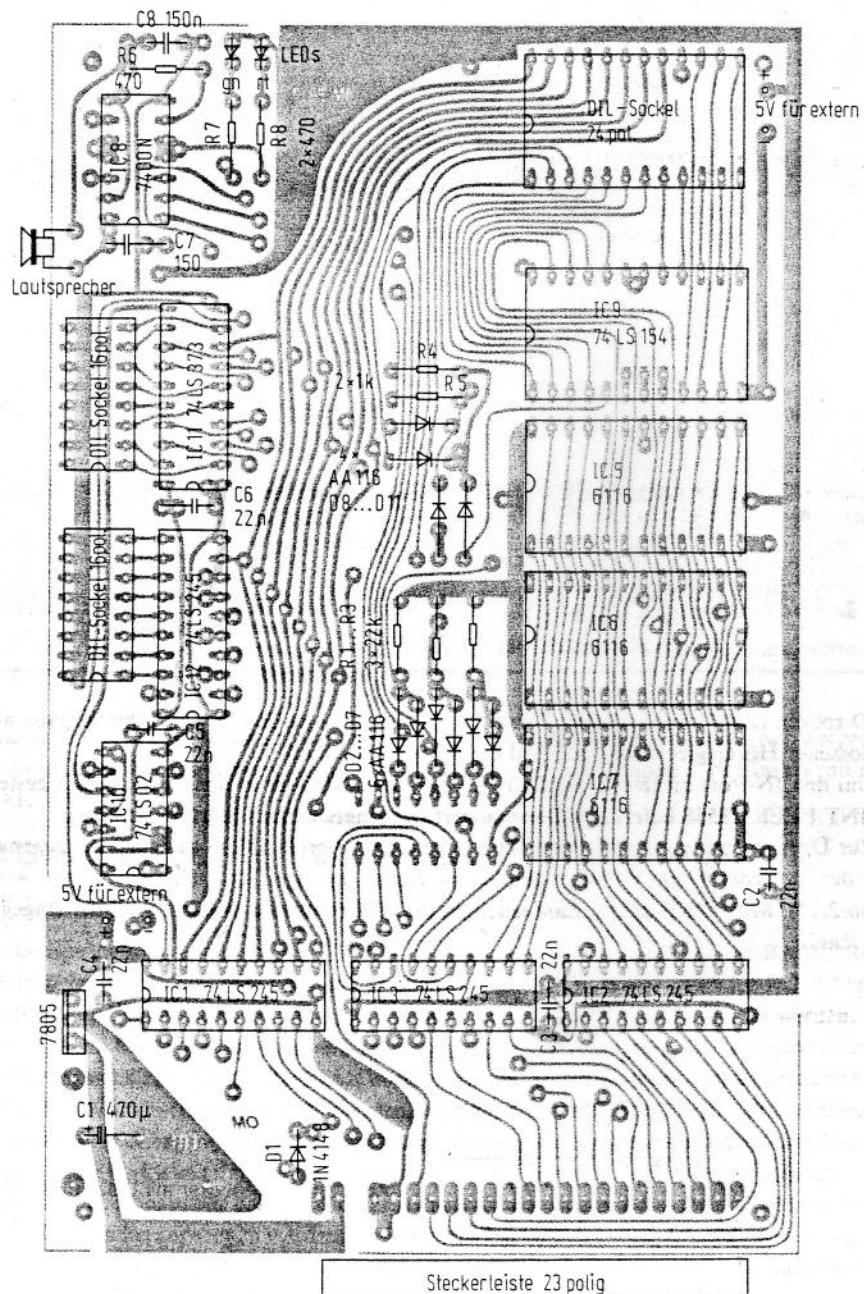

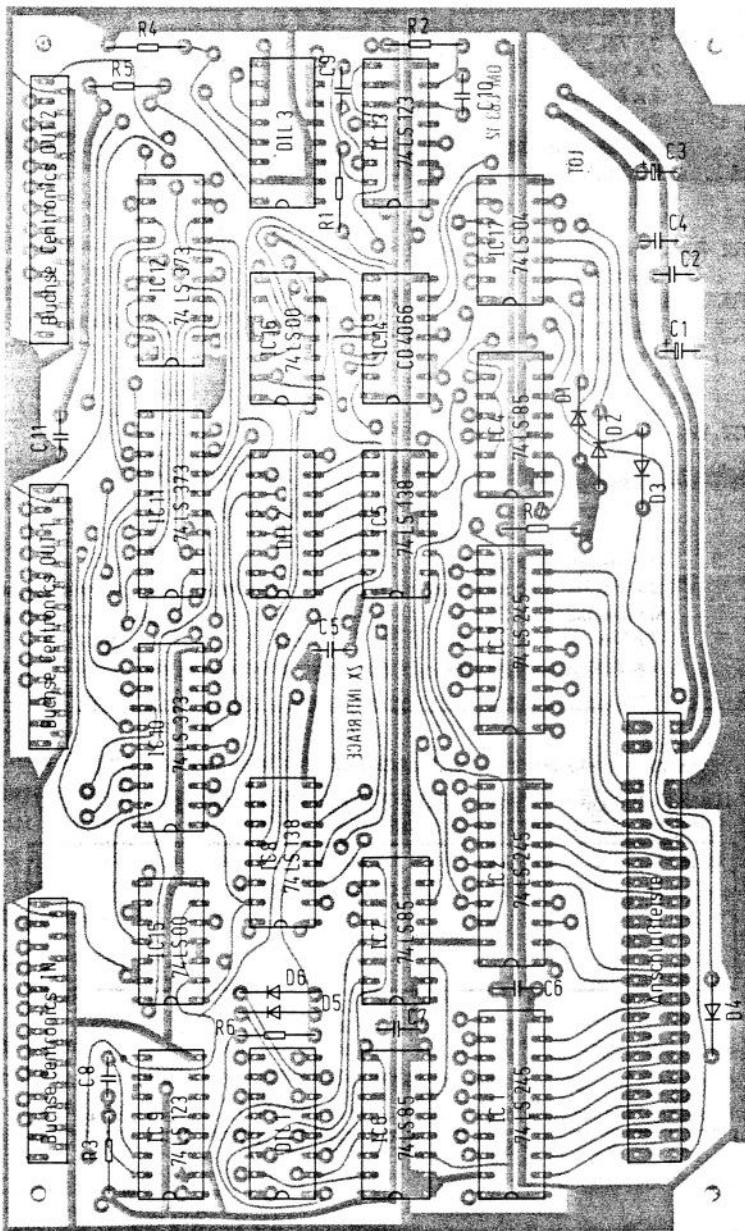

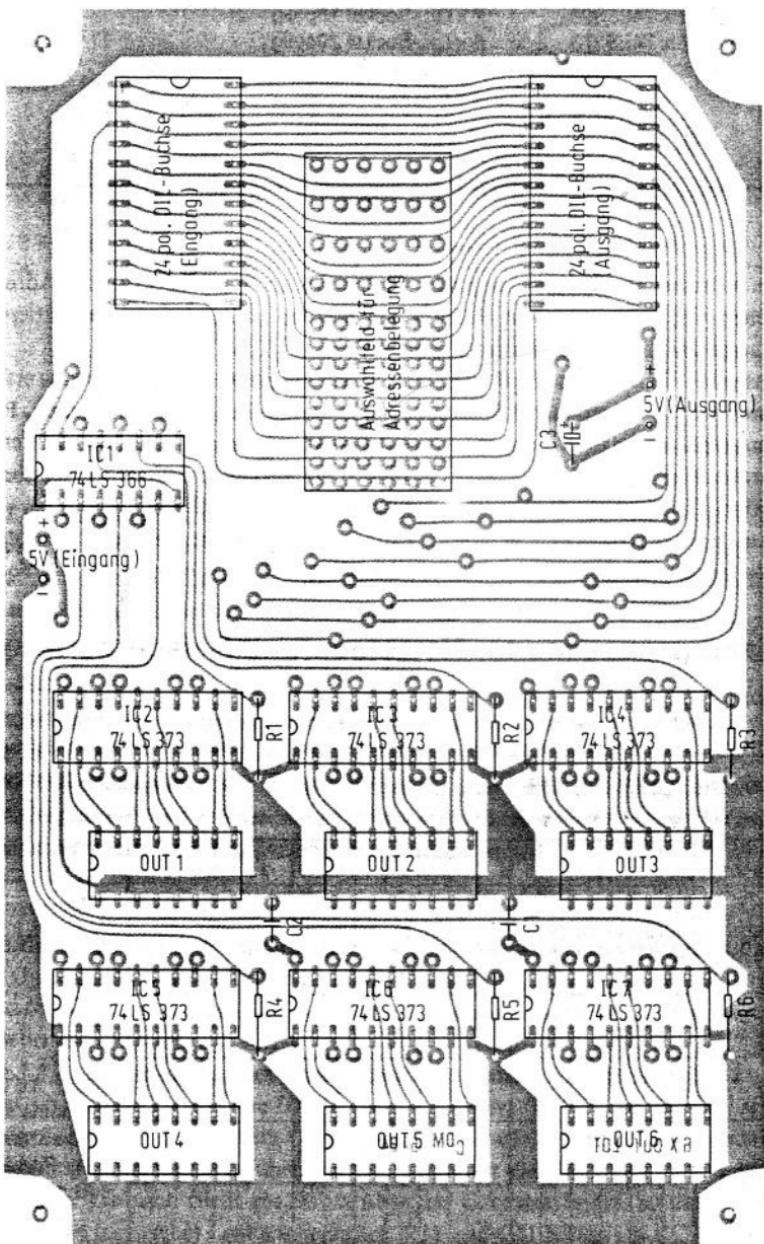

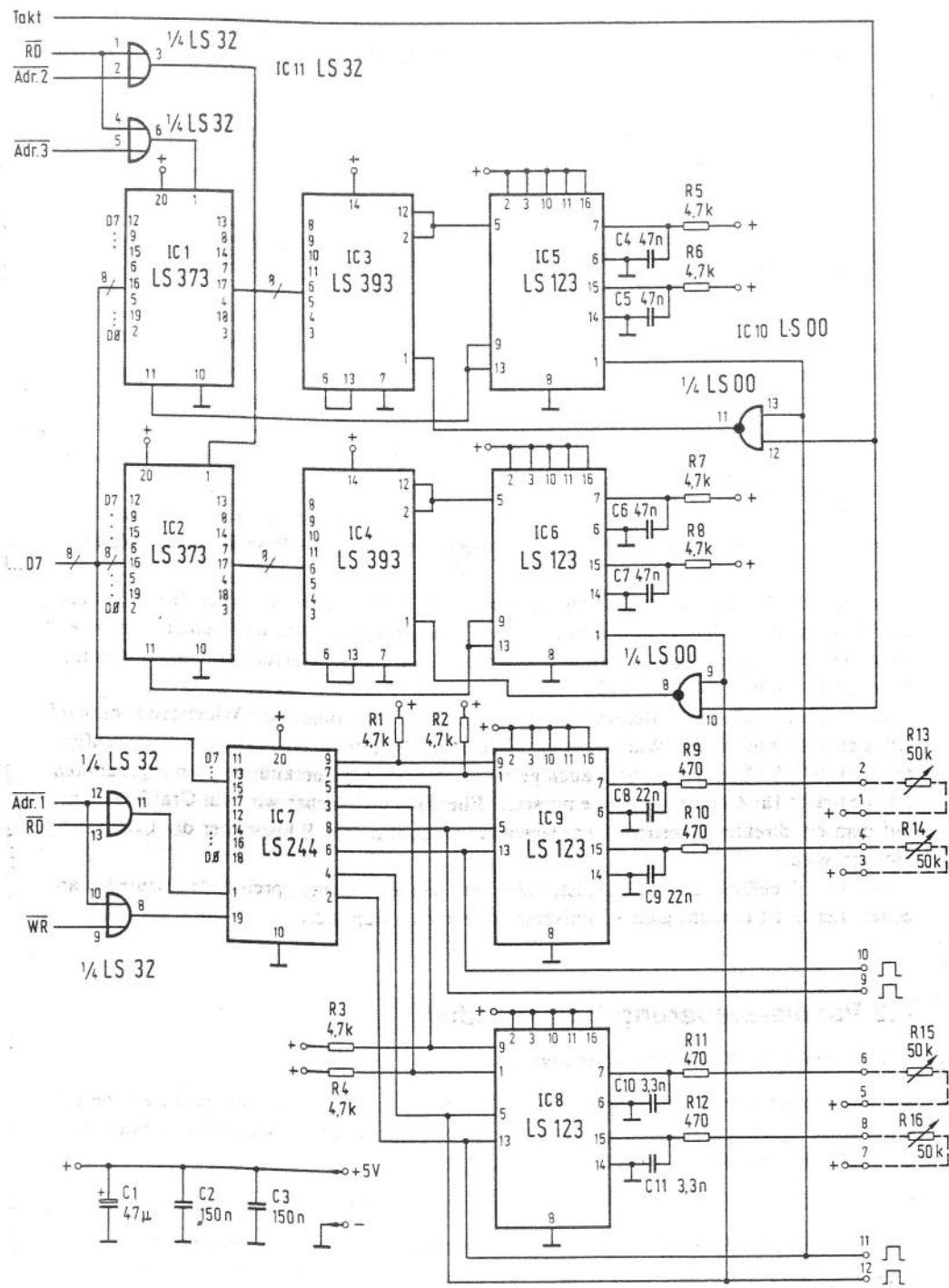

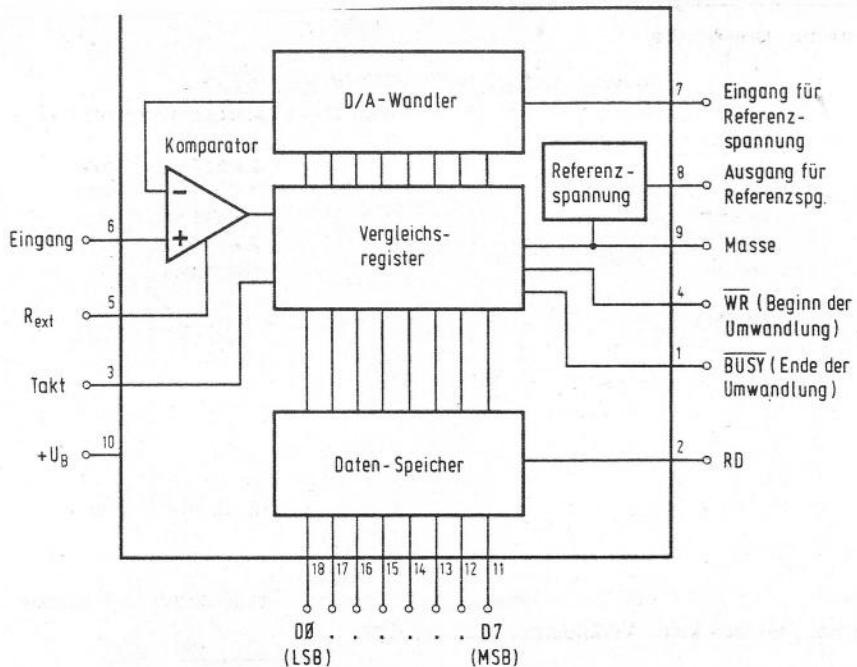

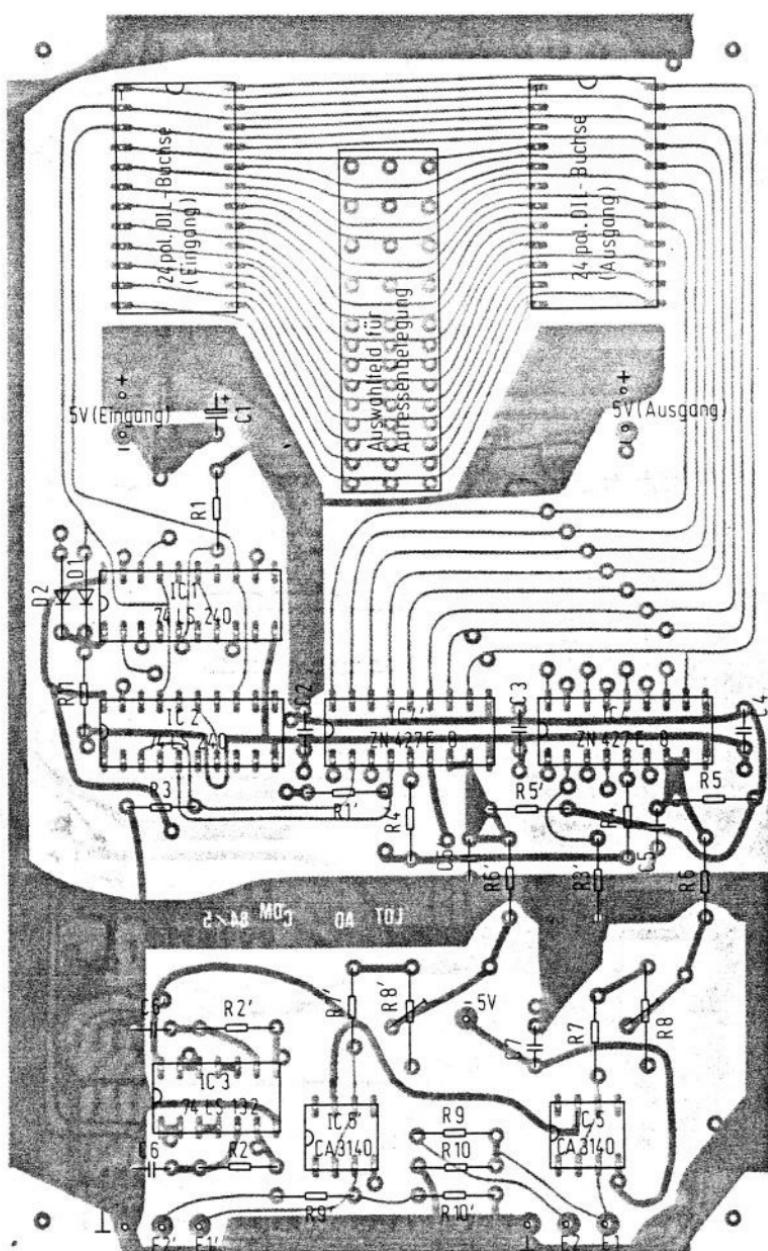

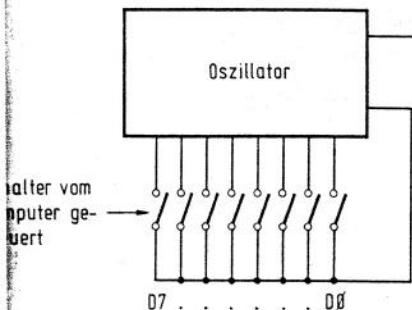

### *2.2.3 Gesamtschaltung der Grundplatine I*

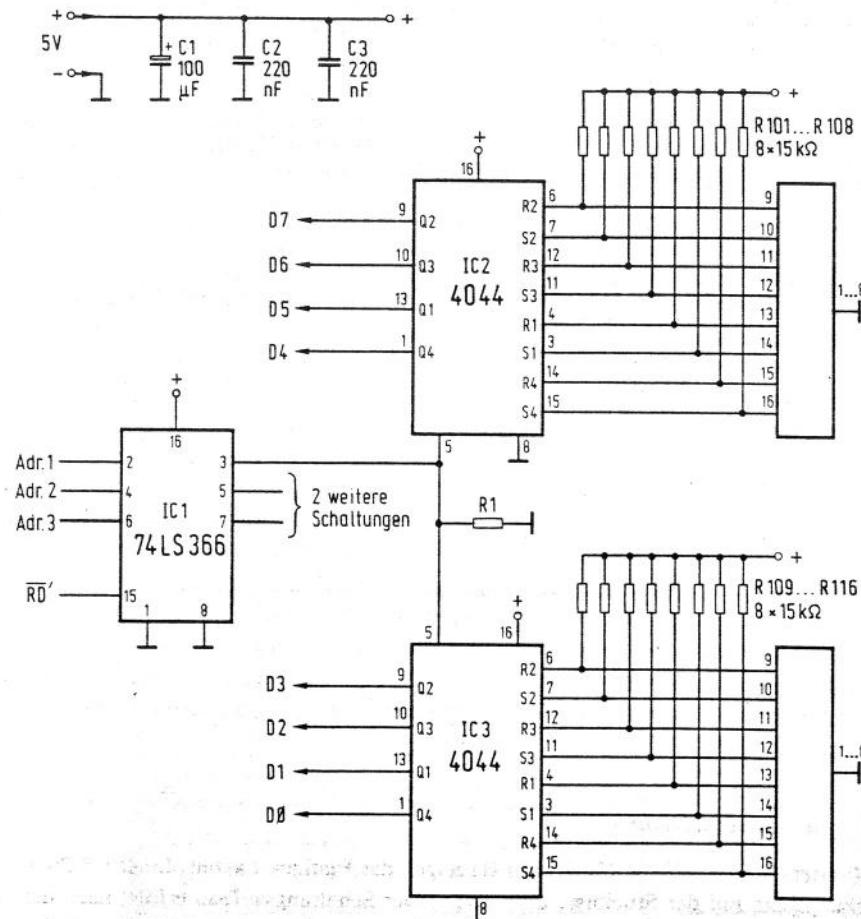

Abb. 2.7 zeigt die Gesamtschaltung der Grundplatte I. Die Stromversorgung erfolgt über den 9-V-Ausgang des ZX 81 und einen Spannungsregler 7805. Zum Abblocken von Impulsstörungen

Abb. 2.7a Schaltbild der Grundplatine I (Speicher und Buspufferung)

## 2 Grundplatinen

Leitungen vom/zum ZX 81

D interne Verbindung

Abb. 2.7b Schaltbild der Grundplatine I (I/O-Ports)

gen auf den Versorgungsleitungen dienen die Kondensatoren C1 ... C7. Selbstverständlich ist auch eine vom ZX 81 unabhängige Stromversorgung möglich. Dazu müssen dann die überflüssig gewordenen Leitungen aufgetrennt werden.

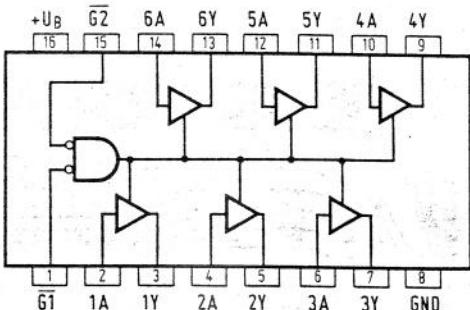

Alle vom Computer kommenden Signale werden mit Bustreibern 74LS245 (IC1 ... 3) gepuffert (Ausnahme: die Adressleitungen A11 und A12, die beide nur eine LS-TTL-Last zu treiben haben). A0 ... A10 gehen nach der Pufferung direkt an die Anschlüsse der Speicher-ICs (IC 5 ... 7). Die Leitungen A14', A13' und MREQ' aktivieren den Adressdekoder 74LS138 wie oben erläutert. In Abhängigkeit von dem aus A10', A11 und A12 gebildeten Eingangswort wird eine der acht Ausgangsleistungen auf logisch 0 geschaltet. Die ODER-Verknüpfung erfolgt für jeweils zwei dieser Ausgangsleistungen über die Germanium-Dioden D2 ... D7. Silizium-Dioden sind wegen ihrer Flussspannung von 0,7 V ungeeignet, da dann eine logische 0 bis zu 1,1 V betragen kann (maximale Ausgangsspannung für logisch 0 bei TTL-Gattern 0,4 V + 0,7 V), das Speicher-IC am CS-Eingang hierfür aber maximal 0,8 V

akzeptiert. Das  $\overline{RD'}$ -Signal wird dem Anschluß  $\overline{OE}$  (output enable), das  $\overline{WR'}$ -Signal dem Anschluß  $\overline{WE}$  (write enable) von IC 5 ... 7 zugeführt.

Um zu verhindern, daß das interne RAM gleichzeitig mit dem externen Speicher auf den Datenbus zugreift, wird es während  $Y_0 = 1$  über die Diode D1 abgeschaltet. Solange  $Y_0 = 0$  oder  $A_{14} = 0$  ist (vergl. Abb.2.1) wird der Datenbus vom internen RAM bzw. ROM belegt. Dann wird der Datenbustreiber IC1 abgeschaltet (der Tristate-Ausgang wird hochohmig), um einen Doppelzugriff zu vermeiden. Die hierfür nötige ODER-Verknüpfung erfolgt über das NAND-Gatter G1, das in negativer Logik ( $Y_0$  und  $A_{14}$  sind hier L-aktiv) eine ODER-Funktion realisiert.

Da der Datenbustreiber in Abhängigkeit von einem Schreib- bzw. Lesezugriff die Daten aus dem Computer hinaus- oder in den Computer hineinleiten soll, muß seine Signalrichtung über die  $\overline{RD'}$ -Leitung umgeschaltet werden (Pin 1 von IC1).  $\overline{RD'} = 0$  bedeutet Lese-Operation („hinein“),  $\overline{RD'} = 1$  bedeutet Nichtlese-Operation („hinaus“).

Die Ports werden vom Adreßdekoder IC9 angesprochen. Dieses IC wird im Adreßbereich 23552 ... 24575 über die Leitung  $Y_7$  von IC4 aktiviert. Dabei wählen A0 ... A3 wie erläutert eine der 16 Ausgangsleitungen an.

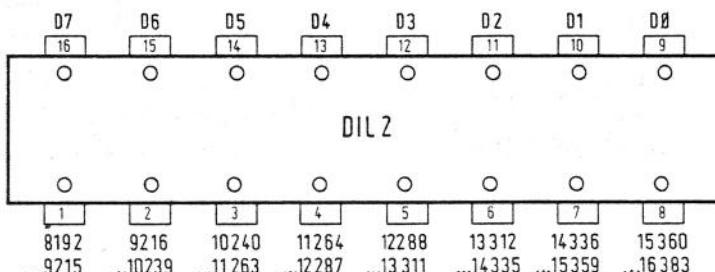

Wenn die Adresse 23558 angesprochen wird, führt Pin 7 von IC9 ein L-Signal. Falls gleichzeitig  $\overline{WR'}$  logisch 0 ist (d. h. wenn z. B. ein POKE-Befehl gegeben wurde), wird über das NOR-Gatter G5 (da negative Logik: UND-Verknüpfung) das 8fach-Latch IC 11 angesprochen (H-Pegel an Pin 11) und speichert die auf dem Datenbus liegenden Informationen. Sie stehen dann an der Buchse DIL 2 extern zur Verfügung.

Falls  $\overline{RD'}$  und Pin 7 von IC9 ein L-Signal führen (also beispielsweise bei einem PEEK-Aufruf) wird auf analoge Weise über G7 IC12 adressiert. G6 dient lediglich als Inverter, da IC12 an Pin 19 in diesem Fall L-Pegel benötigt. Dadurch werden die an DIL3 von außen kommenden Daten in den Computer übernommen.

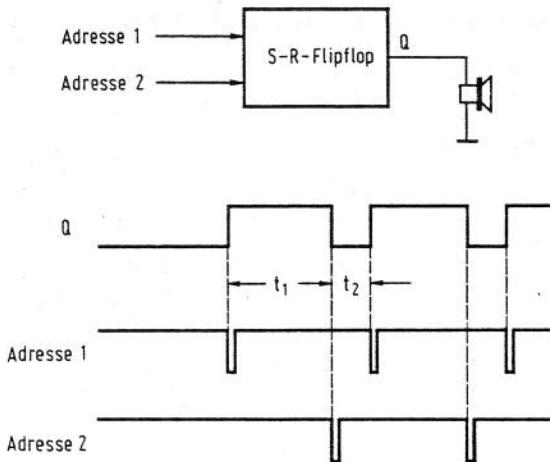

Neben den Ports ist auch noch ein Software-Schalter enthalten. Ein solcher Schalter kann, wie der Name schon sagt, von einem BASIC- oder Maschinenprogramm aus betätigt werden. Hier ist dieser Schalter aus einem Set-Reset-Flipflop mit den beiden NAND-Gattern G2 und G3 aufgebaut. Der Schaltzustand des Flipflops ist durch zwei Leuchtdioden an den Ausgängen erkennbar.

Durch einen Schreibbefehl auf Adresse 23556 wird das Flipflop gesetzt, durch einen gleichartigen Befehl auf Adresse 23557 rückgesetzt. Realisiert wird dies, indem die entsprechende Ausgangsleitung von IC9 über die Dioden D8 ... D11 mit dem  $\overline{WR'}$ -Signal UND-verknüpft wird (negative Logik, da L-aktiv).

Zusätzlich treibt einer der beiden Schalterausgänge über G4 einen Lautsprecher. Jedesmal, wenn umgeschaltet wird, ist im Lautsprecher ein Klick-Geräusch zu hören. Erfolgt die Umschaltung schnell genug, so entsteht ein Ton. Seine Frequenz ist durch die Umschaltfrequenz gegeben, auf diese Weise ist also eine softwaregesteuerte Tonerzeugung möglich. Der Wert von R6 bestimmt die Lautstärke des Tons. Der Lautsprecher ist nicht gegen Masse, sondern gegen +U geschaltet, da TTL-Gatter gegen Masse einen höheren Strom vertragen können.

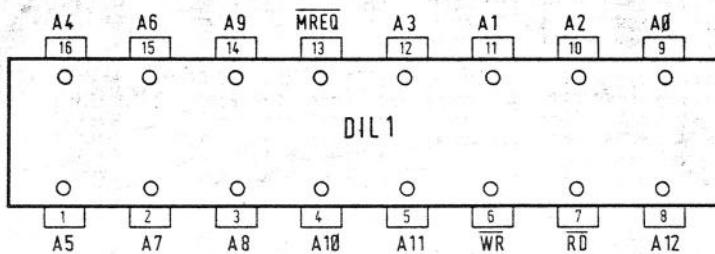

Die verbleibenden 13 dekodierten Adressen sind zusammen mit dem Datenbus und den  $\overline{RD'}$ - sowie  $\overline{WR'}$ -Signalen an die Buchse DIL1 geführt. Auch der CPU-Takt steht an dieser Buchse zur Verfügung. Hier lassen sich die weiteren Zusatzkarten anschließen.

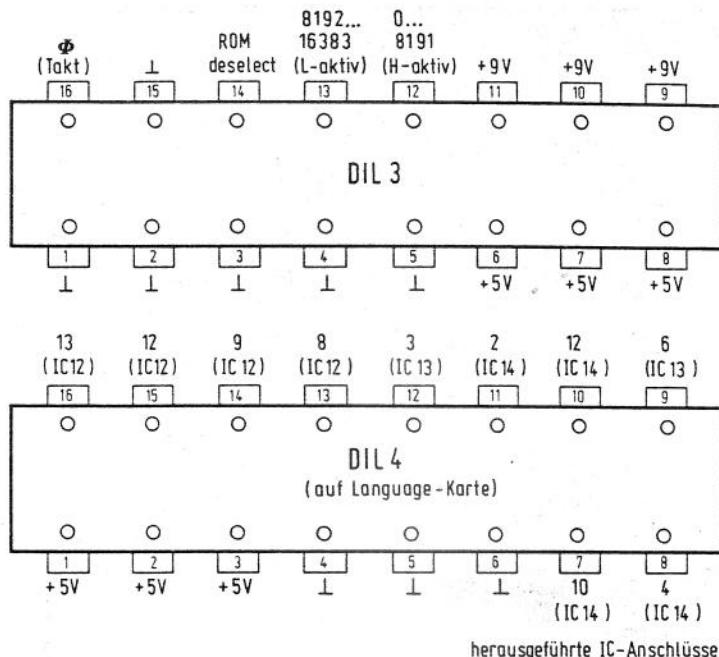

Die Portadressen sowie die Stiftbelegung der DIL-Buchsen sind in Abb.2.8 zusammengefaßt.

23556 Einschalten LED grün

23557 Einschalten LED rot

23558 I/O-Port (jeweils unidirektional)

| DIL 1 |                      |    | DIL 2 (Ausgabe) | DIL 3 (Eingabe) |

|-------|----------------------|----|-----------------|-----------------|

| 1     | Takt ( $\emptyset$ ) | 13 | 23562           | 1 D 0           |

| 2     | RD'                  | 14 | 23561           | 2 D 1           |

| 3     | WR'                  | 15 | 23560           | 3 D 2           |

| 4     | 23552                | 16 | 23559           | 4 D 3           |

| 5     | 23553                | 17 | D 0'            | 5 D 4           |

| 6     | 23554                | 18 | D 1'            | 6 D 5           |

| 7     | 23555                | 19 | D 2'            | 7 D 6           |

| 8     | 23567                | 20 | D 3'            | 8 D 7           |

| 9     | 23566                | 21 | D 4'            |                 |

| 10    | 23565                | 22 | D 5'            | 9...16 Masse    |

| 11    | 23564                | 23 | D 6'            | 9...16 Masse    |

| 12    | 23563                | 24 | D 7'            |                 |

Abb. 2.8 Portadressen und Steckerbelegung

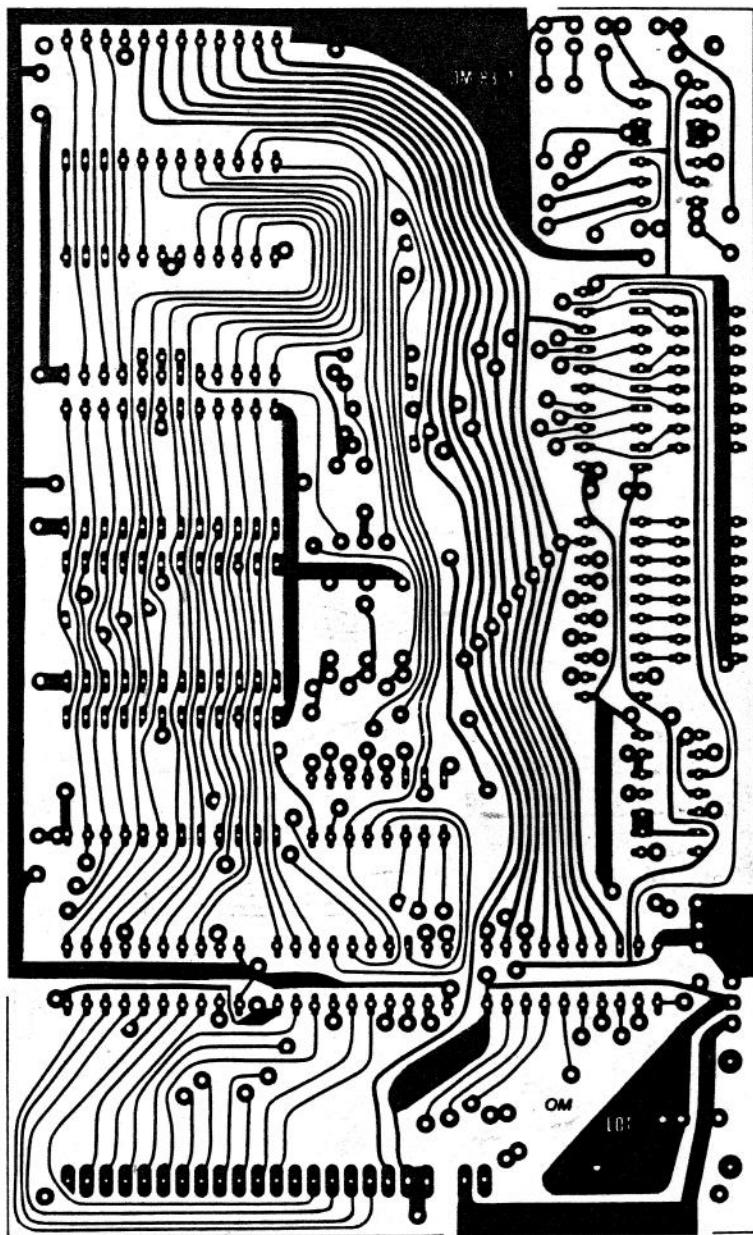

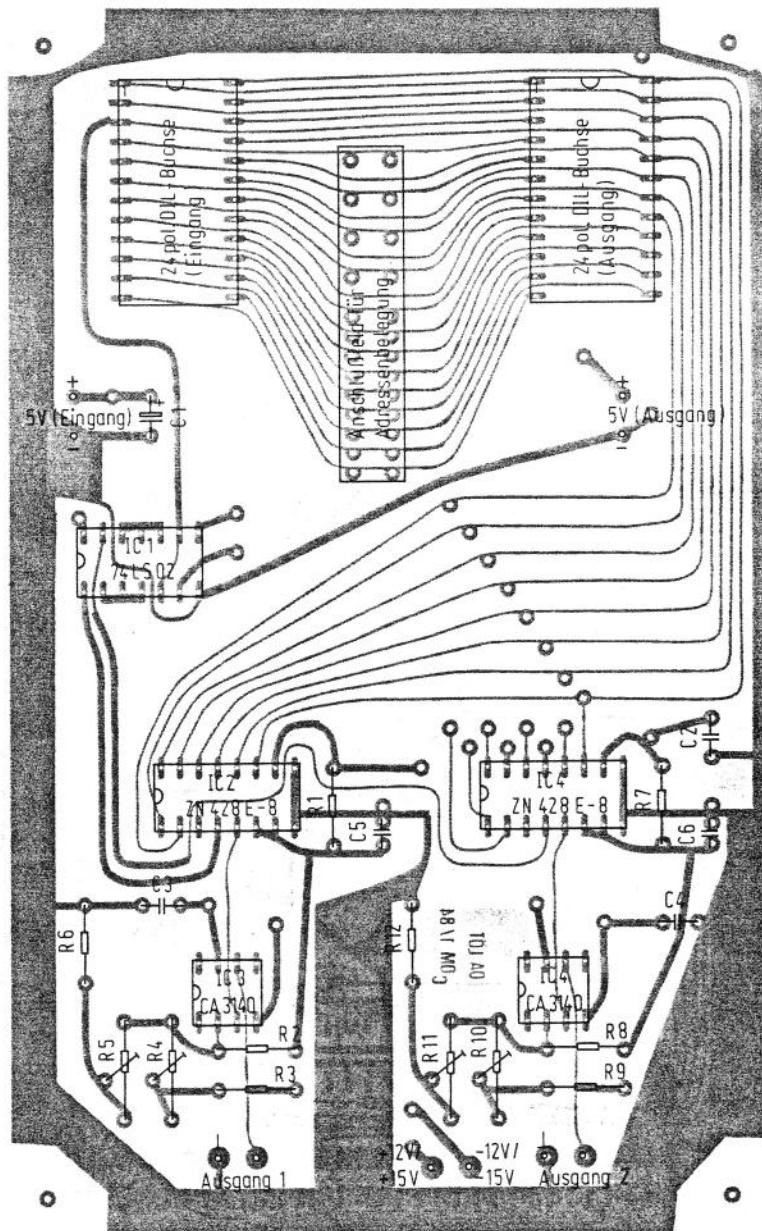

#### 2.2.4 Aufbauhinweise, Inbetriebnahme und Test

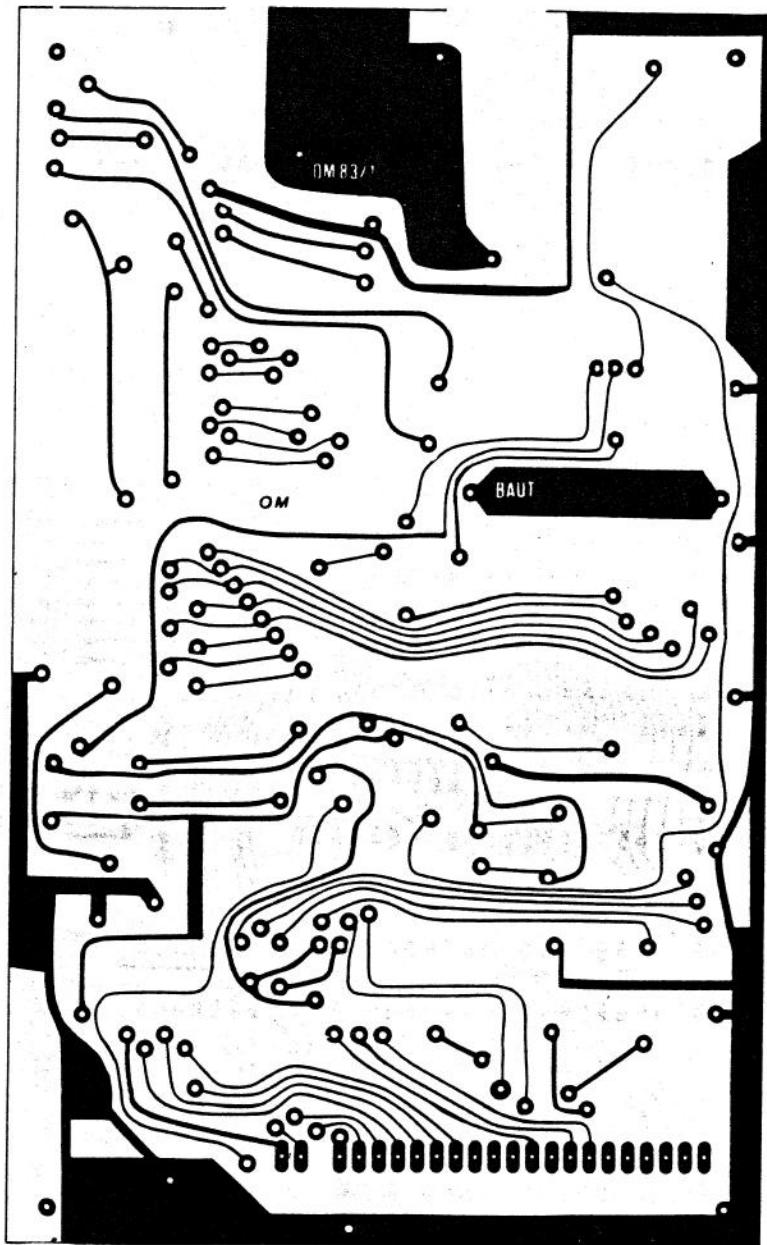

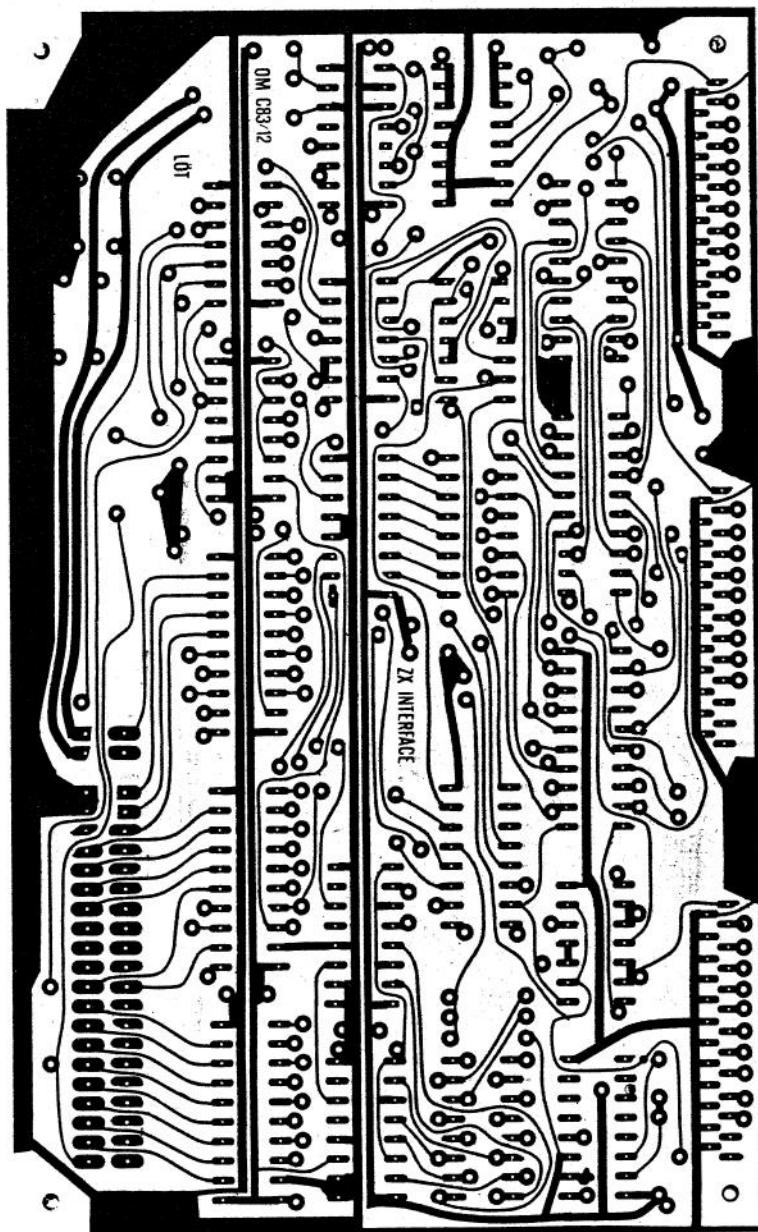

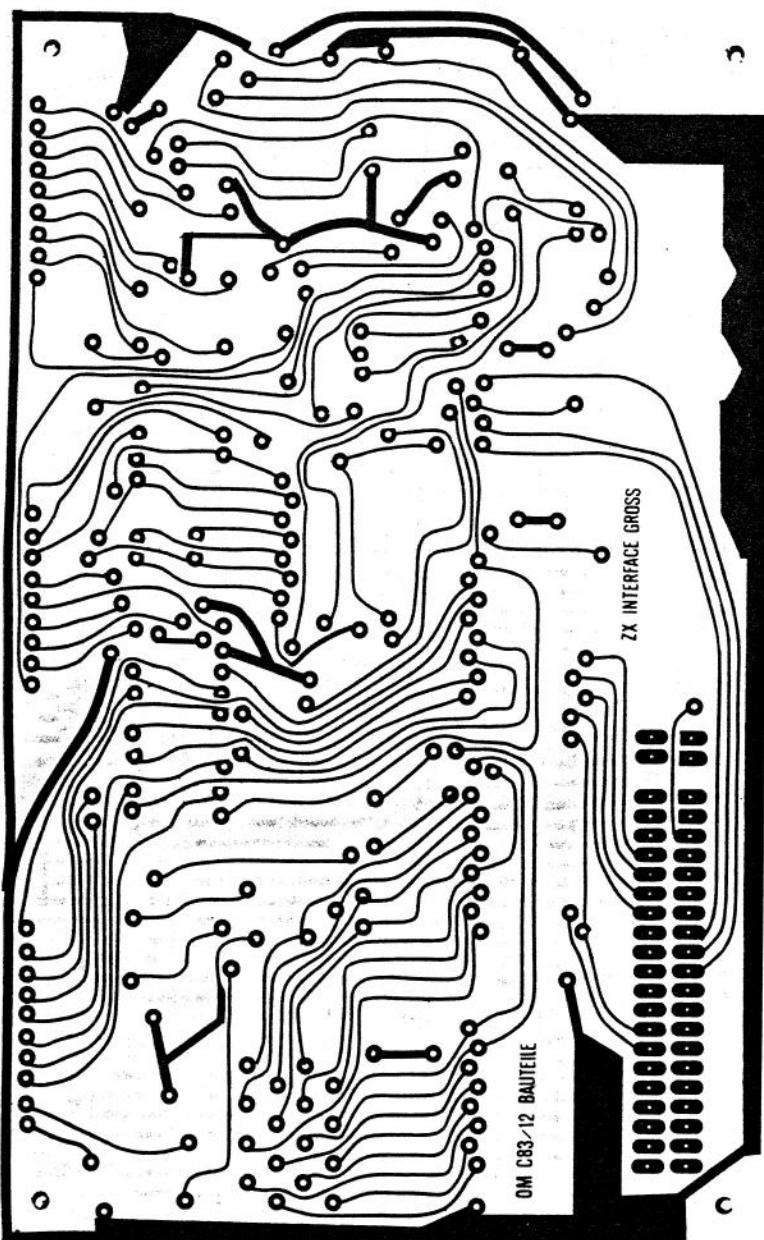

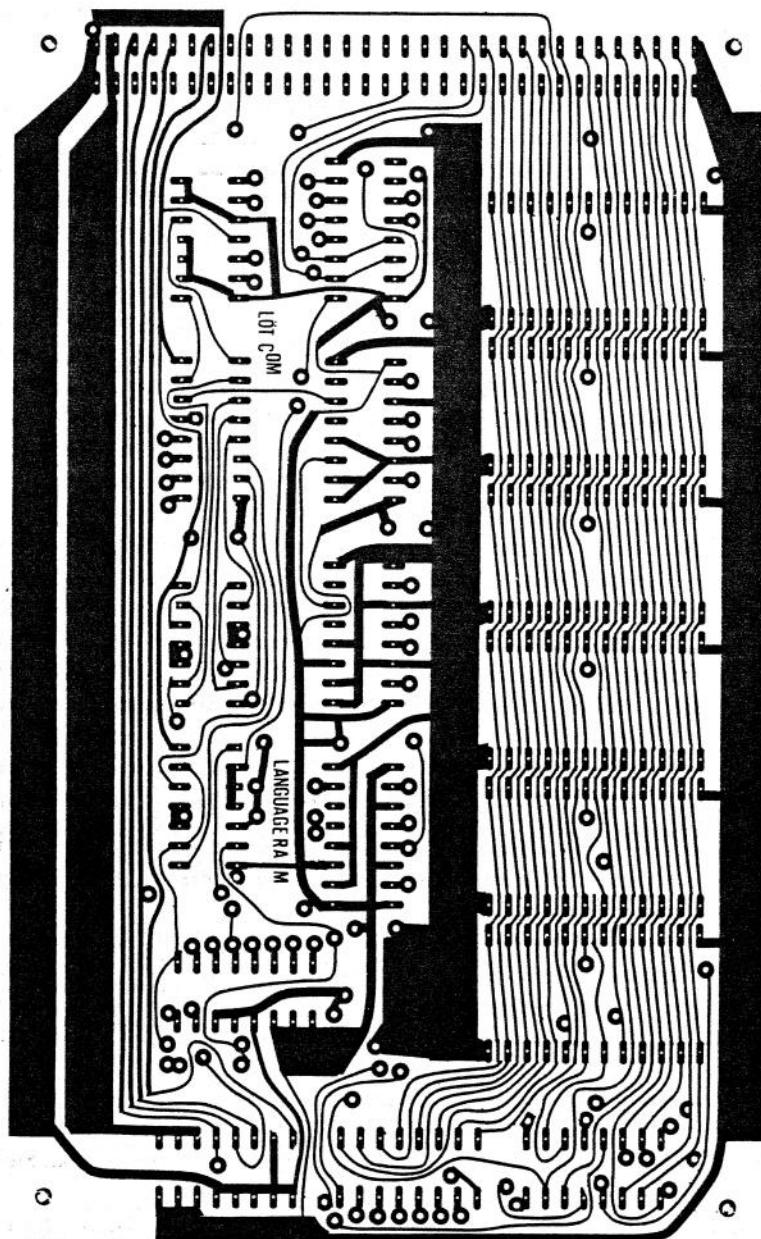

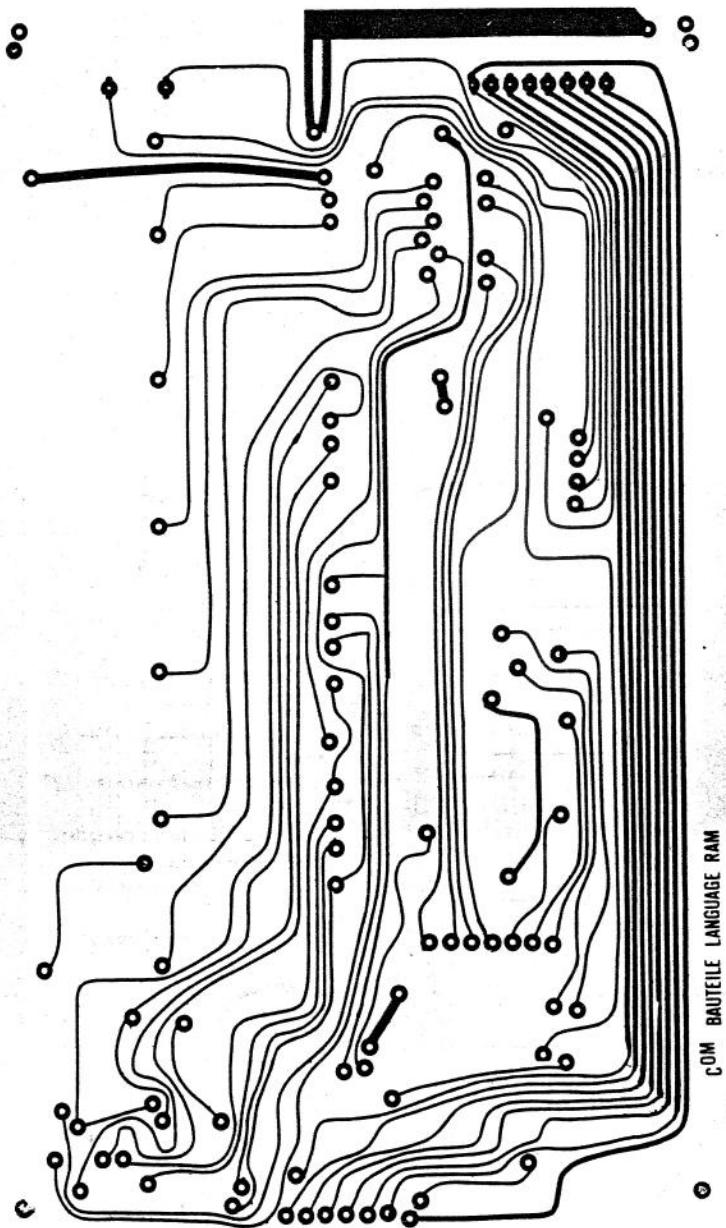

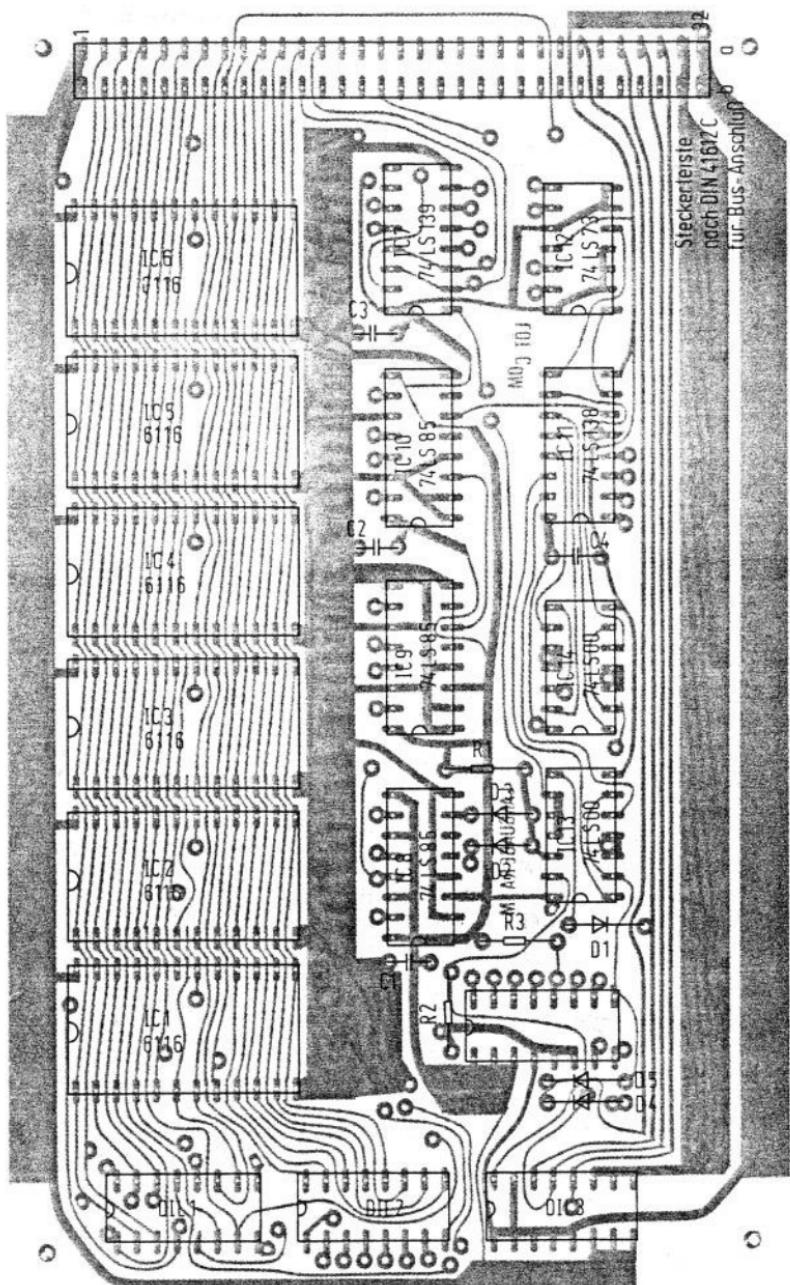

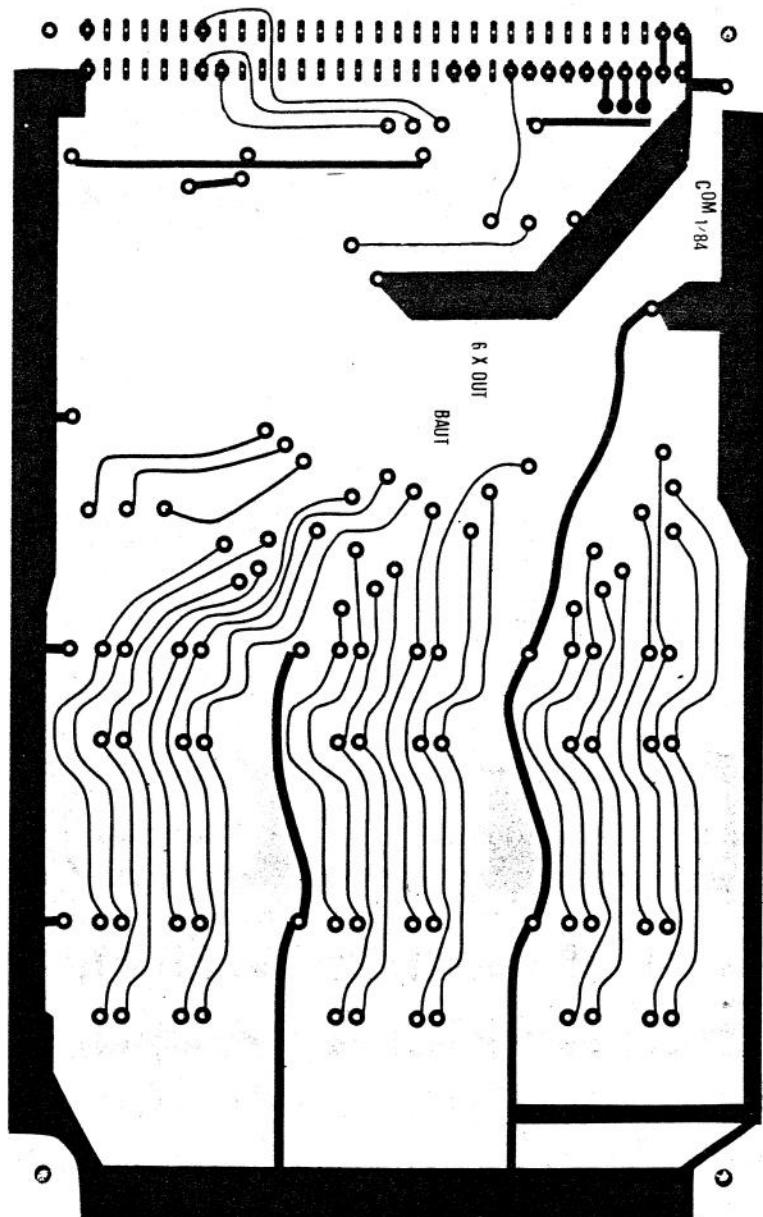

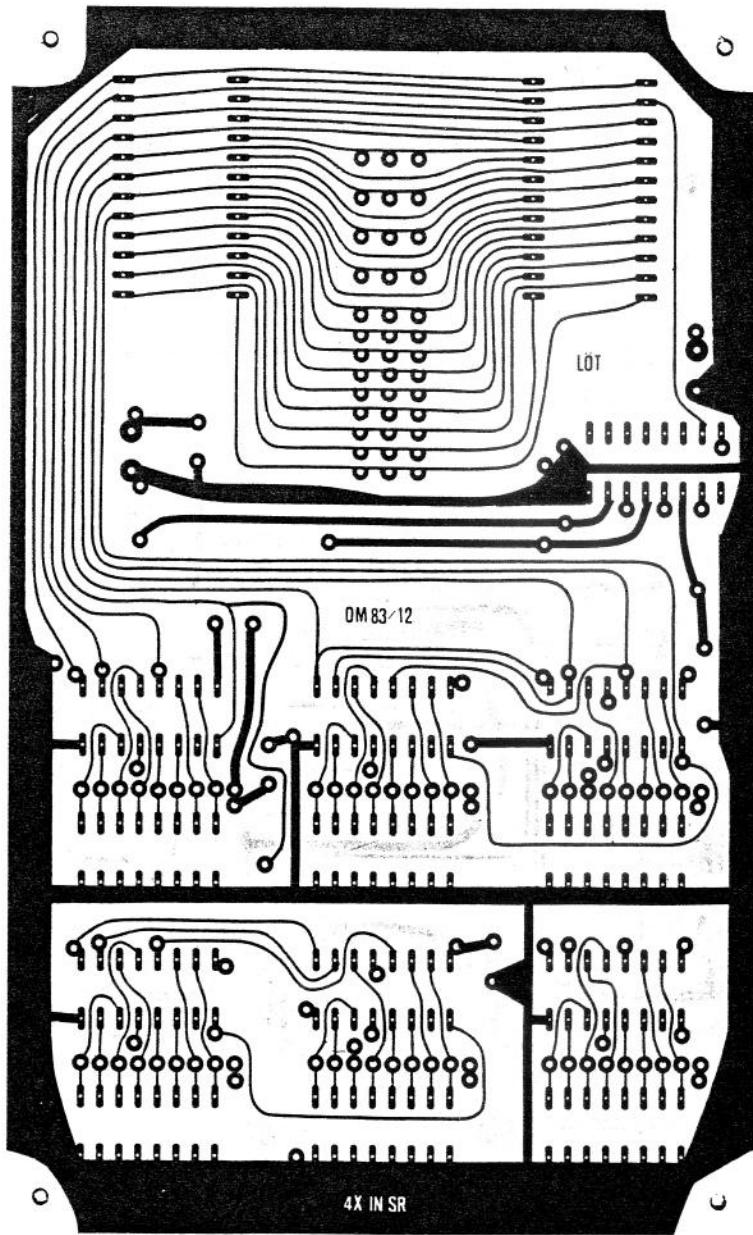

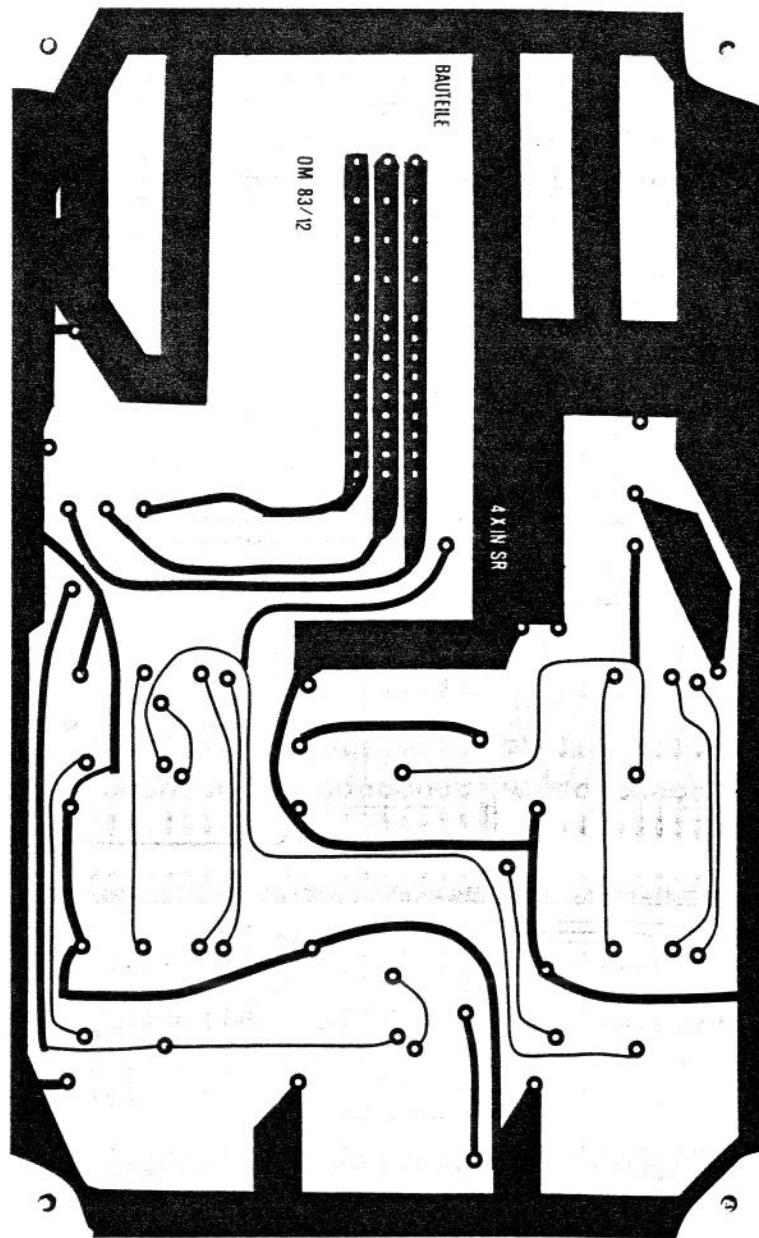

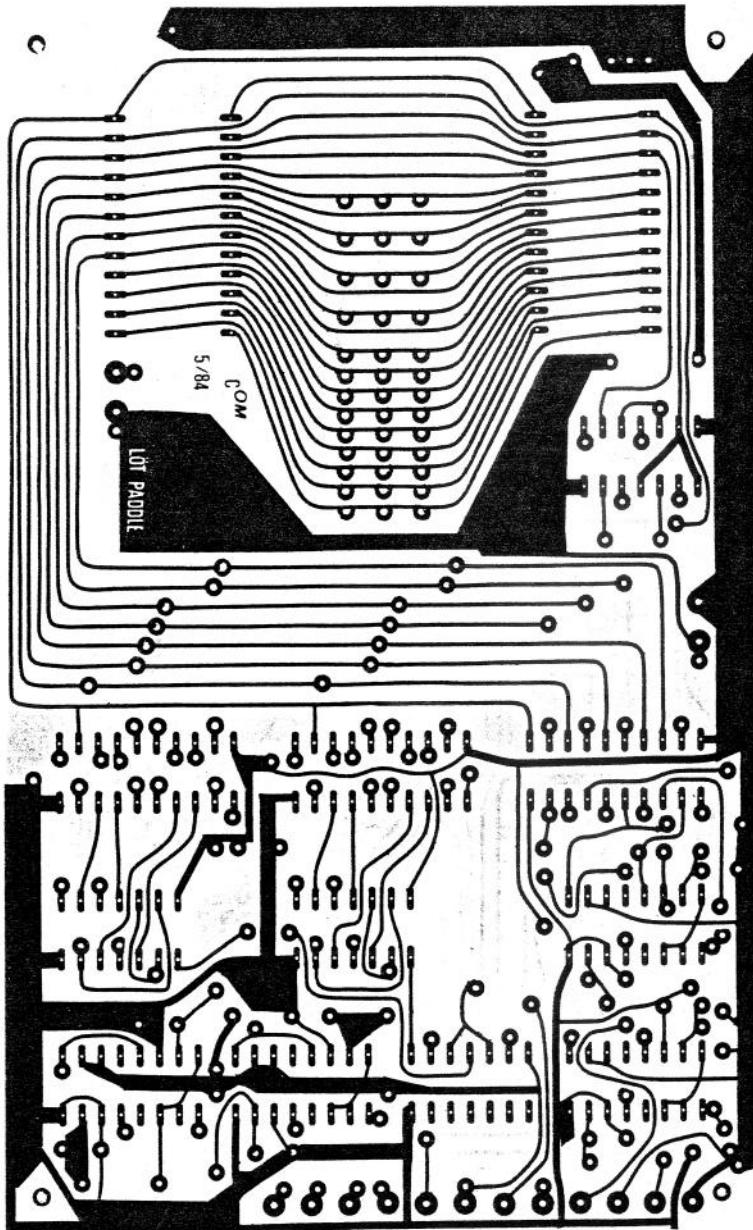

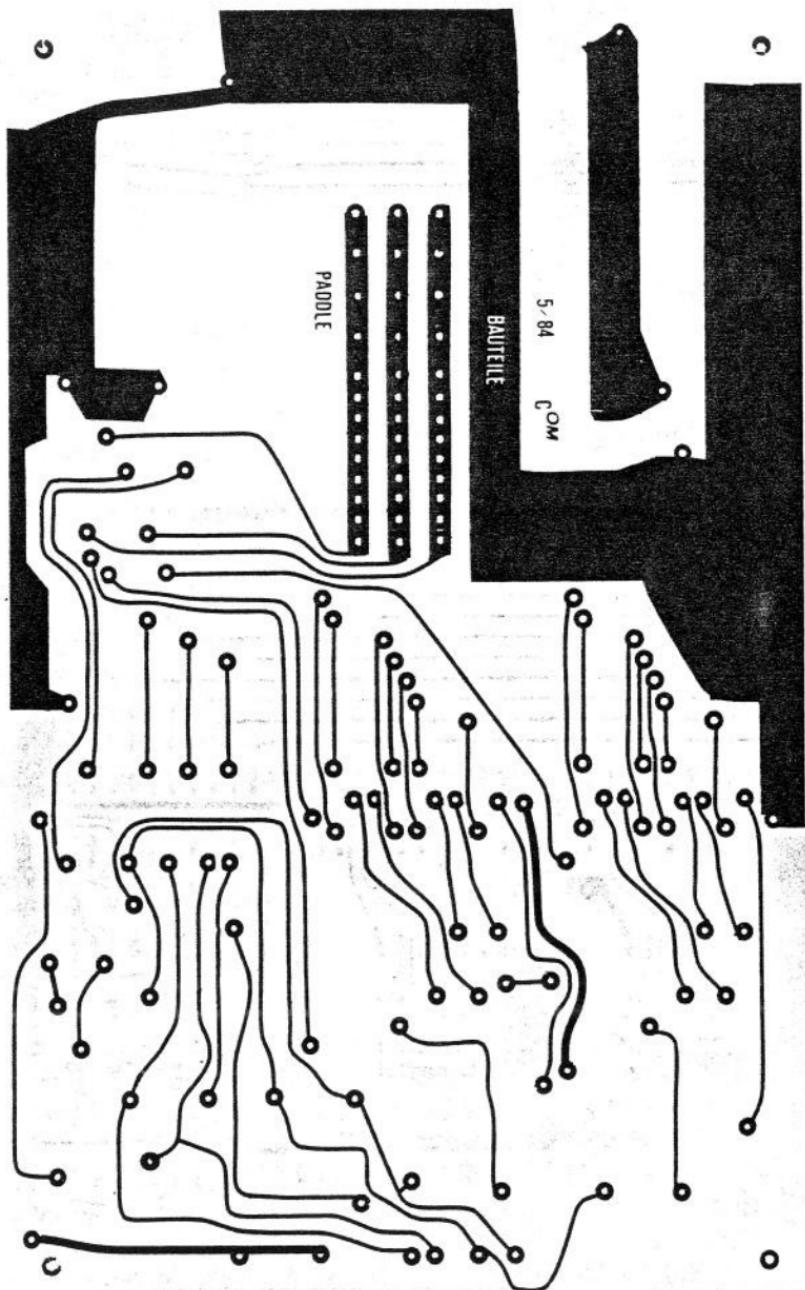

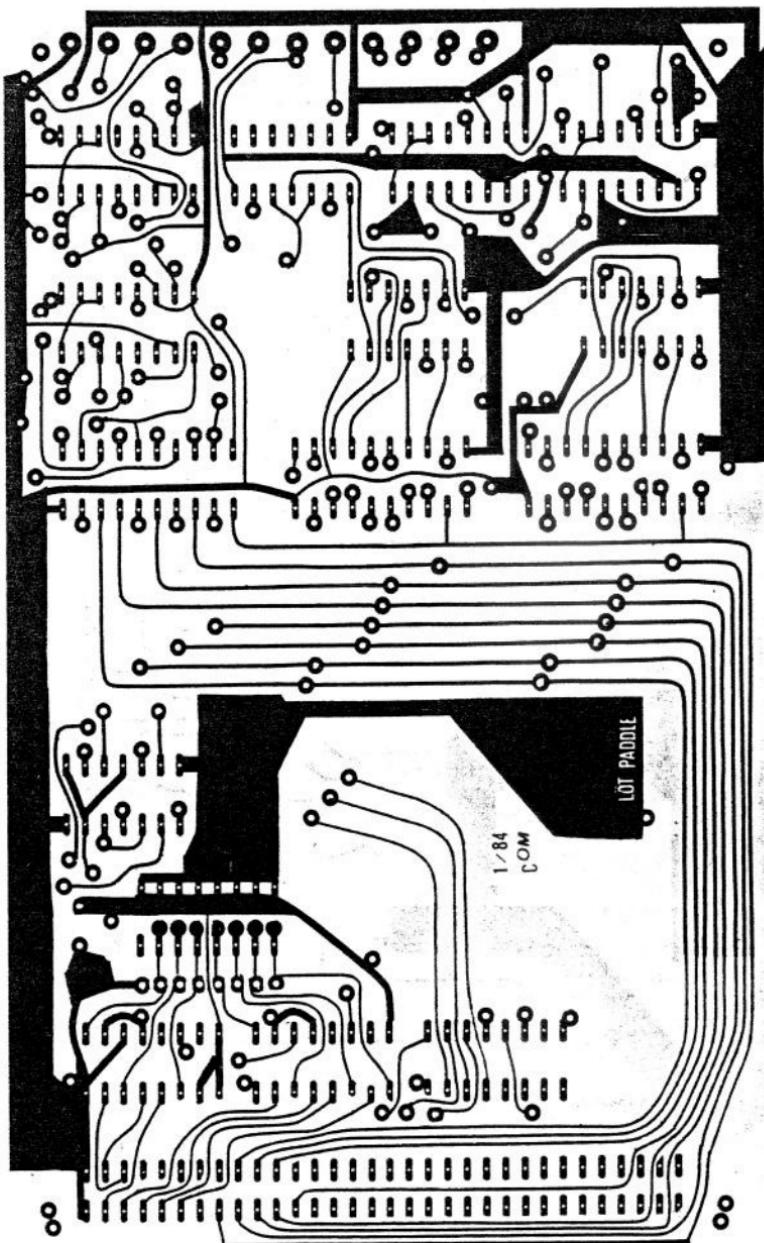

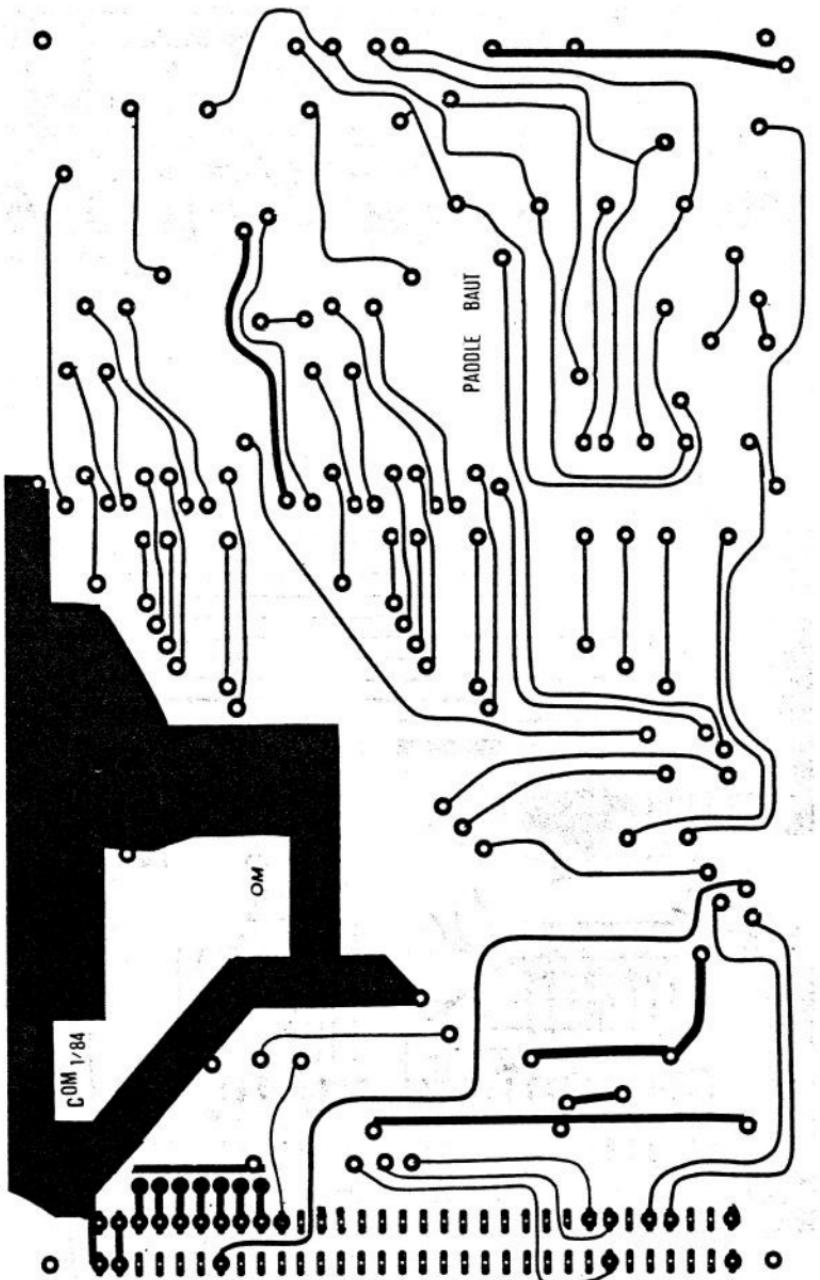

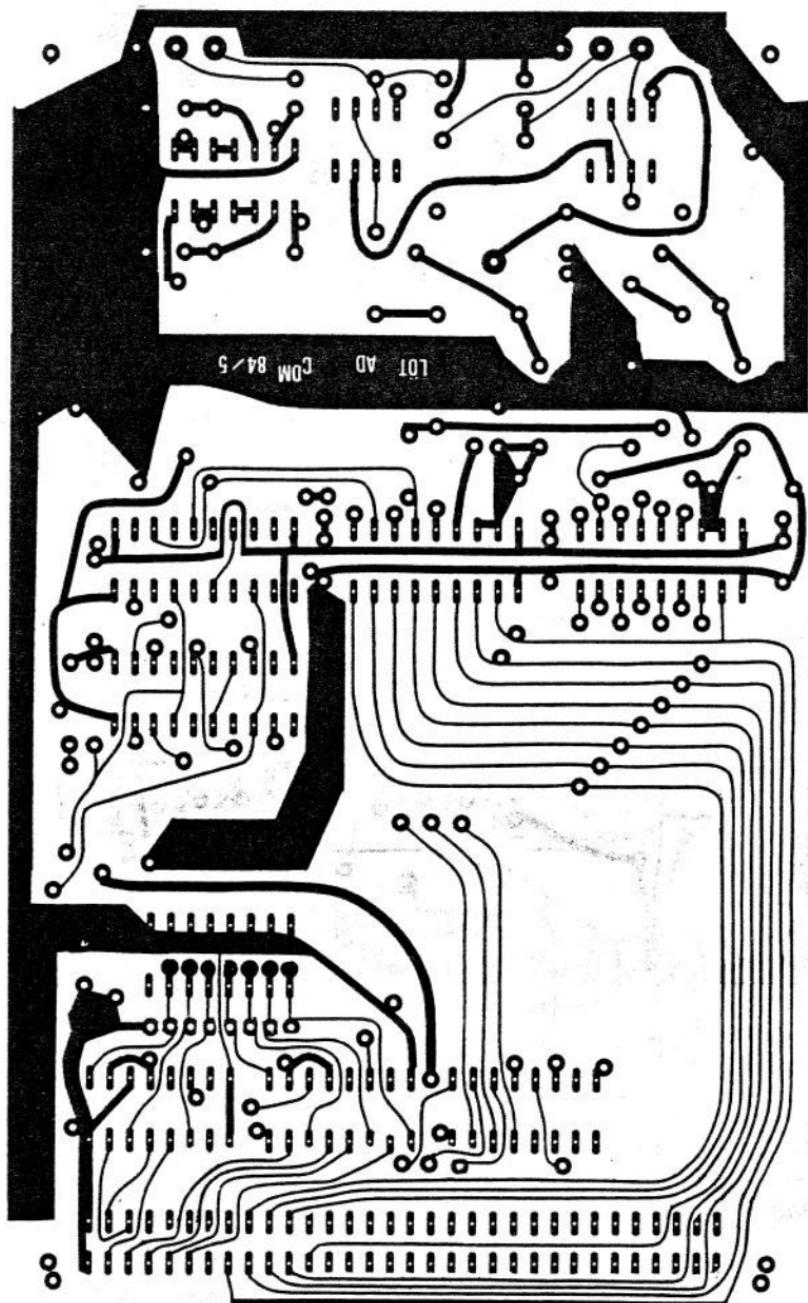

Das Platinenlayout ist in Abb.2.9 gezeigt. Nach Überprüfung der Platine müssen zuerst alle Durchkontaktierungen erfolgen. Ausnahmsweise dürfen bei dieser Platine nicht alle von der Bestückungsseite sichtbaren Bohrungen kontaktiert werden, die Bohrungen der Steckerleiste müssen frei bleiben. Es sollte möglichst nichts vergessen werden, da einige Kontaktierungen unter IC-Sockeln liegen und später nicht mehr zugänglich sind. Anschließend werden die IC-Sockel, dann Kondensatoren und sonstige Bauteile eingesetzt und verlötet.

Beim Einlöten der Steckerleiste ist genügend Abstand zur Platine einzuhalten, damit das Anstecken an den ZX 81 ohne Schwierigkeiten möglich ist. Die A-Kontaktreihe wird von der Bestückungsseite her verlötet. Für den Spannungsregler sollte ein geeignetes Kühlblech vorgesehen werden (Befestigungsbohrungen sind auf der Platine vorhanden).

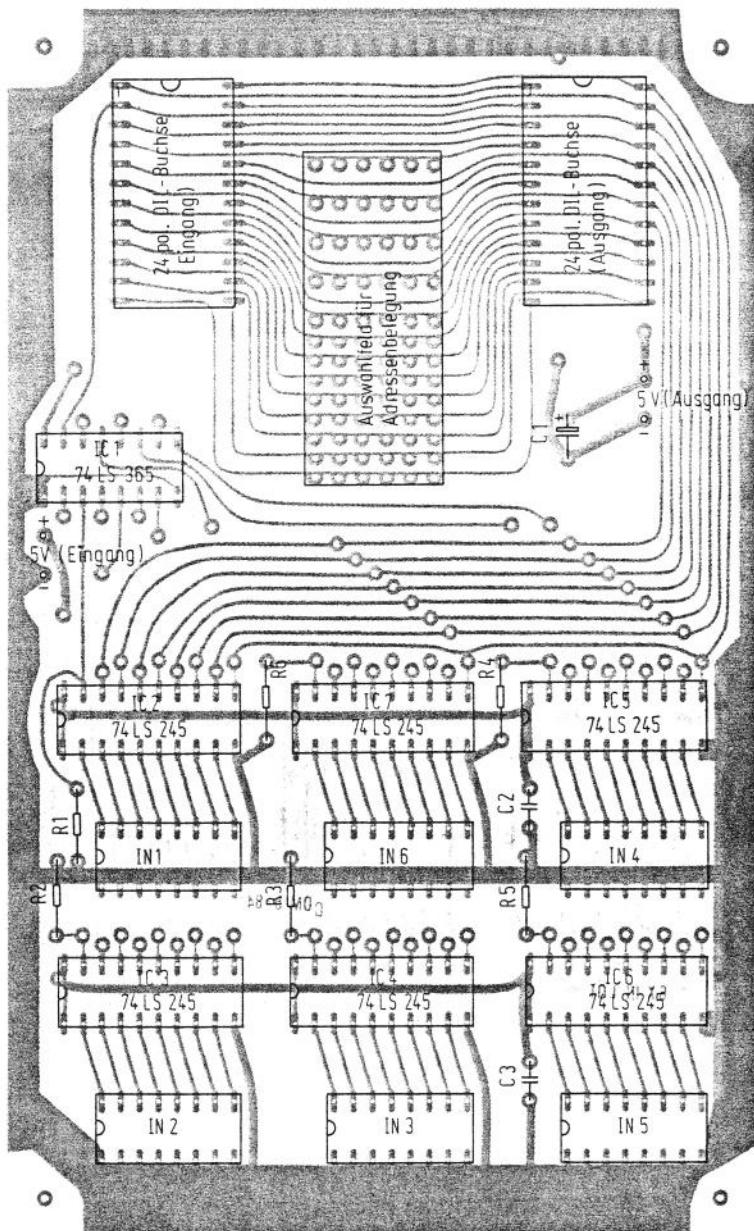

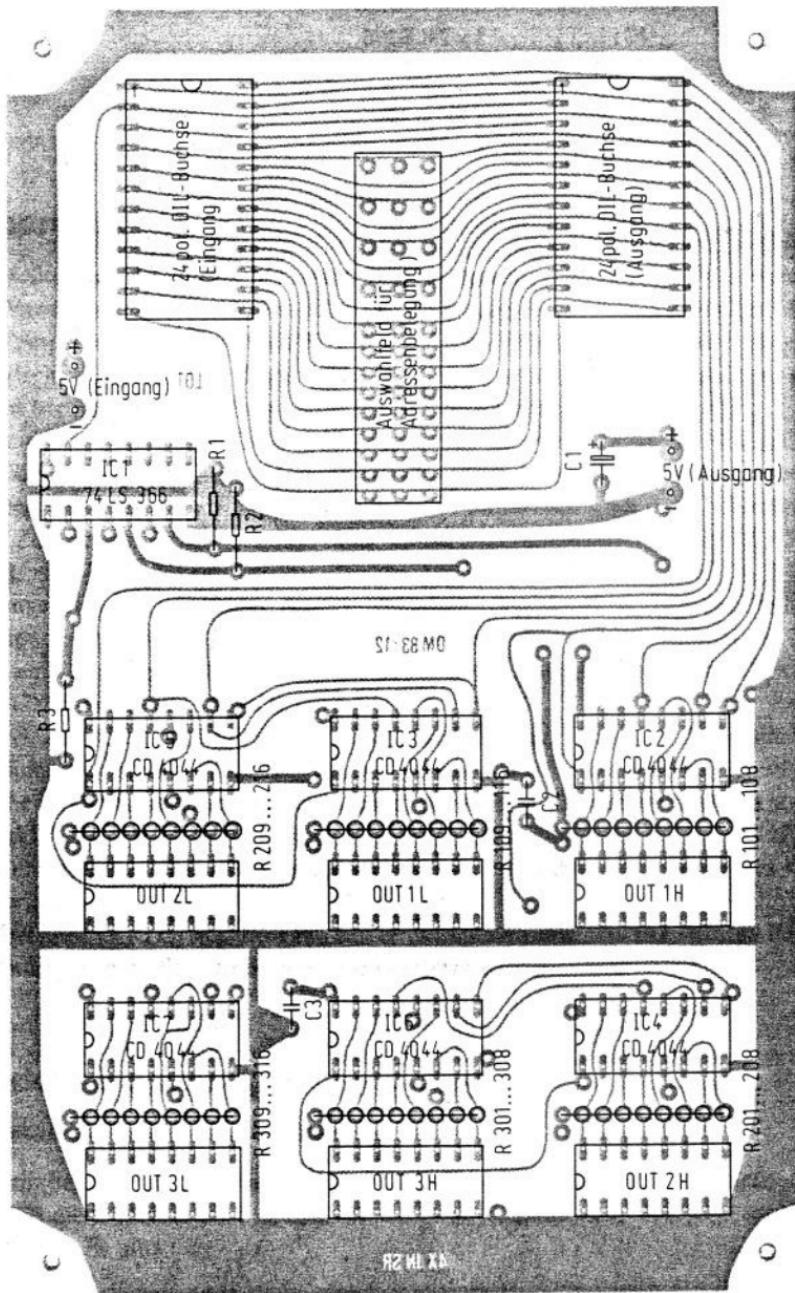

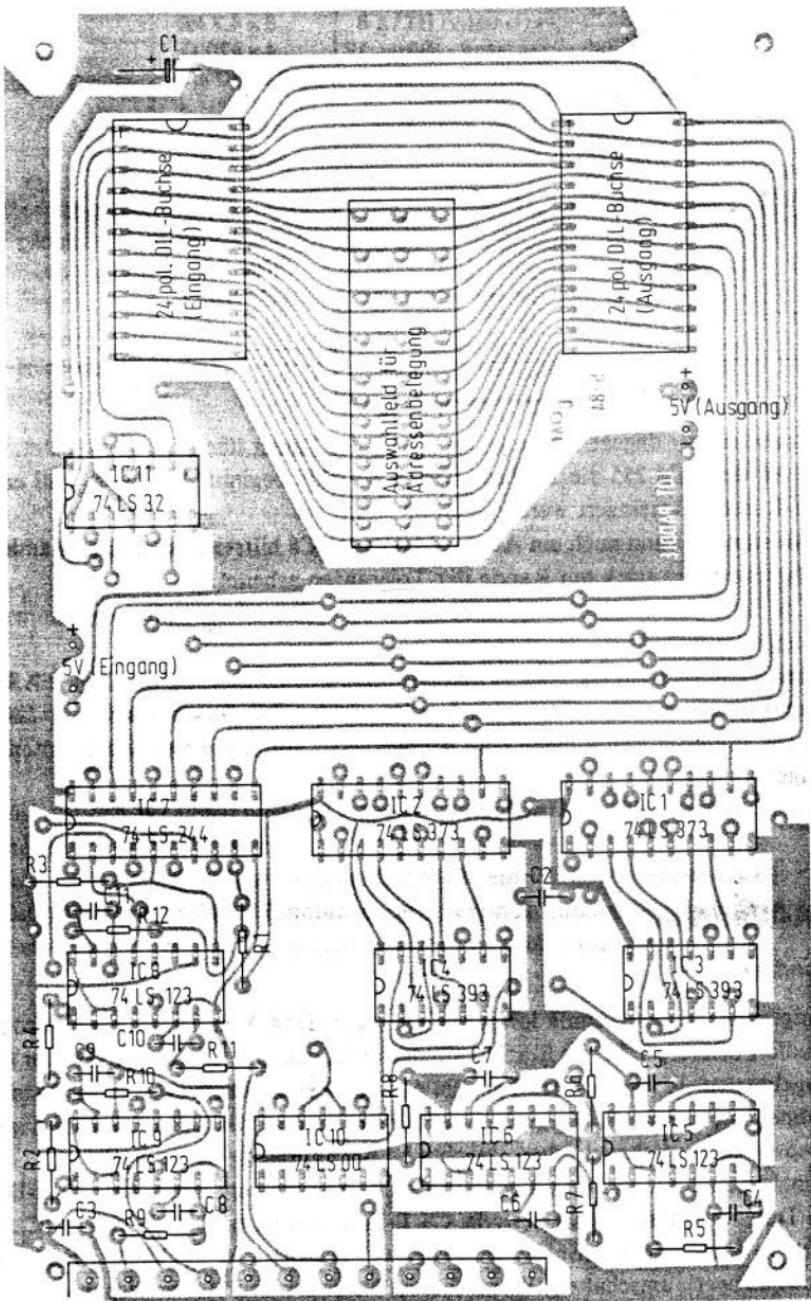

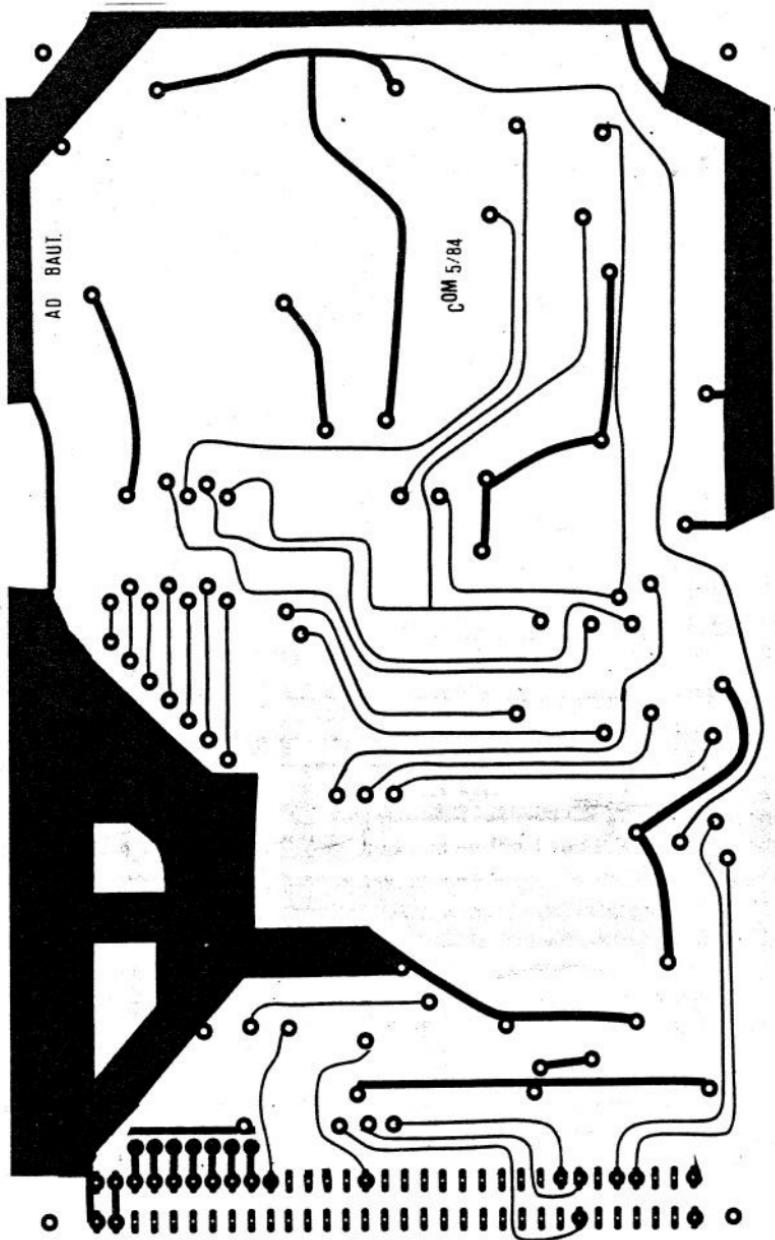

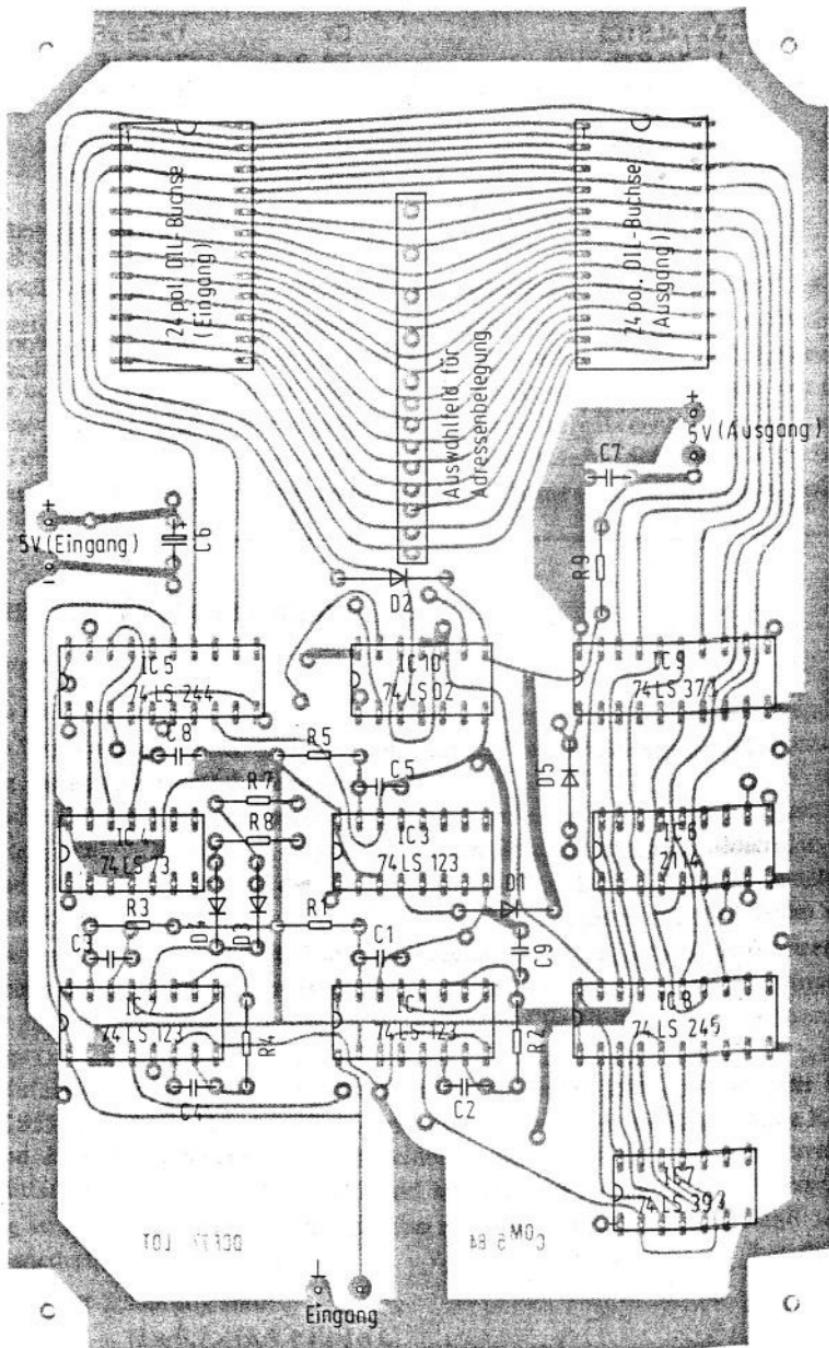

Abb.2.10 zeigt den Bestückungsplan (Blick auf Bauteileseite) sowie die Stückliste zur Grundplatine I.

Bei der Inbetriebnahme empfiehlt es sich, die Platine zunächst ohne eingesteckte ICs in Betrieb zu nehmen. Wenn keine Kurzschlüsse vorhanden sind, muß nun auf dem Bildschirm der Cursor erscheinen. Dann werden die ICs eingesetzt (Betriebsspannung ausschalten!). Es dauert jetzt etwas länger, bis der Cursor erscheint, da infolge der Speichererweiterung nun ein größerer Speicherbereich geprüft wird.

RAMTOP (PRINT PEEK 16388 + 256 × PEEK 16389) liefert bei richtiger Funktion 23552. Falls gewünscht, lassen sich auch nur ein oder zwei Speicher-ICs einsetzen. Dabei ist auf die richtige Reihenfolge zu achten, da der Computer einen durchgehenden Speicherbereich benötigt. RAMTOP ist in diesem Fall 19456 bzw. 21504.

POKE 23556, Zahl

schaltet LED grün,

POKE 23557, Zahl

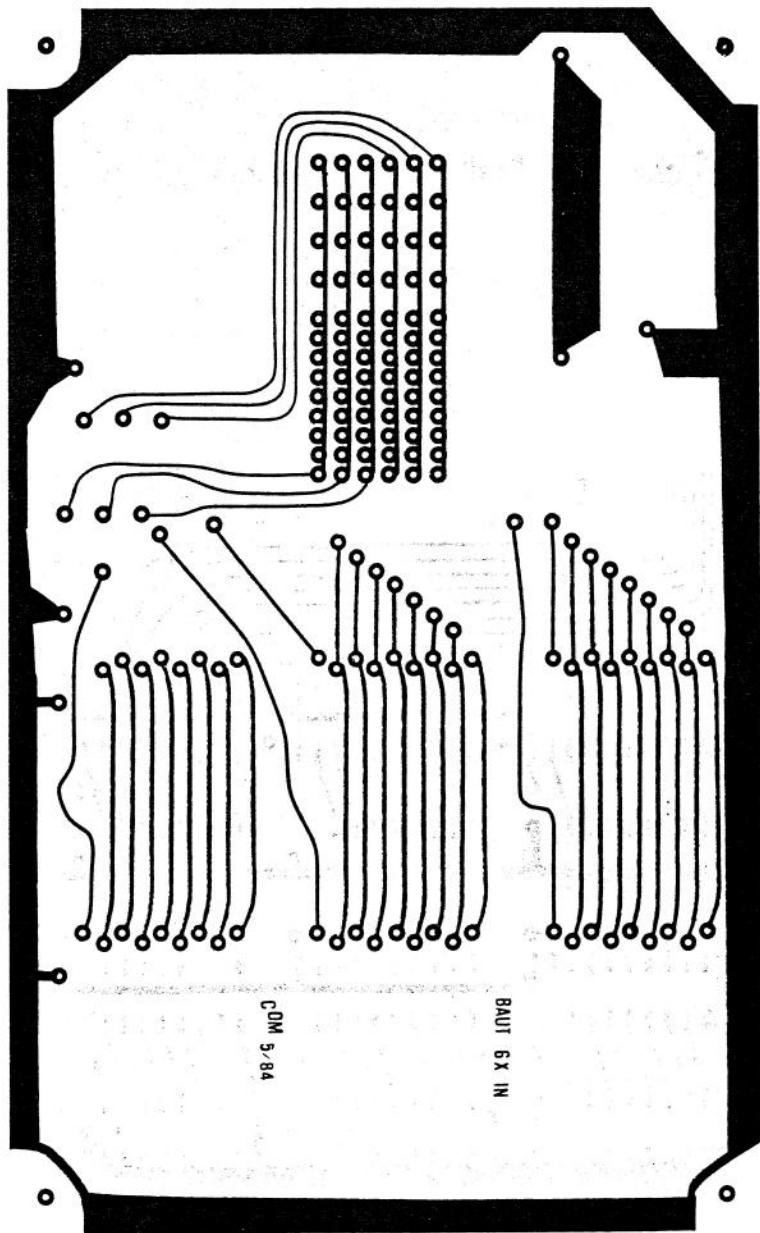

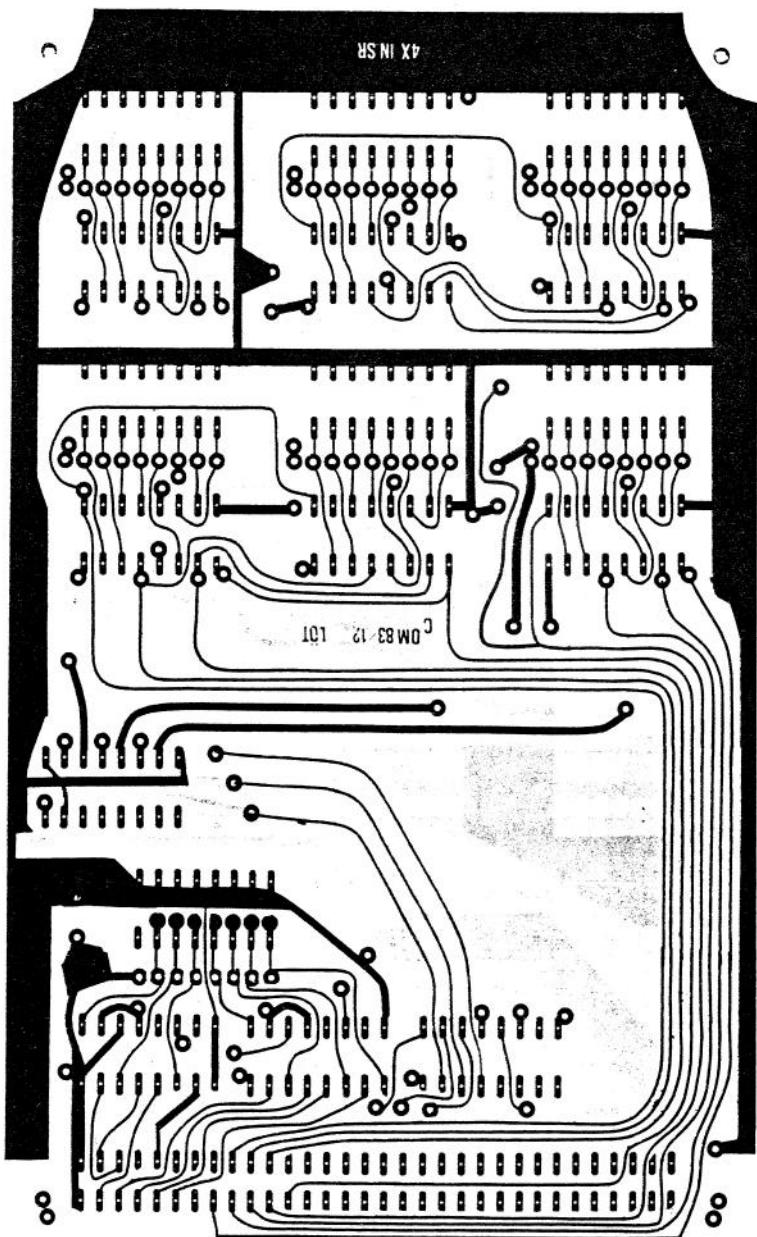

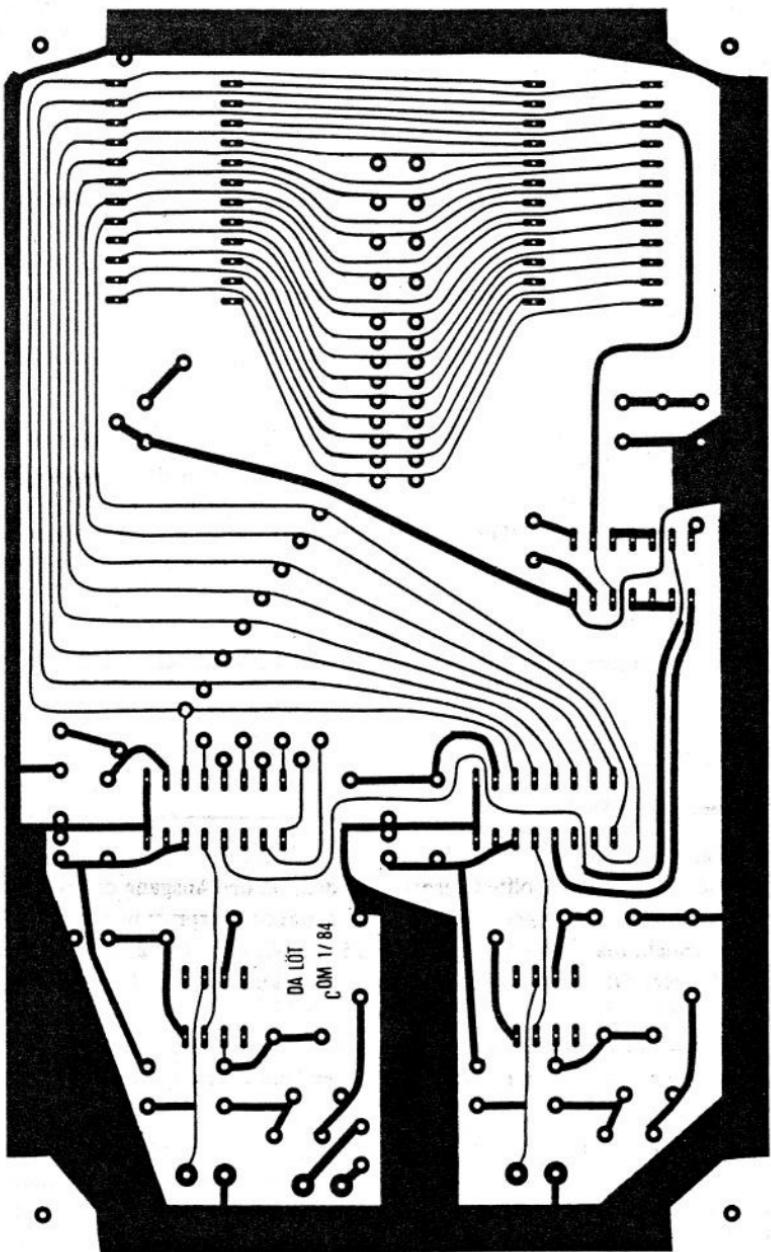

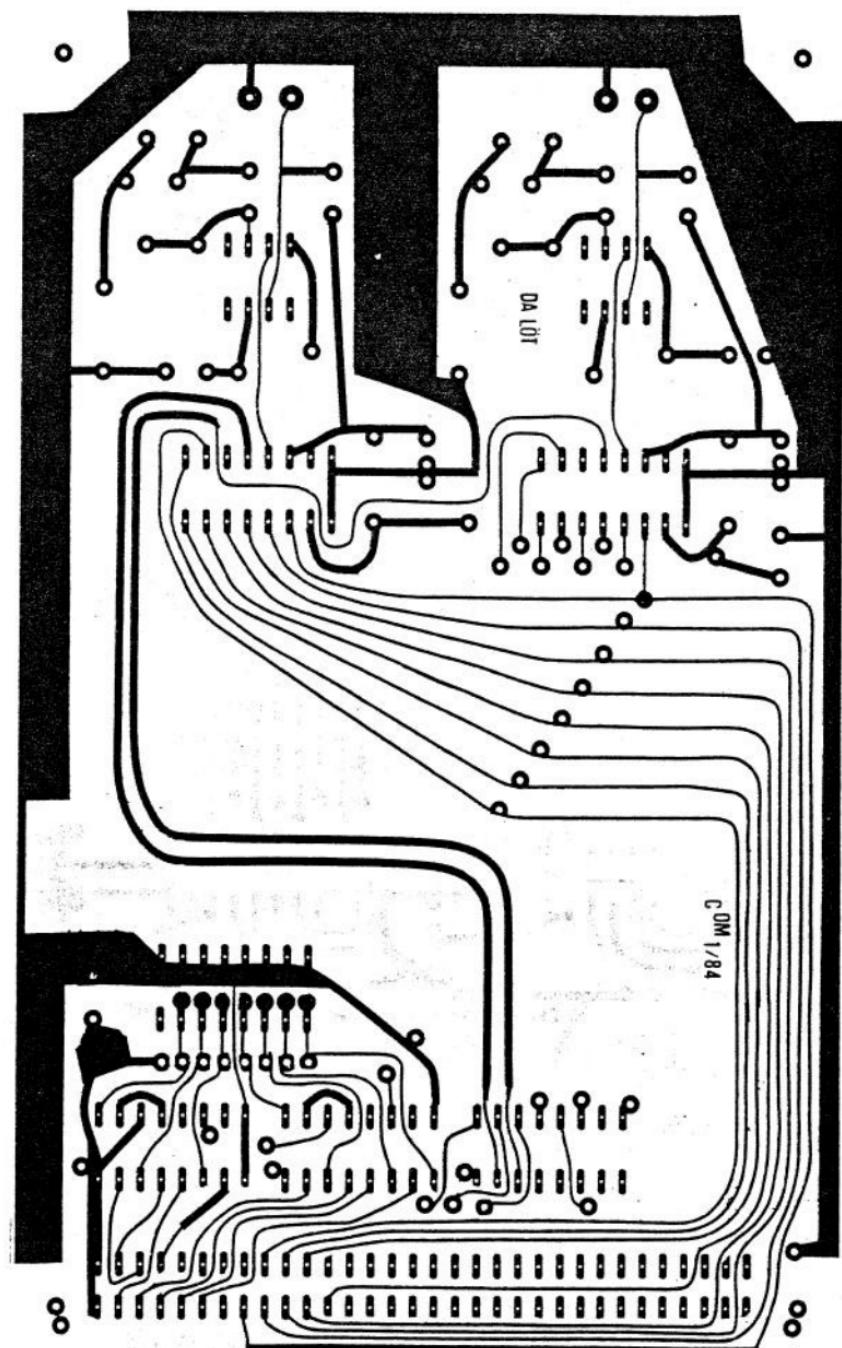

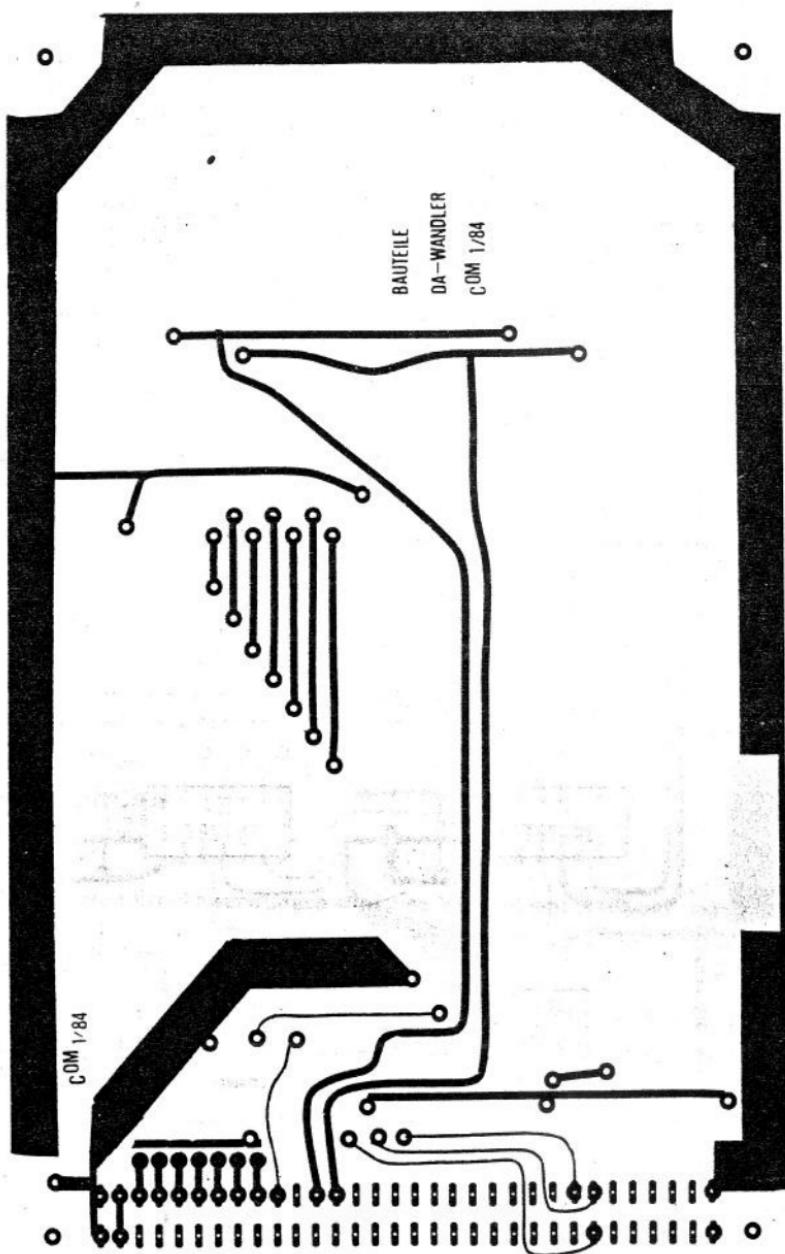

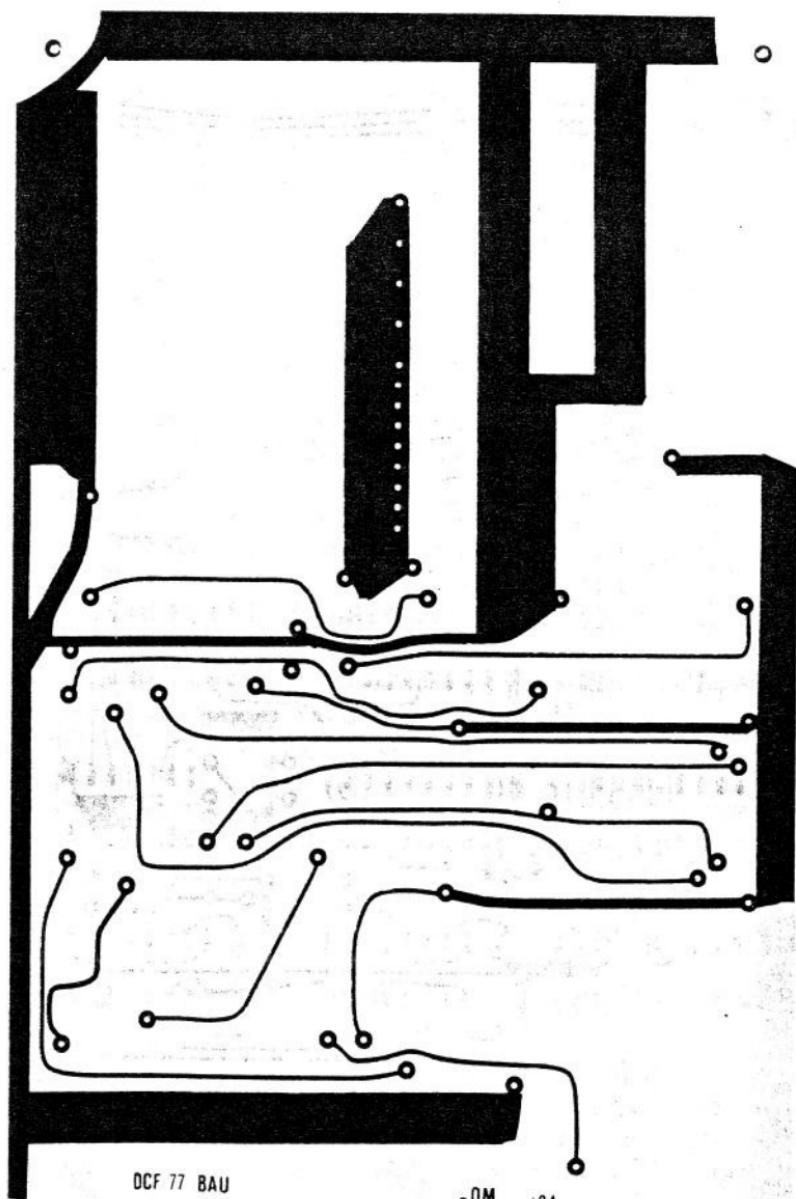

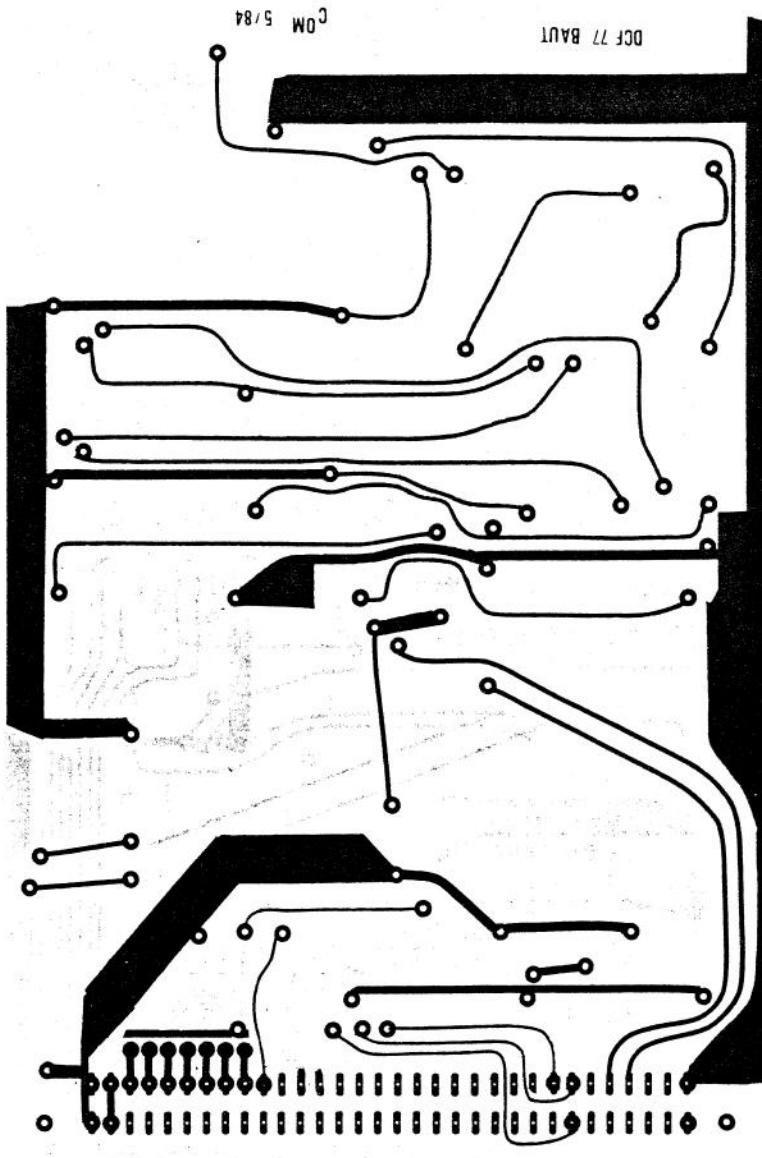

Abb. 2.9a Platinenlayout, Lötseite

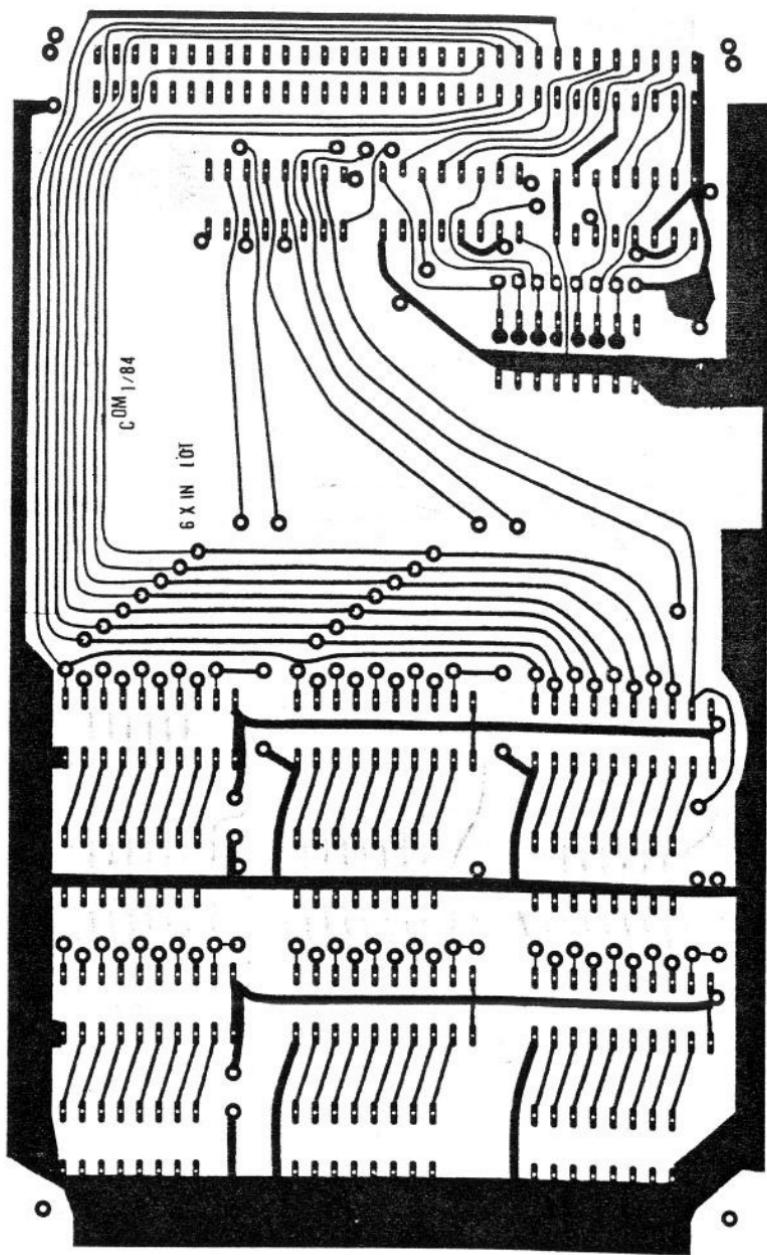

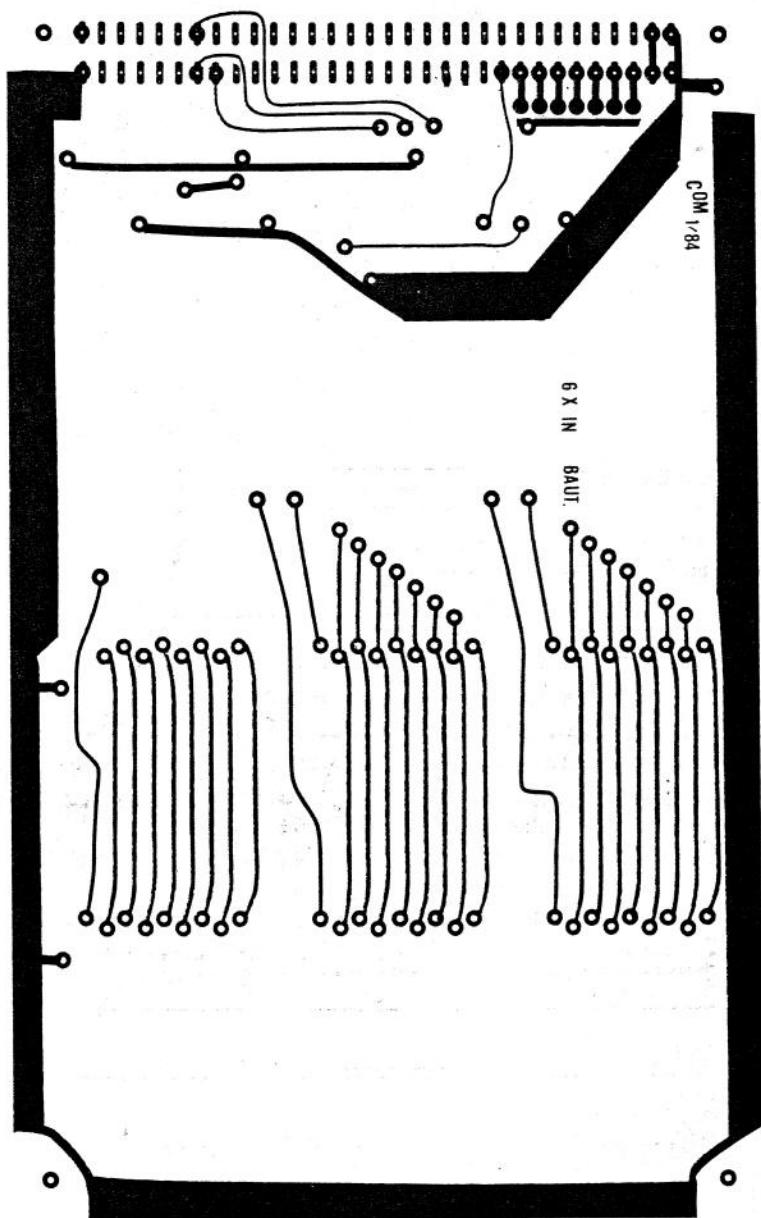

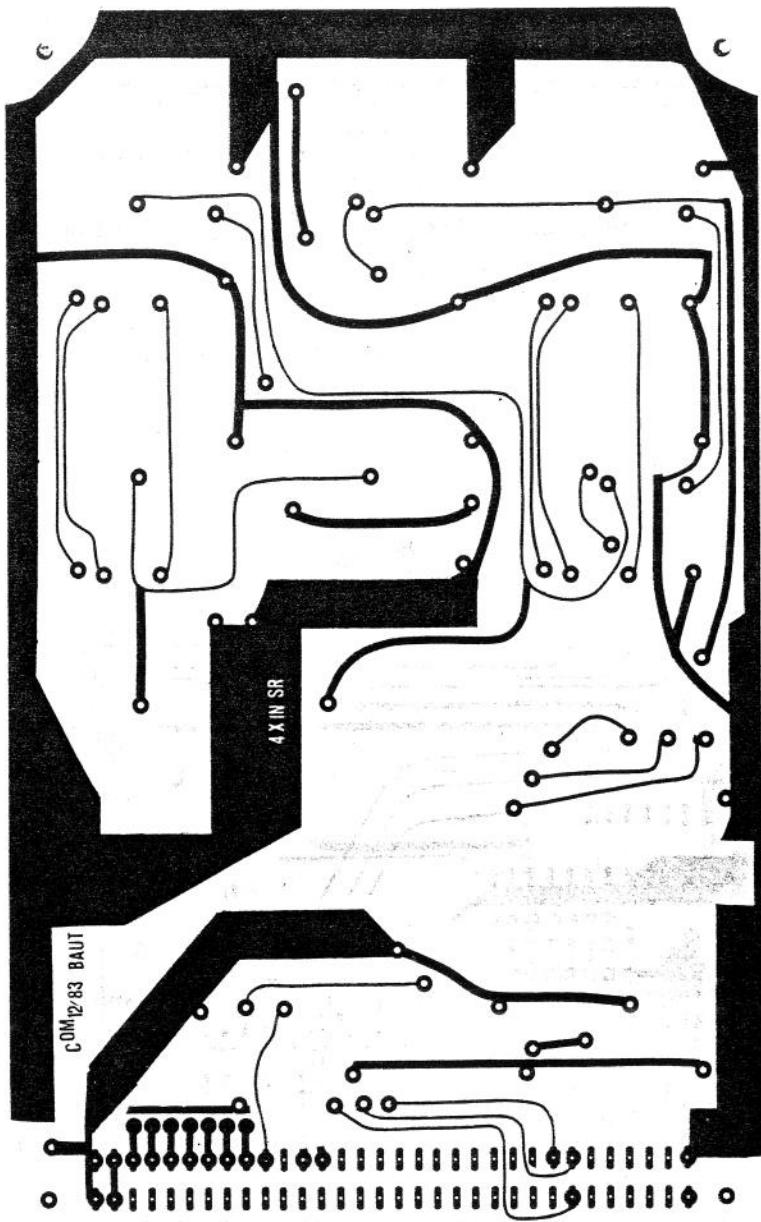

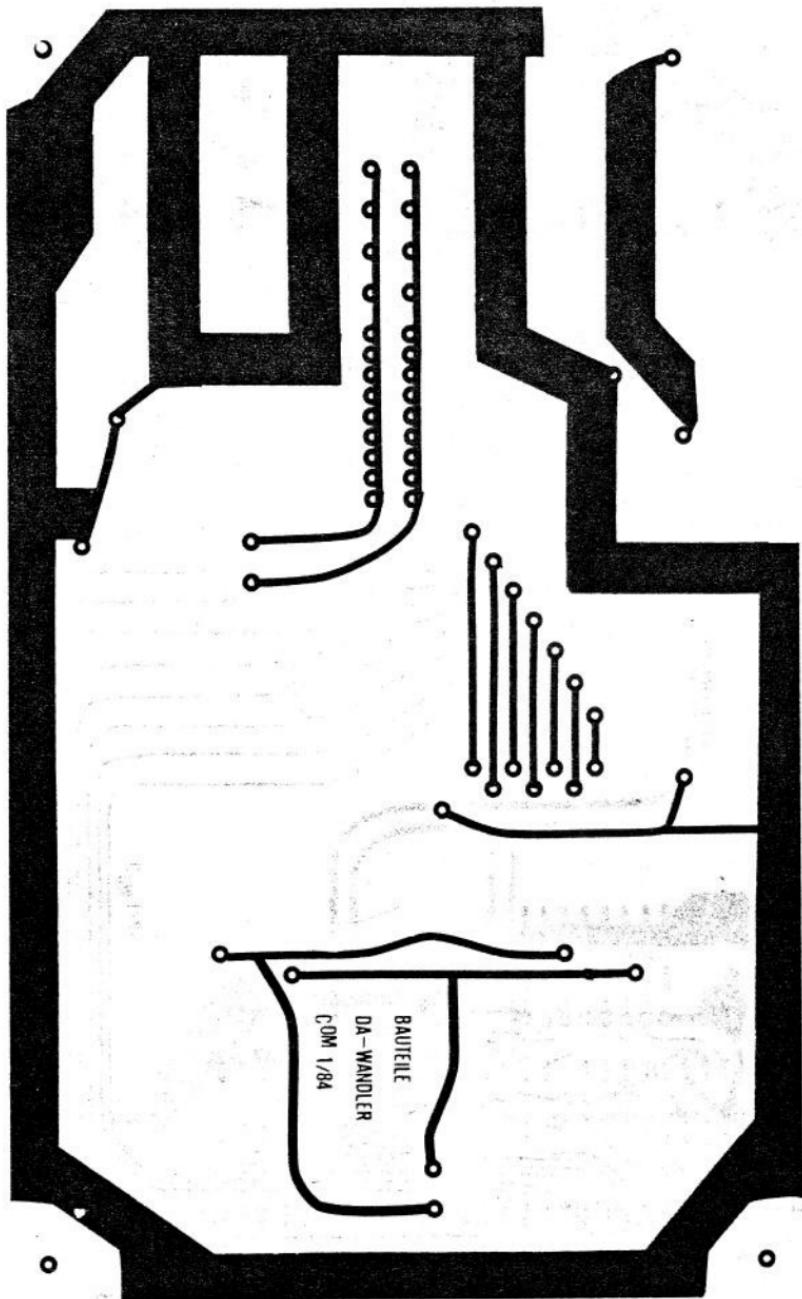

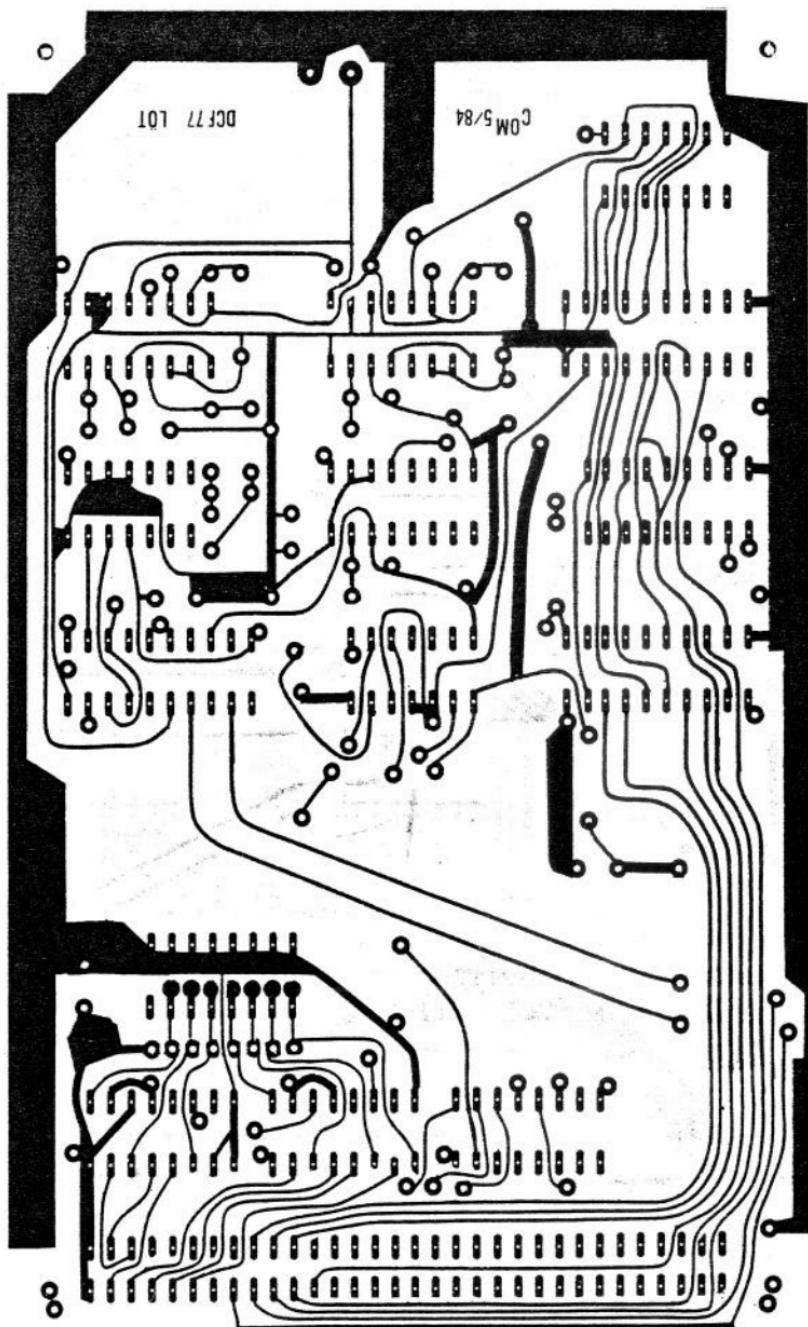

Abb. 2.9b Platinenlayout, Bestückungsseite

Abb. 2.10 Bestückungsplan (Blick auf die Bauteileseite)

**Stückliste der Grundplatine I**

|               |                                                                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC1, 2, 3, 12 | 4 x 74LS245                                                                                                                                                                                                        |

| IC5, 6, 7     | 3 x HM 6116LP-3                                                                                                                                                                                                    |

| IC10          | 1 x 74LS02                                                                                                                                                                                                         |

| IC9           | 1 x 74LS154                                                                                                                                                                                                        |

| IC4           | 1 x 74LS138                                                                                                                                                                                                        |

| IC11          | 1 x 74LS373                                                                                                                                                                                                        |

| IC8           | 1 x 7400N (keine LS-Version, da höherer Ausgangsstrom<br>für den Lautsprecher)<br>1 x 7805 (Spannungsregler 5V)<br>1 x LED rot 3 mm<br>8 x Anreih-LED rot (für OUT-Kontrolle)                                      |

| D1            | 1 x 4148 (o. ä. Si-Diode)                                                                                                                                                                                          |

| D2 ... D11    | 10 x AA 116 (o. ä. Ge-Diode)                                                                                                                                                                                       |

| R1 ... R3     | 3 x 22 kΩ                                                                                                                                                                                                          |

| R4 ... R5     | 2 x 1 kΩ                                                                                                                                                                                                           |

| R6 ... R8     | 3 x 470 Ω                                                                                                                                                                                                          |

| C1            | 1 x 470 μF                                                                                                                                                                                                         |

| C2 ... C6     | 5 x 22 nF                                                                                                                                                                                                          |

| C7 ... C8     | 2 x 150 nF                                                                                                                                                                                                         |

| Sp            | 1 x Lautsprecher 50 Ω (geeignet auch Postkapsel 32 Ω)<br>1 x Steckerleiste 2 x 23polig, Raster 2,54 mm<br>1 x DIL-Schalter 8polig<br>1 x DIL-Stecker 16polig<br>5 x Stecksockel 24polig<br>5 x Stecksockel 20polig |

|               | 3 x Stecksockel 16polig<br>2 x Stecksockel 14polig<br>Kleinmaterial (Steckstifte)                                                                                                                                  |

LED rot ein (Zahl kann zwischen 0 und 255 liegen). Ein an den Lautsprecherausgang angeschlossener Hörer gibt dabei jedesmal ein Klickgeräusch ab.

Um den IN-Port zu testen, wird ein 8poliger DIL-Schalter in den Sockel DIL3 gesteckt. PRINT PEEK 23558 liefert den Dezimalwert der eingestellten Binärkombination.

Zur Überprüfung des OUT-Ports (DIL2) sind acht Anreih-LEDS geeignet, die zusammen mit den erforderlichen Vorwiderständen in einen 16poligen DIL-Stecker gelötet werden (Abb. 2.11). Mit POKE 23558, Zahl leuchten die LEDs gemäß dem Binärwert der eingegebenen Zahl.

Abb. 2.11 DIL-Stecker mit LEDs für OUT-Port

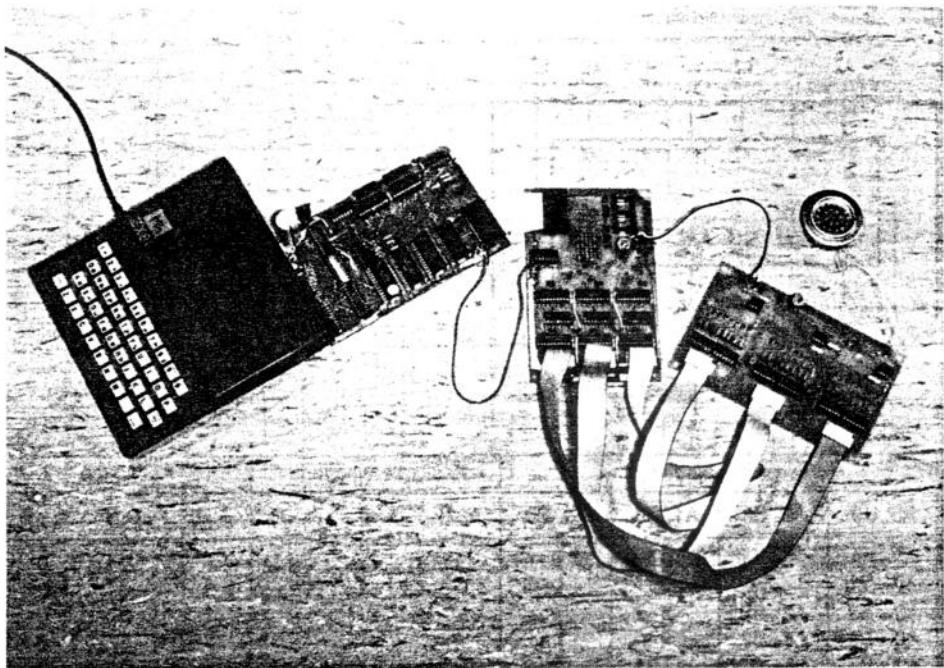

Abb. 2.12 Grundplatine I zusammen mit dem Sechsach-OUT-Port am ZX 81. Daran angeschlossen ist die Tongenerator-Platine (C-Umschaltung).

Damit ist die Grundplatine I einsatzbereit. Anwendungen finden sich thematisch aufgegliedert an anderer Stelle in diesem Buch. Abb. 2.12 zeigt die Grundplatine I im Einsatz mit dem ZX 81.

## 2.3 Grundplatine II (großes System)

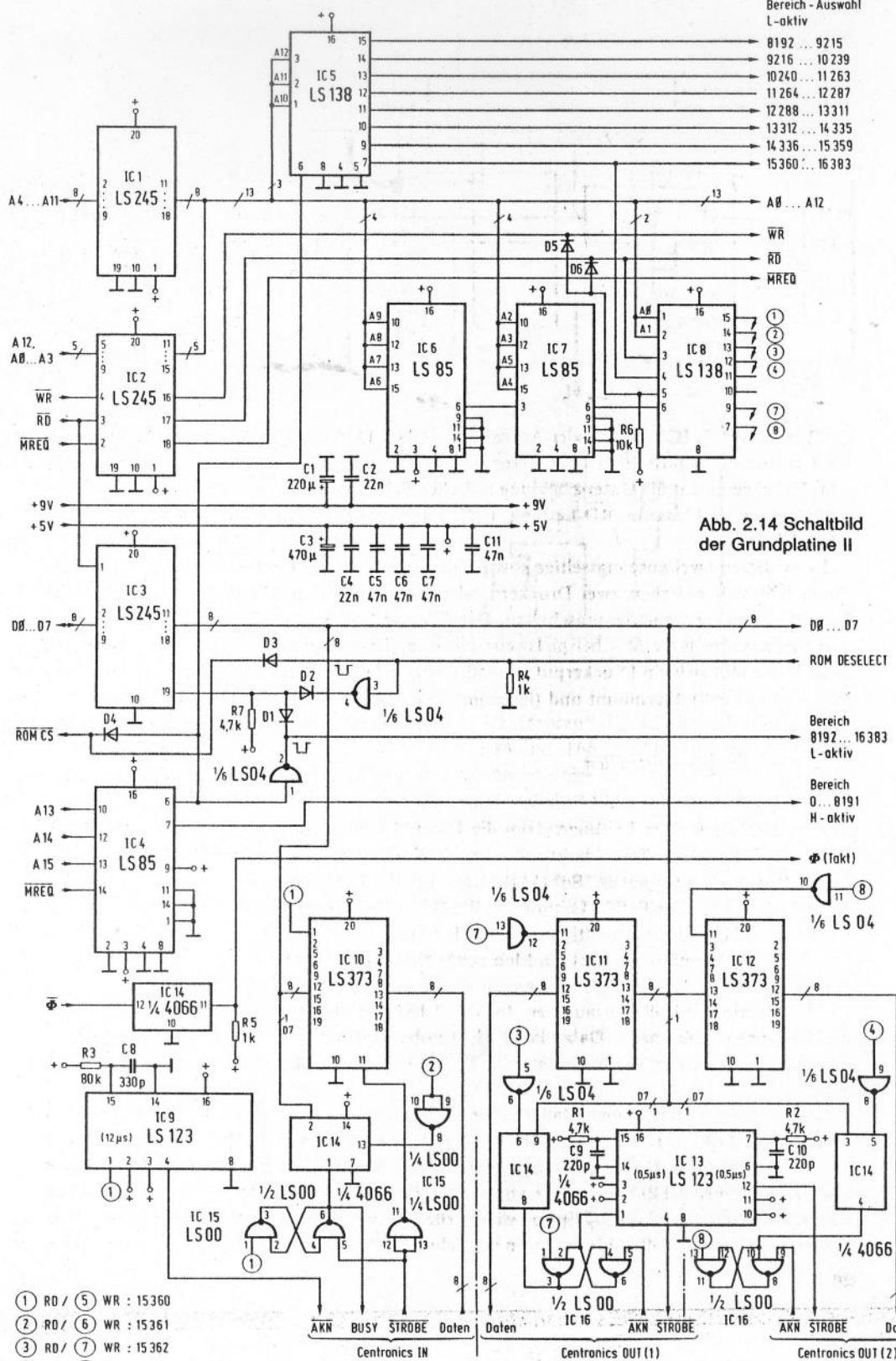

### 2.3.1 Konzeption und Adreßdekodierung

Aus der Speicherorganisation des ZX 81 (Abb. 2.1) war zu erkennen, daß das BASIC-ROM im Adressbereich 8192 ... 16383 doppelt erscheint. Natürlich ist dieses „Geister-ROM“ völlig überflüssig und kann durch ein H-Signal auf der Leitung ROMCS ausgeblendet werden. Dadurch steht ein 8 KByte großer Adressbereich zusätzlich zur Verfügung. Es liegt nahe, ihn für Erweiterungsschaltungen zu nützen. Außerdem kann in diesem Bereich auch zusätzliche Speicherkapazität zur Verfügung gestellt werden, die allerdings nicht für BASIC-Programme geeignet ist. Maschinenprogramme sind hier dagegen sehr gut aufgehoben, da sie den BASIC-Speicher nicht verkleinern und vom System auch nicht überschrieben werden können.

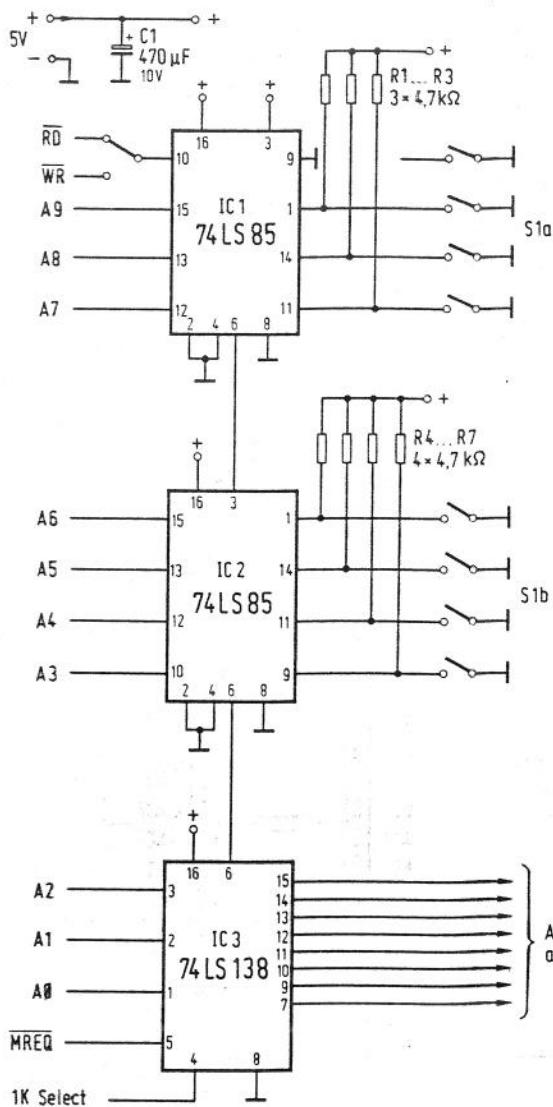

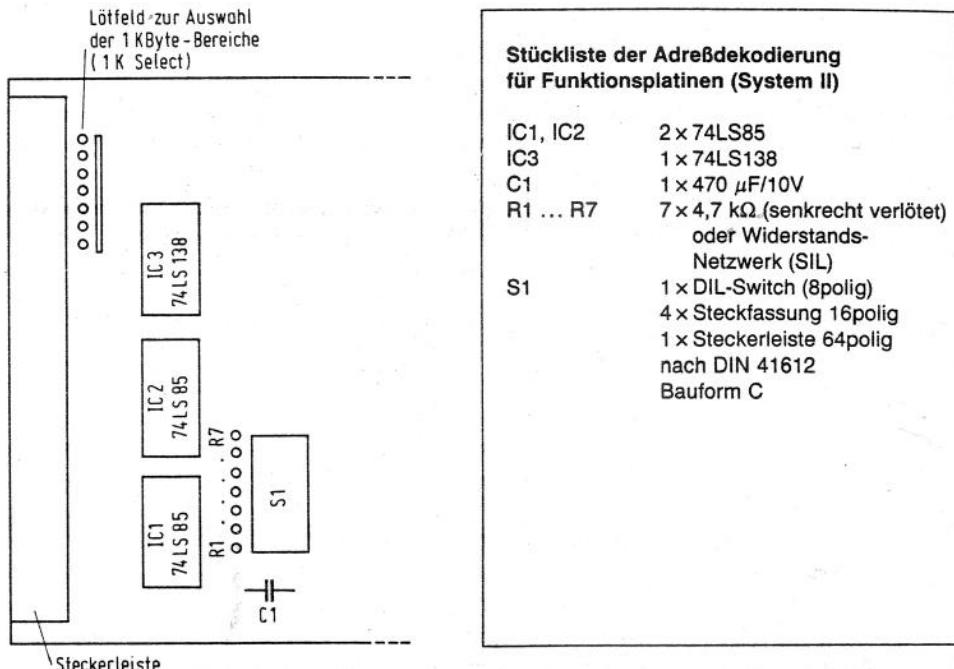

Um keine Probleme mit unvollständiger Adreßdekodierung zu bekommen, müssen alle 16 Adreßleitungen herangezogen werden. In Sonderfällen läßt sich eine Adreßdekodierung einfach durch die Verwendung von NAND-Gattern erreichen. Allerdings können dann beliebige Adressen nicht ohne größeren Aufwand benutzt werden.

Hierfür besser geeignet ist der 4-Bit-Comparator 74LS85 (Abb. 2.13). Ein an den Eingängen A0 ... A3 angelegtes 4-Bit-Wort (A) wird mit einem zweiten an B0 ... B3 (B) verglichen.

Bereich - Auswahl

L-aktiv

8192 ... 9215

9216 ... 10239

10240 ... 11263

11264 ... 12287

12288 ... 13311

13312 ... 14335

14336 ... 15359

15360 ... 16383

Abb. 2.14 Schaltbild

der Grundplatine II

(1) RD / (5) WR : 15360

(2) RD / (6) WR : 15361

(3) RD / (7) WR : 15362

(4) RD / (8) WR : 15363

Centronics IN

Centronics OUT(1)

Centronics OUT(2)

## 2 Grundplatinen

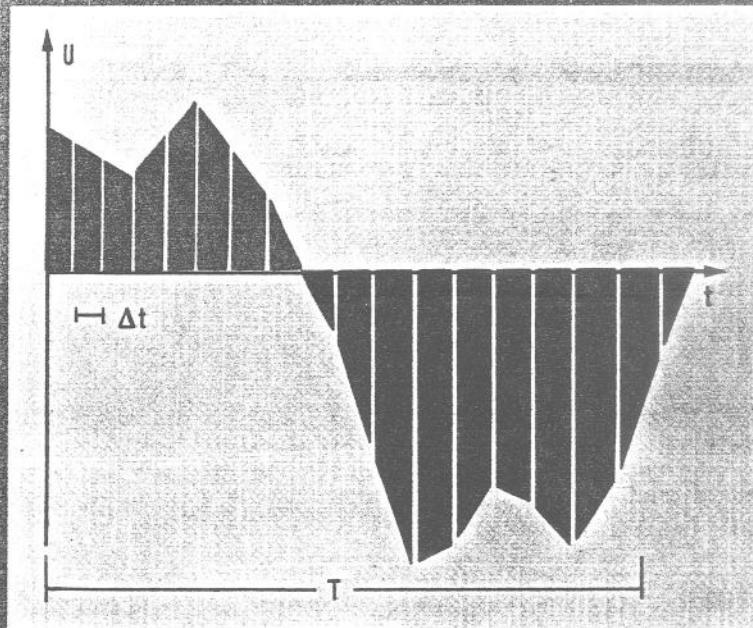

Abb. 2.15 Signale bei einer Centronics-Parallelschnittstelle

Über IC6, IC7, IC8 werden vier Adressen zwischen 15360 und 15363 festgelegt, auf denen die Centronics-Schnittstellen bzw. deren Status-Informationen angesprochen werden können. Dabei geschieht die Unterscheidung zwischen Schreib- und Leseadresse über die an Pin 3 von IC8 angeschlossene RD-Leitung (vgl. auch das Logikdiagramm des 74LS138 in Abb. 2.3).

Es existieren zwei ausgangsseitige sowie eine eingangsseitige Centronics-Schnittstelle. Dadurch lässt sich zwischen zwei Druckern oder ähnlichen Peripherie-Geräten mit paralleler Schnittstelle softwaremäßig umschalten. Der Centronics-Eingang erlaubt es, parallele Daten von einem anderen Gerät - beispielsweise einem anderen Computer - zu übernehmen. Auf diese Weise lässt sich ein Druckerpuffer realisieren, indem der ZX 81 die Druckerdaten dieses Rechners (schnell) übernimmt und (langsam) an einen Drucker weiterreicht.

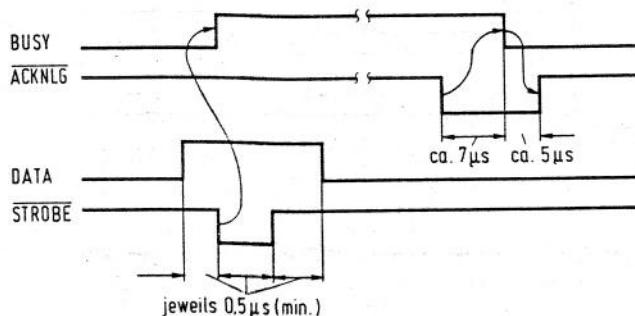

### 2.3.2 Centronics-Schnittstellen

Centronics-Schnittstellen sind Parallelschnittstellen mit einer Datenbreite von 8 Bit. Zusätzlich besitzen sie weitere Leitungen, um die Datenübertragung zu kontrollieren (Abb. 2.15). Wenn die Daten an der Schnittstelle zur Verfügung stehen (Datenausgabe), wird der STROBE-Impuls ausgegeben. Sobald der Drucker die Daten übernimmt, signalisiert er das durch H-Pegel auf der BUSY-Leitung. Ist die Datenübernahme beendet, gibt die ACKNLG-Leitung (acknowledge - Bestätigung) einen L-Impuls ab. Nun können erneut Daten in die Schnittstelle eingeschrieben werden. Man nennt ein solches Verfahren „handshaking“ (Händeschütteln). Für den Centronics-Eingang sind die Verhältnisse sinngemäß, nur daß ZX 81 und Peripherie ihre Rolle vertauschen. In Abb. 2.15 ist zusätzlich das Zeitverhalten der einzelnen Leitungen eingetragen. Dabei ist es nicht unbedingt nötig, daß BUSY- und ACKNLG-Signal gemeinsam zur Verfügung stehen. So verwenden die Ausgänge nur das ACKNLG-Signal.

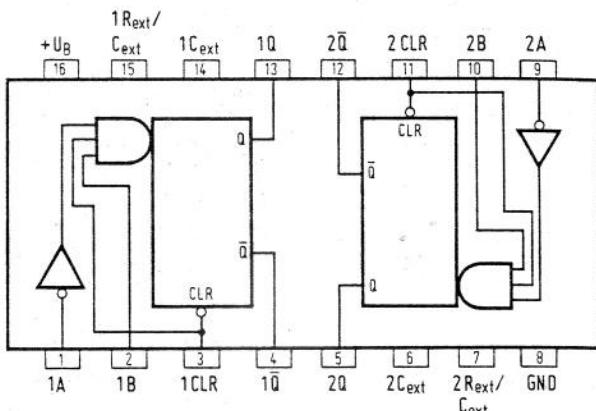

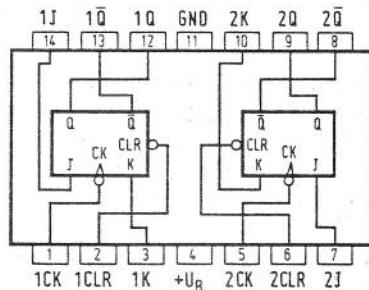

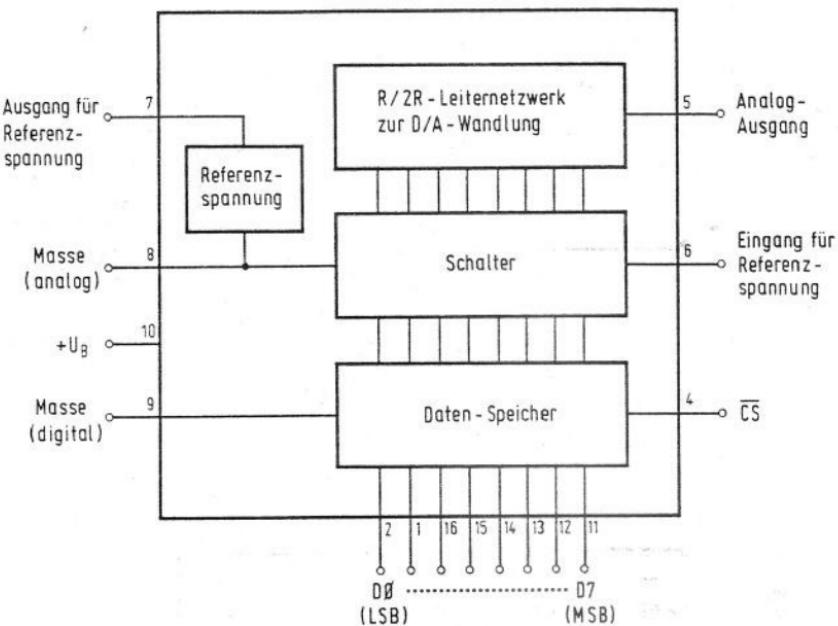

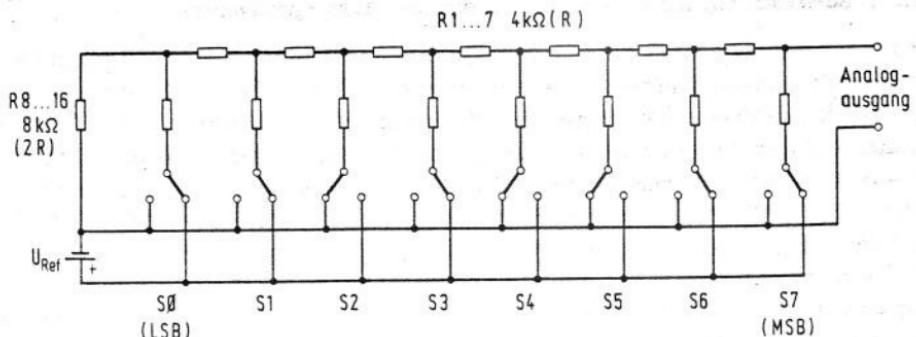

In Abb. 2.14 ist zu erkennen, daß die Ausgangsdaten in ein 8-bit-Latch geschrieben werden (74LS373, IC11 bzw. IC12, angesprochen über (7) bzw. (8) von IC8). Dabei wird gleichzeitig über ein SR-Flipflop (IC16) der monostabile Multivibrator (1/2 IC13, 74LS123) getriggert und erzeugt einen STROBE-Impuls von 0,5 µs Dauer. Wenn der Drucker die Datenübernahme bestätigt, wird das SR-Flipflop wieder rückgesetzt. Sein Zustand wird über einen Analogschalter (IC14, 1/4 4066) beim Lesen der Schnittstellenadresse auf die Datenleitung D7 ge-

Abb. 2.16 2-fach-Monovibrator

74LS123

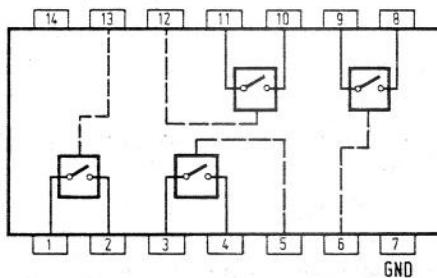

Abb. 2.17 4-fach-Analogschalter 4066

| Schaltzustand | Schaltspannung |

|---------------|----------------|

| Ein           | H (+5V)        |

| Aus           | L (0V)         |

legt. Durch Abfragen dieses Status-Bits kann ein „Überfahren“ der Schnittstelle infolge einer zu hohen Datenrate vermieden werden. In Abb. 2.16 und Abb. 2.17 sind die Anschlußbelegungen des Monovibrators 74LS123 bzw. des Analogschalters 4066 aufgeführt.

Das Zeitverhalten der hier auftretenden Signale entspricht nicht ganz exakt den vorher beschriebenen Konventionen. Im praktischen Betrieb ergaben sich aber keinerlei Probleme.

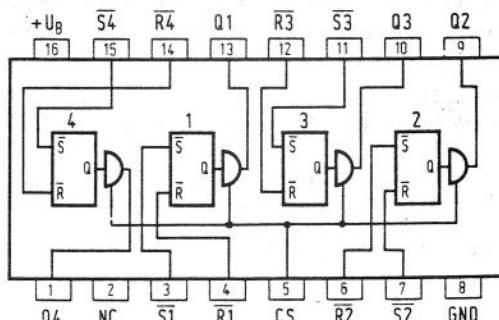

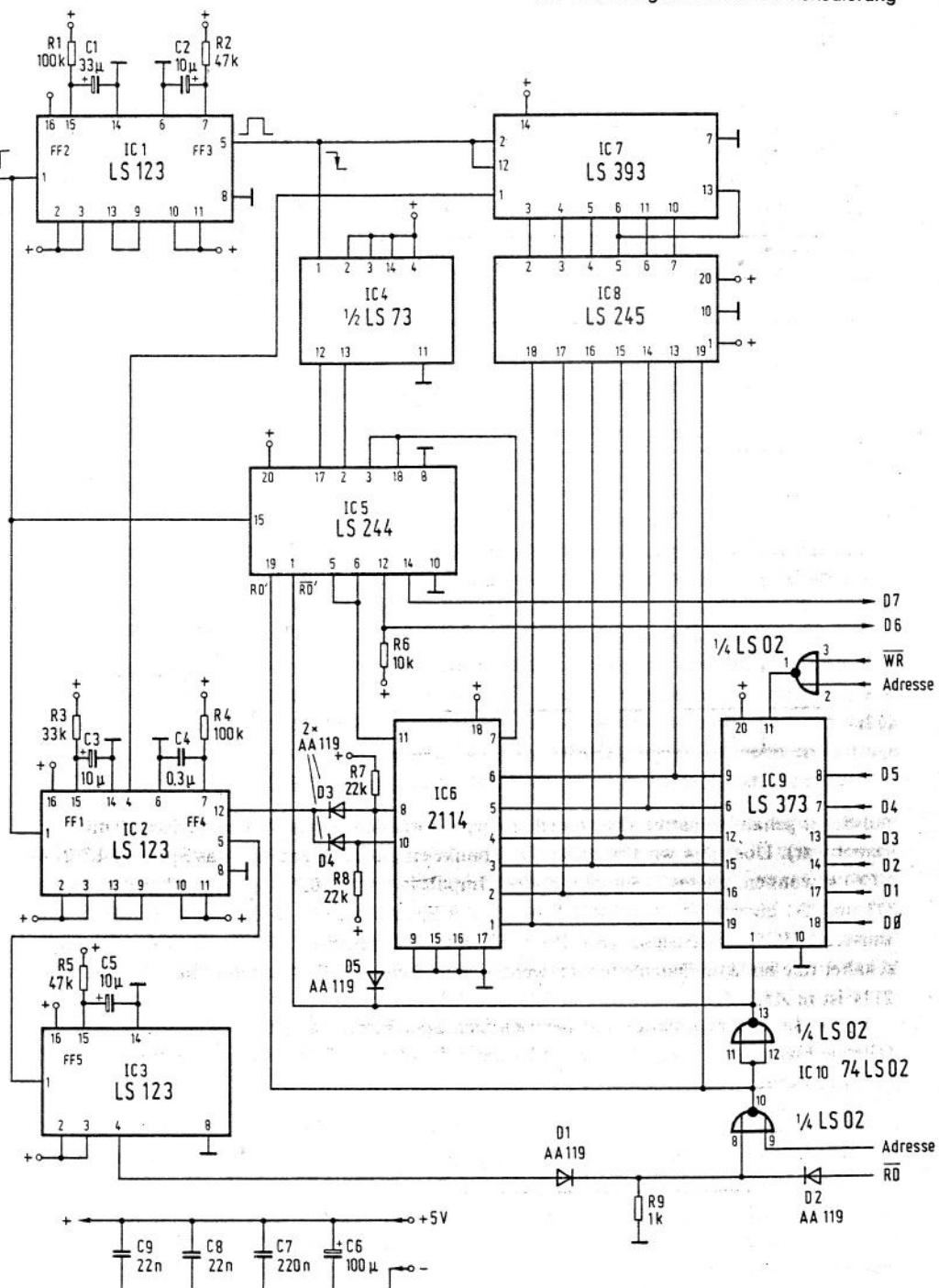

Bei der Eingangsschnittstelle liegen die Verhältnisse entsprechend umgekehrt. Die von außen kommenden Daten liegen am Eingang von IC10 (74LS373) an, und werden mit dem STROBE-Signal abgespeichert. Dabei wird gleichzeitig ein SR-Flipflop (IC15) gesetzt. Der Zustand dieses Flipflops wird beim Lesen der entsprechenden Statusadresse über einen Analogschalter (IC14, 1/4 4066) ebenfalls auf die Datenleitung D7 gelegt. Werden die Daten aus dem Latch ausgelesen, erfolgt gleichzeitig ein Rücksetzen des SR-Flipflops und das Auslösen des ACKNLG-Signals (IC9, 1/2 74LS123).