ENCICLOPEDIA PRACTICA DE LA

# INFORMATICA APLICADA

Cuando se trabaja con un ordenador, lo único que puede apreciarse, a simple vista, es una especie de caja negra que, misteriosamente, acepta una serie de instrucciones.

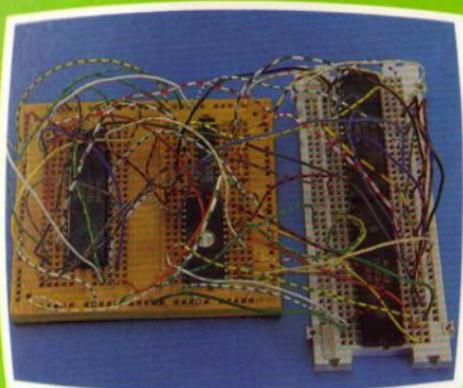

En realidad, un ordenador es una máquina capaz de recibir, transformar, almacenar y suministrar datos. En este libro se construye un pequeño ordenador, capaz de realizar dichas funciones, a partir de un microprocesador. Podrá observar de qué partes se compone el ordenador y cómo conectarlas entre sí. Además, podrá adentrarse en el mundo del «hardware» utilizando, por ejemplo, como un temporizador para controlar cualquier electrodoméstico casero.

Por otra parte, se ha pensado en la construcción de un ordenador dinámico. A partir del diseño básico, podrá ampliarlo con el único límite que impone la propia imaginación.

Cómo construir su propio ordenador

15

## Cómo construir su propio ordenador

AIA

SINCLAIR

AMSTRAD

CHAMODORF

IBM

EDICIONES SIGLO CULTURAL

*Una publicación de*

**EDICIONES SIGLO CULTURAL, S.A.**

Director-editor:

**RICARDO ESPAÑOL CRESPO.**

Gerente:

**ANTONIO G. CUERPO.**

Directora de producción:

**MARÍA LUISA SUÁREZ PÉREZ.**

Directores de la colección:

**MANUEL ALFONSECA**, Doctor Ingeniero de Telecomunicación

y Licenciado en Informática

**JOSE ARTECHE**, Ingeniero de Telecomunicación

Diseño y maquetación:

**BRAVO-LOFISH.**

Dibujos:

**JOSÉ OCHOA Y ANTONIO PERERA.**

**Tomo XV. Cómo construir su propio ordenador**

AULA DE INFORMATICA APLICADA

**JOAQUÍN SALVACHUÁ**, Diplomado de Telecomunicación

**JOSE LUIS TODO**, Diplomado de Telecomunicación

**FERNANDO SUERO**, Diplomado de Telecomunicación

Ediciones Siglo Cultural, S.A.

Dirección, redacción y administración:

Sor Angela de la Cruz, 24-7.<sup>o</sup> G. Teléf. 279 40 36. 28020 Madrid.

Publicidad:

Gofar Publicidad, S.A. Benito de Castro, 12 bis. 28028 Madrid.

Distribución en España:

COEDIS, S.A. Valencia, 245. Teléf. 215 70 97. 08007 Barcelona.

Delegación en Madrid: Serrano, 165. Teléf. 411 11 48.

Distribución en Ecuador: Muñoz Hnos.

Distribución en Perú: DISELPESA.

Distribución en Chile: Alfa Ltda.

Importador exclusivo Cono Sur:

CADE, S.R.L. Pasaje Sud América, 1532. Teléf.: 21 24 64.

Buenos Aires - 1.290. Argentina.

Todos los derechos reservados. Este libro no puede ser, en parte o totalmente, reproducido, memorizado en sistemas de archivo, o transmitido en cualquier forma o medio, electrónico, mecánico, fotocopia o cualquier otro, sin la previa autorización del editor.

ISBN del tomo: 84-7688-053-7.

ISBN de la obra: 84-7688-018-9.

Fotocomposición:

ARTECOMP, S.A. Albarracín, 50. 28037 Madrid.

Imprime:

MATEU CROMO. Pinto (Madrid).

© Ediciones Siglo Cultural, S. A., 1986

Depósito legal: M-1132-1987.

Printed in Spain - Impreso en España.

Suscripciones y números atrasados:

Ediciones Siglo Cultural, S.A.

Sor Angela de la Cruz, 24-7.<sup>o</sup> G. Teléf. 279 40 36. 28020 Madrid

Octubre, 1986.

P.V.P. Canarias: 365.

# ÍNDICE

|                                                                        |                             |           |

|------------------------------------------------------------------------|-----------------------------|-----------|

| <b>1</b>                                                               | <b>Partes del ordenador</b> | <b>5</b>  |

| <b>2</b>                                                               | <b>El microprocesador</b>   | <b>9</b>  |

| <b>3</b>                                                               | <b>La memoria</b>           | <b>25</b> |

| <b>4</b>                                                               | <b>La entrada-salida</b>    | <b>31</b> |

| <b>5</b>                                                               | <b>Software</b>             | <b>57</b> |

| <b>6</b>                                                               | <b>Aplicaciones</b>         | <b>61</b> |

| Apéndice A: Sistemas de numeración y su representación en el ordenador |                             | 65        |

| Apéndice B: Consejos a la hora de montar el circuito                   |                             | 71        |

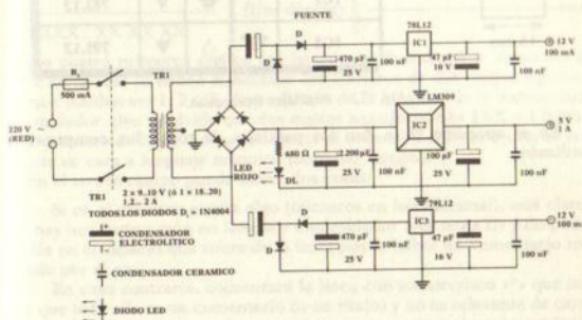

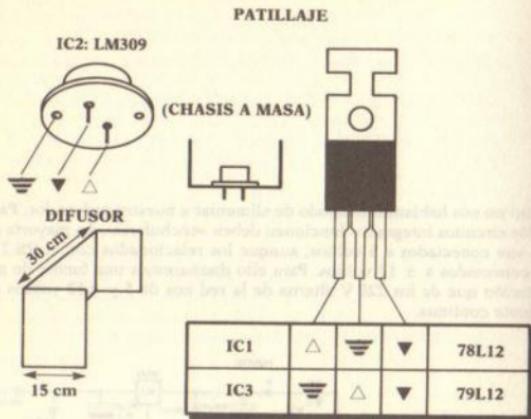

| Apéndice C: Fuente de alimentación                                     |                             | 75        |

| Apéndice D: Listado fuente del programa monitor                        |                             | 77        |

| Apéndice E: Listado hexadecimal del programa monitor                   |                             | 91        |

| Apéndice F: Códigos de programación                                    |                             | 97        |

| Apéndice G: Patillaje de circuitos integrados                          |                             | 107       |

| Apéndice H: Bibliografía                                               |                             | 111       |

# V

AMOS A ver, paso a paso, cómo funciona un ordenador; de qué partes se compone y cómo se conectan entre sí. A partir de estas ideas generales veamos cómo llevarlas a la práctica con la construcción de un pequeño, pero versátil, microordenador.

Todo ordenador tiene dos partes bien diferenciadas: el hardware y el software. El hardware es el conjunto de circuitos que componen físicamente el ordenador. El software son los programas e instrucciones que indican a los circuitos qué funciones deberán realizar.

En este capítulo describiremos brevemente el hardware. Los ordenadores tienen tres partes básicas:

- La unidad central de procesos (CPU) o microprocesador.

- La memoria.

- La unidad de entrada-salida (I/O).

La CPU es el «cerebro» del ordenador. Es la que controla a las demás partes y la que realiza las operaciones.

La memoria es un almacén donde están guardados los datos y las instrucciones que la CPU debe utilizar y en ella almacena los resultados.

Con esto parece que tenemos todo lo necesario, pero no es así, ya que para que los resultados de las operaciones puedan ser útiles es necesario comunicarse con el exterior. De esta función se encarga la unidad de I/O. Se encarga de transmitir datos del ordenador al exterior (pantalla del ordenador, impresora, etc.) y del exterior al ordenador (teclado, cinta cassette, etc.).

\* Las iniciales corresponden a las palabras en inglés. (CPU = Central Processing Unit; I/O = Input/Output). A partir de ahora todas las iniciales se referirán a su escritura en inglés, ya que esta forma es la comúnmente aceptada.

Los programas que aparecen en este libro funcionan en los ordenadores:

IBM-PC, XT, AT y compatibles.

AMSTRAD-464, 664, 6128, 1512.

SINCLAIR-SPECTRUM 48 K, 128 K, PLUS, PLUS 2.

MSX-Todos los modelos.

COMMODORE-CBM 64 y CBM 128.

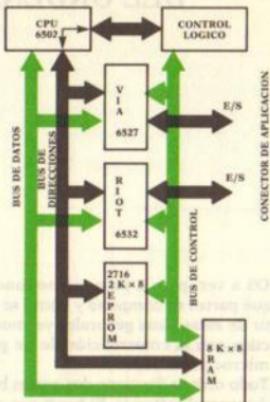

Fig. 1.1. Diagrama de bloques del ordenador.

El ordenador sólo trabaja con datos que le son comprensibles. Estos son bits, o dígitos binarios (para mayor información, ver el apéndice A). Cada bit sólo puede ser o un 1 o un 0. Pero como el ordenador no trata con números, esto se representará como 0 voltios, cuando se quiera representar un 0, y como 5 voltios cuando se quiera representar un 1. A los grupos de 8 bits se les conoce como bytes. Los microprocesadores llamados «de 8 bits» sólo pueden procesar al mismo tiempo un byte.

Como se observa en la figura 1.1, en el ordenador cada bloque está relacionado con los demás mediante una serie de líneas, o cables, conocidos como buses.

Existen tres buses: el de control, el de datos y el de direcciones.

El bus de control es el que se encarga de llevar desde la CPU a los demás bloques las instrucciones que éstos deben realizar.

El bus de datos es el que lleva la información, o datos, que los distintos bloques se comunican. El ancho de este bus (número de bits que se corresponde con el número de cables) es el de ancho de palabra = 1 byte.

El bus de direcciones da la dirección, como su nombre indica, adonde debe llevarse el dato. Está organizado como las direcciones de correos.

Por ejemplo, para que la CPU almacene un dato en la memoria debe enviar por el bus de control la señal de que quiere guardar el dato en la

memoria, el dato por el bus de datos, y en qué parte de la memoria quiere almacenarlo por el bus de direcciones. Del ancho del bus de direcciones dependerá el máximo de memoria que el ordenador puede utilizar.

Esta organización, o arquitectura, se conoce como arquitectura von Neumann, en honor del primero al que se le ocurrió. John von Neumann la aplicó en los años cuarenta a la construcción de los primeros ordenadores, y desde entonces no se han realizado realmente diferentes. Actual-

Fig. 1.2. Esquema general del ordenador.

mente se intenta buscar alguna que permita a varias CPUs realizar tareas cooperando entre ellas, pero no se ha encontrado ninguna de utilidad comparable.

Veamos ahora cómo se realizan estas ideas generales en la realización de nuestro ordenador.

Como CPU vamos a usar el microprocesador 6502. Este es un «chip», o circuito integrado, que lleva todo lo necesario para componer una CPU. Hasta hace poco tiempo una CPU ocupaba el tamaño de un televisor, aproximadamente.

La memoria está dividida en dos partes: la RAM y la ROM. La diferencia está en que en la RAM pueden leerse y escribirse datos, mientras en la ROM sólo leerse. La segunda diferencia es que si apagamos el ordenador, los datos almacenados en la RAM desaparecerán, mientras los existentes en la ROM permanecerán; por ello, los programas que permitirán realizar operaciones estarán en la ROM y los datos en la RAM.

De las comunicaciones se encargarán dos chips especializados, la VIA y la RIOT. Estos controlarán las comunicaciones con un teclado y un display (como en una calculadora). No se ha incluido una «Televisión», o CRT, por complicar demasiado el diseño.

Por último, para permitir comunicarse con otros ordenadores se han incluido dos tipos de conexiones estándar: RS-232 y CENTRONICS.

Una vez vistas las partes principales de nuestro ordenador veremos cada una más detalladamente en los siguientes capítulos.

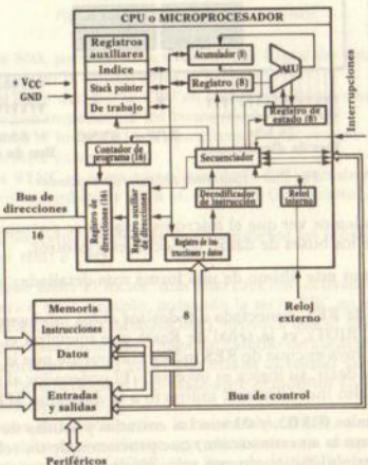

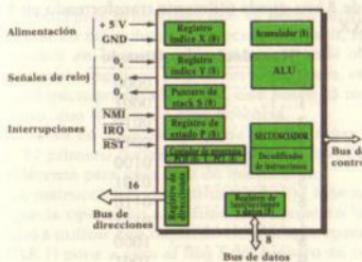

En la figura puede verse el esquema de un microprocesador genérico.

## ARQUITECTURA DEL 6502

Este microprocesador, de marca y modelo diferentes, posee un lenguaje máquina distinto, adecuado a las posibilidades que el chip ofrece.

En la figura puede verse el esquema de un microprocesador genérico.

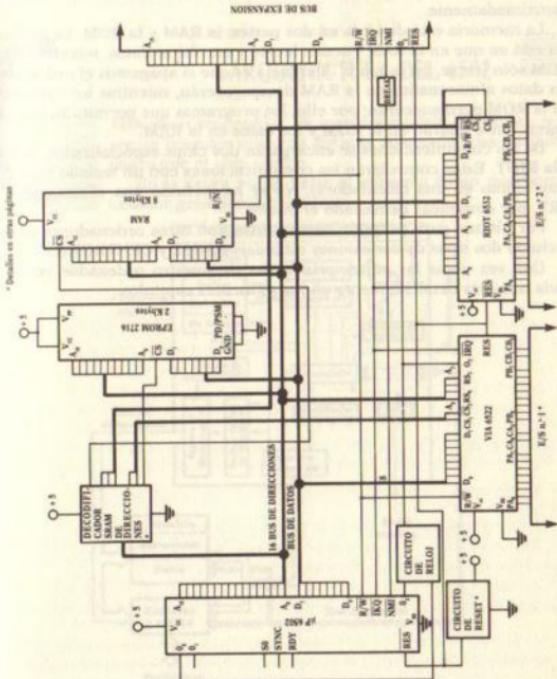

Fig. 2.1. Esquema del ordenador.

En nuestro ordenador utilizaremos el microprocesador 6502, de la marca Rockwell.

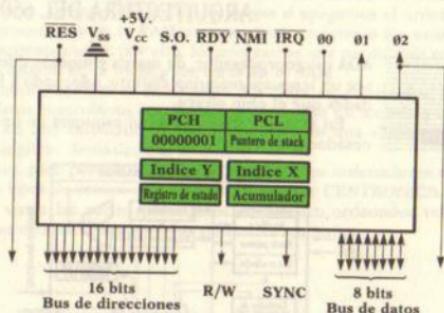

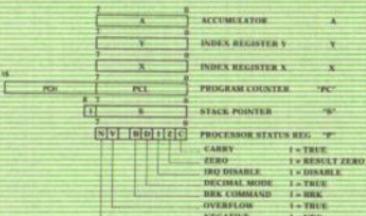

Este es un microprocesador de 8 bits, es decir, su bus de datos puede manejar simultáneamente palabras de 8 bits. Puede manejar hasta 64 Kbytes de memoria (su bus de direcciones es de 16 bits:  $2^{16}$  bits = 65536 bytes = 64 Kbytes). Y la frecuencia de reloj es de 1 MHz (en la versión que utilizaremos). En la siguiente gráfica podemos observar la estructura interna del microprocesador 6502 desde el punto de vista del programador (arquitectura software).

Fig. 2.2. Esquema del microprocesador.

En ella podemos ver que el microprocesador se comunica con el exterior mediante los buses de datos, direcciones y control.

Describamos este último de una forma más detallada:

- La patilla RES, conectada a todos los chips inteligentes (microprocesador, VIA, RIOT), es la señal de Reset que inicializa el sistema al encenderse. (La raya encima de RES indica claramente que la señal es activa a nivel bajo es decir, su lógica es inversa.) (El ordenador al recibir esta señal hace un salto incondicional indirecto a la dirección \$FFFC \$FFFF.)

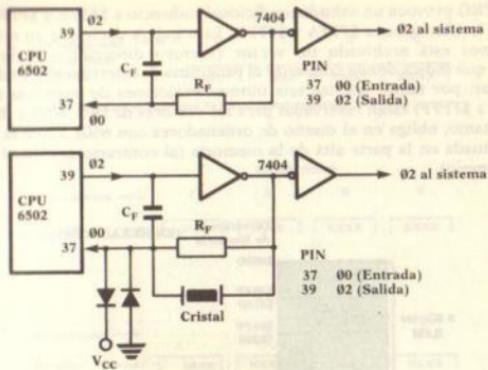

- Las señales 01, 02, y 03 son las entradas y salidas de reloj. 01 y 02 son salidas (para la sincronización) que provienen de un reloj interno del chip. Para la estabilización de este reloj interno es necesaria una señal de reloj exterior conectada a 00, según uno de los esquemas de la figura.

Fig. 2.3. Esquemas posibles de reloj.

- La linea S.O. permite la activación del flag V de sobrepasamiento desde el exterior (no la utilizaremos).

- La linea RDY detiene la CPU en todos los ciclos, excepto en escritura, y deja en alta impedancia los buses (no la usamos).

- La linea R/W indica a los dispositivos si el acceso es de lectura (nivel alto) o escritura (nivel bajo).

- La linea SYNC se pone a uno cuando la CPU accede a un código de operación (ver ensamblador para «Código de Operación»). (Tampoco la usamos.)

- Por último, estudiamos más detalladamente las señales de interrupción; éstas son: NMI e IRQ.

Como ya debe saber el lector, una interrupción, activada por una señal hardware exterior (por ejemplo, pulsando la tecla ESC en el AMSTRAD o en el PC o BREAK en el COMMODORE), provoca que el microprocesador deje la tarea que está haciendo y haga un cambio de contexto, es decir, archive en memoria el estado en el que estaba al recibir la interrupción y pase a ejecutar otro programa (normalmente el monitor en ROM u otra rutina del Sistema Operativo).

Hay dos tipos de interrupción; la mascarable (IRQ), que puede ser inhabilitada por software (mediante una instrucción en máquina que la desactiva) y la no mascarable (NMI), que fuerza a la CPU a abandonarlo todo (suele usarse para abortar situaciones catastróficas = es un BREAK «salvaje»).

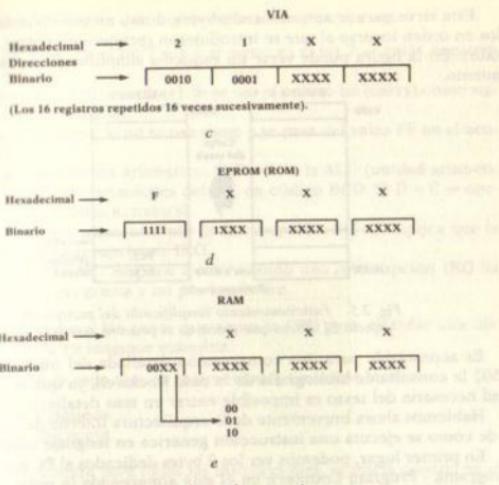

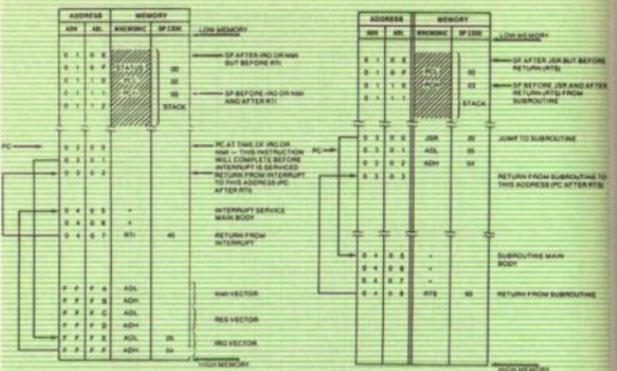

La IRQ provoca un salto incondicional indirecto a \$FFFE y \$FFFF y la NMI a las direcciones \$FFFA y \$FFFB. Esto quiere decir que en estas direcciones está archivado un vector (vector = dirección = 16 bits = 2 bytes), que indica dónde comienza el programa de interrupción. Podemos observar, por tanto, que las seis últimas posiciones de memoria (de la \$FFFA a \$FFFF) están reservadas para los vectores de IRQ, NMI y RESET y, por tanto, obliga en el diseño de ordenadores con 6502 a que la ROM vaya situada en la parte alta de la memoria (al contrario que en el Z-80, por ejemplo).

Fig. 2.4. Mapa de memoria.

Veamos ahora más detalladamente la arquitectura software del 6502.

Además de las seis posiciones anteriormente citadas, hay dos páginas de memoria (una página = 256 bytes = de \$XXOO a \$XXFF), que son usadas de forma especial por el 6502.

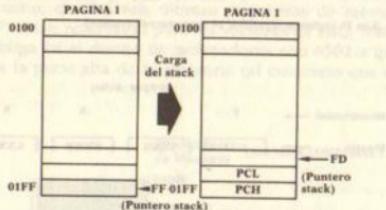

La página cero (\$0000 a \$00FF) es una zona de memoria de acceso rápido (ya que se ahorra un ciclo de máquina cada vez que se usa), por lo que suele utilizarse para almacenar en ella variables o datos de uso frecuente (normalmente las variables internas del sistema). La página 1 (\$0100 a \$01FF) es la zona reservada al STACK o pila. ¿Qué es la pila? Intentaremos explicarlo brevemente.

Cuando en el programa máquina hay que hacer un cambio de contexto (un salto a subrutina o una interrupción), hace falta archivar el estado de la CPU o enviar una serie de parámetros, para lo que se necesita una zona de memoria de acceso rápido en la que almacenar en un orden preestablecido esta información.

La pila ofrece un método muy sencillo mediante el puntero del stack (uno de los registros de la CPU accesible por software en lenguaje máquina).

Esta sirve para ir amontonando bytes, como en un «montón» y sacarlos en orden inverso al que se introdujeron (primero en entrar, último en salir). En la figura puede verse un esquema simplificado de su funcionamiento.

Fig. 2.5. Funcionamiento simplificado del puntero de stack. El último que entra, es el primero que sale.

Es aconsejable para una comprensión detallada del microprocesador 6502 la consulta de bibliografía de la casa Rockwell, ya que por la brevedad necesaria del texto es imposible entrar en más detalles.

Hablemos ahora brevemente de la arquitectura interna de los registros y de cómo se ejecuta una instrucción genérica en lenguaje máquina.

En primer lugar, podemos ver los 2 bytes dedicados al PC (contador de programa - Program Counter); en él está almacenada la posición de memoria en la que está el byte que estamos ejecutando.

El puntero del stack (en realidad, un solo byte, ya que el otro es fijo y indica la página 1) contiene la dirección del último byte almacenado en la pila.

Los registros de índice X e Y se utilizan en las operaciones en las que se necesitan valores de índice o desplazamiento relativo y son de 8 bits (son registros versátiles, pero no de uso general).

El acumulador es el registro primordial de la CPU. En él se realizan todas las operaciones aritméticas y lógicas.

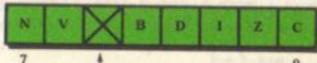

Por último, el registro de estado es un registro de 8 bits, 7 de los cuales son flags (banderas o indicadores) que nos indican cuál es el estado de la CPU en cada momento. En la figura puede verse la colocación de cada indicador.

Fig. 2.6. Estructura de los bits del registro de Estado, que actúan como señalizadores o alarmas (flags).

A continuación damos una breve explicación de cada uno:

N: Flag de signo: si el bit 7 = 1 y el signo es el bit 7  $\Rightarrow$  valor negativo en el AC, y N = 1.

V: Sobrepasamiento (overflow): Si se usa el octavo bit (carry) como signo e igual a 1  $\Rightarrow$  overflow.

C: Señal de acarreo: Si no se usa signo y se pasa del valor FF en el acumulador el C = 1.

D: Flag de tratamiento aritmético: Si D = 1  $\Rightarrow$  la ALU (unidad aritmética lógica) realiza las operaciones del AC en código BCD. Si D = 0  $\Rightarrow$  operaciones en código binario natural.

I: Bandera de enmascaramiento de interrupción: Si I=1 implica que la CPU no aceptará interrupciones IRQ.

B: Señal de BREAK: Se pone a uno cuando una interrupción IRQ ha sido activada por programa y no por hardware.

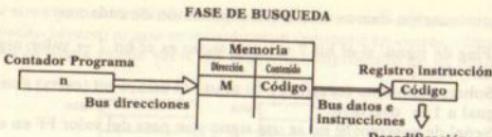

Describamos ahora los pasos que sigue la CPU para ejecutar una instrucción genérica en lenguaje máquina.

La ejecución de todo tipo de instrucciones tiene dos fases:

- Fase de búsqueda.

- Fase de ejecución.

La primera, común para todas las instrucciones, se inicia cuando en el PC está la dirección del código de la próxima instrucción a ejecutar. Esta dirección se pone en el bus de direcciones y se activa la patilla R/W (con R), con lo que la memoria (ROM o RAM) pone el contenido de la dirección en el bus de datos.

Del bus de datos la CPU lee el código y lo interpreta finalizando la primera fase (ver figura 2.7).

#### MEMORIA DE PROGRAMA

| Dirección | Contenido            |

|-----------|----------------------|

| n         | Código operación AND |

| n + 1     | M <sub>n</sub>       |

| n + 2     | M <sub>n+1</sub>     |

← 8 bits de menos peso de la dirección de M

← 8 bits de más peso de la dirección de M

#### MEMORIA DATOS

| M <sub>n</sub> - M <sub>n+1</sub> | 2.º operando |

|-----------------------------------|--------------|

|                                   |              |

Fig. 2.7. Ejecución de una instrucción.

La fase de ejecución depende de cada instrucción. Si ésta necesita un dato, lo leerá de la memoria de forma similar a como leyó el código, almacenándolo en algún registro o usándolo según el caso. Si este dato es una dirección (2 bytes), es obvio que serán necesarios dos accesos sucesivos a memoria (ver figura).

En el apéndice se pueden ver detalladas tablas que describen todas las instrucciones, su tiempo de ejecución y otros datos de interés. Haremos una descripción breve de ellas en la parte dedicada al ensamblador.

## BUSES Y CRONOGRAMAS

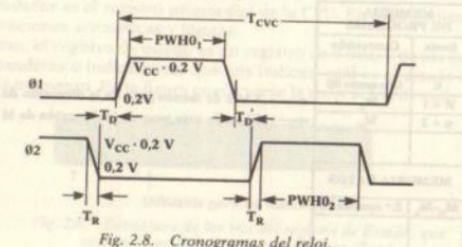

En nuestro ordenador todas las operaciones se realizan sincronamente; esto quiere decir que todas las partes implicadas en una operación actúan al mismo tiempo. Es igual que una orquesta en la que todos los músicos deben dar una misma nota al mismo tiempo, no esperan a oír la del compañero, ya que sería fatal. Al igual que los músicos se «sincronizan» al director de orquesta en el microprocesador todos los sistemas se sincronizan con el reloj. Reloj es una señal periódica, conocida como 01.

Existe otra señal 02 que es la inversa de 01; cuando 01 está en estado alto, 02 está en estado bajo, y viceversa.

Fig. 2.8. Cronogramas del reloj.

La frecuencia de esta señal, las veces que se repite cada segundo, nos da la rapidez con que el ordenador realiza sus operaciones. En nuestro caso será de 1 MHz (un millón de veces por segundo). Aunque pueda parecer mucho, con la tecnología actual no lo es, pues existen otros microprocesadores que funcionan a 8 MHz e incluso a 16 MHz.

Como todas las señales están referidas al reloj, se suelen dibujar con respecto a 01 o 02. A partir de ahora utilizaremos algunos de estos dibujos para explicar las distintas señales de control.

El bus de direcciones está formado por 16 líneas conocidas como A1, A2, ..., A15 (la A viene de address, dirección en inglés).

El bus de datos estará formado por ocho líneas conocidas como D0, D1, ..., D7 (la D viene de Data, es decir, dato).

Fig. 2.9. Esquema Riot.

Los cronogramas de estos dos buses se verán en el capítulo siguiente al hablar de la memoria.

Cuando un usuario programa un ordenador, normalmente lo hace en un lenguaje de «alto nivel», es decir, un lenguaje más cercano al nivel humano.

Este tipo de lenguajes (como el BASIC, PASCAL, COBOL, FORTRAN etc.) resulta incomprendible por el hardware del ordenador (circuitería), que sólo entiende un tipo de lenguaje: el lenguaje máquina (o código objeto). Este lenguaje máquina es una ristra de unos y ceros (pulsos altos y bajos de tensión), y es un lenguaje eléctrico.

Por eso cuando alguien trabaja en alto nivel, está utilizando un programa que traduce su lenguaje al lenguaje máquina.

El lenguaje máquina permite hacer cosas que desde alto nivel son imposibles, ya que se están controlando los recursos del ordenador a su nivel más detallado.

En contrapartida, el lenguaje máquina es prácticamente inutilizable. (Una cantidad semejante de unos y ceros volvería loco a cualquiera.)

Por ello, ya hace tiempo se creó el lenguaje ensamblador. Este lenguaje es una traducción, palabra a palabra, del lenguaje máquina; por ello, el programa que ensambla lo único que hace (en principio) es traducir una serie de códigos y números (nemotécnicos o nemómicos) a una ristra de dígitos binarios.

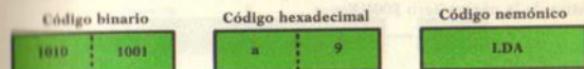

En el 6502 la palabra de datos tiene un ancho de 8 bits, por lo que en principio sería posible la existencia de  $2^8 = 256$  instrucciones, aunque, en realidad, algunos códigos no se utilizan. Un primer paso para la utilización del lenguaje máquina es la comprensión del código hexadecimal, que permite representar números binarios de un número de bits múltiplo de 4 de forma directa y sin operaciones aritméticas intermedias (ver tabla), con lo que un número de 8 bits queda útilmente transformado en \$XX y una dirección en \$XXXX.

| Hexadecimal | Binario |

|-------------|---------|

| 0           | 0000    |

| 1           | 0001    |

| 2           | 0010    |

| 3           | 0011    |

| 4           | 0100    |

| 5           | 0101    |

| 6           | 0110    |

| 7           | 0111    |

| 8           | 1000    |

| 9           | 1001    |

| A           | 1010    |

| B           | 1011    |

| C           | 1100    |

| D           | 1101    |

| E           | 1110    |

| F           | 1111    |

Para mayor información sobre el sistema de numeración binario, ver el apéndice.

Aunque la numeración hexadecimal simplifica enormemente la programación en máquina, carece de un sentido «natural» de número para el hombre (por ello, los ensambladores comerciales permiten la utilización de varios sistemas de numeración: hexadecimal, decimal, octal y binario).

Aunque los códigos podrían escribirse en el programa en su forma numérica, la principal ventaja del ensamblador es que traduce una palabra nemotécnica a su número correspondiente. Por eso en lenguaje ensamblador se utilizan como códigos de operación abreviaturas (del inglés) que in-

dican qué es lo que hace la instrucción. Esto (lo del inglés) obliga al programador en máquina a tener una leve idea sobre lo que algunas palabras en inglés significan. Por ejemplo, la instrucción LDA (Load Acumulator) significa «Carga en el acumulador el dato...». LDA es traducido por el ensamblador al número binario 1010.1001 (ver figura).

Fig. 2.10. Tres formas de expresar la instrucción de "Carga del Acumulador" mostrando la evolución del lenguaje máquina.

Uno de los conceptos principales que se deben tener en cuenta a la hora de programar en máquina es el direccionamiento, es decir, la forma en la que se indica en la instrucción cómo y dónde obtener los datos para ejecutarla (stack, registros, página cero, memoria, etc.).

En el caso del microprocesador 6502, éste posee 13 modos posibles de direccionamiento, que lo dotan de gran potencia.

Las instrucciones en lenguaje máquina pueden tener una longitud de 1, 2 ó 3 bytes. El primero corresponde en todas ellas al código de operación, que es diferente para cada tipo de instrucción.

Por ello, las instrucciones que utilizan un solo byte no poseen mayor información que la operación a realizar (se supone en la mayoría de los casos que el dato a utilizar está implícito en la propia operación). Por ejemplo, CLI (CLEAR I) pone a cero el flag I del registro de estado.

En las instrucciones con 2 bytes, el segundo corresponde a un número de 8 bits (que puede ser un dato o una dirección de página cero \$00XX, de Stack \$01XX, etc.).

En los de 3 bytes, los dos últimos suelen ser una dirección (16 bits = 2 bytes).

Los 13 modos de direccionamiento son los siguientes:

- 1) Inmediato (2 bytes): El segundo byte indica el dato a utilizar (el primero es el código de operación).

#### Ejemplo

Código OP/Operando/Expresión en ensamblador/Expresión

A9 0 0 LDA #00 (A)←00

- 2) Absoluto (3 bytes): Los dos últimos bytes indican la dirección del dato a utilizar.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

AD (2136) LDA 2136 (A) $\leftarrow$ (2136)

3) Por página cero (2 bytes): El segundo byte indica una dirección relativa de la página cero \$00XX.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

A5 (00,61) LDA61 (A) $\leftarrow$ (00,61)

4) Direcciónamiento por página cero, Índice X (Y) (2 bytes): La dirección del operando (que está en la página cero) se halla sumando el segundo byte de la instrucción al contenido del registro X(Y) de la CPU.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

B5 (00,38+X) LDA 38,X (A) $\leftarrow$ (00,38+X)

6) y 7) Absoluto índice X(Y) (3 bytes): La dirección donde está el dato a utilizar se halla sumando a la dirección de los dos últimos bytes de la instrucción el contenido del registro X(Y).

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

BD (22,33+X) LDA 2233,X (A) $\leftarrow$ (22,33+X)

8) Direcciónamiento por acumulador (1 byte): En el acumulador se encuentra el dato a utilizar.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

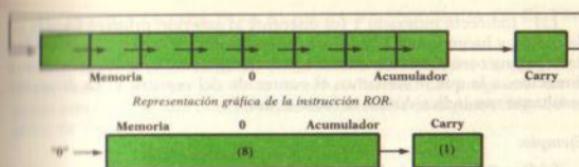

6A ROR Acumulador Ver fig. 2.11

9) Implicada (1 byte): El operando va implicado en la propia instrucción.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

18 Carry CLC C $\leftarrow$ 0

Fig. 2.11. Representación gráfica de la instrucción LSR.

10) Relativo (2 bytes): El segundo byte de la instrucción es un valor offset que se añade al contador de programa para provocar una bifurcación. Esta es condicional si es necesaria alguna condición (del registro de estado) para que se realice.

Ejemplo:

Código OP/Operando/Expresión en ensamblador/Expresión

F0 13 BEQ13 (PC) $\leftarrow$ (PC)+13

11) Indirecto (3 bytes): Los dos últimos bytes proporcionan una dirección. De ella y de la siguiente obtenemos otra, que es la que indica dónde está el dato (esta última dirección se suele llamar vector).

Ejemplo:

Código OP/Operando/Ensamblador/Expresión

6C 3128 JMP(3128) (PC) $\leftarrow$ (3128) Y (3129)

12) Indexado X indirecto (primero indexa y luego indirecciona) (2 bytes): El segundo byte se añade al registro X y el resultado es una dirección de la página cero. Con su contenido y el de la siguiente obtenemos (el vector) dirección del dato.

Ejemplo:

Código OP/Operando/Ensamblador/Expresión

A1 30 LDA(30,X) (A) $\leftarrow$ ((0030)+X)

NOTA: Cuando se escribe ( $\leftarrow$ ) indica el contenido de lo que hay dentro del paréntesis. Por ejemplo (\$30F1), es el número \$XX contenido en la dirección \$30F1.

13) Indirecto indexado Y (es diferente al anterior: primero hace la dirección y luego indexa) (2 bytes): El segundo byte indica una dirección de la página cero. Con su contenido y el del siguiente byte obtenemos otra dirección, a la que le sumamos el contenido del registro Y. La dirección resultante nos indica dónde se halla el dato.

Ejemplo:

Código OP/Operando/Ensamblador/Expresión

B1 32 LDA (32),Y (A)--(((0032)(0033))+Y)

Veamos ahora un pequeño resumen en el que se indica brevemente la función de las principales instrucciones del 6502:

### 1) GRUPO DE INSTRUCCIONES ARITMÉTICAS Y LÓGICAS

Realizan operaciones aritméticas o lógicas:

|     |                      |

|-----|----------------------|

| ADC | Suma aritmética      |

| SBC | Substracción         |

| AND | Operación lógica AND |

| EOR | OR exclusiva         |

| ORA | Operación OR         |

### 2) INSTRUCCIONES DE LECTURA Y ESCRITURA EN MEMORIA

Transfieren información entre la memoria y los registros:

|     |                                    |

|-----|------------------------------------|

| LDA | Cargar acumulador                  |

| LDX | Cargar X                           |

| LDY | Cargar Y                           |

| STA | Almacenar el acumulador en memoria |

| STX | Almacenar el registro X            |

| STY | Almacenar Y                        |

### 3) INSTRUCCIONES DE TRANSFERENCIA ENTRE REGISTROS

Intercambian la información entre registros:

|     |                                               |

|-----|-----------------------------------------------|

| TAX | Transfiere el acumulador a X                  |

| TAY | Transfiere el acumulador a Y                  |

| TXA | Transfiere X al acumulador                    |

| TYA | Transfiere Y al acumulador                    |

| TSX | Transfiere el puntero del stack a X           |

| TXS | Transfiere el registro X al puntero del stack |

### 4) INSTRUCCIONES PARA RUPTURA DE SECUENCIA EN EL PROGRAMA

Estas instrucciones cambian el contenido del contador de programa, lo que implica una ruptura de la secuencia normal del programa. En algunos esta ruptura está condicionada al contenido de algunos flags del registro de estado.

|     |                      |

|-----|----------------------|

| JMP | Salto incondicional  |

| BCC | Bifurcación si C = 0 |

| BCS | Bifurcación si C = 1 |

| BEQ | Bifurcación si Z = 1 |

| BNE | Bifurcación si Z = 0 |

| BMI | Bifurcación si N = 1 |

| BPL | Bifurcación si N = 0 |

| BVC | Bifurcación si V = 0 |

| BVS | Bifurcación si V = 1 |

### 5) INSTRUCCIONES DE USO DEL STACK

Manejan el puntero de stack:

|     |                                      |

|-----|--------------------------------------|

| PHA | Mete al acumulador del stack         |

| PHP | Mete al registro de estado del stack |

| PLA | Saca al acumulador del stack         |

| PLP | Saca al registro de estado del stack |

### 6) INSTRUCCIONES DE TRATAMIENTOS DE SUBRUTINA

Para el uso de subrutinas e interrupciones:

|     |                                                    |

|-----|----------------------------------------------------|

| JSR | Salto a subrutina                                  |

| RTS | Retorno de subrutina                               |

| BRX | Provoca IRQ (interrupción mascarable) por software |

| RTI | Retorno de rutina de interrupción                  |

### 7) INSTRUCCIONES DE CAMBIO DE LOS «FLAGS» DEL REGISTRO DE ESTADO

Ponen dichos flags a cero o unos, según el caso:

|     |       |

|-----|-------|

| CLC | C = 0 |

| CLD | D = 0 |

| CLI | I = 0 |

| CLV | V = 0 |

| SEC | C = 1 |

| SED | D = 1 |

| SEI | I = 1 |

## 8) INSTRUCCIONES DE INCREMENTO Y DECREMENTO

Afectan a memoria o a registros:

|     |                                         |

|-----|-----------------------------------------|

| DEC | Decrementa en 1 el contenido de memoria |

| DEX | Decrementa en 1 el registro X           |

| DEY | Decrementa en 1 el registro Y           |

| INC | Incrementa memoria                      |

| INX | Incrementa el registro X                |

| INY | Incrementa el registro Y                |

## 9) INSTRUCCIONES DE TRASLADO Y ROTACION DE BITS

Permiten desplazar o rotar el acumulador (interviniendo el carry) o la memoria:

|               |                                                     |

|---------------|-----------------------------------------------------|

| ASL           | Desplaza hacia la izquierda el acumulador o memoria |

| LSR           | Desplaza hacia la derecha el acumulador o memoria   |

| (ver figuras) |                                                     |

|     |                                                                |

|-----|----------------------------------------------------------------|

| ROR | Desplazamiento cíclico a la derecha del acumulador o memoria   |

| ROL | Desplazamiento cíclico a la izquierda del acumulador o memoria |

## 10) INSTRUCCIONES DE COMPARACION LOGICA O ARITMETICA

|     |                                                                                              |

|-----|----------------------------------------------------------------------------------------------|

| AND | Operación lógica AND                                                                         |

| CMP | Compará (resta A a M) sin afectar al acumulador. Sólo afecta al registro de estado (N Z y C) |

| CPX | X-M                                                                                          |

| CPY | Y-M                                                                                          |

| BIT | A AND M sólo afecta a los flags                                                              |

## 11) INSTRUCCIONES ESPECIALES

|     |                                              |

|-----|----------------------------------------------|

| NOP | No hace nada ( pierde dos ciclos de máquina) |

|-----|----------------------------------------------|

Como vimos en el capítulo 1, la memoria es una de las partes principales del ordenador, ya que permite tener los programas a ejecutar y los datos a usar.

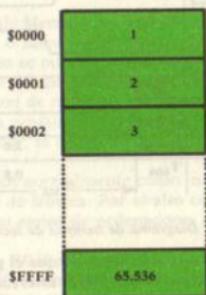

Desde el punto de vista de la CPU la memoria es una serie de «casillas», cada una con una dirección, en las que se pueden leer o guardar datos. Estas direcciones son un número, siendo estas casillas consecutivas y refiriendo cada número, o dirección, a una y sólo una de las casillas.

DIRECCION-CASILLA

Esquema de la memoria.

Fig. 3.1. Esquema de la memoria.

La dirección se indica por un número que la CPU coloca en el bus de direcciones. Como se indicó, este número estará en notación binaria. Por ser este bus de 16 hilos, o líneas, podrá diferenciar, o direccionar,  $2^{16} = 65.536$  posiciones diferentes de memoria, o 64 K (por K se entiende un kilobyte, que está formado por 1024 casillas).

Los datos a leer o escribir serán colocados, o leídos, del bus de datos. Por ser este bus de datos de 8 líneas, podrán tomar los datos  $2^8 = 256$  valores diferentes; pudiendo representar estos datos instrucciones o datos propiamente dichos.

Por último, en el bus de control existe una señal llamada R/W (del inglés Read/Write = lectura/escritura), que indica si la CPU quiere leer o escribir un dato.

Si la señal R/W tiene un nivel lógico alto, un «1», indica que el procesador quiere leer el dato; por el contrario, si tiene un nivel lógico bajo, un «0», el procesador querrá escribir el dato.

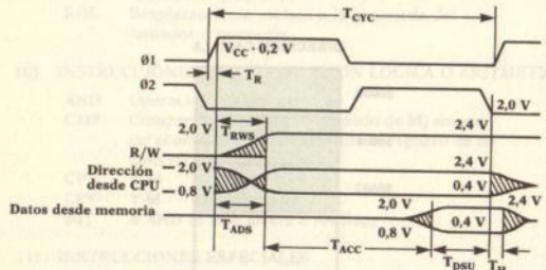

Como se dijo en el capítulo anterior, el ordenador funciona de modo sincrónico dirigido por un reloj; luego las distintas operaciones descritas anteriormente seguirán un orden en el tiempo.

Para realizar una operación de escritura la CPU coloca la dirección de la posición de memoria a leer en el bus de direcciones y un 1 en la línea de R/W durante la parte final del ciclo alto de 01.

Fig. 3.2. Diagrama de tiempos de lectura.

Desde que la memoria recibe la señal de que el procesador quiere leer un dato hasta que lo coloca pasará un cierto intervalo de tiempo. En nuestro caso éste será desde que 02 pasa de estado bajo a estado alto, pues al final del ciclo alto de 02 el procesador tomará como dato el valor que la memoria coloque en el bus de datos.

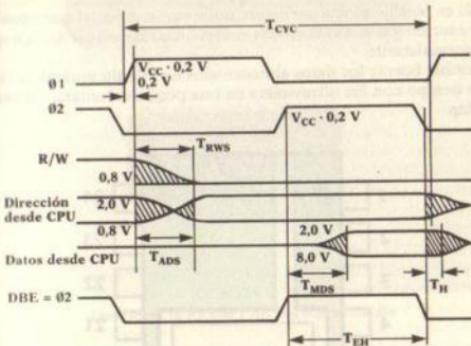

El proceso de escritura es prácticamente idéntico.

Fig. 3.3. Diagrama de tiempos de escritura.

La diferencia está en que mientras 02 está alto R/W está a nivel bajo y que durante la parte alta de 02 el microprocesador coloca el dato a escribir, es leído por la memoria y escrito.

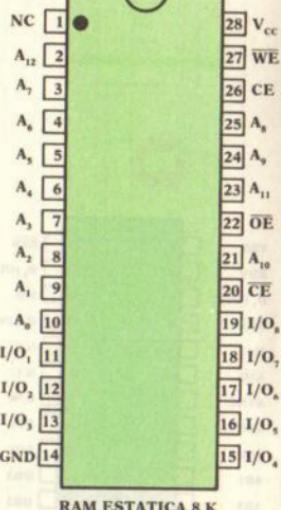

La memoria de nuestro ordenador está formada por dos bloques principales.

La ROM (Read Only Memory = Memoria de sólo lectura) es la que almacena el programa, o software, que controla nuestro ordenador. Como su nombre indica, sólo se pueden realizar en ella operaciones de lectura. Si intentamos escribir un dato en ella, sencillamente no lo admitirá, permaneciendo la posición de memoria direccionada con el valor que tuviese en un principio. La ventaja de este tipo de memoria es que no se borra si se apaga el ordenador, es decir, los datos almacenados estarán siempre listos para la lectura.

Los circuitos usados normalmente como memoria ROM ya vienen con el programa grabado de fábrica. Por el alto coste que esto conlleva sólo se utiliza para grandes series de ordenadores comerciales, ya que así resulta más barato.

Otros circuitos de ROM son las PROM. Estas se pueden grabar, pero sólo una vez, ya que el proceso se realiza fundiendo pequeños fusibles que representan los bits. Tiene el problema que si cometemos un error éste no tendrá posible arreglo.

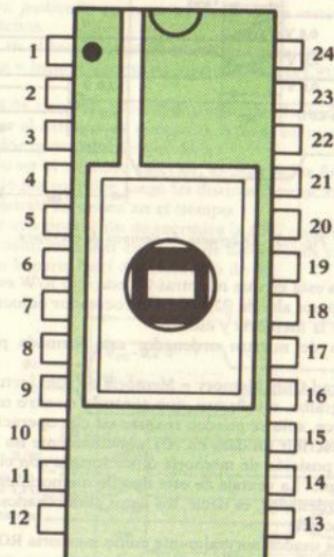

El chip, o circuito integrado, que utilizaremos es la EPROM (Erasable Programmable Read Only Memory = Memoria programable de sólo lectura).

ra). En él es posible grabar mediante un proceso especial que consiste en intentar escribir en ella con circuitos especiales de mayor voltaje que los usados normalmente.

Es posible borrar los datos almacenados en ella iluminándola durante un largo tiempo con luz ultravioleta en una pequeña ventana existente sobre el chip.

Fig. 3.4. Patillaje de una Eprom.

Por ello, esta ventana deberá estar tapada por algún tipo de etiqueta, o pegatina, ya que una excesiva exposición a los rayos solares podrían borrar nuestro programa.

El otro tipo de memoria es la RAM (Random Access Memory = Memoria de acceso aleatorio), es decir, que puede accederse a cualquiera de sus

Aspecto de la Eprom y del microprocesador.

posiciones). En ésta se puede leer y escribir, pero tiene el defecto que todo lo almacenado se pierde si se apaga el ordenador.

En el comercio existen dos tipos de memoria RAM: estáticas y dinámicas.

Las estáticas son más antiguas, pero son más sencillas de manejar por necesitar menos circuitos adicionales. Además, para sistemas pequeños como el nuestro son las más indicadas.

Las dinámicas tienen mayor capacidad, pero tienen un defecto, que olvidan los datos que tienen almacenados cada milésima de segundo, por lo que hay que estar «refrescándolas» constantemente, con la circuitería que esto lleva asociado.

Si los datos que tenemos en esta memoria quieren ser conservados deberán almacenarse en otra parte para no perderlos, tales como guardarlo en una cinta o casette.

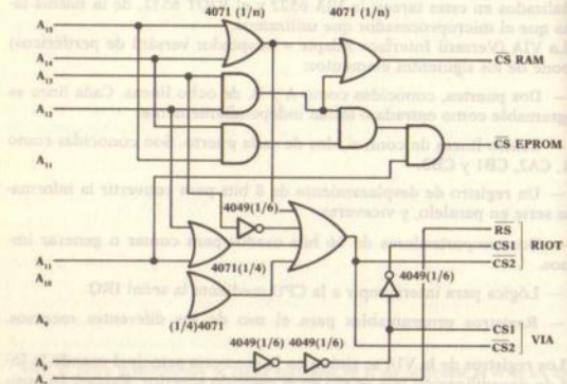

## EL DECODIFICADOR DE DIRECCIONES

El decodificador de direcciones es una parte esencial del circuito de un ordenador. Su función es la de activar una de las patillas del circuito dependiendo de los bits de mayor peso del bus de direcciones. Es decir, de la zona de memoria en la que pretende trabajar el microprocesador y que corresponde a la posición que ocupa en ella el dispositivo y que hemos prefijado previamente mediante el diseño del mapa de memoria.

El decodificador de nuestro ordenador ha sido simplificado expresamente para que podamos realizarlo con unos pocos chips TTL-LS.

Con ellos implementamos las funciones lógicas que tomarán el valor

adecuado para activar las pastillas cuando en el bus de direcciones halla las direcciones correspondientes. Para calcular estas funciones no sólo es necesario conocimientos de electrónica digital, sino también del contenido de los chips existente en el mercado para utilizar el menor número de ellos. Existe una amplia bibliografía al respecto (ver apéndice), aunque en este tipo de diseños es importante la habilidad y técnicas «artesanas».

También se puede aprovechar el hecho de que algunas pastillas tengan varias patillas o terminales de activación del chip a la hora de simplificar el circuito decodificador.

En nuestro caso el decodificador activa la pastilla de 8K de RAM (RAM estática 5565) cuando se direccionan los 8 primeros Kbytes de la memoria. Activa el RIOT cuando utilizamos las direcciones \$20XX y la VIA con las direcciones \$21XX.

Cuando utilizamos los dos últimos Kbytes, activa la EPROM, donde están almacenados los programas de utilidades que se proporcionan.

## L

A función de las etapas de entrada-salida es comunicar el ordenador con el exterior. En la mayoría de los casos debe adaptar el tipo de señal que le llega del exterior a una señal que sea comprensible por el ordenador.

El lugar de llegada de los datos del exterior se conoce normalmente como port, o puerto, siendo en nuestro caso de igual longitud que el bus de datos, 8 bits.

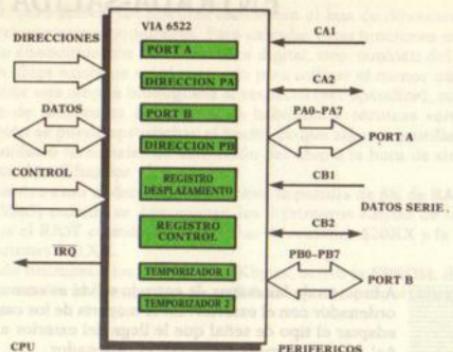

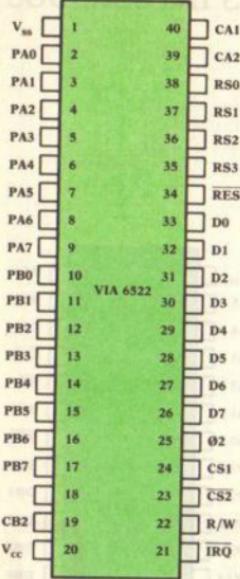

Por ser este tipo de circuitos, usualmente, complicados y voluminosos usaremos dos circuitos integrados especializados en estas tareas: la VIA 6522 y el RIOT 6532, de la misma familia que el microprocesador que utilizamos.

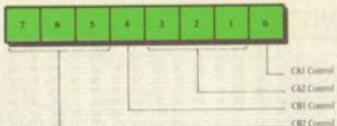

La VIA (Versatil Interface Adapte = Adaptador versátil de periféricos) dispone de los siguientes elementos:

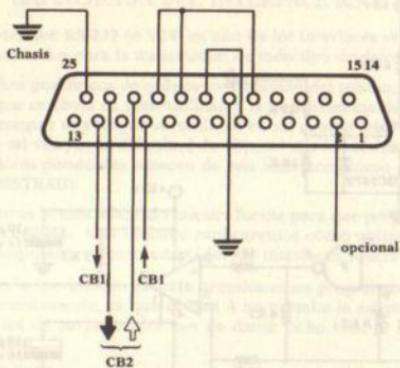

- Dos puertos, conocidos como A y B, de ocho líneas. Cada línea es programable como entrada o salida independientemente.

- Cuatro líneas de control, dos de cada puerto. Son conocidas como CA1, CA2, CB1 y CB2.

- Un registro de desplazamiento de 8 bits para convertir la información serie en paralelo, y viceversa.

- Dos temporizadores de 16 bits usados para contar o generar impulsos.

- Lógica para interrumpir a la CPU mediante la señal IRQ.

- Registros programables para el uso de los diferentes recursos.

Los registros de la VIA se sitúan en la memoria principal usando la lógica de decodificación que se vio en el capítulo anterior. Existen 16 posiciones de memoria que se direccionan por 4RS0, RS1, RS2, RS3

*Nota:* El único problema que se puede encontrar en el decodificador es el de los «glitches» (ver bibliografía sobre este tema). En nuestro caso, es tan sencillo y su retardo tan pequeño ( $20nS \times n$  como máximo) comparado con el período de reloj ( $1\text{ }\mu\text{s} = 10^{-6}\text{ S}$ ).

Fig. 4.1. Esquema de la vía.

(4 bits  $\rightarrow 2^4 = 16$  posiciones). El decodificador activa las patillas CS1 y CS2 cuando nos referimos a las direcciones \$21XX.

Fig. 4.2. Decodificador de direcciones.

Ejemplo práctico del decodificador de un ordenador.

Las direcciones de los port son \$2100 para el B y \$2101 para el A. Las direcciones de los registros de control son \$2102 para el B y \$2103 para el A.

Para programarlos cada bit se colocará un 0 si se quiere programar como entrada y 1 si se quiere programar como salida en los registros de direcciones.

Por ejemplo, para programar todo el port B como salida pondriamos en su registro de control de direcciones el número:

11111111

después de esto todo lo que colocáramos en los registros de los ports saldría al exterior; por el contrario, si lo que queremos es leer en el port B, en el registro de control se colocaría:

00000000

y después el valor que leeríamos del registro del port B sería el que le tuviera llegando del exterior.

Veamos dos ejemplos:

```

:L

1 LDA #11111111 ;PROGRAMA SALIDAS

2 STA DRBV

3 LDA PBV ; LEER DATOS

```

```

:L

1 LDA #00000000 ;PROGRAMA SALIDAS

2 STA DRBV

3 STA PBV ; ESCRIBE DATOS

```

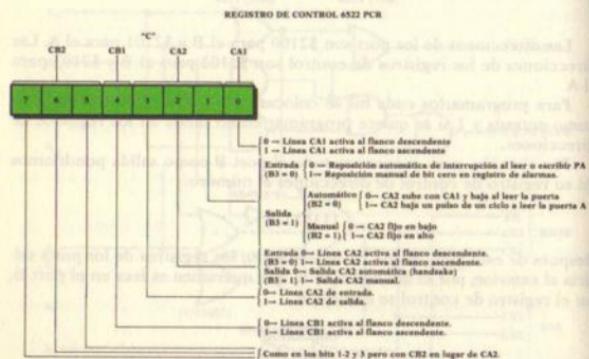

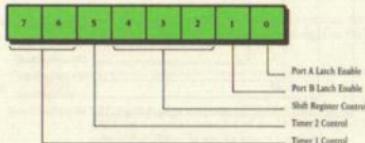

El registro de control de las líneas CA1, CA2, CB1 y CB2 está en la posición \$200C. Su configuración se observa en la figura 4.3.

Fig. 4.3. Función de cada bit del registro de control PCR.

Estas líneas, dos para cada port, sirven para establecer un protocolo, o handshaking. Esta es la forma que tienen dos ordenadores para comunicarse. Antes de transmitir datos deben mandar la señal equivalente de «que van los datos» y si los recibe bien, decir «ya los tengo». El equivalente de las personas son las frases hechas que se utilizan al comenzar una conversación; por ejemplo, dos amigos se encuentran, y antes de contarse nada de interés dicen:

Hola, Fulano, ¿la familia que tal?

La familia bien, ¿y tú que tal?

Bien

le responde, y a partir de aquí comienzan a hablar de los temas que les interesan.

En el siguiente programa observamos un sencillo protocolo que usa sólo una señal de ocupado (Busy). Suele ser el usado para comunicarse con una impresora.

```

:L

1 STA PAU ;DEJA EN PORT A

2 SIGUE LDA PCRV ;COMPROBAR SI LEIDO

3 AND #000001000

4 BEQ SIGUE ;SI NO REPETIR

```

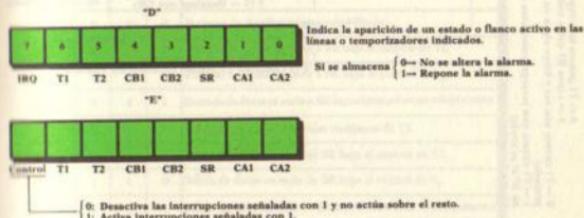

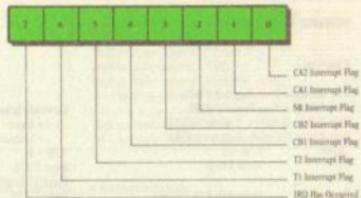

La posibilidad de realizar entrada-salida por interrupciones es muy útil. Para ello existe el registro de control situado en la posición \$200D el de alarma y en la \$200E el de activación.

En la figura 4.4 vemos las misiones de los distintos registros.

Fig. 4.4. Registro de alarmas de interrupciones IFR.

La utilidad de la interrupción es clara en el siguiente ejemplo. Supongamos que tenemos que realizar unas operaciones en la CPU, y leer, por ejemplo, un teclado. Por ser la velocidad de las personas lenta comparada con el ordenador. Si realizáramos un bucle de espera que comprobase si se ha pulsado alguna tecla se perderían algunos segundos, durante los cuales la CPU no ha realizado ninguna de las operaciones pendientes. Por tanto, si hace las operaciones, éstas podrían durar demasiado tiempo y no leer la tecla cuando fuese pulsada. La solución es programar la VIA de forma que cuando llegue un dato genere una señal de interrupción, se lea la tecla pulsada y se continúe con la ejecución del programa.

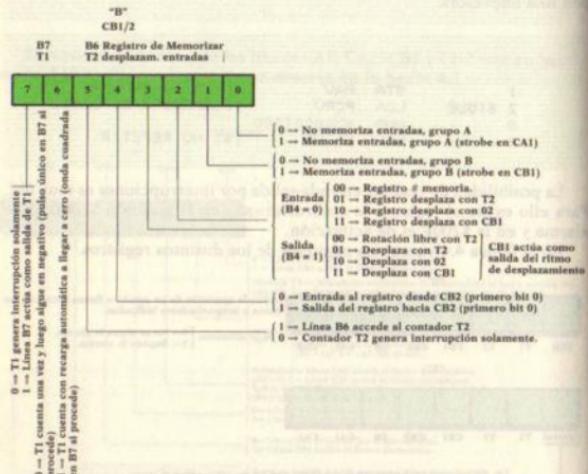

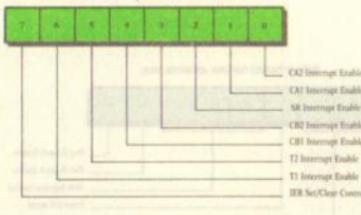

La VIA también dispone de dos temporizadores, o Timers, que tienen diversas utilidades: generar cada cierto número de reloj una interrupción, cortar los impulsos que llegan por las patillas PB6 o generar dichos impulsos por la línea PB7.

En la figura 4.5 se ve qué registros utiliza y su forma de programación.

Fig. 4.5. Registro auxiliar de control ACR.

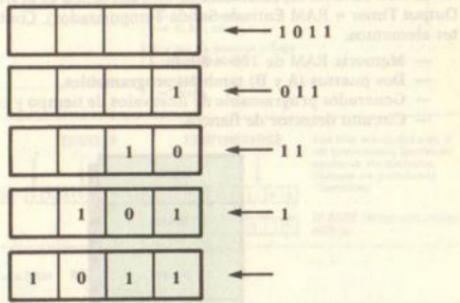

Por último, nos queda por ver el registro de desplazamiento. Este sirve para convertir los datos serie en paralelo, y viceversa.

Los datos están en paralelo, por ejemplo, en el bus de datos. Al mandarse un dato se mandan los ocho bits simultáneamente por las ocho líneas. Esto requiere menos tiempo, pero ocupa más sitio.

El enviar los datos en serie es enviarlos en «fila india». Esto ocupa más tiempo, pero sólo una línea. Para convertir de una forma a otra se utiliza el registro que pasa los bits que le llegan desplazando los que ya le han llegado, de ahí el nombre.

Fig. 4.6.

El registro de desplazamiento está situado en la posición de memoria \$200A y el control en \$200B (compartido con el temporizador).

| Bits de ACR |   |   | MODO DE FUNCIONAMIENTO DE SR                                        |

|-------------|---|---|---------------------------------------------------------------------|

| 2           | 3 | 4 |                                                                     |

| 0           | 0 | 0 | Registro de desplazamiento inhabilitado.                            |

| 0           | 0 | 1 | Entrada de datos en serie a SR bajo el control de T2.               |

| 0           | 1 | 0 | Entrada de datos en serie a SR bajo el control de 0 <sub>r</sub> .  |

| 0           | 1 | 1 | Entrada de datos en serie a SR bajo el control de un reloj externo. |

| 1           | 0 | 0 | Salida de datos en intervalos continuos de T2.                      |

| 1           | 0 | 1 | Salida de datos en serie de SR bajo el control de T2.               |

| 1           | 1 | 0 | Salida de datos en serie de SR bajo el control de 0 <sub>r</sub> .  |

| 1           | 1 | 1 | Salida de datos en serie de SR bajo el control de un reloj externo. |

Fig. 4.7. Funcionamiento del registro de desplazamiento.

La frecuencia con que se realiza el desplazamiento puede determinarse por:

- La activación de la bandera T2.

- Con 02.

- Los flancos descendentes de CB1 (por flanco descendente se entiende el paso de un nivel alto a un nivel bajo).

Un ejemplo de uso de este registro se ve mas adelante en el interfaz RS-232.

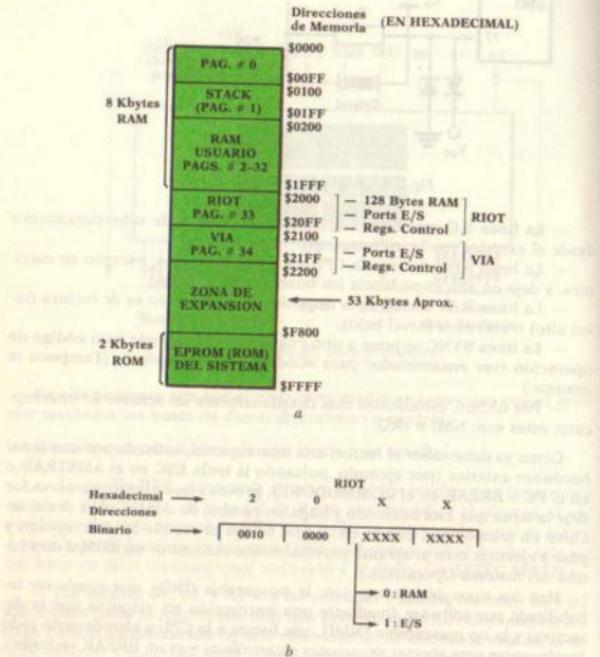

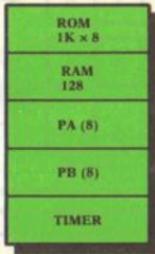

El otro circuito especializado de entrada-salida es la RIOT (RAM Input-Output Timer = RAM Entrada-Salida Temporizador). Contiene los siguientes elementos:

- Memoria RAM de  $128 \times 8$  bits.

- Dos puertos (A y B) también programables.

- Generador programable de intervalos de tiempo y con interrupción.

- Circuito detector de flancos.

Fig. 4.8. RIOT.

La memoria RAM es idéntica a la utilizada por el ordenador.

Sus direcciones en nuestro mapa de memoria son desde \$2000 hasta \$207F. El decodificador descrito en el capítulo anterior la selecciona utilizando las líneas CS1 y CS2.

La función de esta memoria es para usar el ordenador como un control industrial. Se puede realizar una configuración mínima con el microprocesador y la RIOT (versión de este mismo chip que incorpora una memoria ROM).

Los ports de la RIOT son idénticos a los vistos para la VIA. La dirección de port A es \$2080 y la de su registro de control es \$2081. La dirección del port B es \$2082 y la de su registro de control \$2083.

Fig. 4.9.

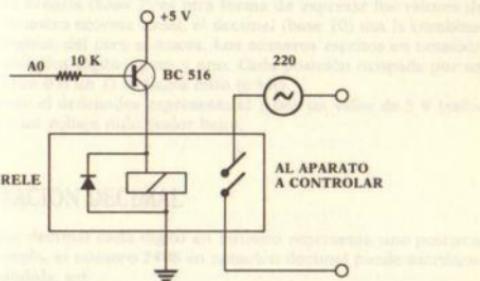

En este chip los ports no son exactamente iguales, en port B es capaz de suministrar una corriente de 3mA, lo que permite controlar directamente un transistor.

La última línea del port A (PA7), además de usarse como línea de entrada-salida, sirve como línea detectora de flancos, cambios de un nivel lógico a otro.

Existen dos formas de detectar los flancos: que si al detectar dicho flanco genere una interrupción, o no.

Los registros de control de dicho detector se activan mediante la escritura en las siguientes direcciones:

- \$2084: Detecta flanco negativo sin interrupción.

- \$2085: Detecta flanco negativo con interrupción.

- \$2086: Detecta flanco positivo sin interrupción.

- \$2087: Detecta flanco positivo con interrupción.

Para desactivar la detección de flancos será suficiente leer el registro de banderas de interrupción: \$2085.

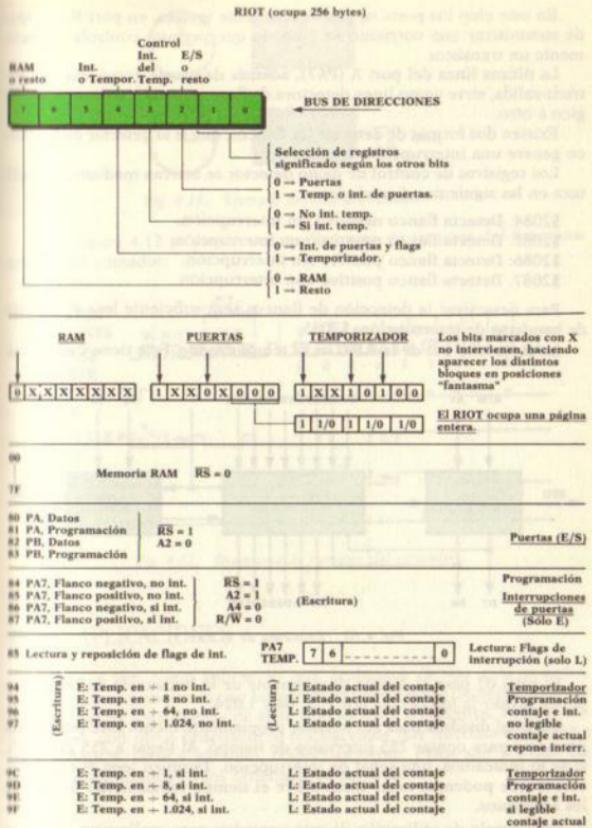

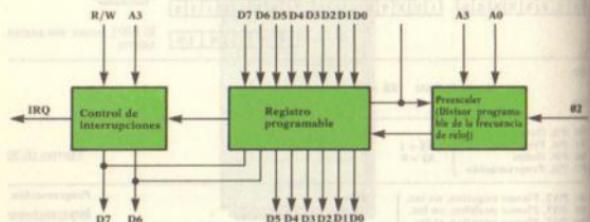

La parte más útil de la RIOT es el temporizador. Este tiene tres partes.

Fig. 4.10. Esquema de la Riot.

El reloj  $\varnothing 2$  pasa al divisor programable de la frecuencia de reloj. Este puede dividir la frecuencia por 1, 8, 64 y 1.024.

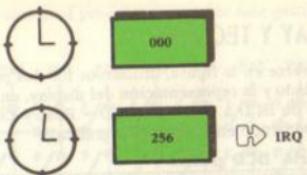

La señal dividida pasa al contador propiamente dicho. Este puede programarse para contar 255 intervalos de tiempo. Al llegar a 255 generará, si se lo indicamos, una señal de interrupción. También leer el contador, con lo que podemos tener ideas sobre el tiempo transcurrido desde que los activamos.

Un ejemplo de utilización de este contador, para realizar un contador de tiempo real de veinticuatro horas, se puede ver en el temporizador descrito en el capítulo siguiente.

Fig. 4.11. Ejemplo del uso del contador.

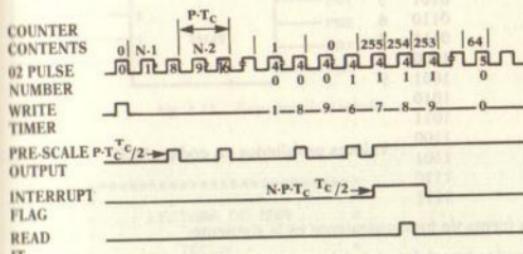

En la figura 4.12 se puede ver un diagrama de tiempos del funcionamiento del contador.

Fig. 4.12. Diagrama de tiempos del contador.

## APLICACIONES

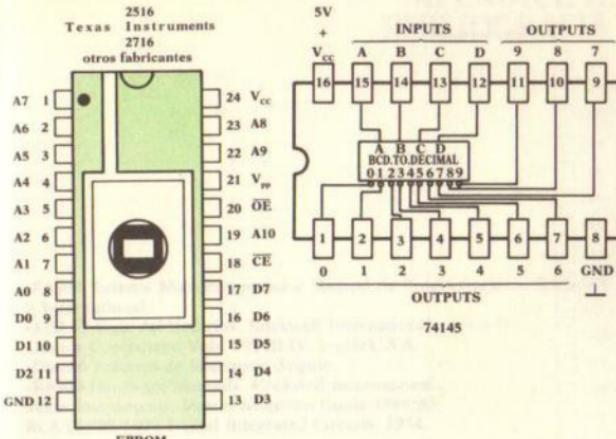

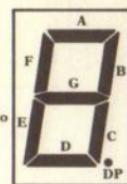

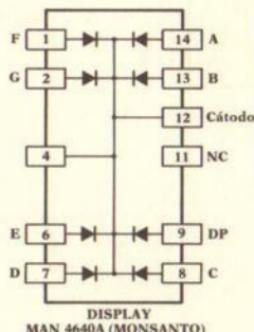

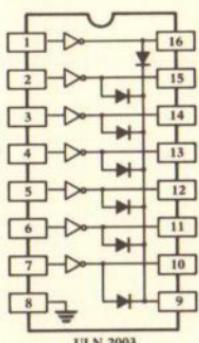

Vamos a ver cómo aplicar lo que acabamos de ver a la práctica. Como comunicaciones con las personas incluiremos un pequeño teclado de 21 teclas y un display de siete segmentos y seis dígitos. Para comunicaciones con otros ordenadores realizaremos dos interfaces: RS-232 y CENTRONICS, serie y paralelo, respectivamente. Estos son los más comúnmente utilizados en los ordenadores personales.

## DISPLAY Y TECLADO

Como puede verse en la figura, utilizamos los dos ports de la vía para la lectura del teclado y la representación del display, en combinación con un decodificador de BCD a decimal. (BCD → Binary Coded Decimal = es decir, decimal codificado en binario (ver gráfica)).

### Binario BCD gráfica

|      |                                  |

|------|----------------------------------|

| 0000 | 0                                |

| 0001 | 1                                |

| 0010 | 2                                |

| 0011 | 3                                |

| 0100 | 4                                |

| 0101 | 5                                |

| 0110 | 6                                |

| 0111 | 7                                |

| 1000 | 8                                |

| 1001 | 9                                |

| 1010 |                                  |

| 1011 |                                  |

| 1100 | Valores prohibidos en código BCD |

| 1101 |                                  |

| 1110 |                                  |

| 1111 |                                  |

La forma de funcionamiento es la siguiente:

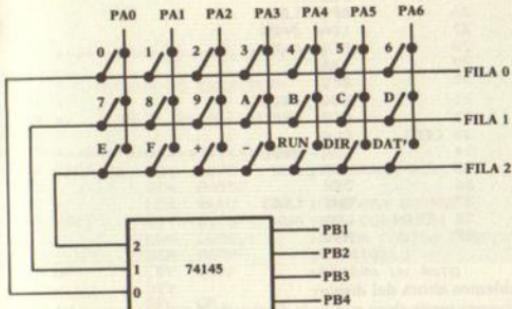

Con los bits del 1 al 4 del port B de la VIA seleccionamos una de las tres filas del teclado (para leer) o uno de los seis displays de siete segmentos (para escribir en ellos). (Con lo que sobre una patilla, la 3.) Al mismo tiempo utilizamos los bits del 0 al 6 del port A para leer o escribir, dependiendo del caso, las siete líneas correspondientes a los siete segmentos, o a las siete columnas del teclado. Veamos ahora por separado cada una de las dos partes: En primer lugar, veamos el proceso de lectura del teclado de una forma algo más detallada.

Para leer el teclado programamos el PORT B como salida y activamos secuencialmente las patas, de la 1 a la 4 inclusive, escribiendo los valores BCD del 0 al 2. Con esto activamos sucesivamente una y sólo una de las filas del teclado (que son tres).

Al mismo tiempo exploramos con el Port A (programado como lectura), las siete columnas con los bits del 0 al 6.

Así, cada vez que activamos una fila, leemos las siete columnas secuencialmente. Si el valor leído es 1 en algún caso, la tecla correspondiente de fila y columna estará pulsada.

Véase a continuación el programa máquina que gestiona el teclado siguiendo esta idea.

Fig. 4.13. Esquema del teclado.

```

1 ****

2 *      *

3 * LECTURA DE UNA *

4 *      *

5 * TECLA   *

6 *      *

7 ****

8 LEEKB  LDA #$00 ;PROGRAMA PORT

9 STA PADR

10 LDX #$06

11 STX PBDR

12 LEEI  LDA PADR

13 BNE SI

14 INX

15 CPX #$09

16 BNE LEEI

17 JSR ESCRIBE

18 JMP LEEKB

19 SI   STX AUX1

20 PHA

21 JSR ESCRIBE

22 PLA

23 LDX AUX1

```

```

24 LEE2    LDY #\$7F

25 DEY

26 BPL LEE2

27 LDA PADR

28 STA AUX

29 TXA

30 SEC

31 SBC #\$06

32 BEQ LEFIN

33 LEE3    CLC

34 LDA #\$06

35 ADC AUX

36 DEX

37 BNE LEE3

38 LEFIN   LDA AUX

39 RTS

```

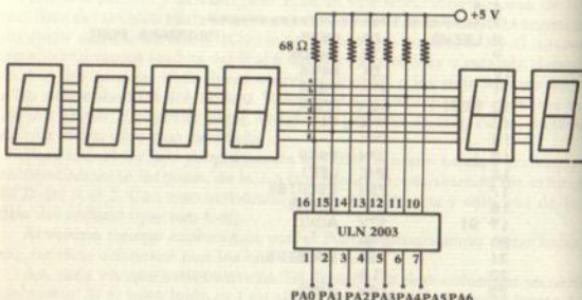

Hablemos ahora del display.

Debemos tener claro que cada display de siete segmentos debe ser reescrito cada cierto tiempo para que se mantenga constantemente encendido. Por ello, lo refresharemos siempre que la CPU no tenga otra tarea más importante que hacer.

Para escribir en un determinado dígito del display programamos como salida el Port B y activamos las patas de 1 a 4 con el número en BCD correspondiente al dígito a escribir (del 4 al 9). En el port A (programado como salida) escribimos en los bits del 0 al 7 el carácter a escribir, con lo que cada bit encenderá el segmento correspondiente.

Fig. 4.14. Esquema del «Display».

Veamos el programa de control.

1.

```

1 ****

2 *

3 * RUTINA DE ESCRITURA *

4 *

5 * EN EL DISPLAY *

6 *

7 ****

8 ESCRIBE LDA #\$7F ;PROGRAMA PORT A

9 STA PADR

10 LDY #\$05 ;PREPARA BUFFER

11 ESC1 LOY OUTBF,X ;LEE CODIGO

12 LDA CODE,Y ;CARGA CODIGO DISPLAY

13 STA PADR ;ESCRIBELO

14 UP LOY #\$7F ;ESPERA UN RATO

15 DEY

16 BPL UP

17 STY PADR ;REPROGRAMA PORT A

18 LDA #\$06

19 STA PBDR ;REPROGRAMA PORT B

20 DEX

21 BPL ESC1 ;FIN ?

22 RTS

```

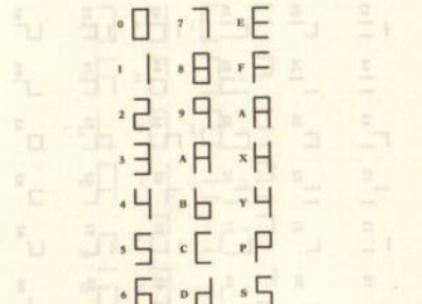

Utilizamos la tabla para encender los segmentos de cada dígito.

Fig. 4.15. Códigos para «Display».

Pero si quisiera usar otra, aquí damos todos los posibles códigos.

|   |    |   |                |                |                |                |                |                |                |                |                |                |                |                |                |                |                |                |                |                |    |    |

|---|----|---|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----|

| - | -  | 1 | 02             | 03             | 04             | -              | 05             | 06             | 07             | -              | 08             | -              | 09             | 0A             | -              | 0B             | 0C             | -              | 0D             | 0E             | 0F |    |

|   | 10 | - | 11             | 1              | 12             | 1              | 13             | 1              | 14             | -              | 15             |                | 16             | 17             | L              | 18             | L              | 19             | L              | 1A             | L  | 1B |

|   | 20 | - | 21             | 11             | 22             | 11             | 23             | 1              | 24             | 1              | 25             |                | 26             | 1              | 27             | 1              | 28             | 1              | 29             | 1              | 2A |    |

|   | 30 | - | 31             | 1              | 32             | 1              | 33             | 1              | 34             | 1              | 35             |                | 36             | 1              | 37             | 1              | 38             | 1              | 39             | 1              | 3A |    |

|   | 40 | - | 41             | 1              | 42             | 1              | 43             | 1              | 44             | -              | 45             |                | 46             | 1              | 47             | -              | 48             | 1              | 49             | -              | 4A |    |

|   | 50 | - | 51             | 1              | 52             | 1              | 53             | 1              | 54             | -              | 55             |                | 56             | 1              | 57             | 1              | 58             | 1              | 59             | 1              | 5A |    |

|   | 60 | - | 61             | 1              | 62             | 1              | 63             | 1              | 64             | 1              | 65             | 1              | 66             | 1              | 67             | -              | 68             | -              | 69             | -              | 6A |    |

|   | 70 | - | F <sub>1</sub> | H <sub>1</sub> | H <sub>2</sub> | P <sub>1</sub> | h <sub>1</sub> | h <sub>2</sub> | H <sub>3</sub> | H <sub>4</sub> | H <sub>5</sub> | H <sub>6</sub> | R <sub>1</sub> | H <sub>7</sub> | E <sub>1</sub> | H <sub>8</sub> | E <sub>2</sub> | b <sub>1</sub> | b <sub>2</sub> | H <sub>9</sub> |    |    |

Fig. 4.16. Figuras posibles del «Display».

Y una propuesta de caracteres posibles, para que el sufrido lector pueda utilizar caracteres alfanuméricos:

|   |   |    |   |

|---|---|----|---|

| : | - | O  | 4 |

| A | - | P  | 5 |

| B | - | Q  | 6 |

| C | - | R  | 7 |

| D | - | S  | 8 |

| E | - | T  | 9 |

| F | - | U  | + |

| G | - | V  | - |

| H | - | W  | - |

| I | - | X  | - |

| J | - | Y  | / |

| K | - | Z  | - |

| L | 0 | \$ | - |

| M | 1 | 1  | & |

| N | 2 | ^  | - |

| S | 3 | ~  | - |

Fig. 4.17. Posible código ASCII en el «Display».

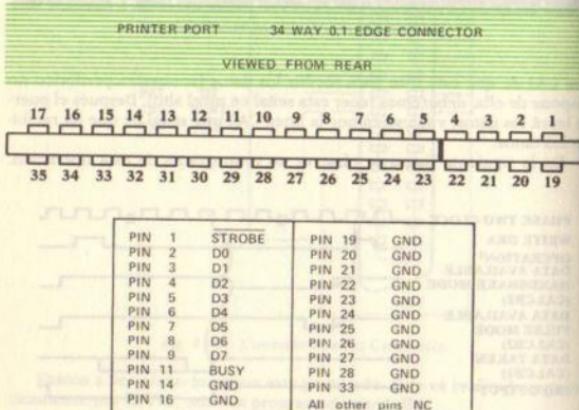

## CENTRONICS

El interface paralelo más usado es el CENTRONICS. En él se comunican los ocho bits de golpe por ocho líneas diferentes.

Uno de los datos principales de un interface es su velocidad de transmisión. Esta suele darse en baudios, que son los bits de información que transmite por segundo. Parece lógico que ésta sea lo más alta posible, pero hay que tener en cuenta que a mayor velocidad hay una mayor probabilidad que se cometan errores de transmisión (que los datos recibidos no sean los mismos que los emitidos).

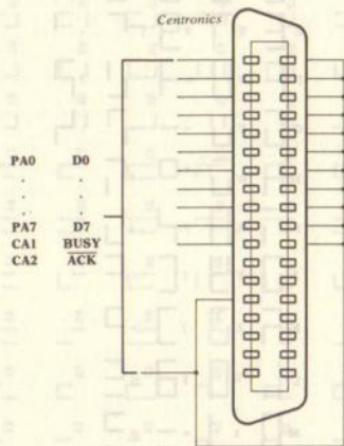

Para su realización práctica usaremos el port A de la VIA para los datos y las líneas CA1 y CA2 para el protocolo.

Fig. 4.18. Conexión interfaz Centronics.

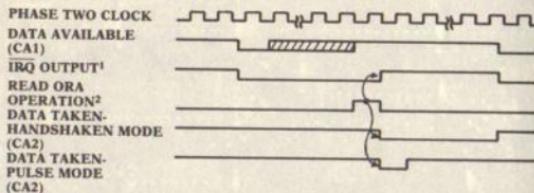

Vamos a ver cómo funciona este protocolo. Este es realizado automáticamente por la VIA, una vez programada para ello.

Vamos a ver el protocolo de lectura.

El periférico del que queremos leer debe mandar una señal por la lí-

Realización práctica de entrada/salida.

nea CA1 de que está listo para recibir los datos (si nuestro periférico no dispone de ella, deberemos tener esta señal en nivel alto). Después el puerto leerá los datos, y mandará por la línea CA2 una señal de que ha recibido los datos.

En la siguiente figura se observa un cronograma de esta operación.

PHASE TWO CLOCK

WRITE ORA

OPERATION<sup>1</sup>

DATA AVAILABLE-

HANDSHAKE MODE

(CA2.CB2)

DATA AVAILABLE

PULSE MODE

(CA2.CB2)

DATA TAKEN

(CA1.CB1)

IRQ OUTPUT<sup>2</sup>

Fig. 4.19. Diagrama de tiempos del «Handshake» de escritura.

Veamos el protocolo de escritura:

Al escribir el dato a enviar en el registro del puerto éste genera la señal de dato listo en la línea CA2 y espera la señal de dato recibido en la línea CA1. Esto se observa en la siguiente figura:

Fig. 4.20. Diagrama de tiempos del «Handshake» de lectura.

En nuestro caso el protocolo del AMSTRAD sólo dispone de la línea de «Busy» (equivalente a la señal de dato recibido vista anteriormente).

Fig. 4.21. Conector paralelo Centronics.

El programa que gestiona este interfaz es el siguiente:

```

1 ****

2 *

3 *      PROG. CENTRONICS      *

4 *

5 ****

6 *

7 * PROGRAMACION DEL PORT A

8 * COMO ENTRADA/SALIDA

9 * INTERFACE CENTRONICS

10 *

11 * PARA LEER EL PUNTO DE ENTRADA

12 * ES INCENT

13 *

14 * PARA ESCRIBIR ES OUTCENT

15 *

16 INCENT LDA #0 ;RUTINA DE ENTRADA

17 STA DR4V ;PROGRAMA REG. DIRECCION

18 STA CENFLAG

19 JMP CONT

20 OUTCENT LDA #FF ;RUTINA SALIDA

21 STA DR4V ;PROGRAMA RES. DIRECCION

22 LDA #B01

23 STA CENFLAG

24 CONT LDA #0 ;PARTE COMUN

25 STA PAU ;REGISTRO FLAGS INT.

26 LDA PCRU ;REGISTRO DE CONTROL

27 AND #M11111000

28 ORA #M200001000

29 STA PCRU

30 *

31 LDA ACRV ;REGISTRO AUXILIAR DE CONTROL

32 AND #M11111110

33 ORA #M00000001

34 STA ACRV

35 *

36 LDA #M10000011

37 ORA IERV ;ACTIVACION DE INTER.

38 STA IERV

39 LDA #0

40 STA IFRV

41 CLI

42 RTS

```

Si se usase un periférico con las dos señales de protocolo, es decir, con la señal «ACK» (equivalente del papel representado por CA2 en lo visto anteriormente), el esquema de conexión sería idéntico, pero conectando CA2 a ACK.

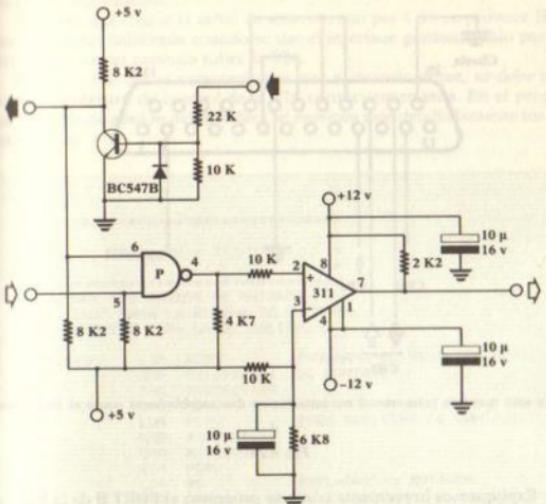

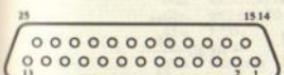

## EXPLICACION DEL INTERFACE RS-232

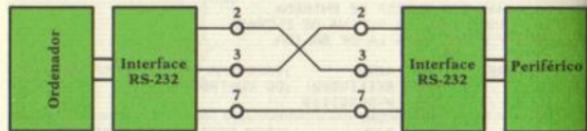

El interface RS-232 (o V24) es uno de los interfaces serie más comúnmente utilizados para la transmisión de todo tipo de datos.

Muchos periféricos de ordenador disponen del mismo, como estándar, por lo que es obvia su gran utilidad y la conveniencia de disponer de él para conseguir una mayor versatilidad en un equipo informático. Sin embargo, y tal vez por la dificultad de obtener sus tensiones, muchos de los ordenadores personales carecen de esta interface (como, por ejemplo, la gama AMSTRAD).

Nosotros hemos adaptado nuestra fuente para que proporcione las tensiones necesarias. Más adelante explicaremos cómo utilizar nuestra placa microcomputadora como adaptador de interfaces RS232-CENTRONICS.

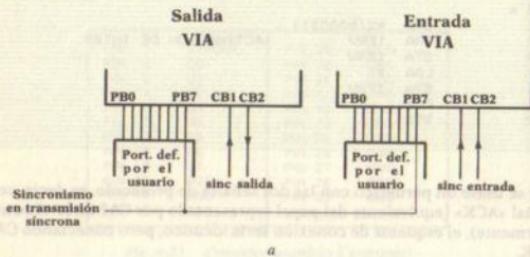

Como la transmisión es serie necesitaremos programar el Port B de la VIA adecuadamente, ya que el Port A no permite la adaptación de forma automática de paralelo (del bus de datos: ocho bits) al canal serie que necesitamos.

El RS-232 funciona con lógica negativa. Esto quiere decir que cuando queremos transmitir un «0» debemos transmitir un valor de tensión positivo (+12, aunque permite en teoría cualquiera en el rango +5+15) y cuando deseamos transmitir un «1» negativo -12 (-5-15). Por estas razones, necesitamos hacer un cambio en el nivel de tensiones a la salida serie de la VIA, esto se puede hacer con el circuito de la figura 4.22. En ella se puede ver también unas indicaciones acerca del conector, el patillaje, etc.

Interface RS-232

Por cada canal de I/O necesitaremos un adaptador de nivel como el de la figura:

\* La puerta P forma parte del IC. 74LS27 (que tiene cuatro puertas NAND).

b

El conector RS 232/V24

- |                             |                                                                                  |

|-----------------------------|----------------------------------------------------------------------------------|

| 1. Masa del chasis *        | 9-14. No utilizados                                                              |

| 2. Emisión de datos ← a CB2 | 15. Bit de sincronización interno para emisión, a CB1                            |

| 3. Recepción de datos →     | 16. No utilizado                                                                 |

| 4. Solicitud de emisión *   | 17. Bit de sincronización de recepción, procede del emisor, a CB1                |

| 5. Lista para emitir *      | 18-19. No utilizados                                                             |

| 6. Bloque de datos listo *  | 20. Terminal de datos listo                                                      |

| 7. Masa de señal ⊥          | 21. No utilizado                                                                 |

| 8. Detección de portadora   | 22. Indicador de llamada entrante                                                |

|                             | 23. Selector de velocidad de transmisión                                         |

|                             | 24. Bit de sincronización de emisión hacia el dispositivo de transmisión (a CB1) |

|                             | 25. No utilizado                                                                 |

c

Una forma sencilla de conexión sería la siguiente:

Con este montaje (asíncrono) necesitaríamos dos cambiadores como el de la figura.

Fig. 4.22.

d

Expliquemos brevemente cómo se programa el PORT B de la VIA para la gestión serie ( $\rightarrow$  RS-232/V24).

#### Como entrada

bits ACR

234

Asíncrono

|     |                       |

|-----|-----------------------|

| 011 | $\rightarrow$ ACR: 76 |

| 001 |                       |

Síncrono

|    |  |

|----|--|

| 11 |  |

|----|--|

#### Como salida

bits ACR

234

Asíncrono

|     |                       |

|-----|-----------------------|

| 111 | $\rightarrow$ ACR: 76 |

| 100 |                       |

|    |  |

|----|--|

| 11 |  |

|----|--|

En el caso síncrono habrá que escribir en T1 (registro de la VIA) el período correspondiente.

Cada vez que llegue la señal de sincronismo por CB1 se provoca IRQ, que debe estar habilitada cuando se use el interfaz gestionándolo por interrupción: ver el capítulo sobre la VIA.

Dependiendo de las características que el usuario desee, se debe programar el registro de control de la VIA consecuentemente. En el programa máquina de gestión del Interface se explican más detalladamente los pasos a seguir.

```

1 ****

2 *          ;PROGRAMA EL REGISTRO AUXILIAR

3 *          ;DE CONTROL

4 *          ;IDEM REGISTRO DE CONTROL

5 *          ;HAY DOS PUNTOS DE ENTRADA

6 *          ;INRS PARA LA RUTINA DE ENTRADA

7 *          ;Y OUTRS PARA LA DE SALIDA

8 *

9 *

10 INRS    LDA ACRV      ;PROGRAMA EL REGISTRO AUXILIAR

11       AND #11100001  ;DE CONTROL

12       ORA #00001110

13       STA ACRV      ;IDEM REGISTRO DE CONTROL

14       LDA PCRV      ;RSFLAG=0 -> ENTRADA

15       AND #00001111

16       ORA #00000000

17       STA PCRV      ;IDEM REGISTRO DE CONTROL

18       LDA #0          ;RSFLAG=0 -> ENTRADA

19       STA RSFLAG

20       JMP CONTI

21 OUTRS   LDA ACRV      ;IDEM REGISTRO AUXILIAR DE

22       AND #11100001  ;CONTROL

23       ORA #00001110

24       STA ACRV      ;IDEM REGISTRO DE CONTROL

25       LDA PCRV      ;IDEM REGISTRO DE CONTROL

26       AND #00000111

27       ORA #00000000

28       STA PCRV      ;RSFLAG=1 -> SALIDA

29       LDA #1          ;RSFLAG=1 -> SALIDA

30       STA RSFLAG

31 CONTI   LDA #0          ;ACTIVAMOS LA INTERRUPCION

32       STA IFRU      ;CORRESPONDIENTE

33       LDA IERU

34       ORA #10000100

35       STA IERU

36       CLI

37       RTS

```

Como se observa en el programa, la velocidad de transmisión es programable por software, por lo que podrá variar según la aplicación.

## AMPLIACIONES

Con lo visto hasta ahora ya tenemos la versión básica de nuestro ordenador. Por sobrar líneas de los puertos de entrada salida que se pueden usar para posibles ampliaciones.

Para añadirle más memoria a nuestro ordenador será necesario colocar más decodificadores para generar la señal de selección de chips, según la cantidad de memoria que queramos añadir. Para ello, debemos observar en el mapa de memoria qué zonas están libres.

Como conexión mínima:

Una vez vista la zona en la que queremos colocar la memoria debemos ver qué direcciones, en binario, le corresponden; con ello diseñaremos un circuito combinacional que detecte dichas direcciones.

## E

N este capítulo trataremos de la «inteligencia» del ordenador. Con un mismo hardware se pueden realizar muchas funciones distintas, que sólo dependerán de la imaginación de quien realice los programas.

Para guardar el programa seleccionamos una EPROM capaz de almacenar 2 Kbytes (2048 bytes), por ser las más fáciles de localizar en el mercado y aunque pueda parecer extraño, son más baratas que las EPROM de 1 Kbyte (1024 bytes) (porque al ser más antiguas escasean en el mercado).

De todas formas, siempre podremos utilizar lo que sobra de RAM para introducir programas.

Por ello, realizamos dos tipos de programas: un pequeño editor que nos permita introducir nuestros programas en código máquina, depurárselos y ejecutarlos, y un programa de reloj de veinticuatro horas, que permita ejecutar una rutina definida por el usuario al llegar una hora predeterminada.

Junto a estos programas existen diversas rutinas, que éstos utilizan, que gestionan los recursos del sistema, tales como el teclado, el display, los interfaces serie y paralelo.

Siempre podremos poner en la RAM libre nuestras propias aplicaciones; además, la mitad de la EPROM está vacía. En ella podemos almacenar nuestras utilidades.

## EDITOR

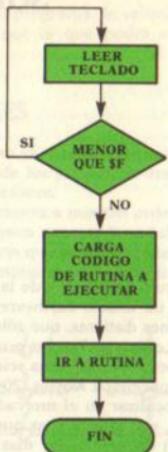

La parte principal de este programa está realizado por un bucle que espera que se pulse alguna tecla.

Si la tecla pulsada es de alguna de las funciones, lo que detecta por ser su código mayor que \$F, ejecuta la rutina.

Fig. 5.1. Organigrama del bucle principal.

Para la ejecución de dicha función toma la dirección de una tabla, indexándola con el código de dicha función.

Almacena dicho dato en FUNC y ejecuta un salto indirecto a dicha posición, con lo que la dirección efectiva es la que almacenamos anteriormente.

|    |             |                          |

|----|-------------|--------------------------|

| 13 | SBC #10     | ;TRANSFORMAR TECLA       |

| 14 | ASL         | ;EN VALOR                |

| 15 | TAX         | ;PARA CALCULAR DIRECCION |

| 16 | LDA TABLA,X | ;DE LA FUNCION           |

| 17 | STA FUNC    |                          |

| 18 | INX         |                          |

| 19 | LDA TABLA,X |                          |

| 20 | STA FUNC+1  |                          |

| 21 | JMP (FUNC)  | ;EJECUTA LA FUNCION      |

Veamos ahora las distintas funciones del editor.

Para observar el contenido de una posición de memoria pulsaremos la tecla de función DIR, seguida de cuatro cifras hexadecimales, que serán la dirección a observar.

En el display aparecerá la dirección pulsada y el dato contenido en ella, en hexadecimal.

Si queremos observar el contenido de la dirección de memoria siguiente bastará con pulsar la tecla +.

Para observar el contenido de la anterior posición de memoria pulsaremos la tecla -.

Si ahora queremos modificar la posición de memoria cuyo contenido estamos observando bastará con pulsar la tecla de función DATO y dos cifras hexadecimales que representarán el nuevo contenido de dicha posición de memoria.

Con esto podemos observar y modificar cualquier posición de memoria de nuestro ordenador, pero ¿cómo ejecutar un programa?

Para ejecutar un programa pulsaremos DIR y la dirección en que comienza el programa. Después pulsaremos RUN y dicho programa comenzará a ejecutarse.

Además de observar las posiciones de memoria podríamos querer observar y modificar los registros internos de la CPU.

Para observar el contenido de cualquier registro pulsaremos, sucesivamente, las teclas DIR, DATO y una tercera que representará el código del registro a visualizar. Los códigos son:

- A para el acumulador

- 0 para el registro X

- 1 para el registro Y

- 2 para el registro de status

- 3 para el puntero del stack

Una vez realizada la anterior función si queremos modificar alguno de estos registros bastará con pulsar la tecla DATO y las dos cifras hexadecimales que representen el nuevo contenido.

## NECESIDADES SOFTWARE

Si realizas el que aquí aparece entenderás lo siguiente: