# DGITAL COMPUTER 2 FUNDAMENTALS

SIXTH EDITION

THOMAS C. BARTEE

## A Lasting Tribute

Presented to the

UNIVERSITY OF INDIANAPOLIS

KRANNERT MEMORIAL LIBRARY

In Memory of

Mrs. Fern Nicoson Eder

by

Mr. James Eder

## DIGITAL COMPUTER FUNDAMENTALS

## DIGITAL COMPUTER FUNDAMENTALS SIXTH EDITION

#### THOMAS C. BARTEE

Harvard University

#### McGRAW-HILL BOOK COMPANY

New York | St. Louis | San Francisco | Auckland | Bogotá | Hamburg Johannesburg | London | Madrid | Mexico | Montreal | New Delhi Panama | Paris | São Paulo | Singapore | Sydney | Tokyo | Toronto

UNIVERSITY OF INDIANAPOLIS

Krannert Memorial Library

#### DIGITAL COMPUTER FUNDAMENTALS

Copyright © 1985, 1981, 1977, 1972, 1966, 1960 by McGraw-Hill, Inc.

All rights reserved.

Printed in the United States of America.

Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in data base or retrieval system,

1234567890 DOCDOC 8987654

without the prior written permission of the publisher.

4-66800-20-0 NASI

This book was set in Times Roman by Waldman Graphics, Inc.

The editors were Sanjeev Rao and J. W. Maisel; the designer was Nicholas Krenitsky;

the production supervisor was Diane Renda.

New drawings were done by J & R Services, Inc.

R. R. Donnelly & Sons Company was printer and binder.

#### Library of Congress Cataloging in Publication Data

Bartee, Thomas C.

Digital computer fundamentals.

### CONTENTS

#### PREFACE xi

#### 4

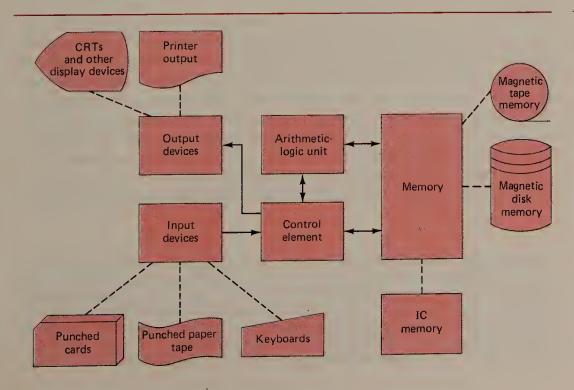

#### COMPUTER OPERATION 1

| 1.1  | Electronic Digital Computers                   | 2           |

|------|------------------------------------------------|-------------|

| 1.2  | Application of Computers to Problems           | 3<br>5<br>6 |

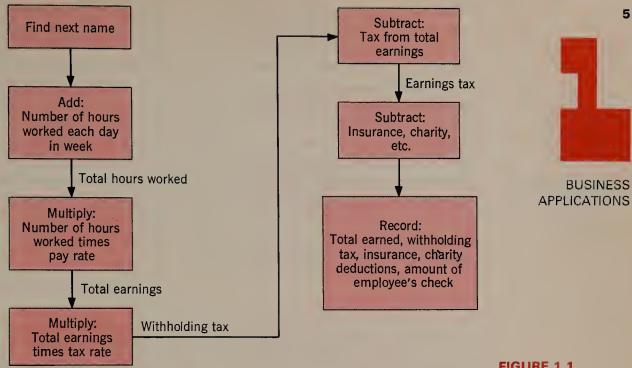

| 1.3  | Business Applications                          | 5           |

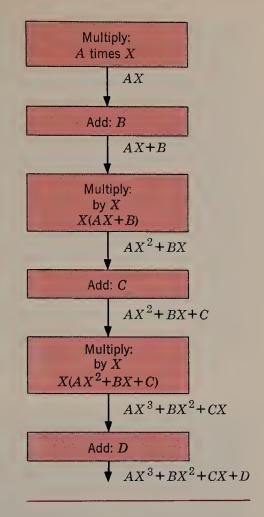

| 1.4  | Scientific Applications                        | 6           |

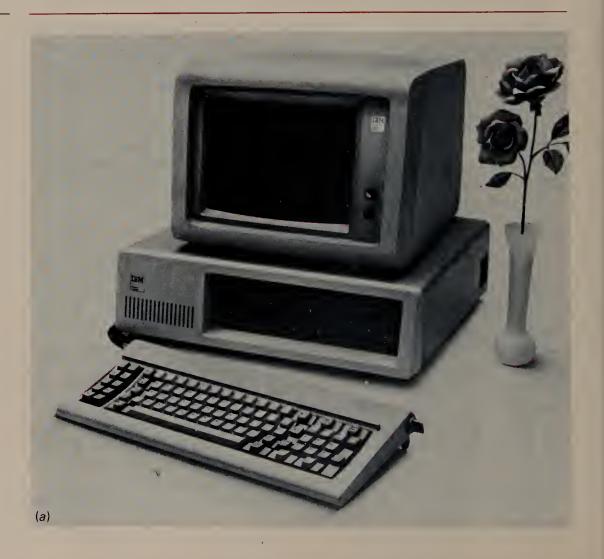

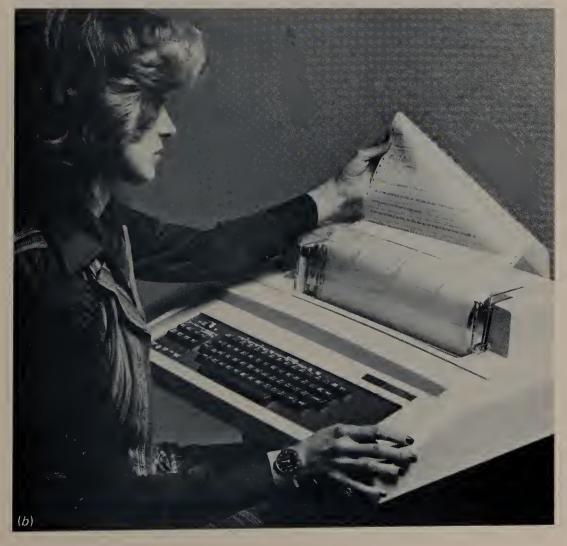

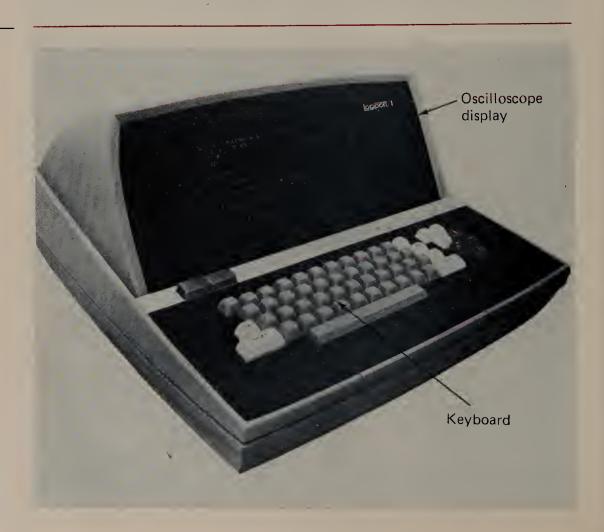

| 1.5  | Some Different Types of Computer Systems       | /           |

| 1.6  | Computers in Control Systems                   | 11          |

| 1.7  | Basic Components of a Digital Computer         | 13          |

| 1.8  | Construction of Memory                         | 14          |

| 1.9  | Instructions                                   | 15          |

| 1.10 | Multiplication Instruction                     | 17          |

| 1.11 | Branch, Skip, or Jump Instructions             | 18          |

| 1,12 | Programming Systems                            | 20          |

| 1.13 | Assembly Languages                             | 2′          |

| 1.14 | High-Level Languages                           | 23          |

| 1.15 | A Short Introduction to Higher-Level Languages | 23          |

| 1.16 | Summary                                        | 27          |

|      |                                                |             |

vi

CONTENTS

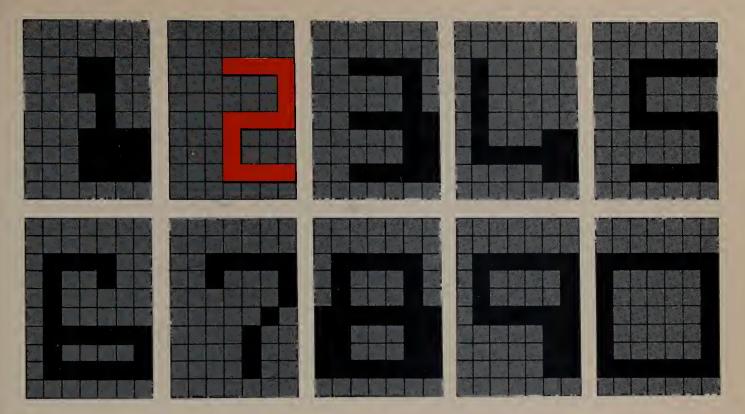

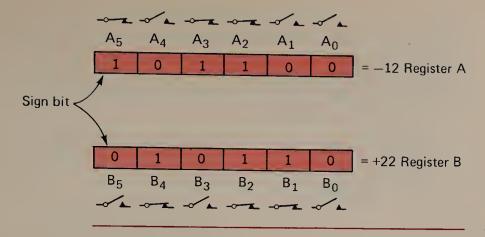

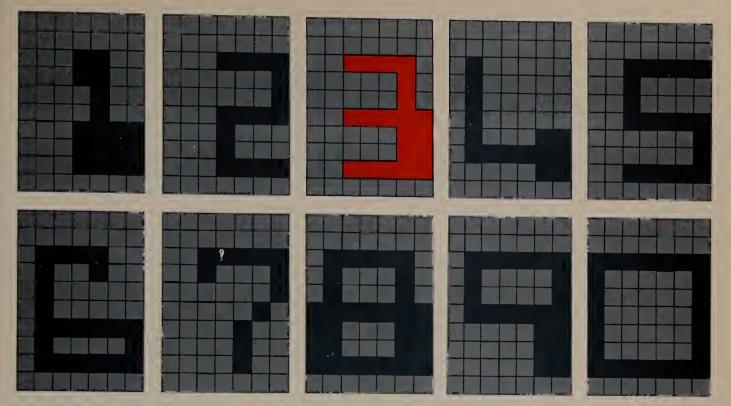

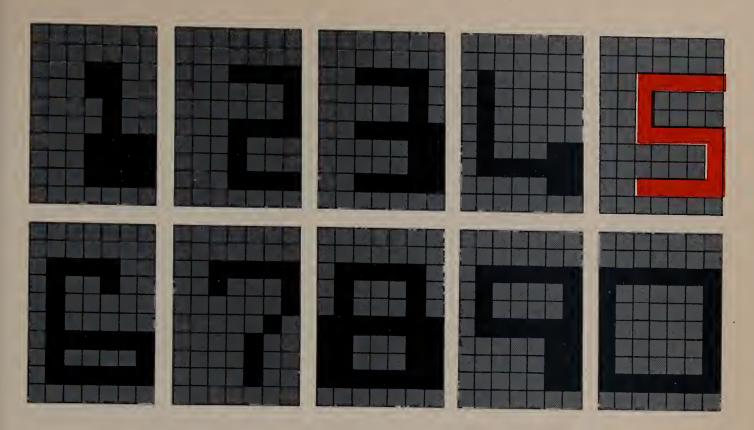

#### NUMBER SYSTEMS 33

| 2.1          | Decimal System                                                     | 3        |

|--------------|--------------------------------------------------------------------|----------|

| 2.2          | Bistable Devices                                                   | 3:       |

| 2.3          | Counting in the Binary System                                      | 3        |

| 2.5          | Binary Addition and Subtraction Binary Multiplication and Division | 3        |

| 2.6          | ,                                                                  | 3        |

| 2.7          | Converting Decimal Numbers to Binary Negative Numbers              | 39       |

| 2.7          | Use of Complements to Represent Negative Numbers                   | 40<br>41 |

| 2.9          | Complements in Other Number Systems                                | 4(       |

| 2.10         | Binary Number Complements                                          | 43       |

| 2.11         | Binary-Coded-Decimal Number Representation                         | 44       |

| 2.12         | Octal and Hexadecimal Number Systems                               | 46       |

| 2.13         | Summary                                                            | 5        |

| 2.10         |                                                                    | 5        |

|              | BOOLEAN ALGEBRA AND GATE NETWORKS 59                               |          |

| 3.1          | Fundamental Concepts of Boolean Algebra                            | 60       |

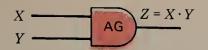

| 3.2          | Logical Multiplication                                             | 61       |

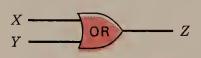

| 3.3          | AND Gates and OR Gates                                             | 62       |

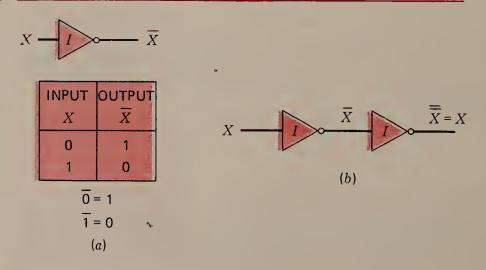

| 3.4          | Complementation and Inverters                                      | 63       |

| 3.5          | Evaluation of Logical Expressions                                  | 65       |

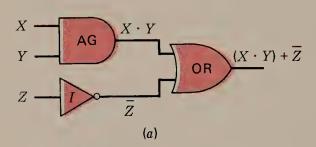

| 3.6          | Evaluation of an Expression Containing Parentheses                 | 66       |

| 3.7          | Basic Laws of Boolean Algebra                                      | 67       |

| 3.8          | Proof by Perfect Induction                                         | 70       |

| 3.9          | Simplification of Expressions                                      | 71       |

| 3.10         | De Morgan's Theorems                                               | 71       |

| 3.11         | Basic Duality of Boolean Algebra                                   | 72       |

| 3.12         | Derivation of a Boolean Expression                                 | 73       |

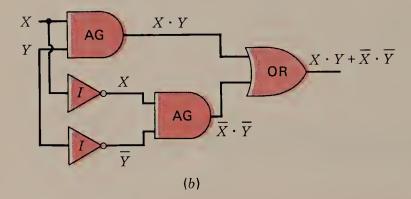

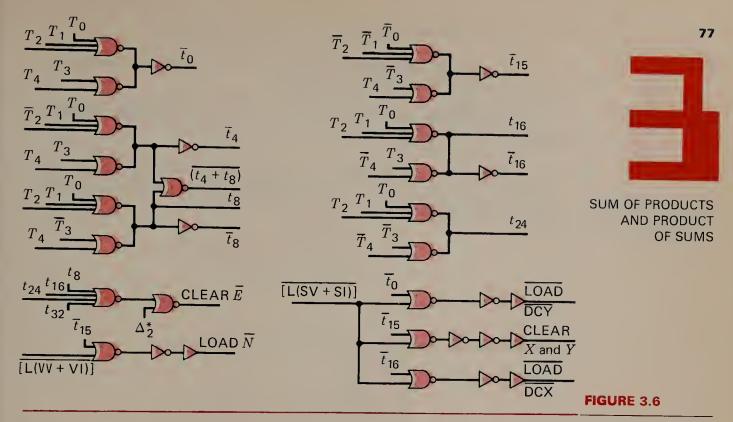

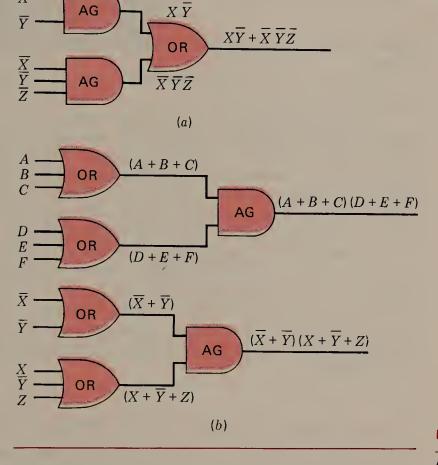

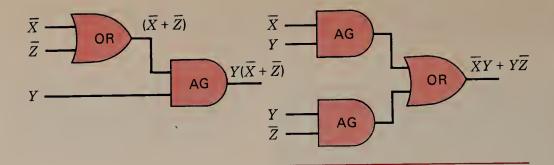

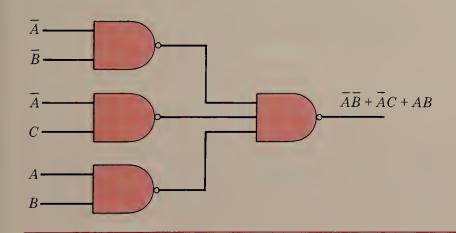

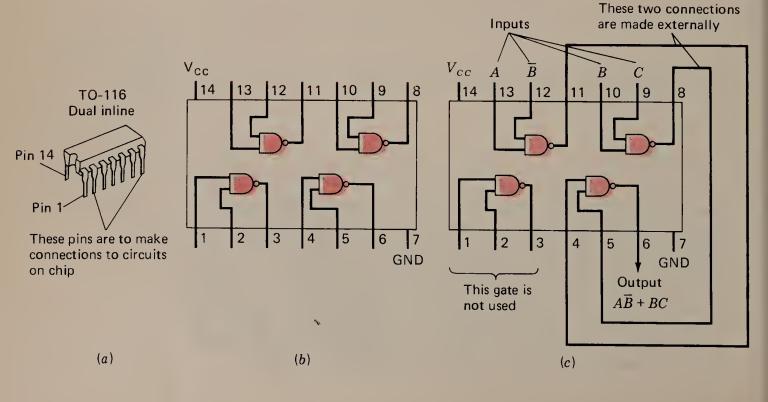

| 3.13         | Interconnecting Gates                                              | 76       |

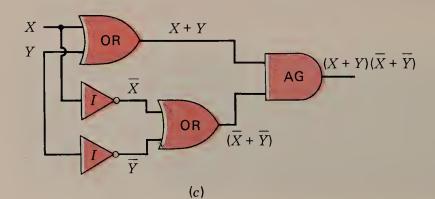

| 3.14         | Sum of Products and Product of Sums                                | 77       |

| 3.15         | Derivation of Product-of-Sums Expressions                          | 78       |

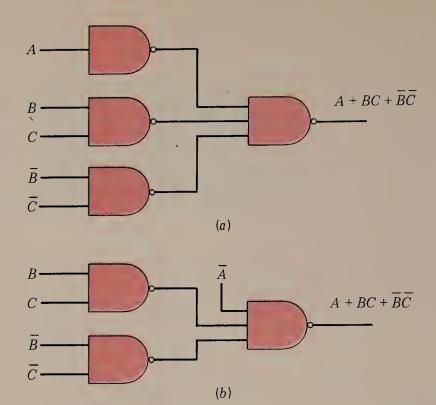

| 3.16         | Derivation of Three-Input-Variable Expression                      | 80       |

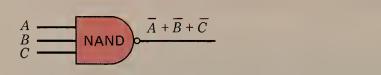

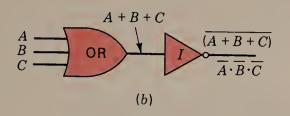

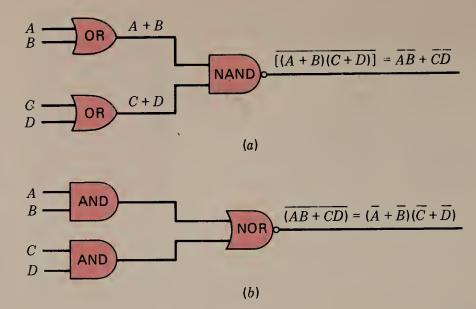

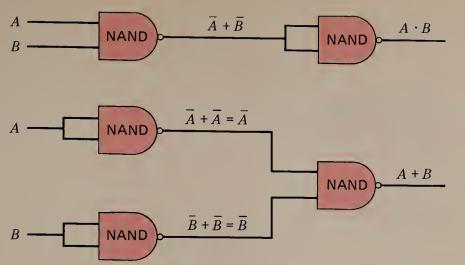

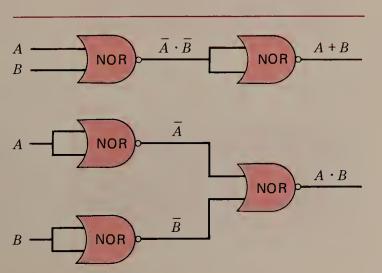

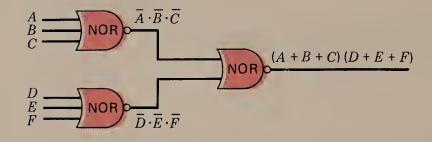

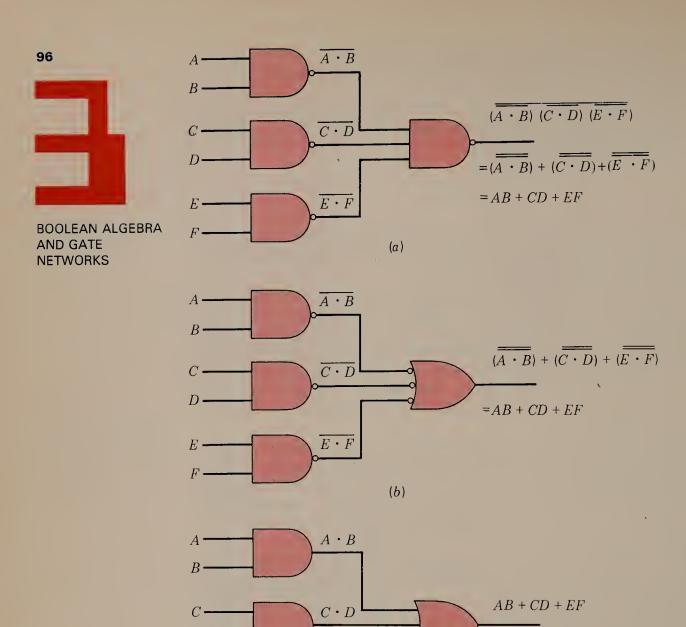

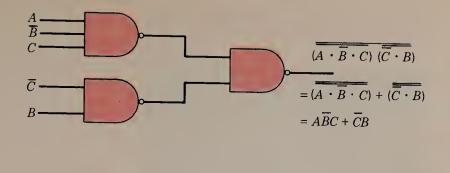

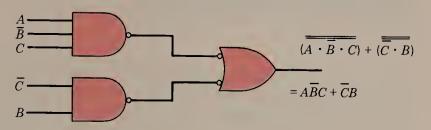

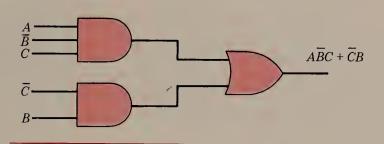

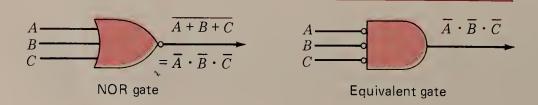

| 3.17         | NAND Gates and NOR Gates                                           | 82       |

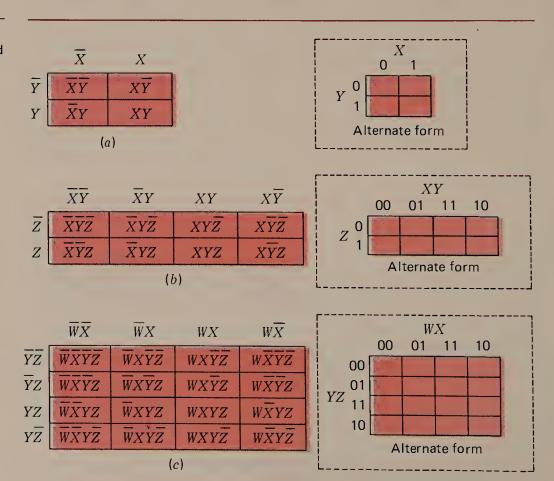

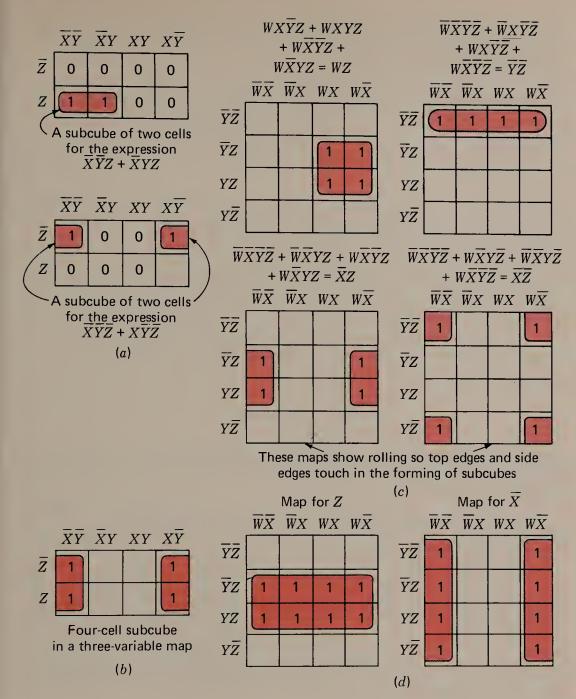

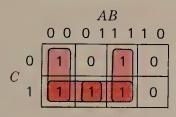

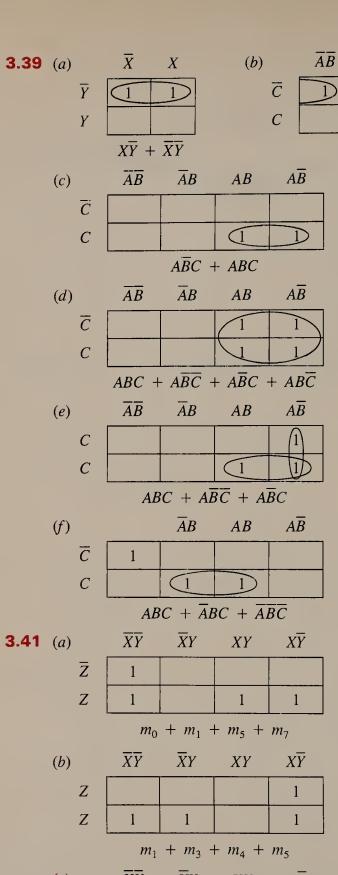

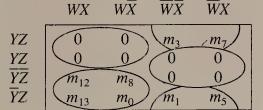

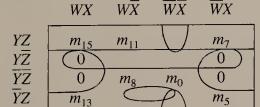

| 3.18         | The Map Method for Simplifying Expressions                         | 84       |

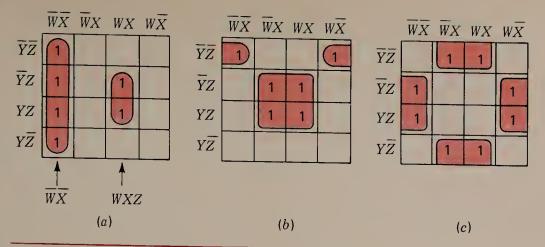

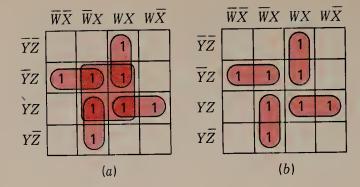

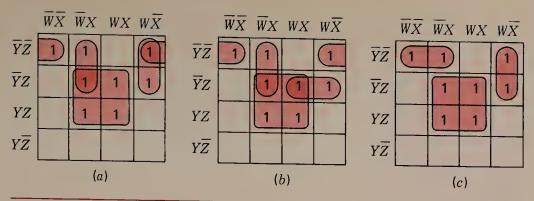

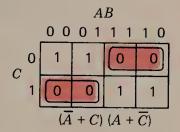

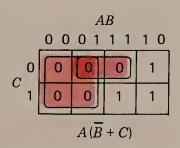

| 3.19         | Subcubes and Covering                                              | 88       |

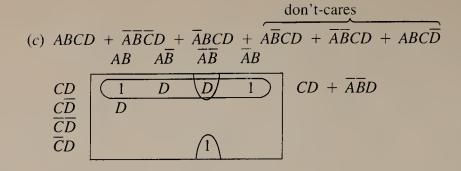

| 3.20         | Product-of-Sums Expressions—Don't-Cares                            | 93       |

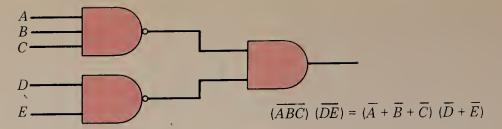

| 3.21         | Design Using NAND Gates                                            | 95       |

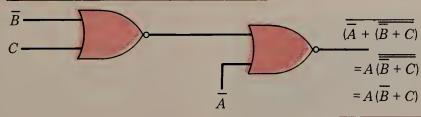

| 3.22         | Design Using NOR Gates                                             | 98       |

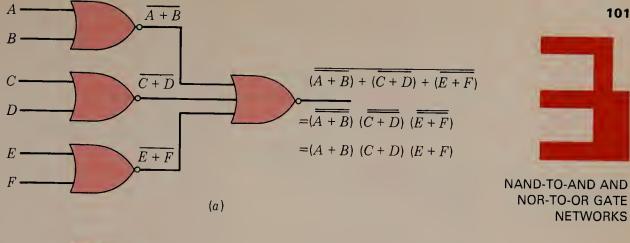

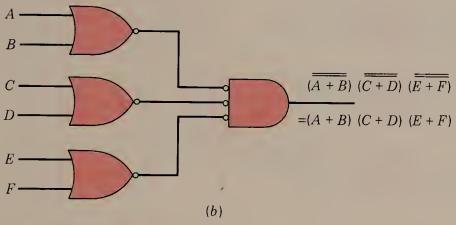

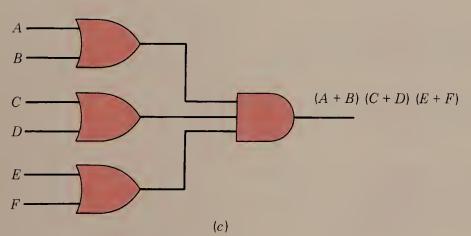

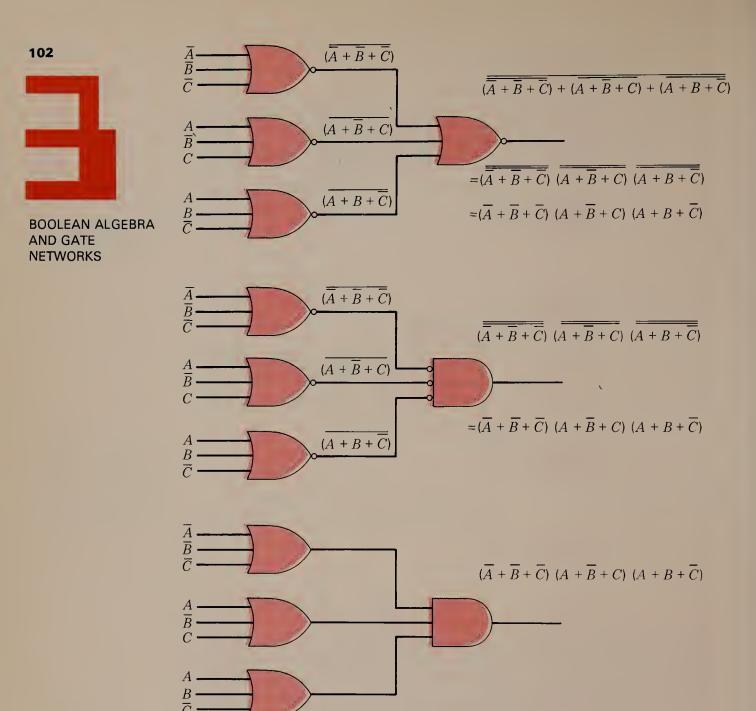

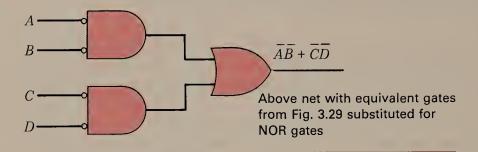

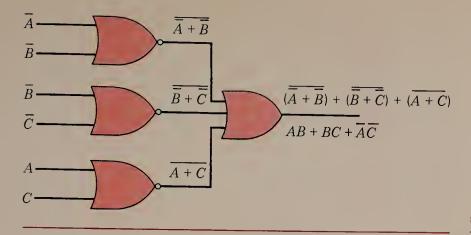

| 3.23         | NAND-to-AND and NOR-to-OR Gate Networks                            | 101      |

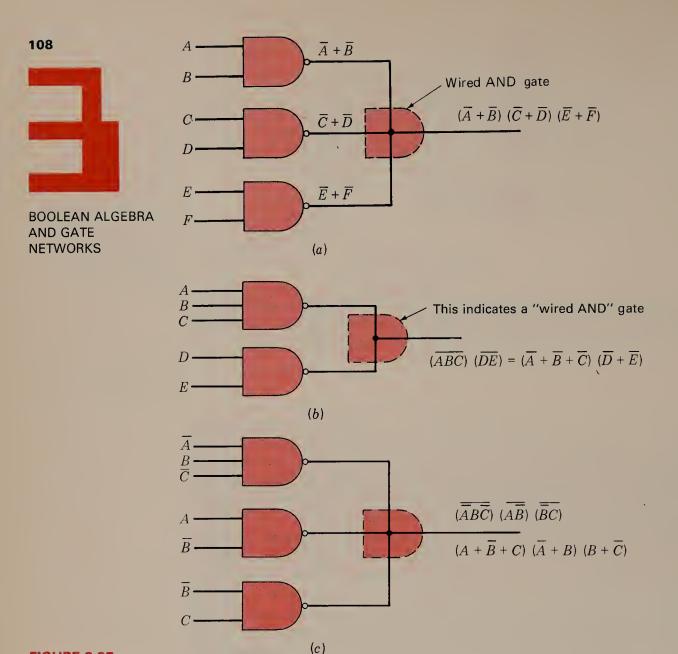

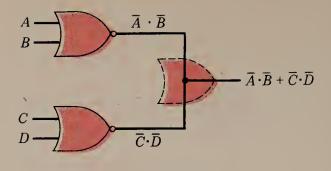

| 3.24<br>3.25 | Wired OR and Wired AND Gates                                       | 107      |

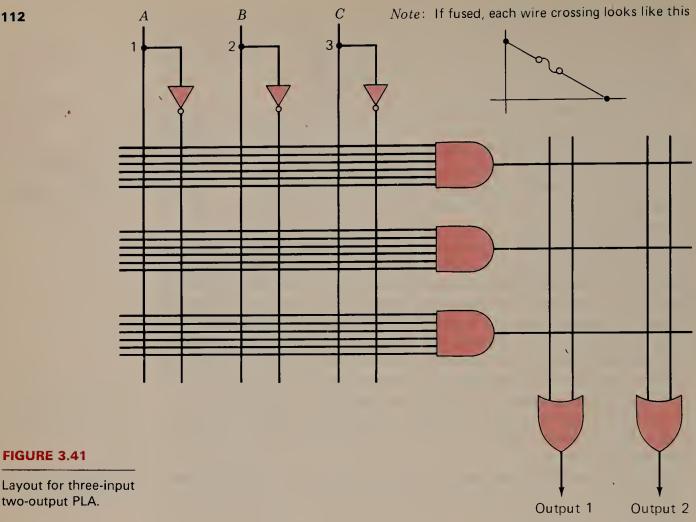

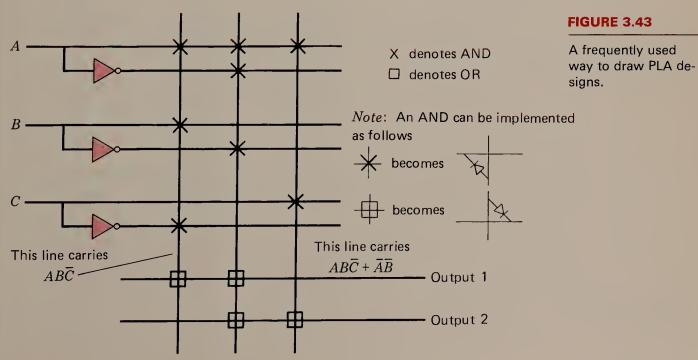

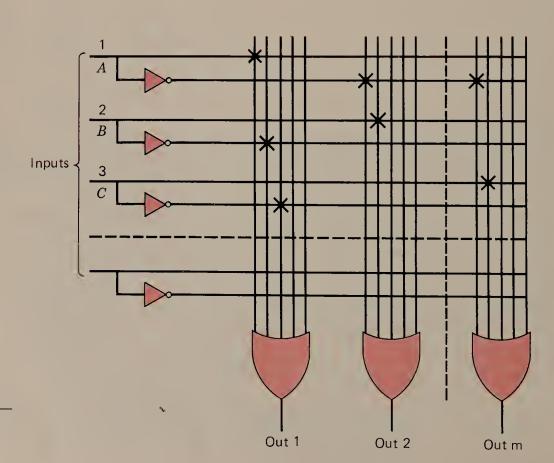

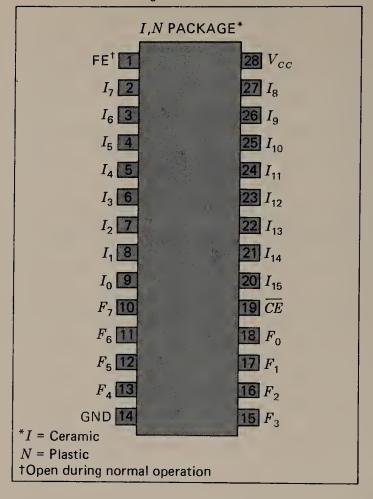

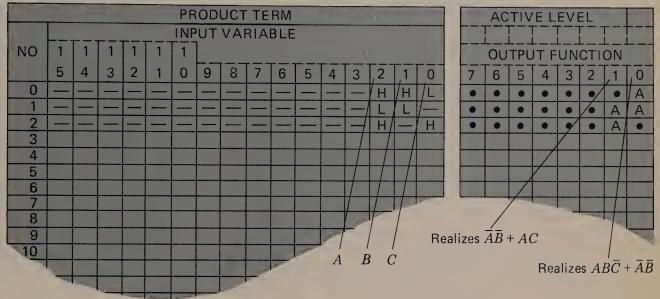

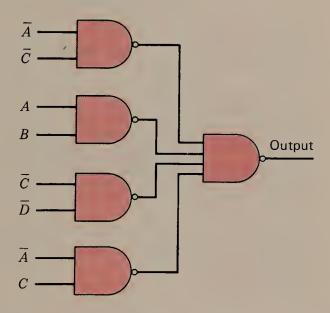

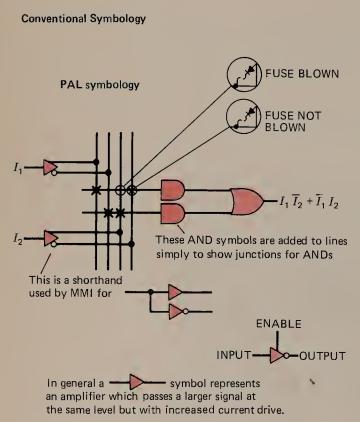

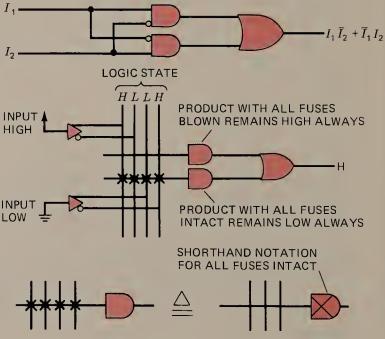

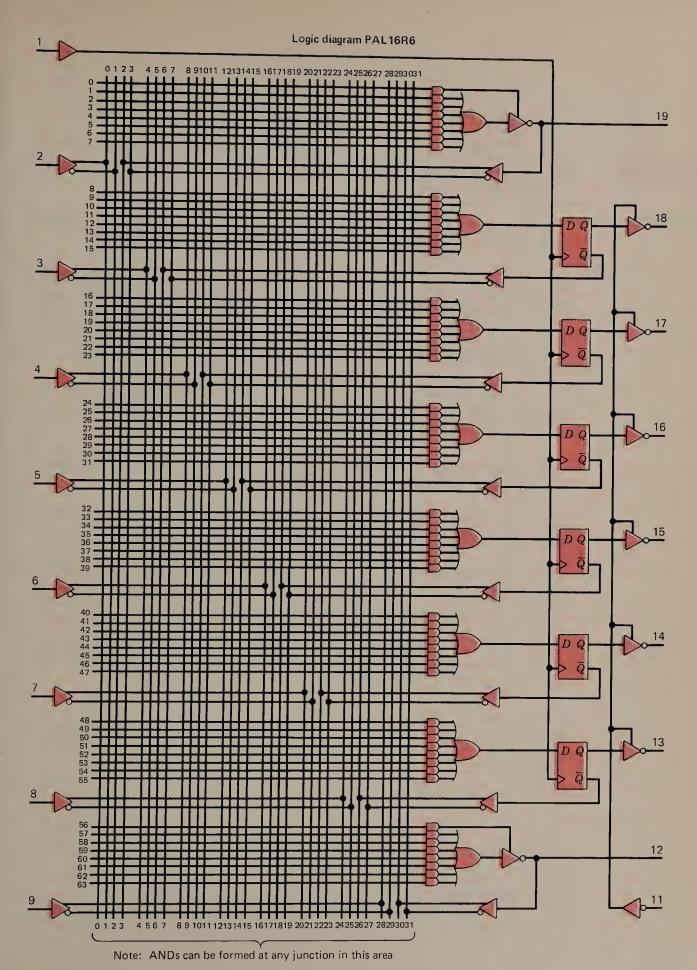

| 3.25         | PLAs and PALs                                                      | 109      |

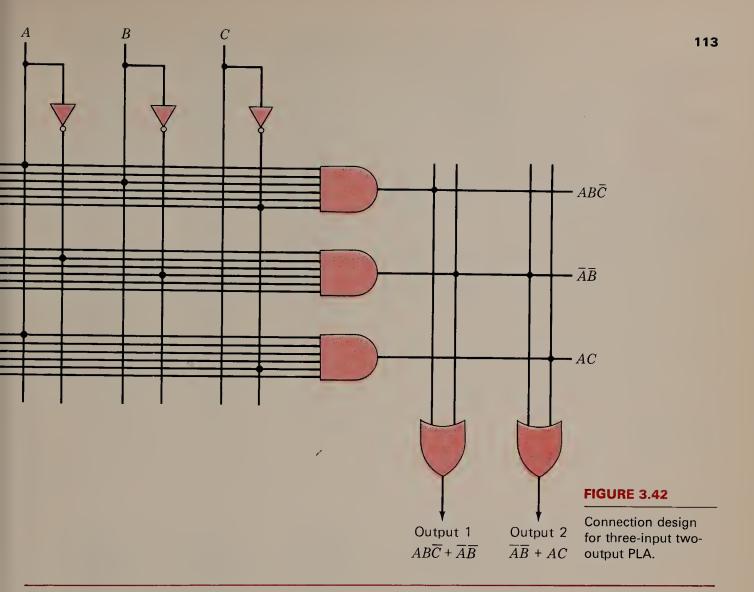

| 3.27         | Example of a Design Using a PLA                                    | 116      |

| 3.27         | Summary                                                            | 110      |

4 vii

|             | LOGIC DESIGN 135                                  |            | 001177170 |

|-------------|---------------------------------------------------|------------|-----------|

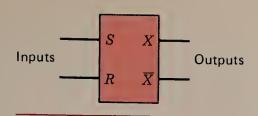

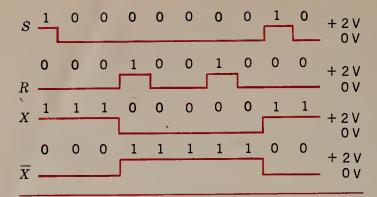

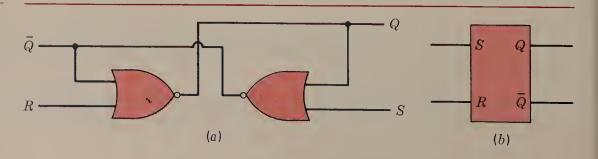

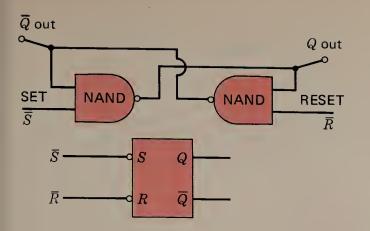

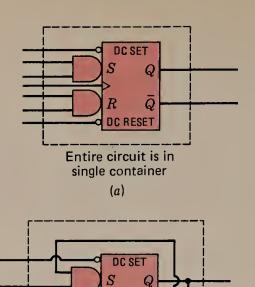

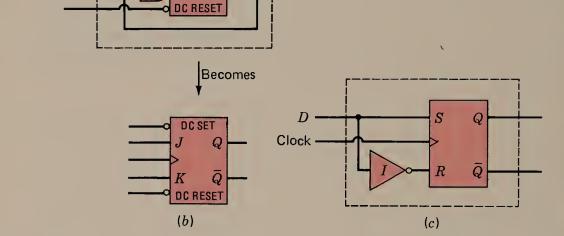

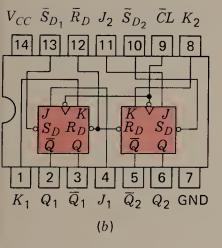

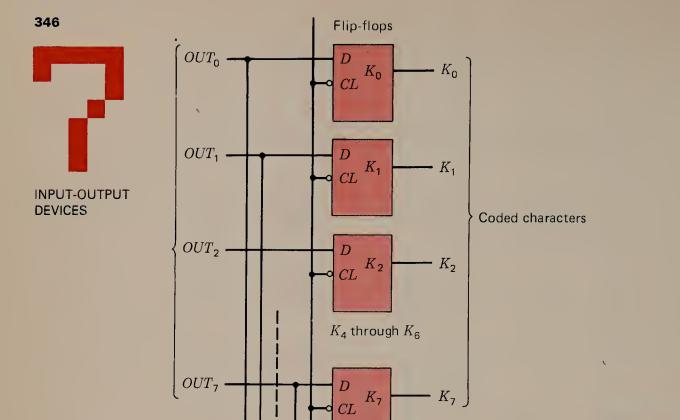

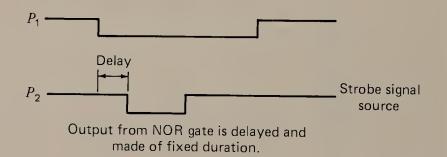

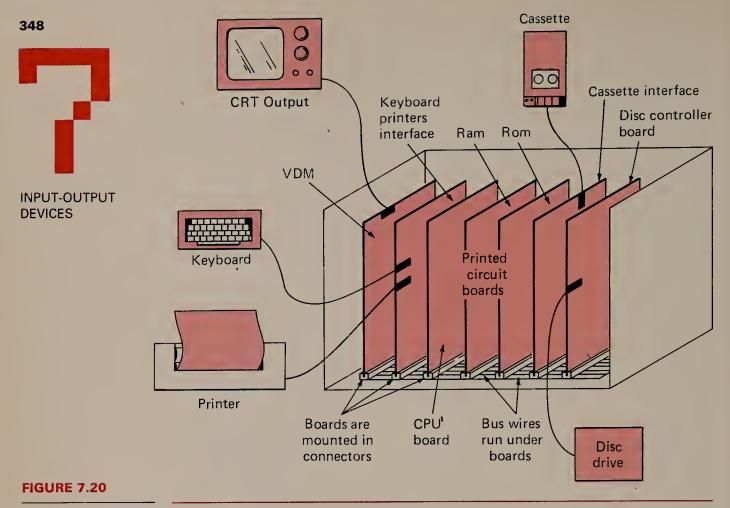

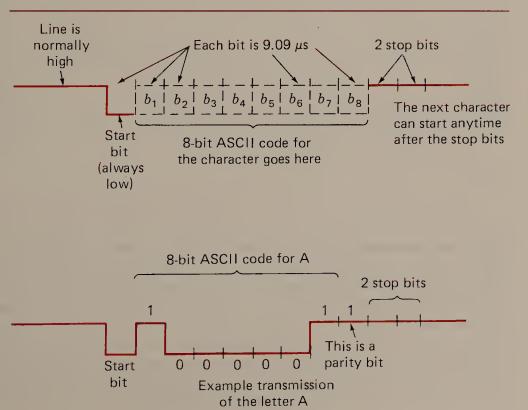

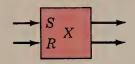

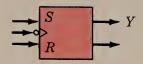

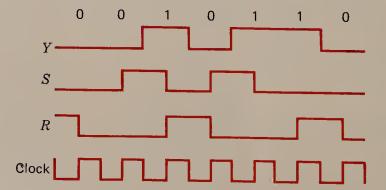

| 4.1         | Flip-Flops                                        | 136        | CONTENTS  |

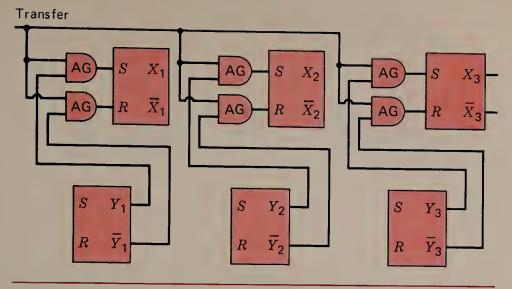

| 4.2         | Transfer Circuits                                 | 138        |           |

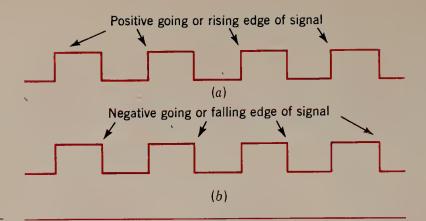

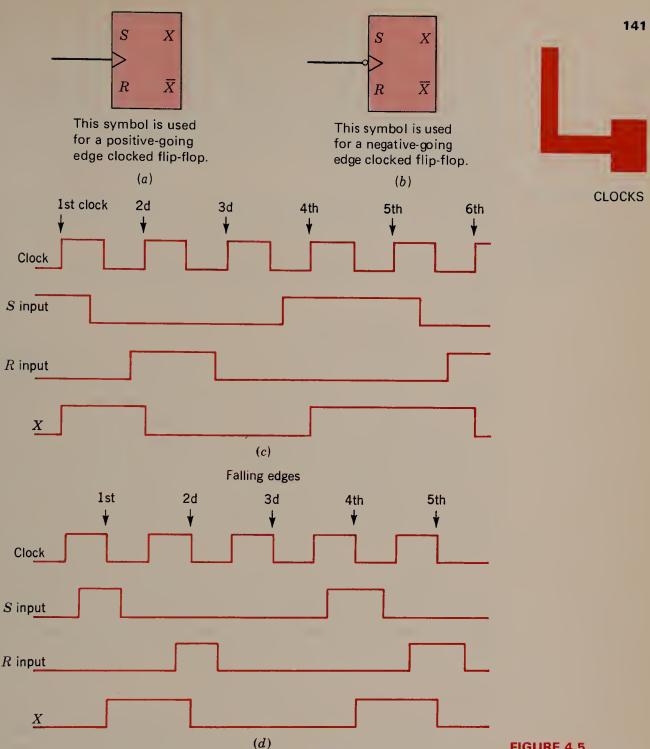

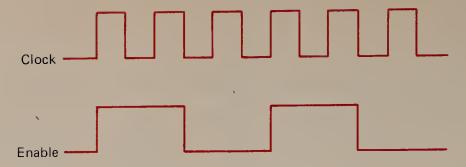

| 4.3         | Clocks                                            | 139        |           |

| 4.4         | Flip-Flop Designs                                 | 142        |           |

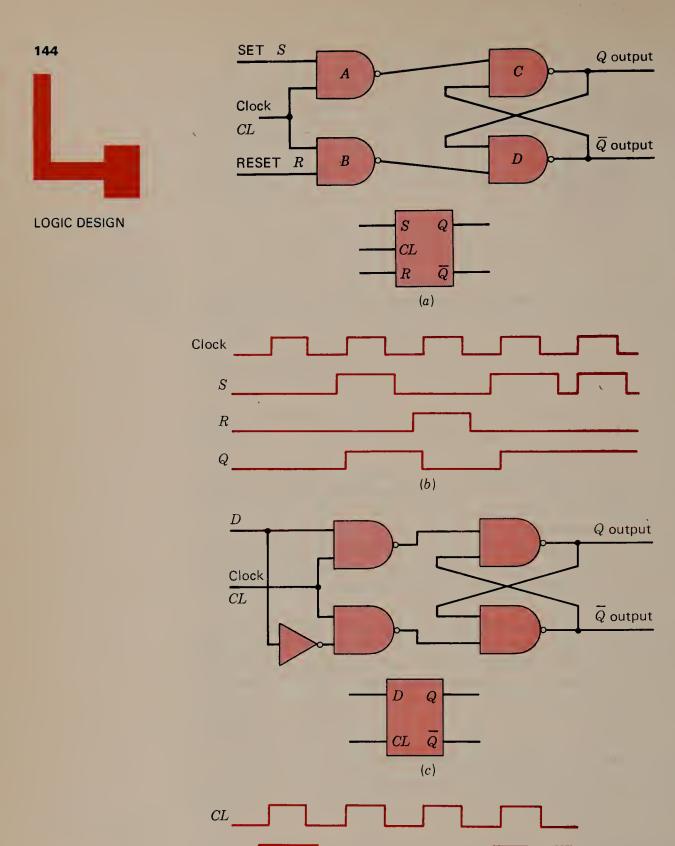

| 4.5         | Gated Flip-Flop                                   | 142        |           |

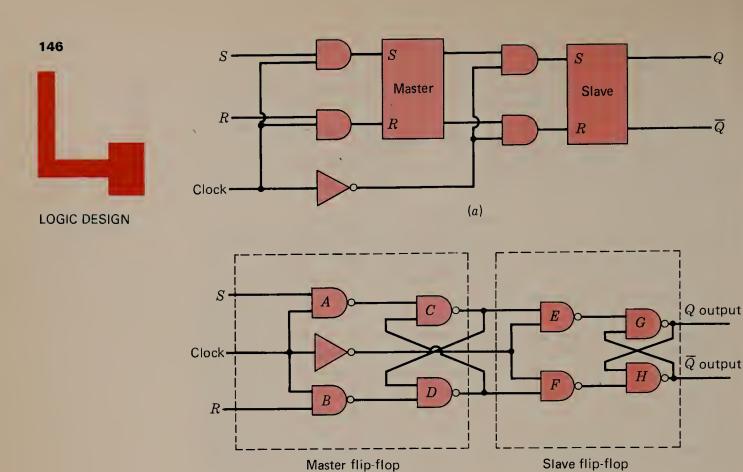

| 4.6         | Master-Slave Flip-Flop                            | 144        |           |

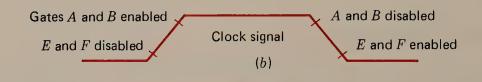

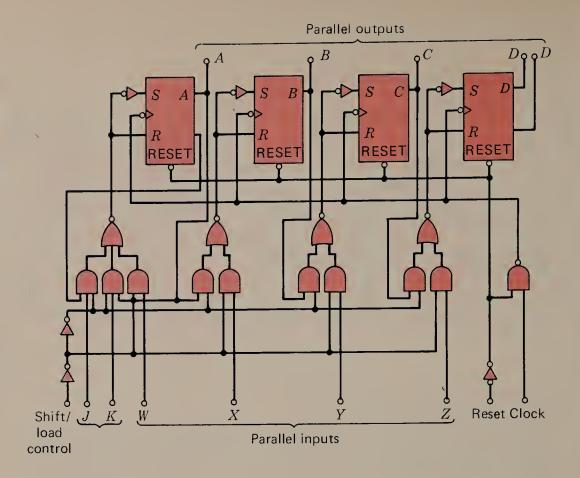

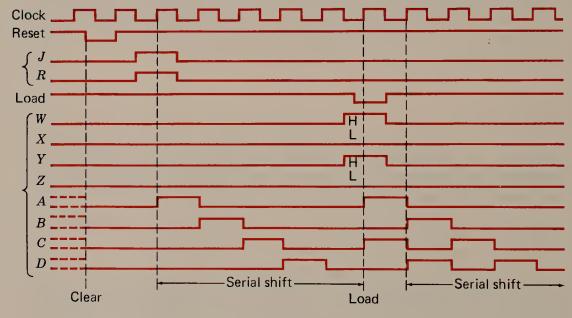

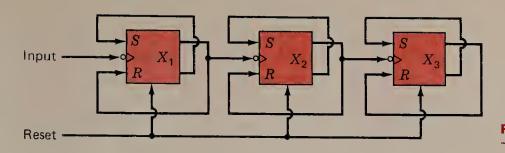

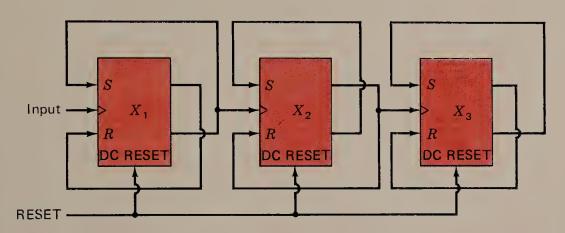

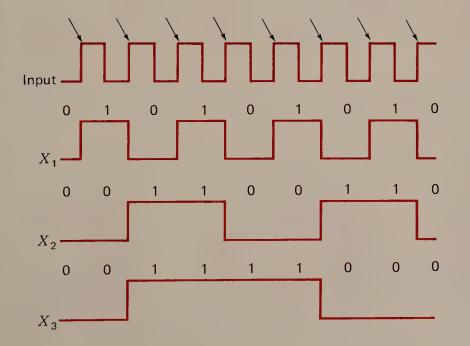

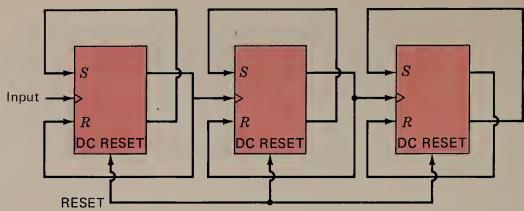

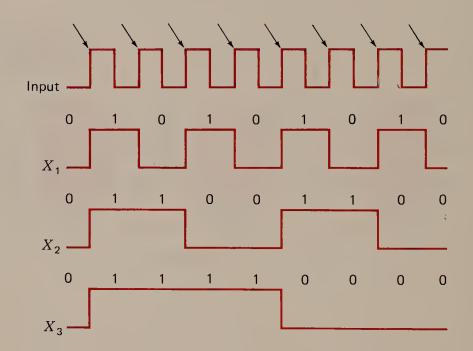

| 4.7         | Shift Register                                    | 147        |           |

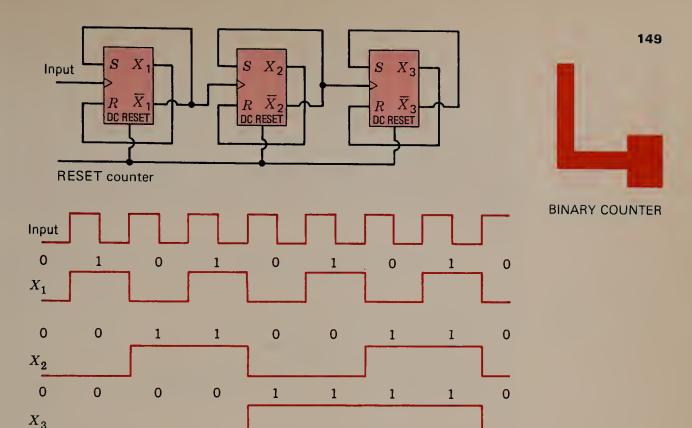

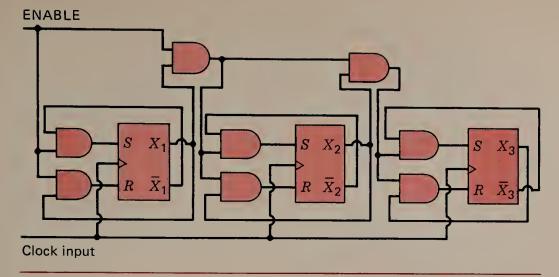

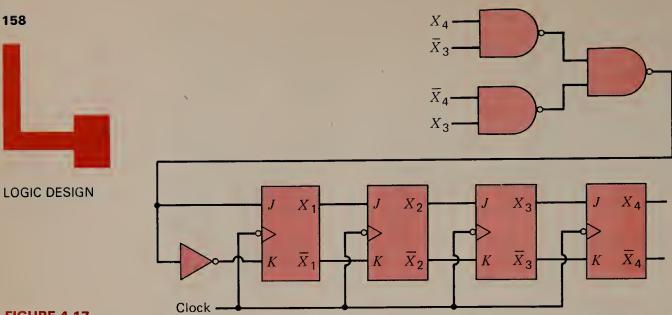

| 4.8         | Binary Counter                                    | 148        |           |

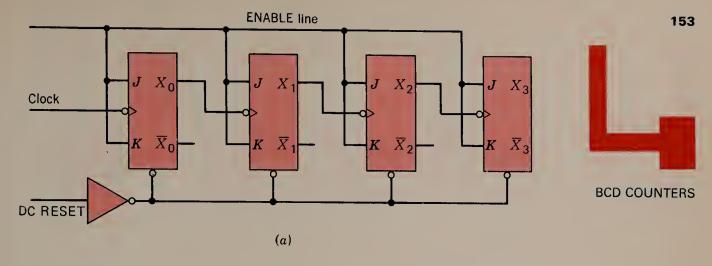

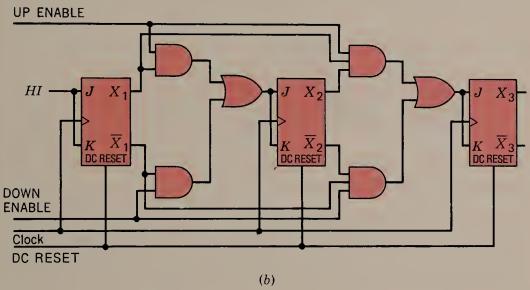

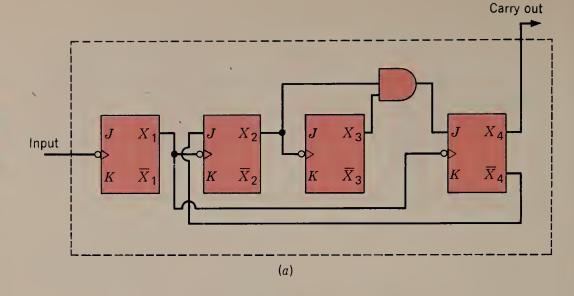

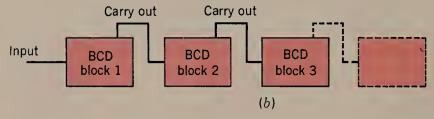

| 4.9         | BCD Counters                                      | 153        |           |

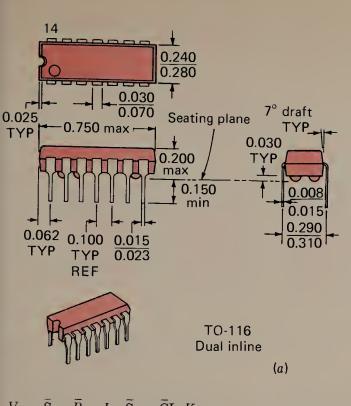

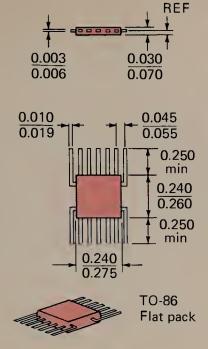

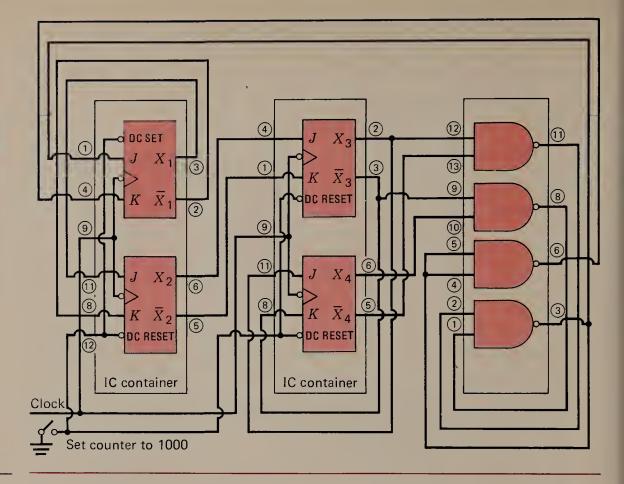

| 4.10        | Integrated Circuits                               | 155        |           |

| 4.11        | Medium-, Large-, and Very Large Scale Integration | 162        |           |

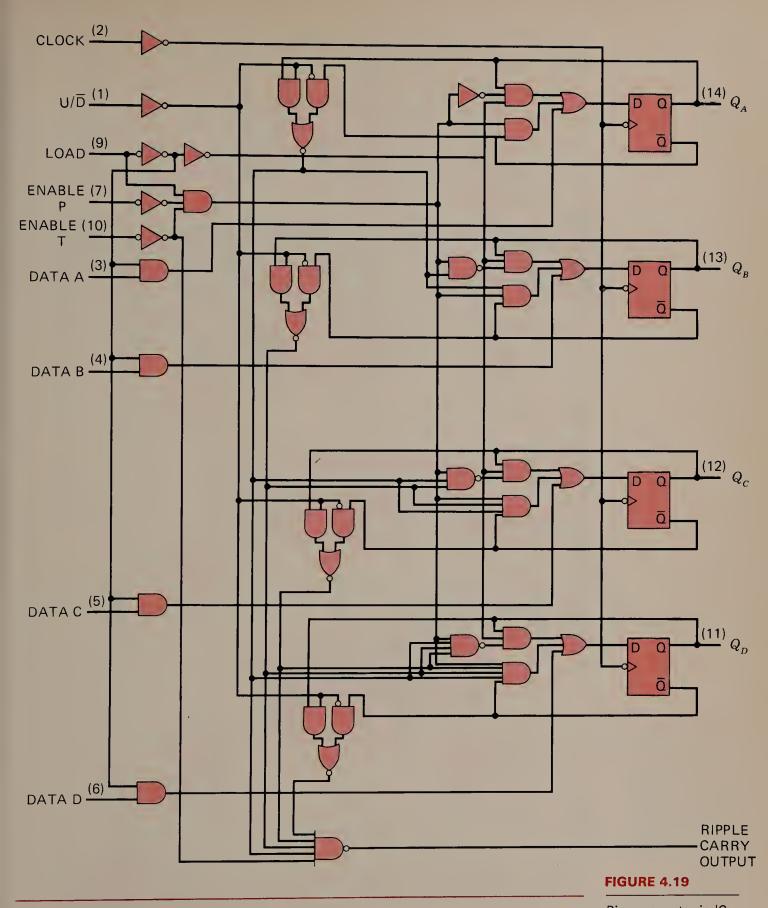

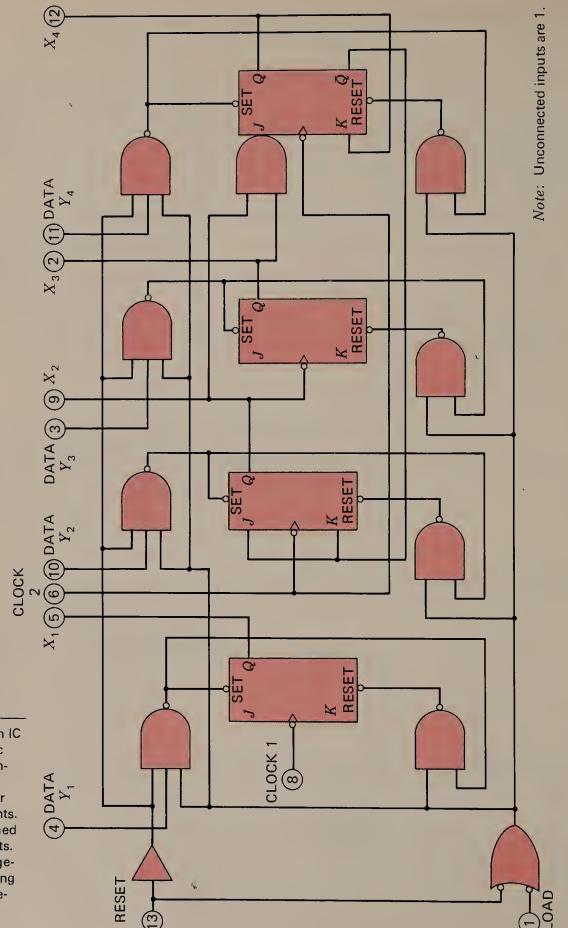

| 4.12        | Counter Design                                    | 166        |           |

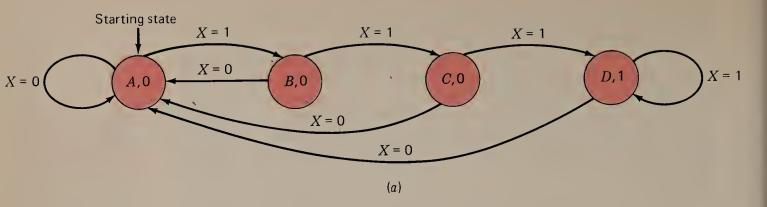

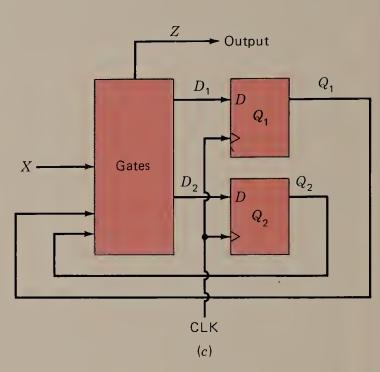

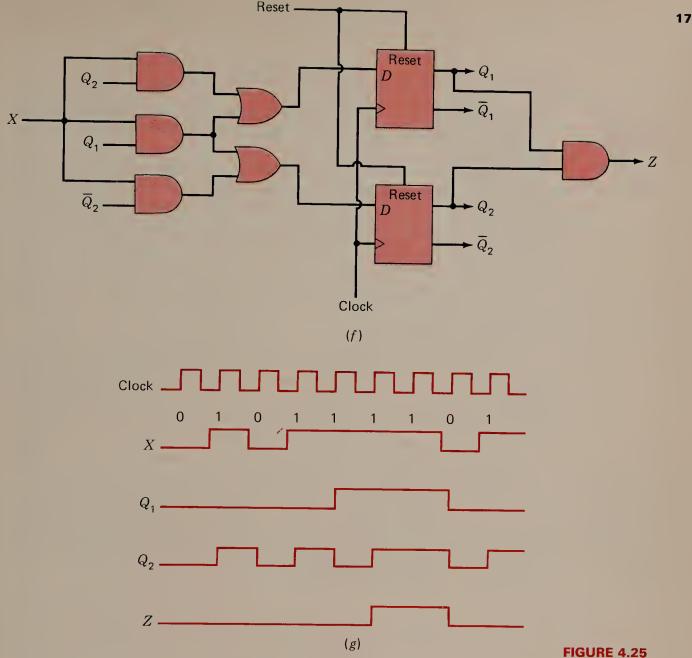

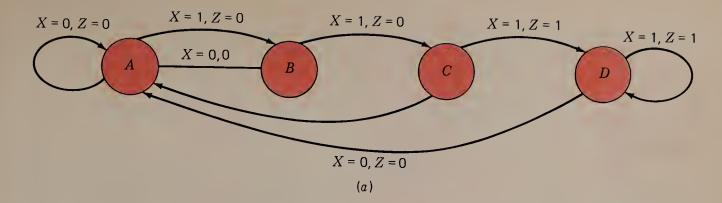

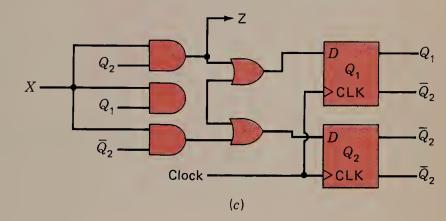

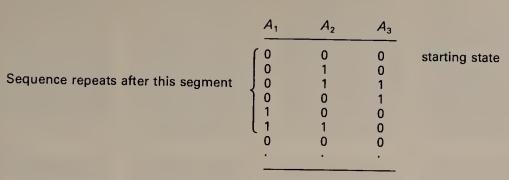

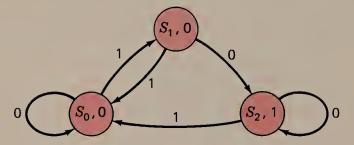

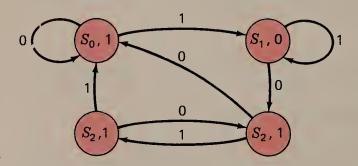

| 4.13        | State Diagrams and State Tables                   | 170        |           |

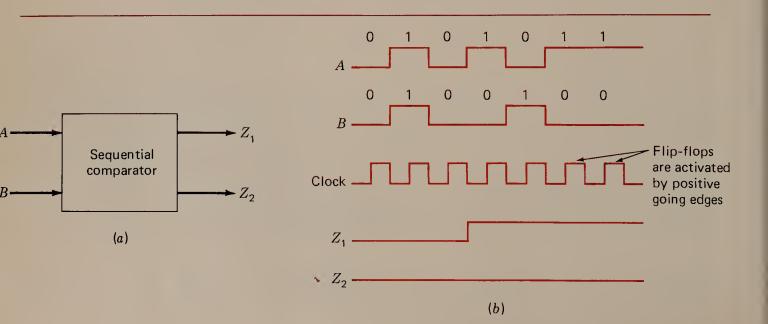

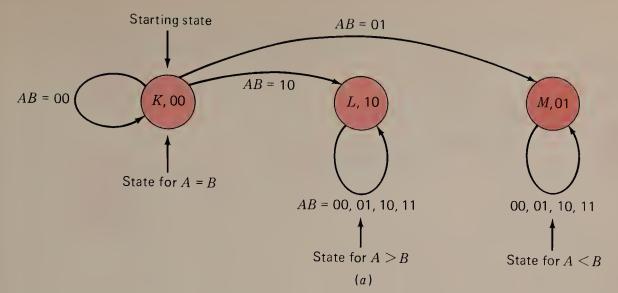

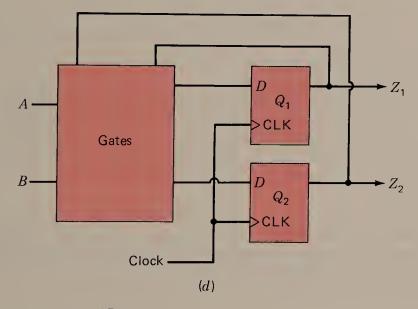

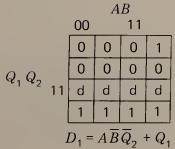

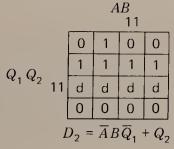

| 4.14        | Design of a Sequential Magnitude Comparator       | 176        |           |

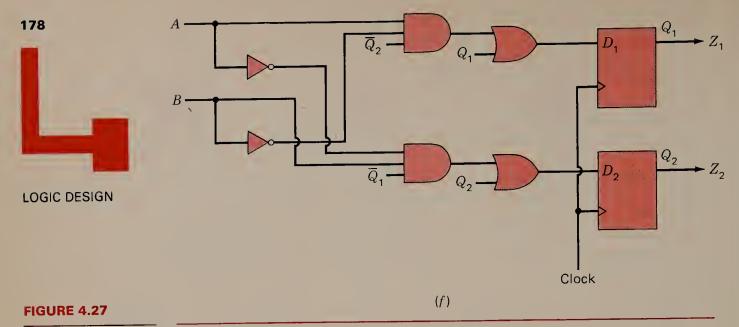

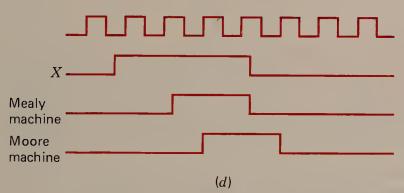

| 4.15        | Comments—Mealy Machines                           | 178        |           |

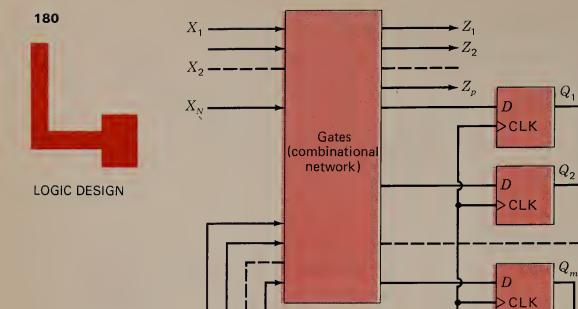

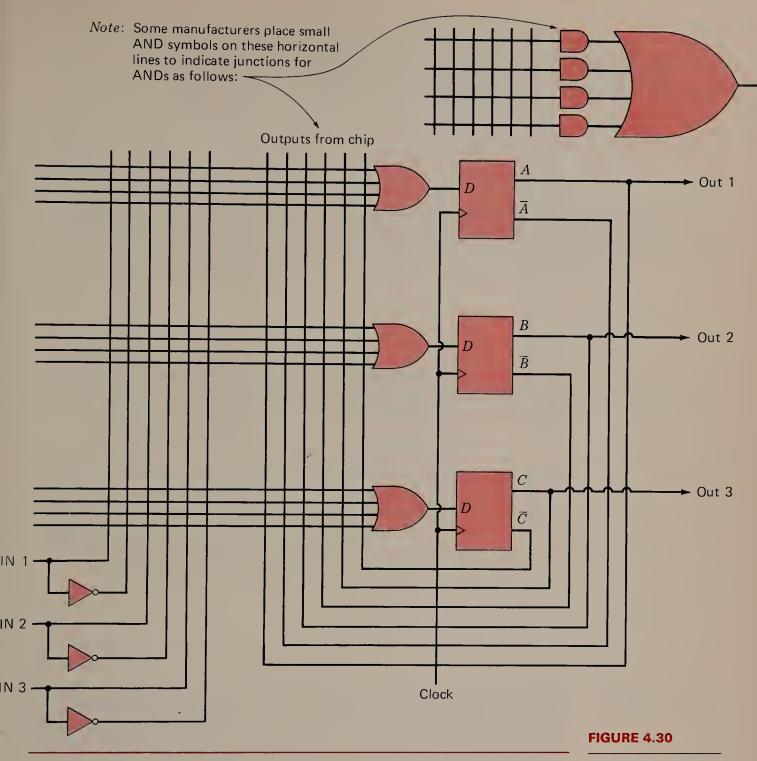

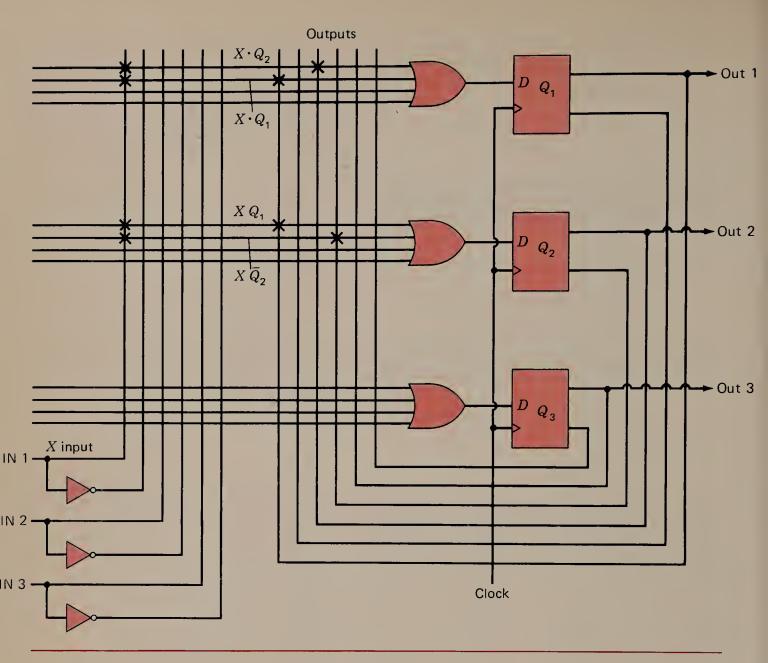

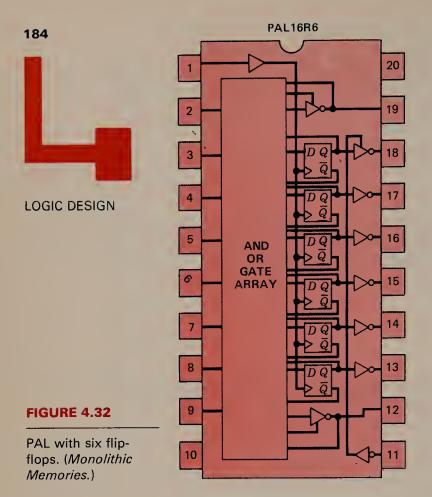

| 4.16        | Programmable Arrays of Logic Cells                | 180        |           |

| 4.17        | Summary                                           | 183        |           |

|             |                                                   |            |           |

|             | _,                                                |            |           |

|             | <b>5</b> THE ARITHMETIC-LOGIC UNIT 193            |            |           |

|             |                                                   |            |           |

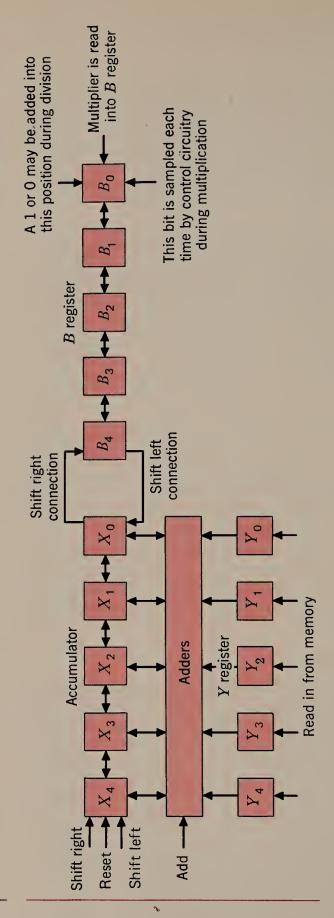

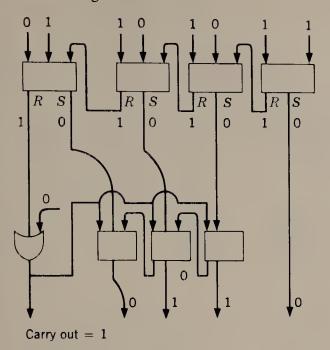

| 5.1         | Construction of the ALU                           | 194        |           |

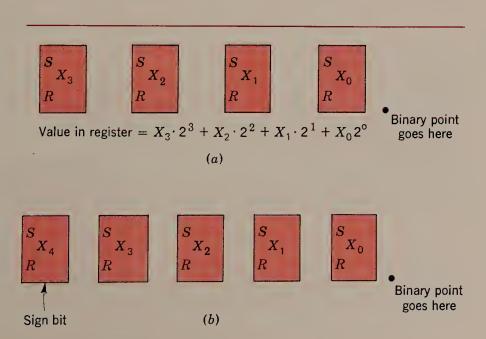

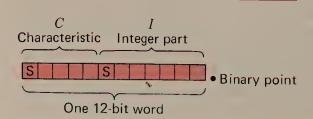

| 5.2         | Integer Representation                            | 195        |           |

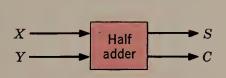

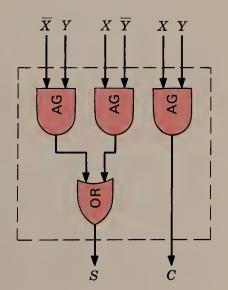

| 5.3         | Binary Half-Adder                                 | 196        |           |

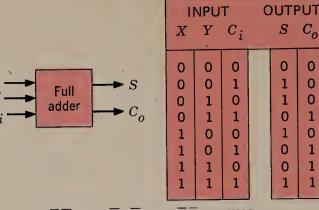

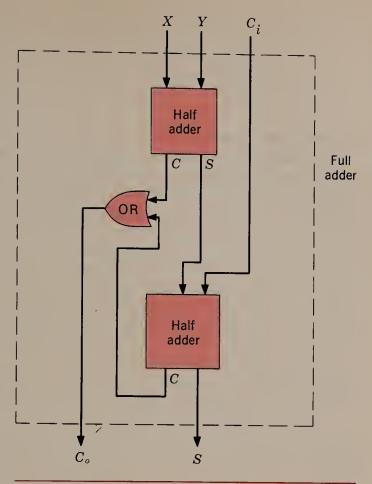

| 5.4         | Full-Adder                                        | 197        |           |

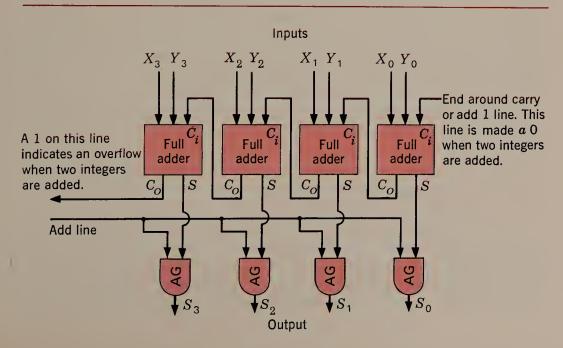

| 5.5         | A Parallel Binary Adder                           | 198        |           |

| 5.6         | Positive and Negative Numbers                     | 200        |           |

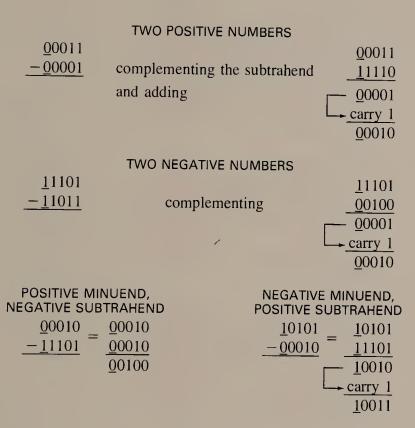

| 5.7         | Addition in the 1s Complement System              | 201        |           |

| 5.8         | Addition in the 2s Complement System              | 203        |           |

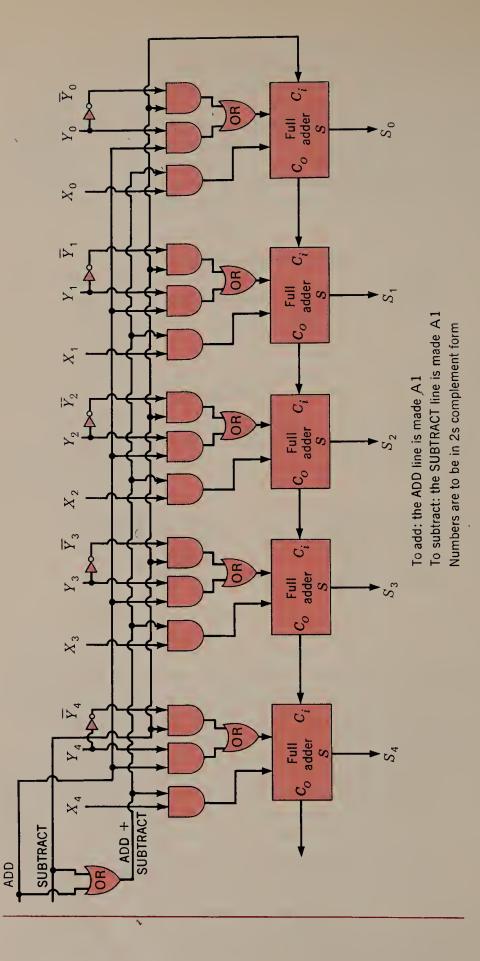

| <b>5</b> .9 | Addition and Subtraction in a Parallel            | 204        |           |

|             | Arithmetic Element                                | 204        |           |

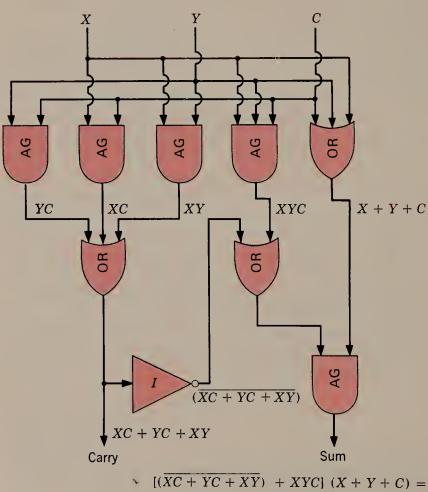

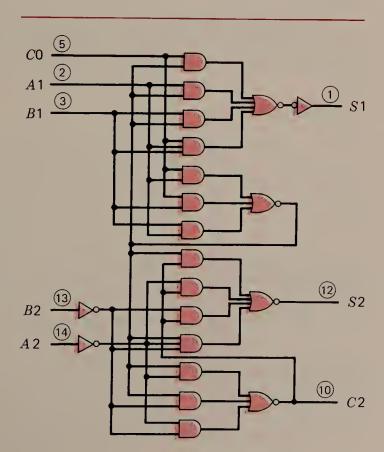

| 5.10        | Full-Adder Designs                                | 208        |           |

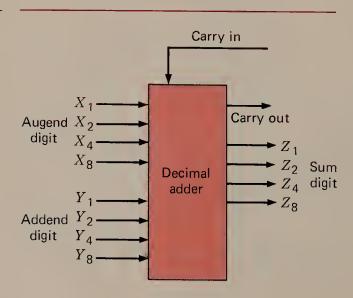

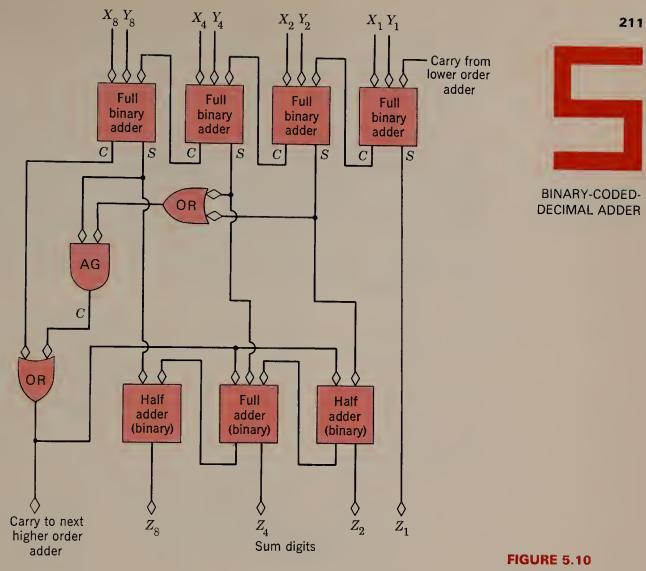

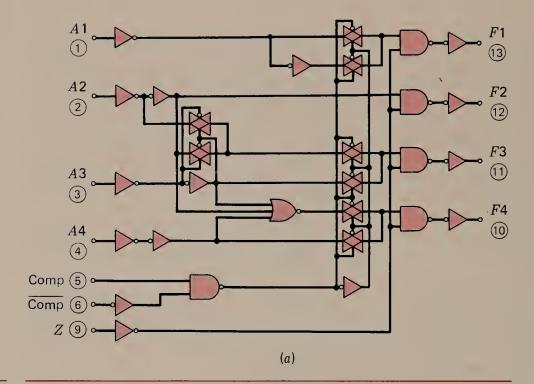

| 5.11        | Binary-Coded-Decimal Adder                        | 210<br>212 |           |

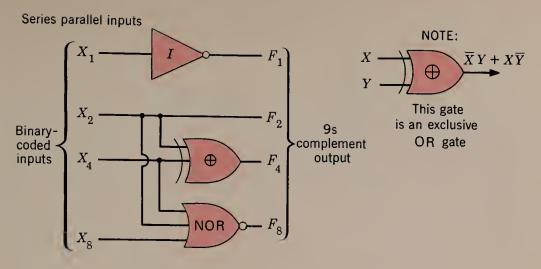

| 5.12        | Positive and Negative BCD Numbers                 | 212        |           |

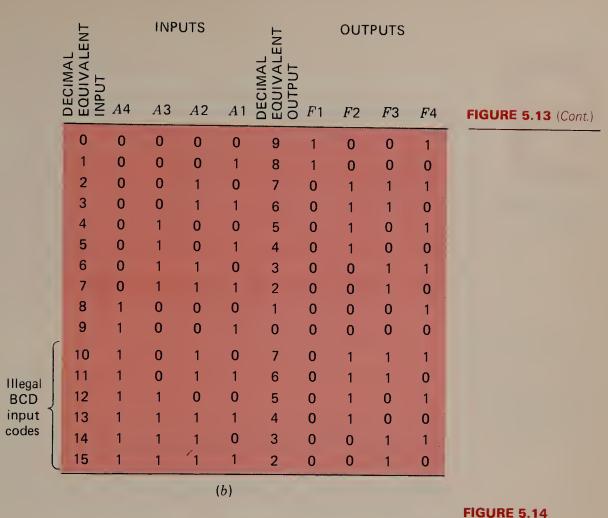

| 5.13        | Addition and Subtraction in the                   | 214        |           |

|             | 9s Complement System                              | 218        |           |

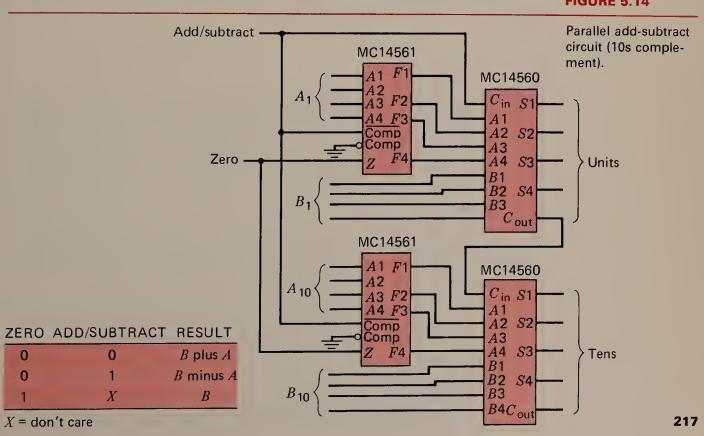

| 5.14        | Shift Operation                                   | 219        |           |

| 5.15        | Basic Operations                                  | 223        |           |

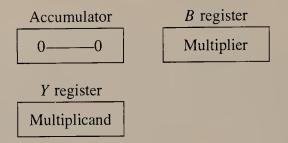

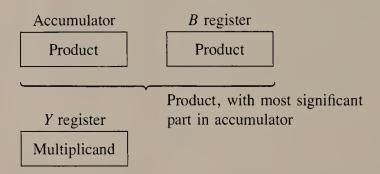

| 5.16        | Binary Multiplication                             | 226        |           |

| 5.17        | Decimal Multiplication                            | 227        |           |

| 5.18        | Division                                          | 233        |           |

| 5.19        | Logical Operations                                | 235        |           |

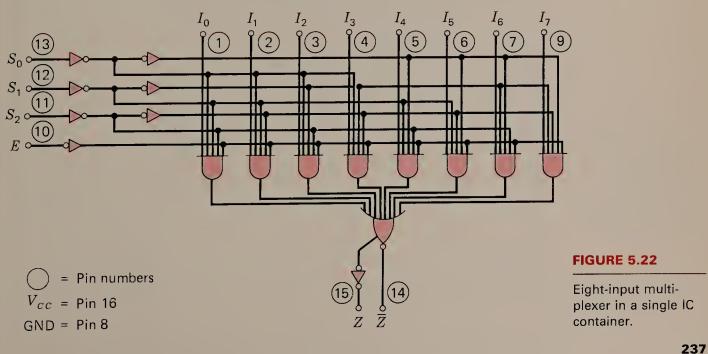

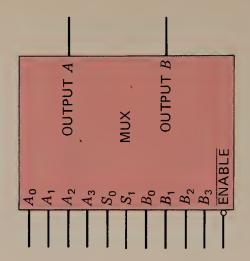

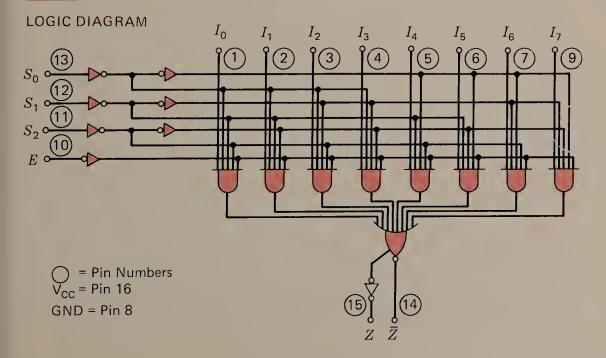

| 5.20        | Multiplexers                                      | 239        |           |

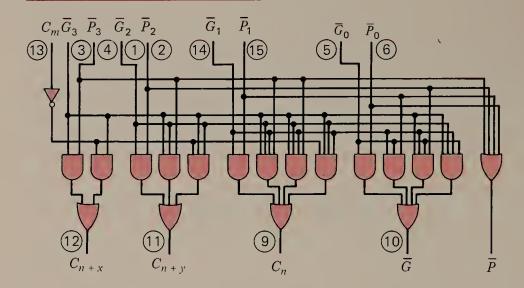

| 5.21        | High-Speed Arithmetic—Speeding up Addition        | 233        |           |

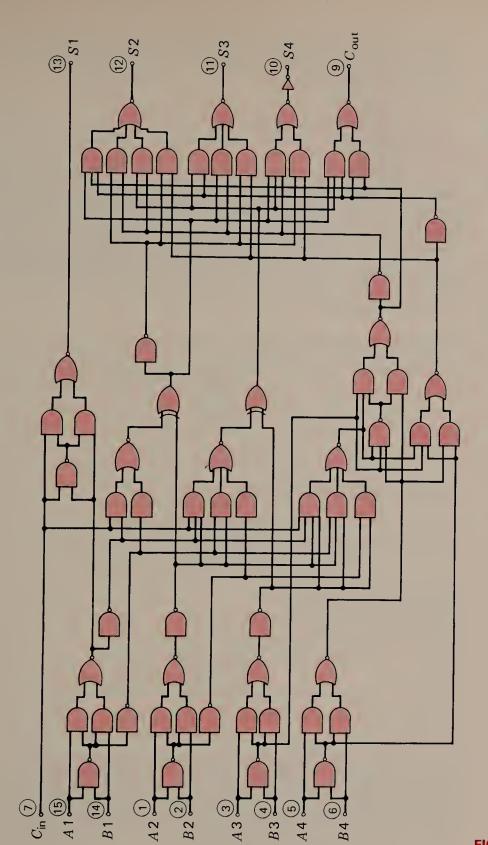

| iii     | 5.22       | High-Speed Arithmetic—Parallel Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 243        |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

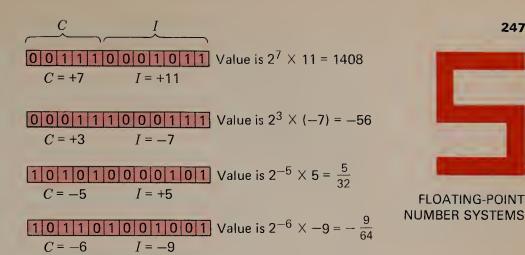

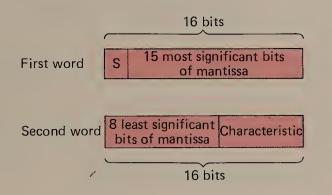

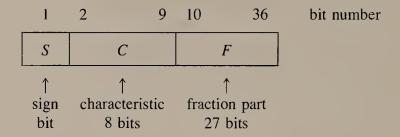

| ONTENTS | 5.23       | Floating-Point Number Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 243        |

|         | 5.24       | Performing Arithmetic Operations with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 054        |

|         | 5.25       | Floating-Point Numbers Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 251        |

|         | 5.25       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 252        |

|         |            | <b>6</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         |            | THE MEMORY ELEMENT 261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

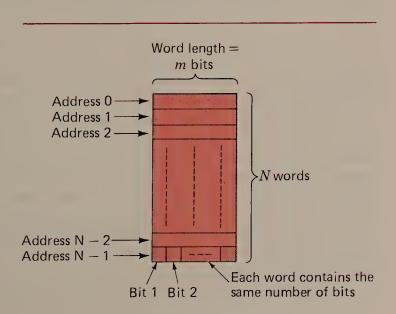

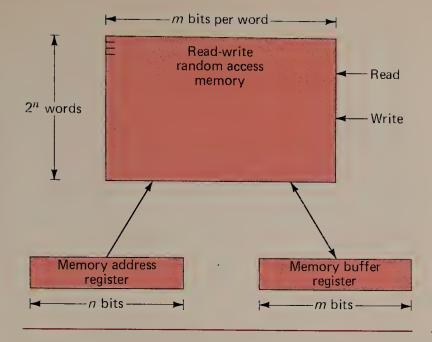

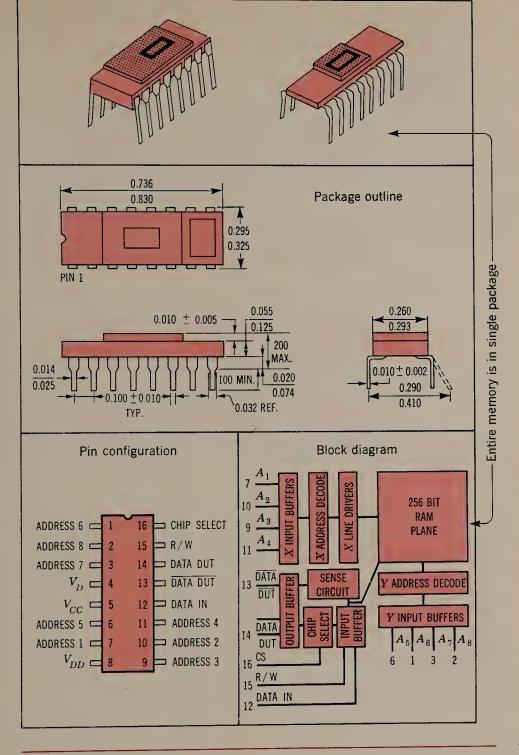

|         | 6.1        | Random-Access Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 263        |

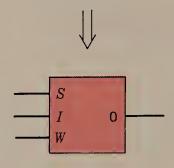

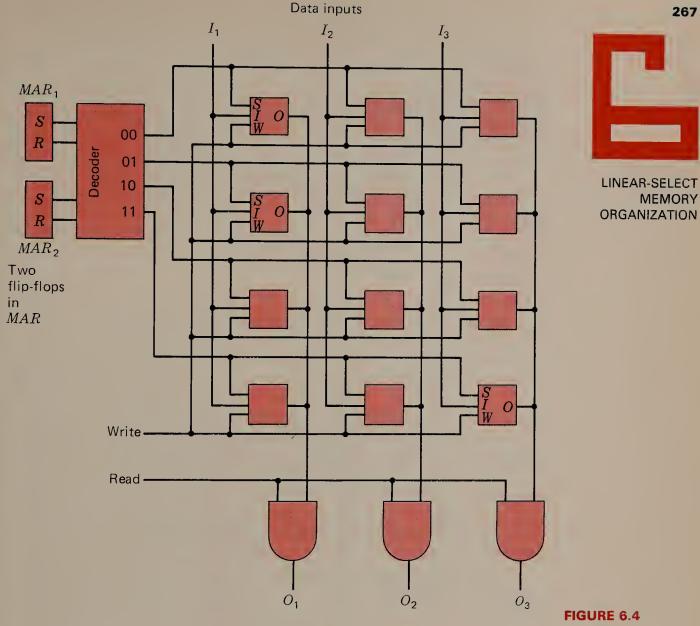

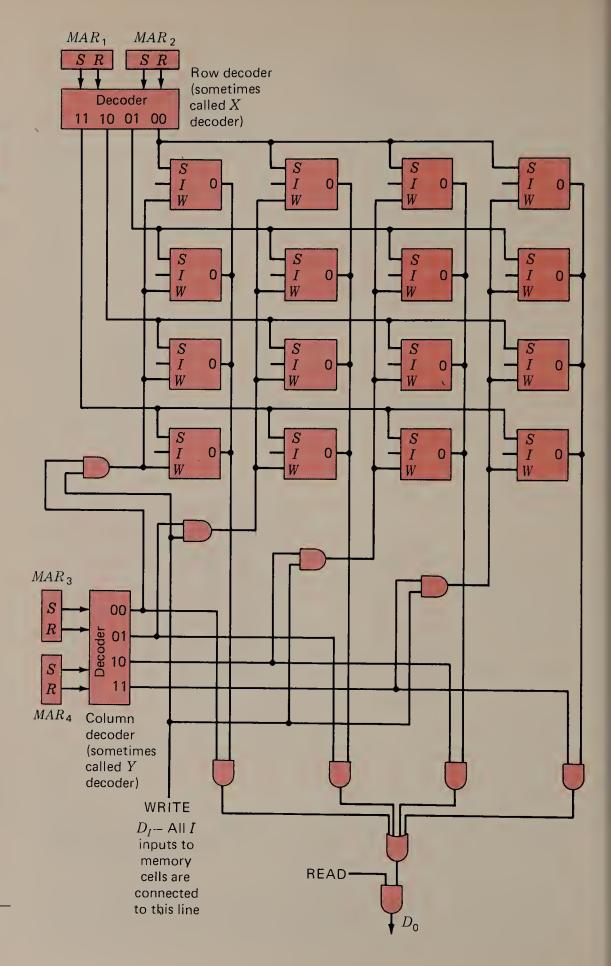

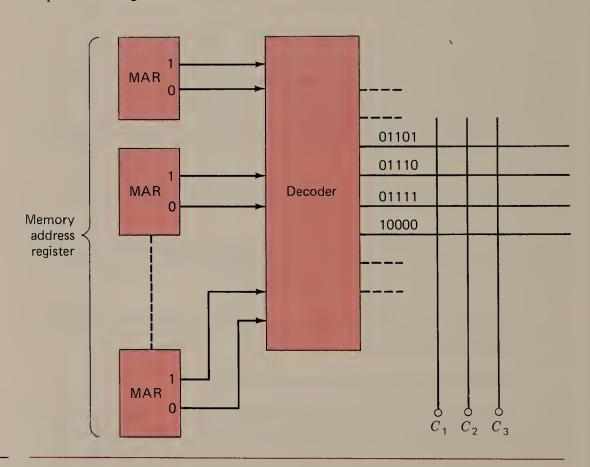

|         | 6.2        | Linear-Select Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 265        |

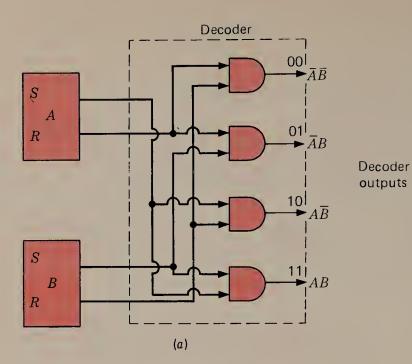

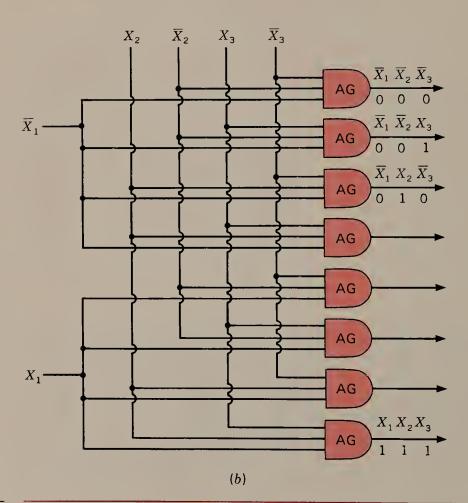

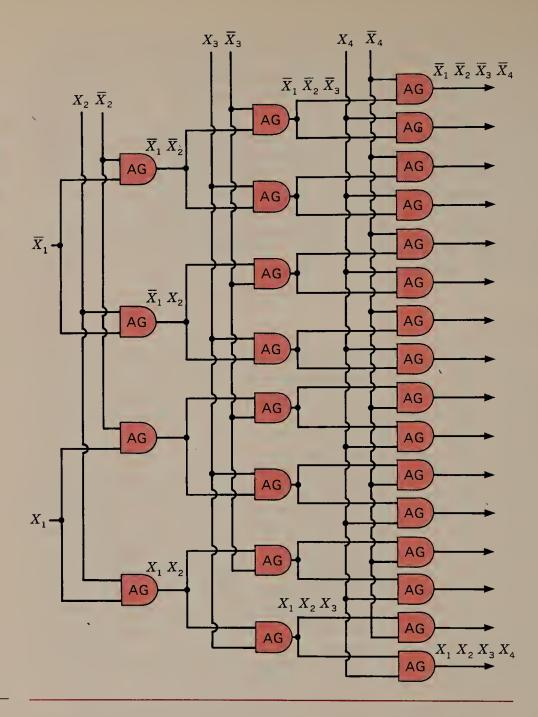

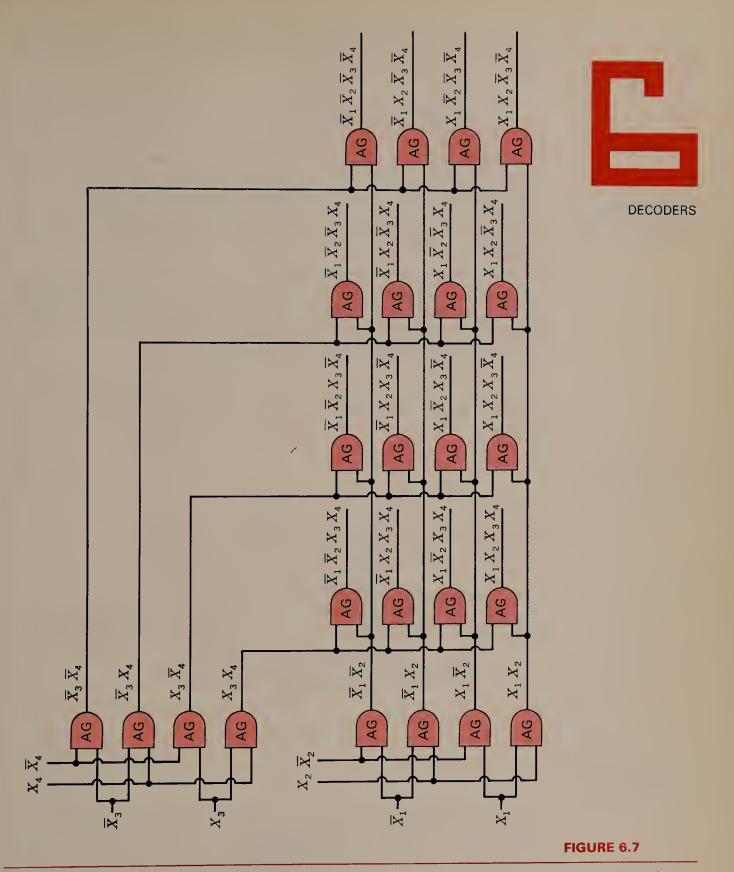

|         | 6.3        | Decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269        |

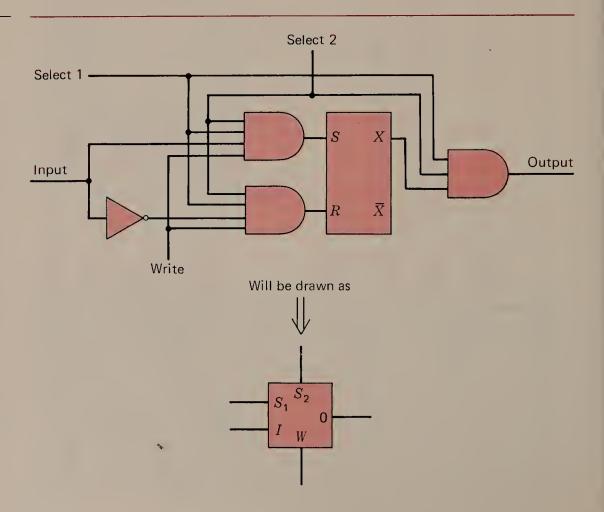

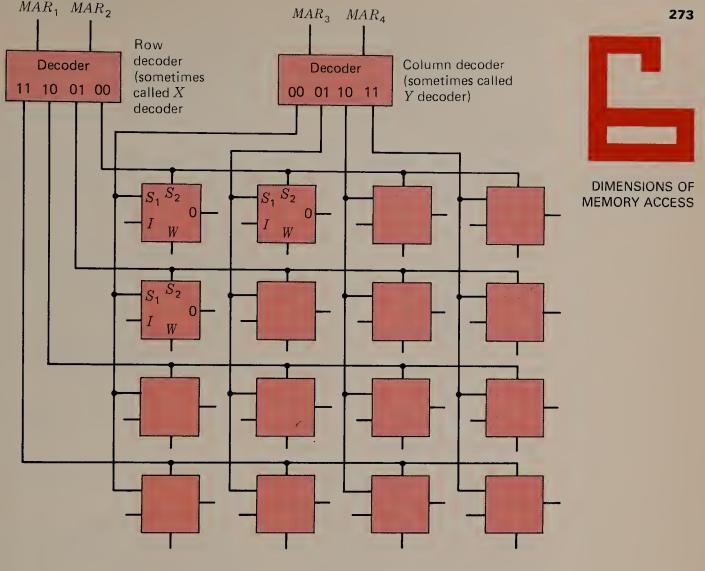

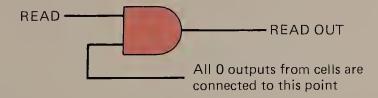

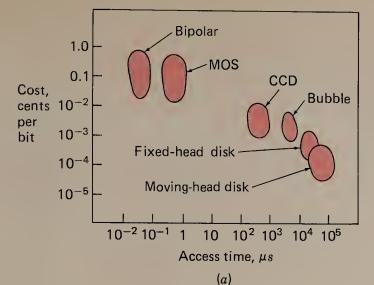

|         | 6.4        | Dimensions of Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 272        |

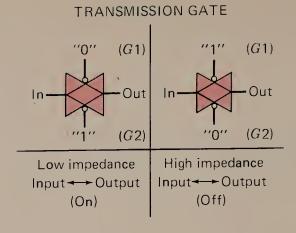

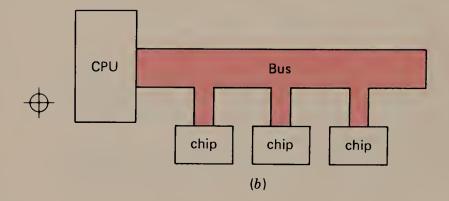

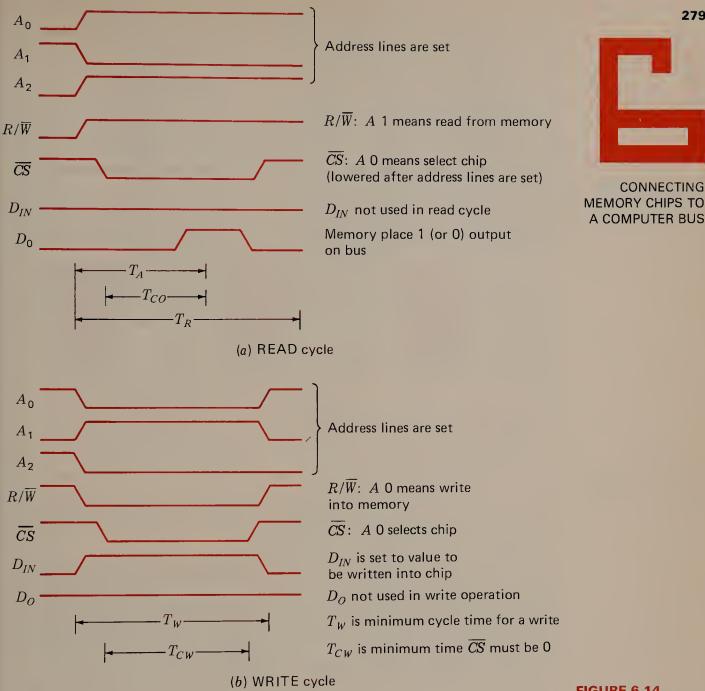

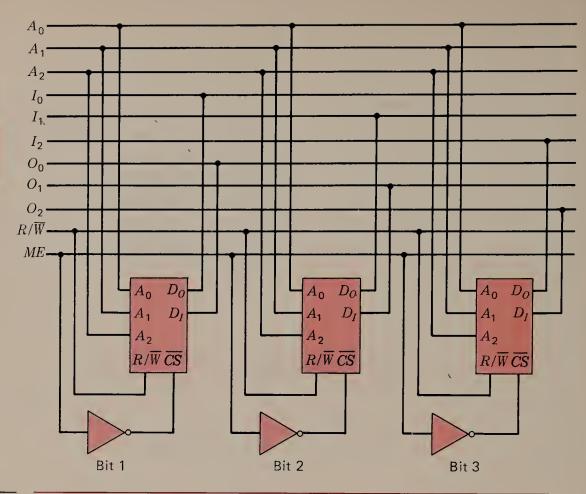

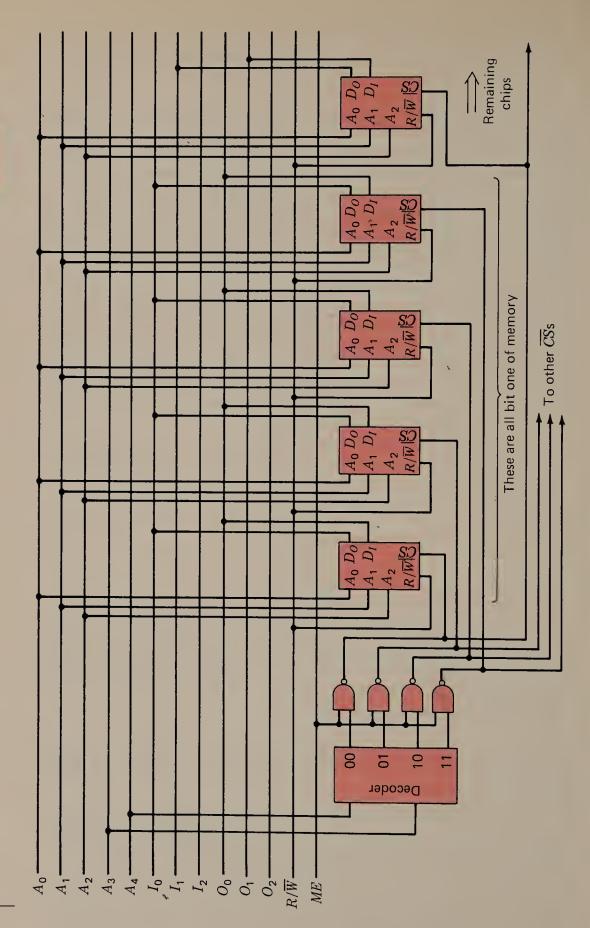

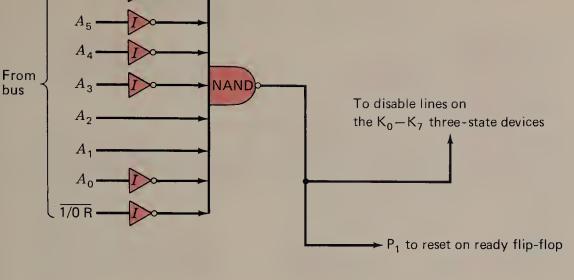

|         | 6.5<br>6.6 | Connecting Memory Chips to a Computer Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 277        |

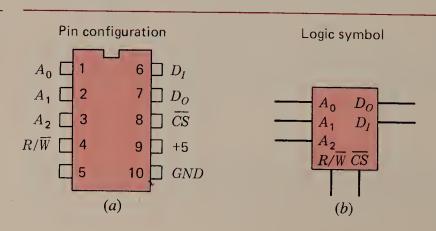

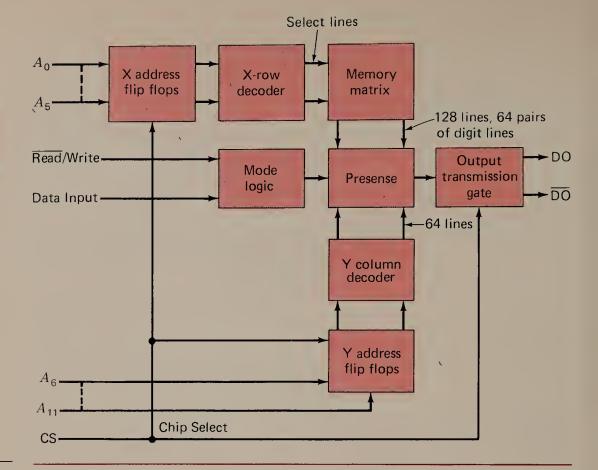

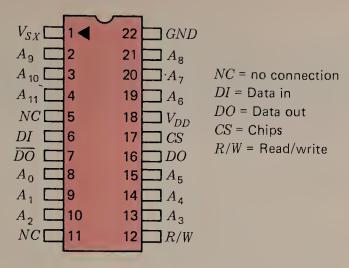

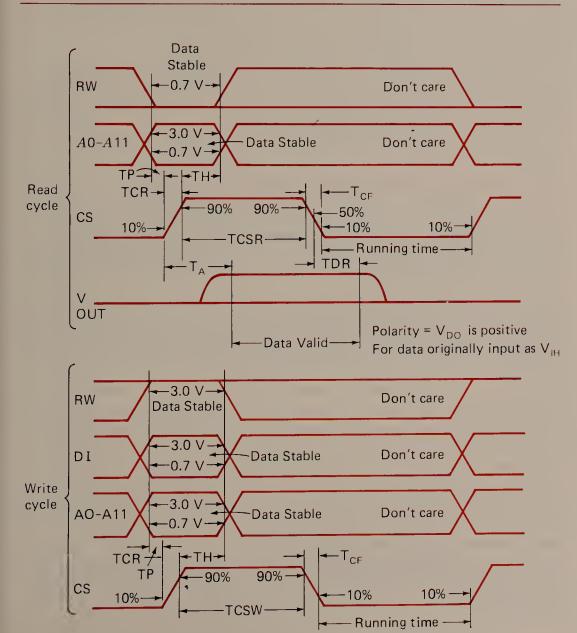

|         | 6.7        | Random-Access Semiconductor Memories Static Random-Access Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 281        |

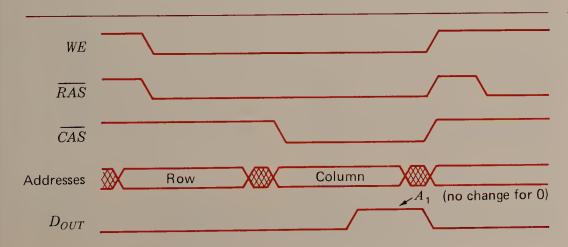

|         | 6.8        | Dynamic Random-Access Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 284        |

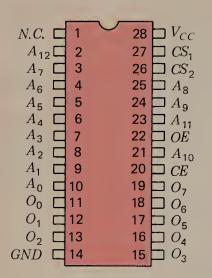

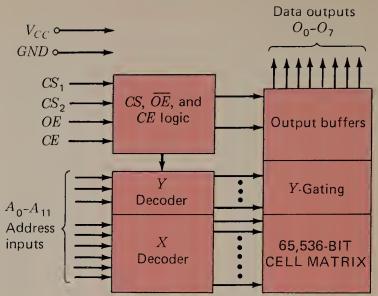

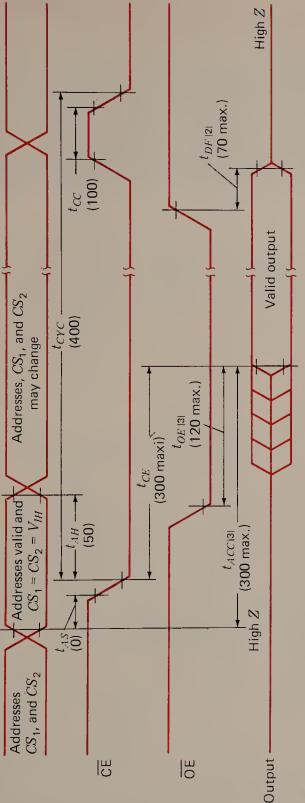

|         | 6.9        | Read-Only Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 286        |

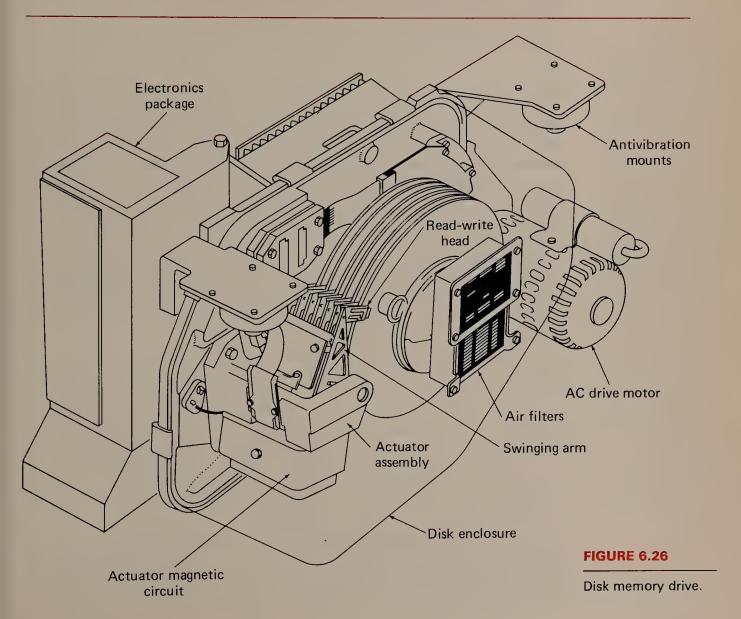

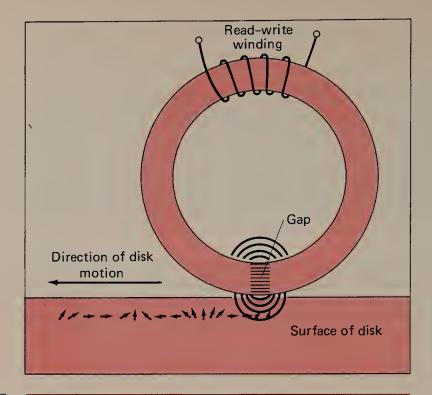

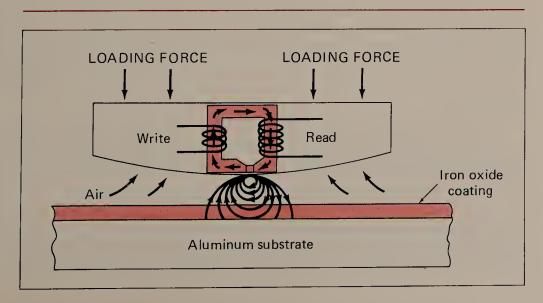

|         | 6.10       | Magnetic Disk Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 288        |

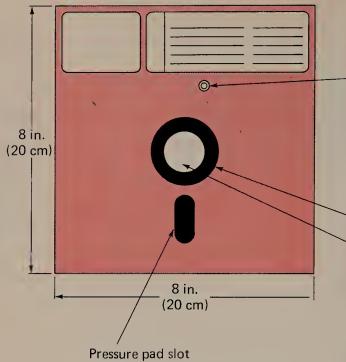

|         | 6.11       | Flexible-Disk Storage Systems—The Floppy Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 295<br>299 |

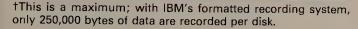

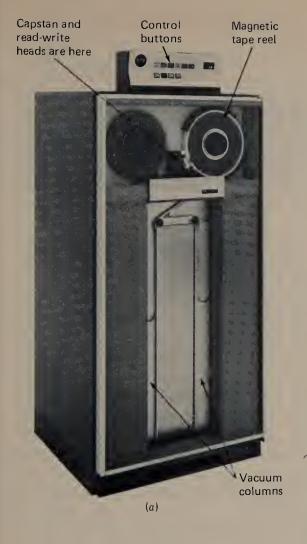

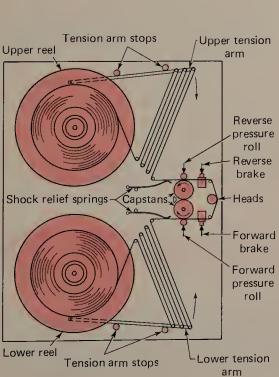

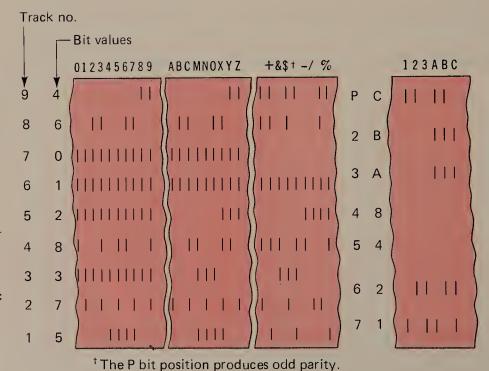

|         | 6.12       | Magnetic Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 302        |

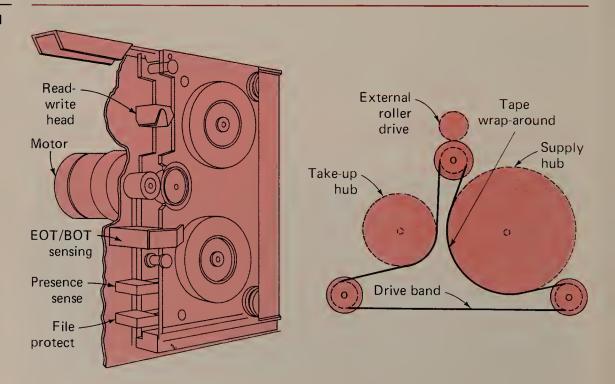

|         | 6.13       | Tape Cassettes and Cartridges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 307        |

|         | 6.14       | Magnetic Bubble and CCD Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 310        |

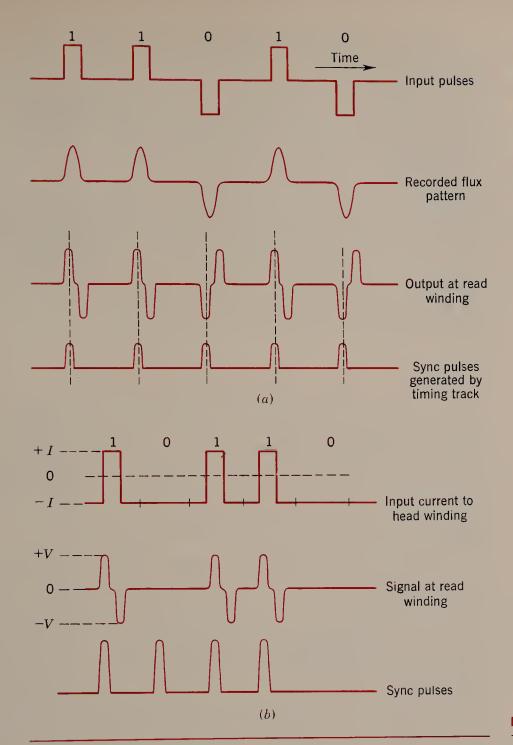

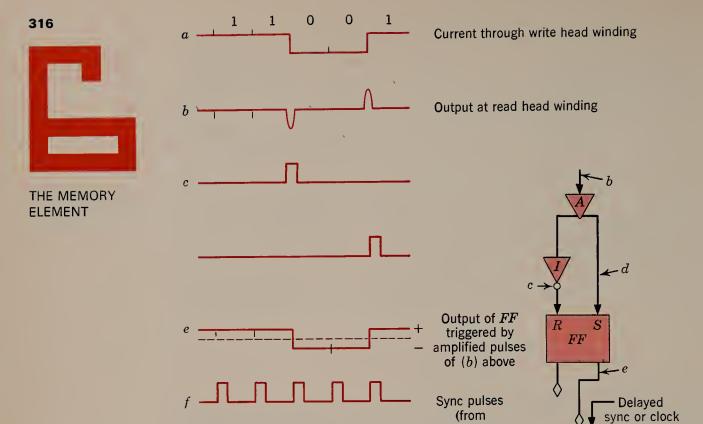

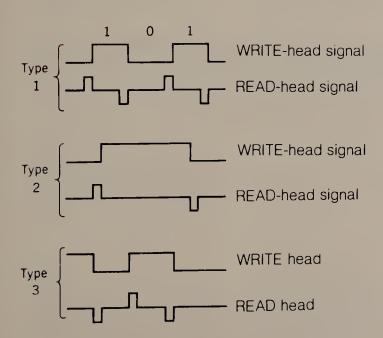

|         | 6.15       | Digital Recording Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 311        |

|         | 6.16       | Return-to-Zero and Return-to-Bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|         |            | Recording Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 312        |

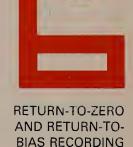

|         | 6.17       | Nonreturn-to-Zero Recording Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 314        |

|         | 6.18       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 316        |

|         |            | <b>7</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         |            | INPUT-OUTPUT DEVICES 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

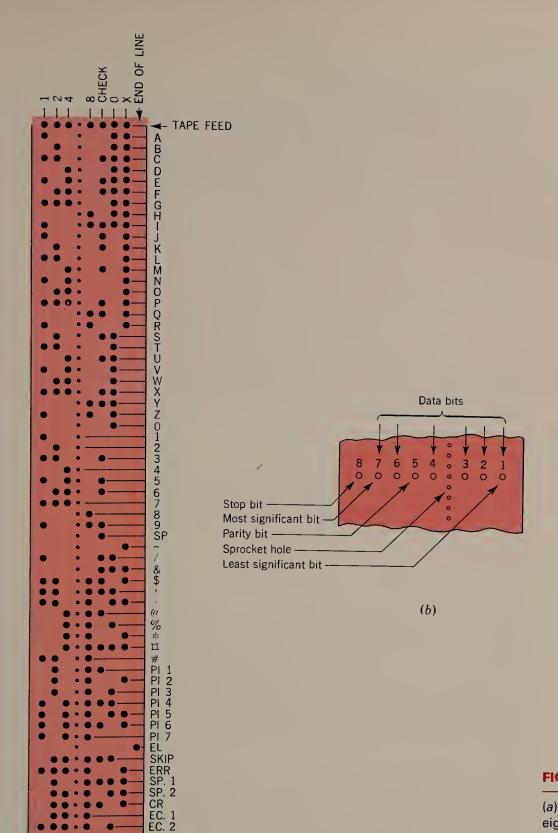

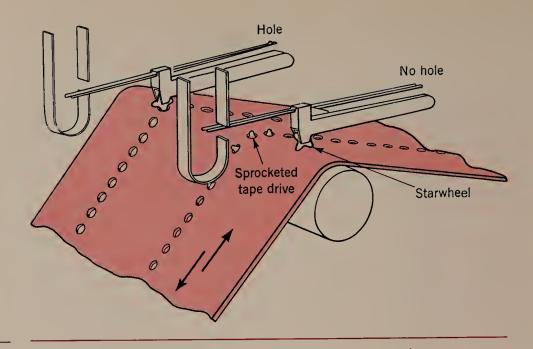

|         | 7.1        | Punched Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 324        |

|         | 7.2        | Tape Readers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 326        |

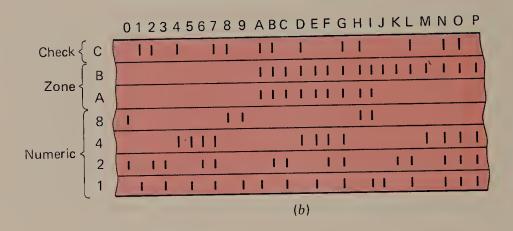

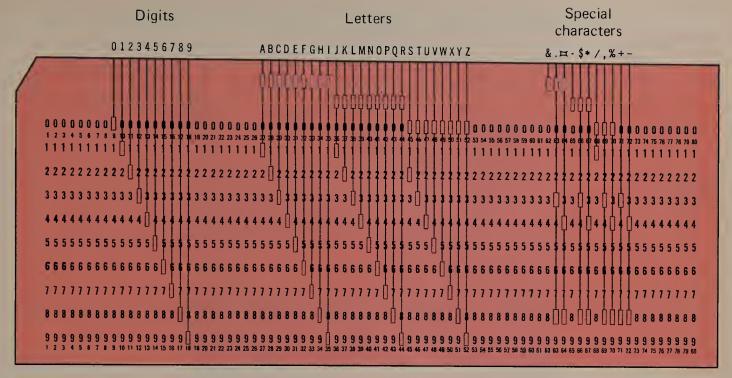

|         | 7.3        | Punched Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 328        |

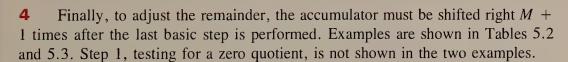

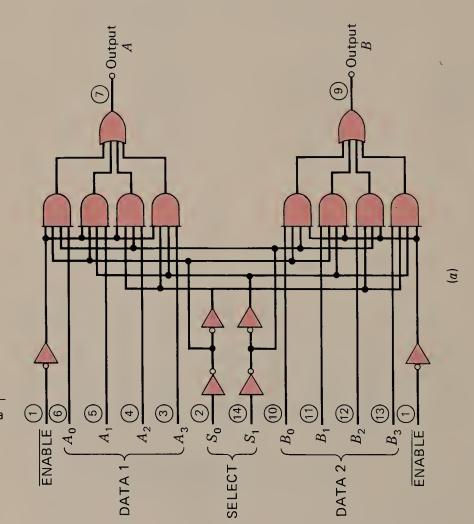

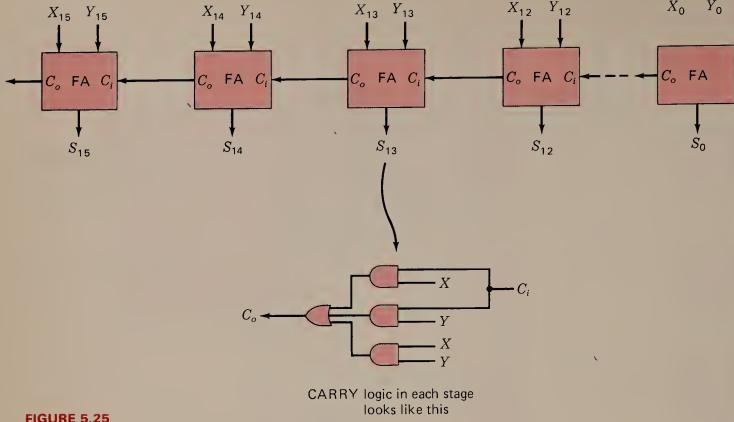

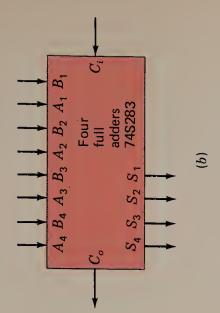

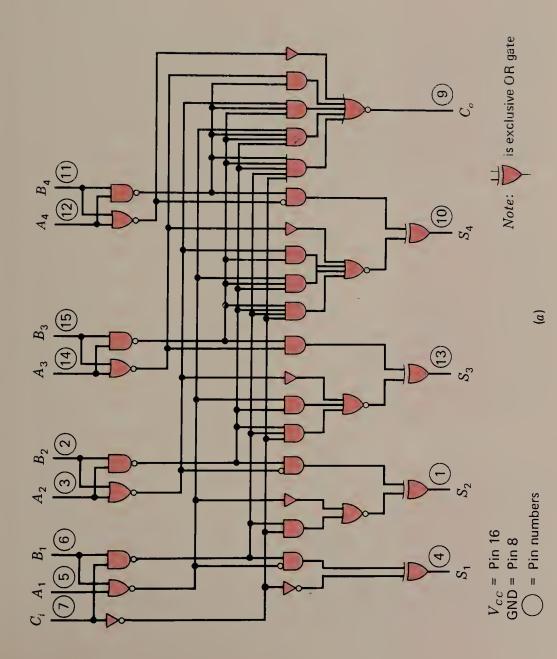

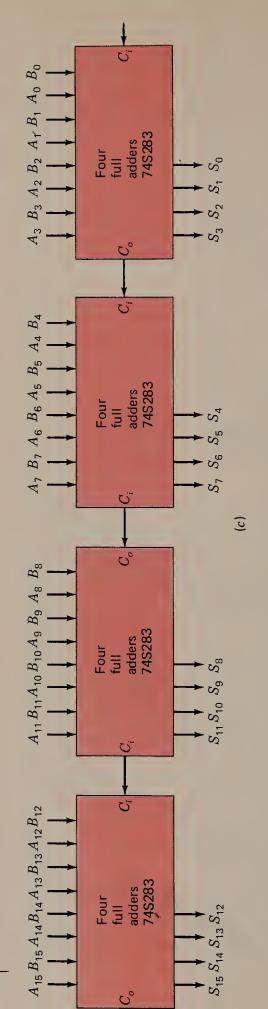

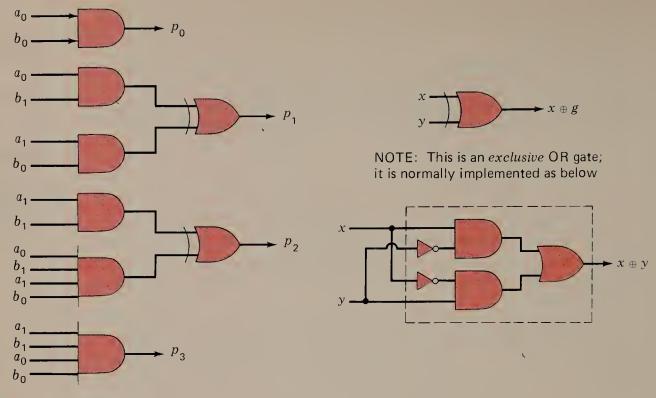

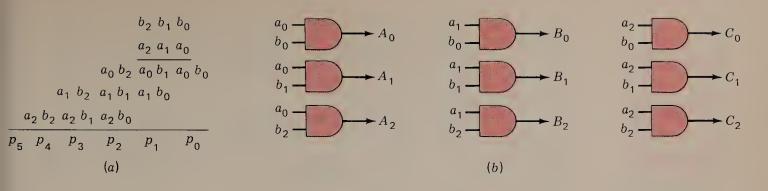

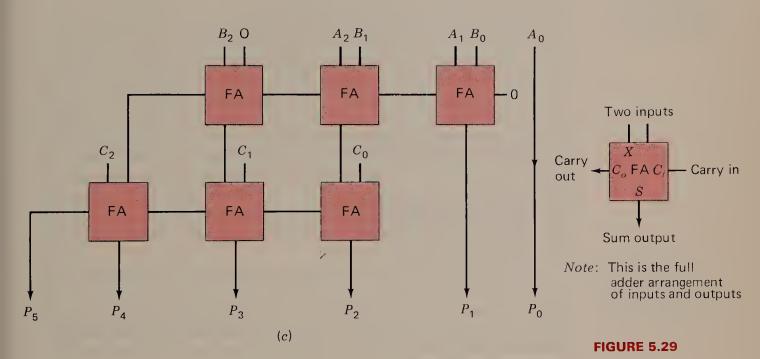

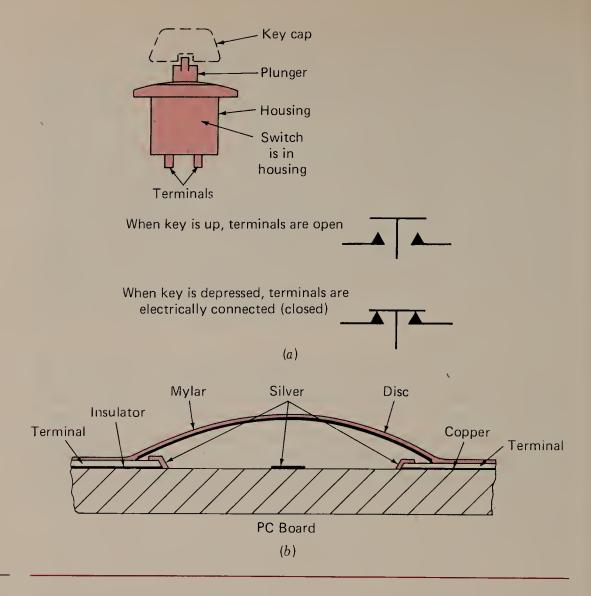

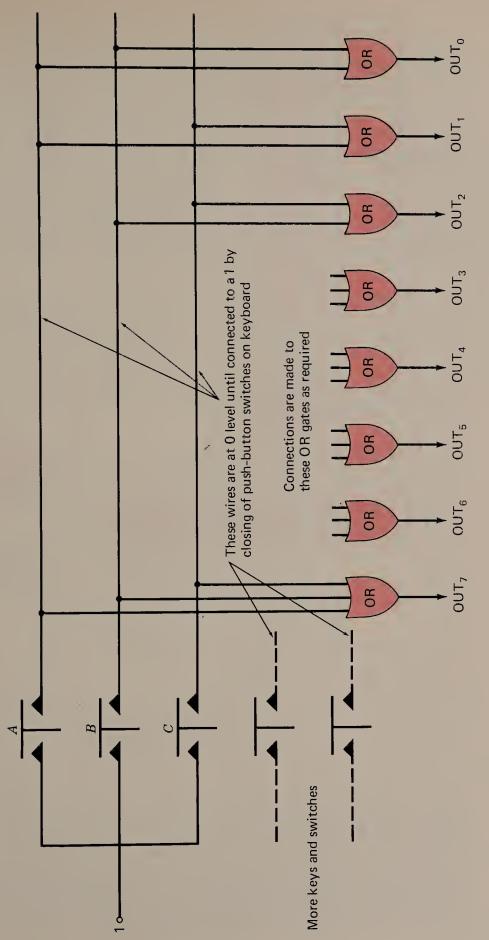

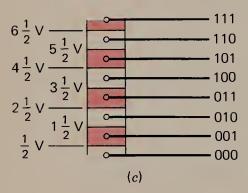

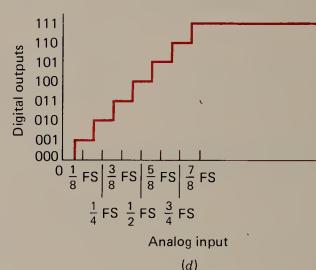

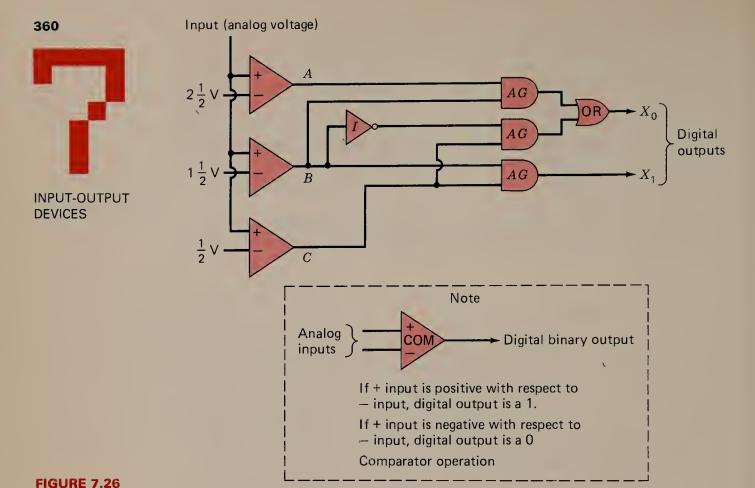

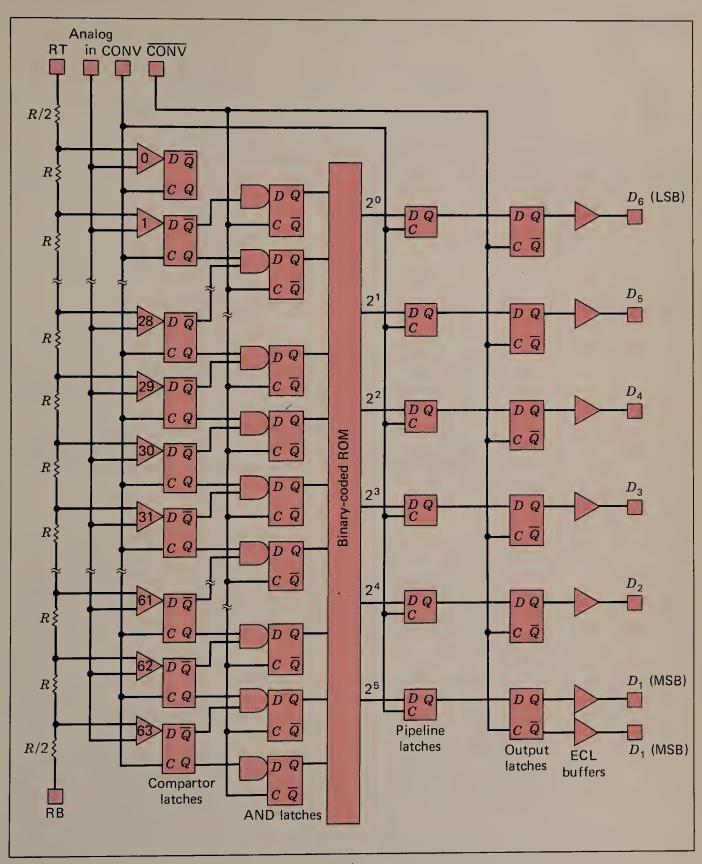

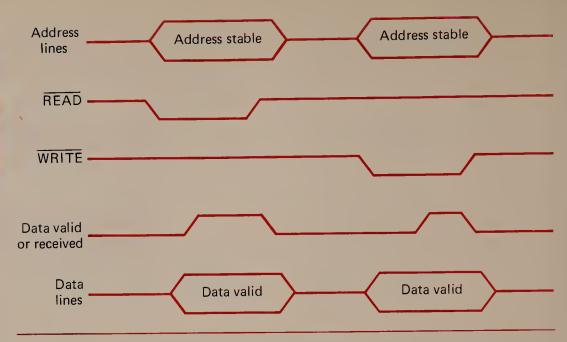

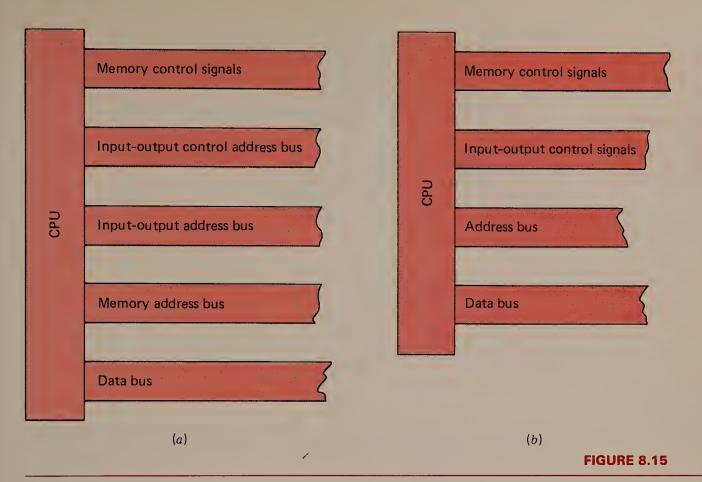

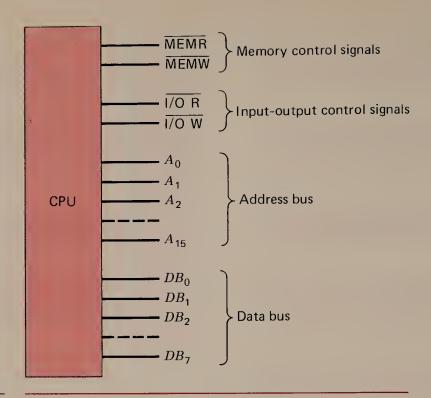

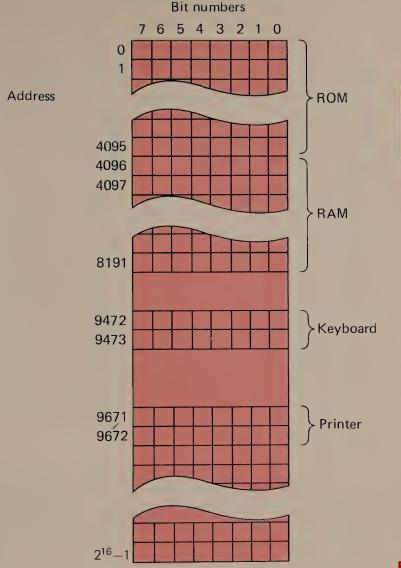

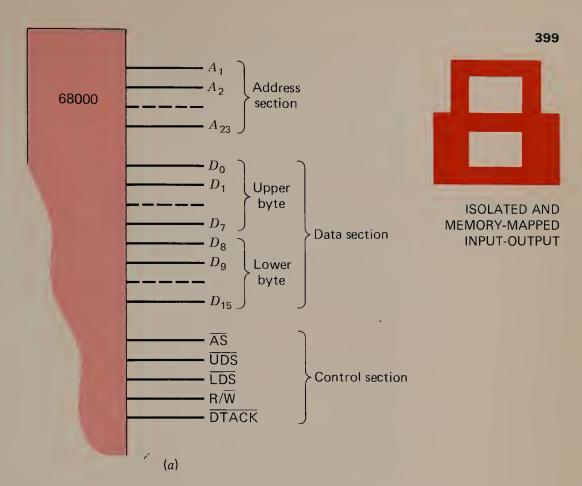

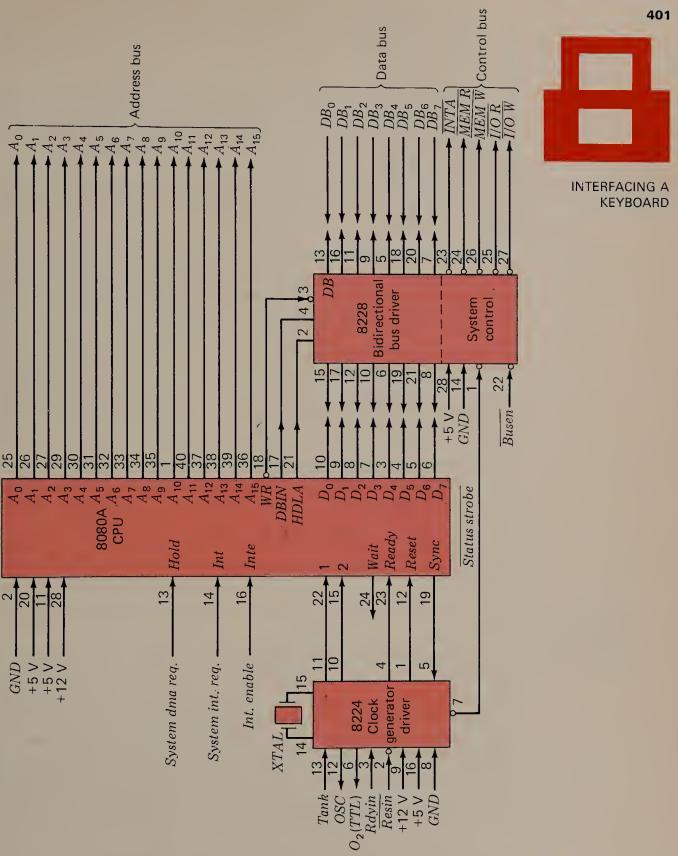

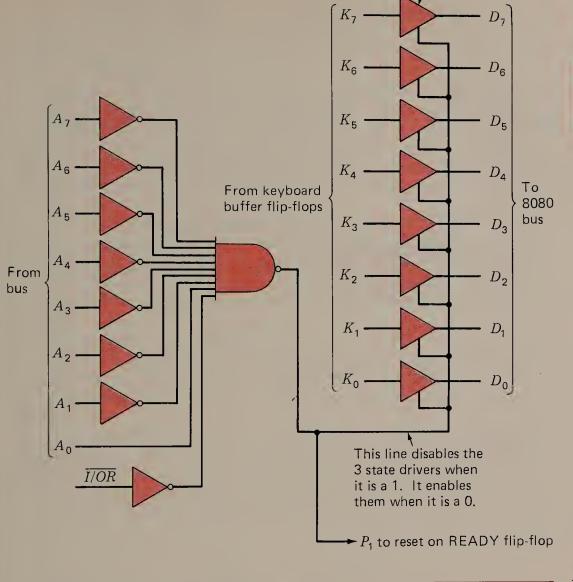

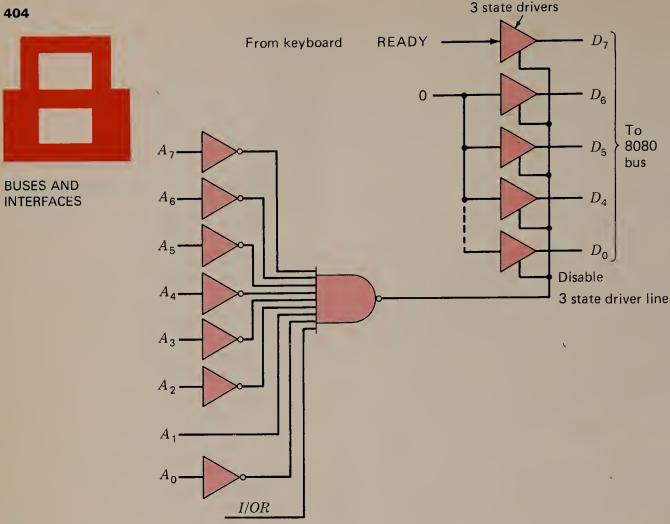

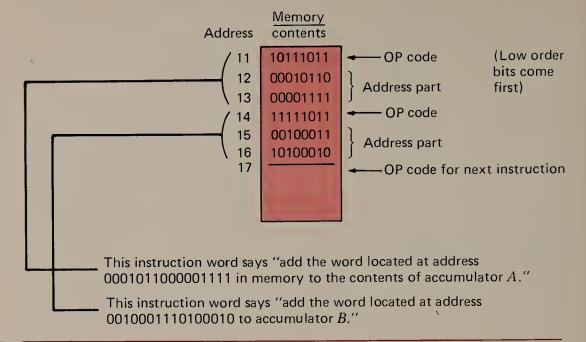

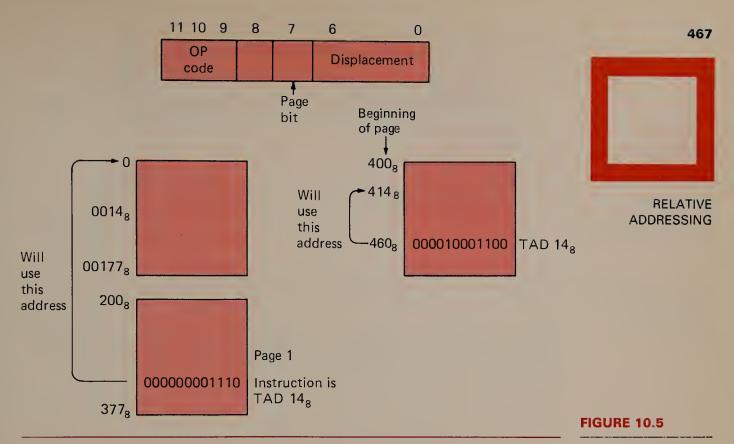

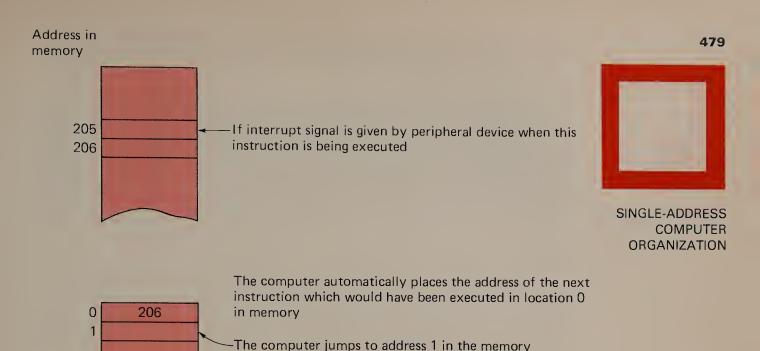

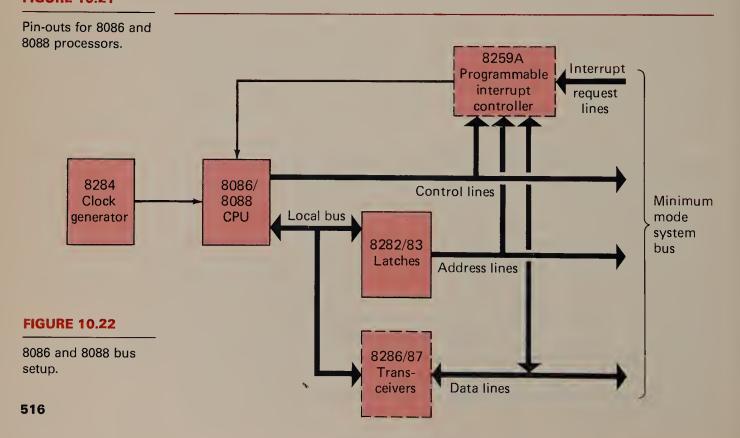

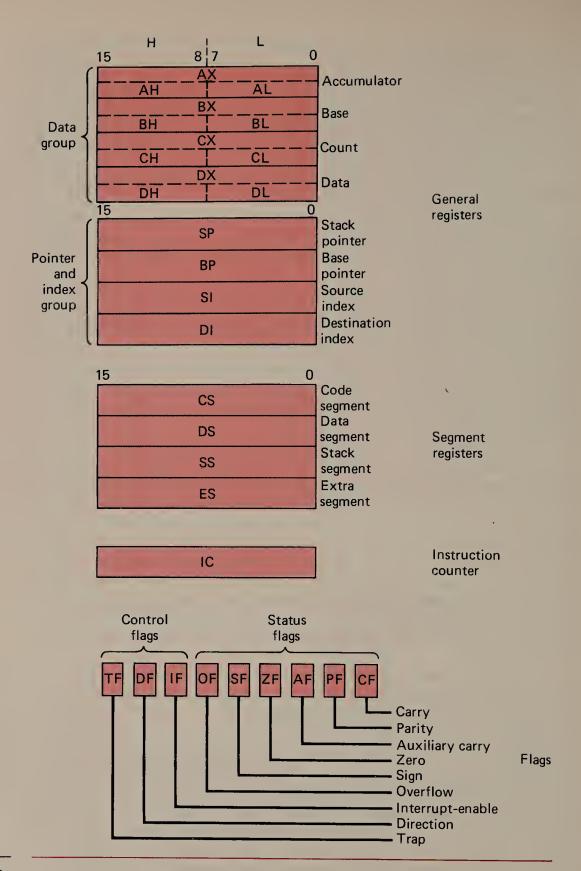

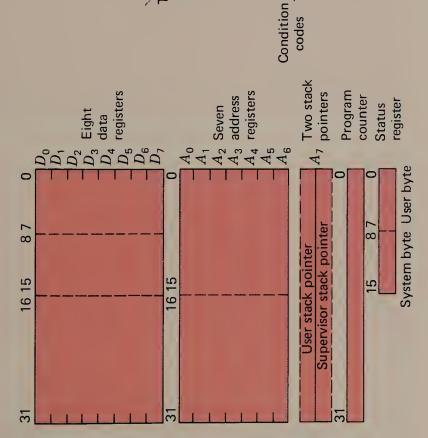

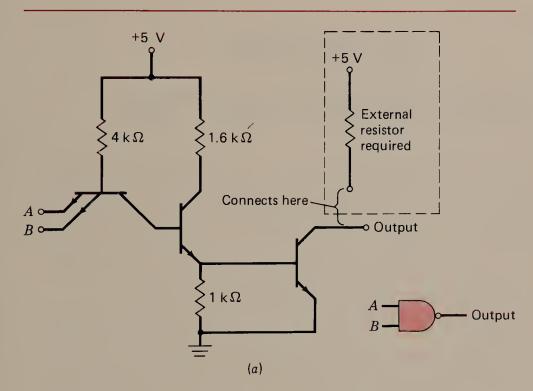

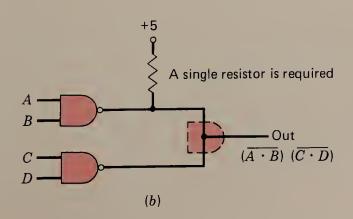

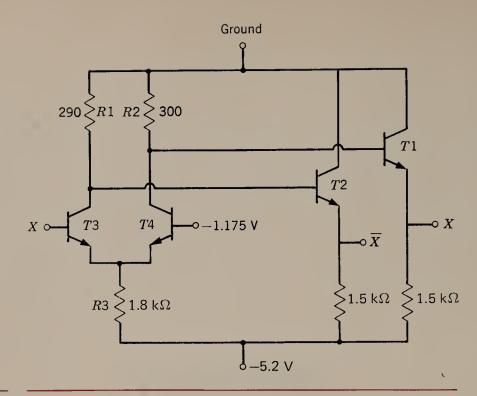

|         | 7.4        | Card Readers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 329        |