# Assembly Language Programming with the Commodore 64

Publishing Director: David Culverwell Acquisitions Editor: Terrell Anderson

Production Editor/Text Design: Michael J. Rogers

Art Director/Cover Design: Don Sellers Assistant Art Director: Bernard Vervin Manufacturing Director: John A. Komsa

Copy Editor: Keith R. Tidman

Typesetter: Pagecrafters, Inc., Oswego, NY Printer: Fairfield Graphics, Fairfield, PA

Typefaces: Helvetica (display), Palatino (text), and

Typewriter (computer-related material)

# Assembly Language Programming with the Commodore 64

Marvin L. De Jong

The School of the Ozarks Pt. Lookout, MO

Brady Communications Company, Inc.

A Prentice-Hall Publishing Company

Bowie, MD 20715

# Assembly Language Programming with the Commodore 64

Copyright ©1984 by Brady Communications Company, Inc.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or by any information storage and retrieval system, without permission in writing from the publisher. For information, address Brady Communications Company, Inc., Bowie, Maryland 20715.

# Library of Congress Cataloging in Publication Data

De Jong, Marvin L.

Assembly language programming with the Commodore 64.

Bibliography: p. Includes index.

1. Commodore 64 (Computer)—Programming. 2. Assembler language (Computer program language) I. Title. OA76.8.C64D4 1984 001.64'2 84-6347

### ISBN 0-89303-319-7

Prentice-Hall International, Inc., London

Prentice-Hall Canada, Inc., Scarborough, Ontario

Prentice-Hall of Australia, Pty., Ltd., Sydney

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Prentice-Hall of Southeast Asia Pte. Ltd., Singapore

Whitehall Books, Limited, Petone, New Zealand

Editora Prentice-Hall Do Brasil LTDA., Rio de Janeiro

Printed in the United States of America

85 86 87 88 89 90 91 92 93 94

2 3 4 5 6 7 8 9 10

# **Contents**

### Preface / ix

### 1 The Commodore 64 Microcomputer System / 1

- I. Introduction / 1

- II. Components of the Commodore 64 / 2

- III. Microcomputer System Buses / 6

- IV. The Microcomputer in Action / 9

- V. An Overview of the 6510 Registers / 18

- VI. Additional Reading / 21

- VII. Summary / 21

# 2 Writing, Assembling, and Executing Programs / 23

- I. Introduction / 23

- II. Microcomputer Instructions / 23

- III. Addressing Modes / 25

- IV. The Components and Form of an Assembly Language Program / 31

- V. Loading and Executing Simple Programs / 34

- VI. Summary / 39

- VII. Exercises / 40

# 3 Data Transfer Instructions—Using an Editor/Assembler / 41

- I. Introduction / 41

- II. Data Transfer Instructions: Load and Store / 43

- III. Data Transfer Instructions: Register Transfers / 46

- IV. Writing and Assembling Programs / 48\*

- A. Using the editor / 49

- B. Using the assembler / 51

- C. Executing the machine-language program / 52

- D. Debugging programs / 53

- V. Summary / 53

- VI. Exercises / 54

# 4 Arithmetic Operations in Assembly Language / 57

- I. Introduction / 57

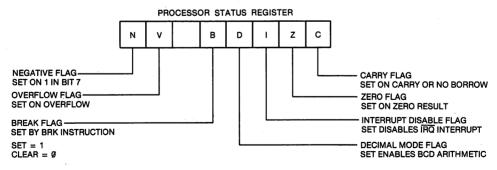

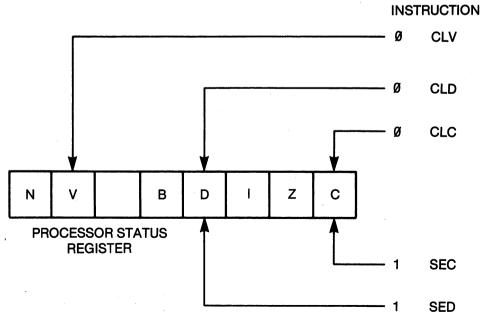

- II. The Processor Status Register and the Carry Flag / 58

- III. Flag Modification Instructions / 59

- IV. The ADC Instruction / 60

- V. Multiple-Byte Addition / 63

- VI. The SBC Instruction / 64

- VII. Multiple-Byte Subtraction / 66

- VIII. Decimal-Mode Arithmetic / 67\*

- IX. Signed-Number Arithmetic / 69\*

- X. The JSR and RTS Instructions / 71

- XI. Summary / 72

- XII. Exercises / 73

<sup>\*</sup>The beginning programmer may find that the sections marked with an asterisk are more difficult. Skip these sections if that is the case.

# 5 Logic Operations in Assembly Language / 77

- I. Introduction / 77

- II. The AND, ORA, and EOR Instructions / 78

- III. Simple Programs to Illustrate the Logic Instructions / 80

- IV. Using the Logic Instructions / 81

- V. Summary / 86

- VI. Exercises / 87

### 6 Branches and Loops / 91

- I. Introduction / 91

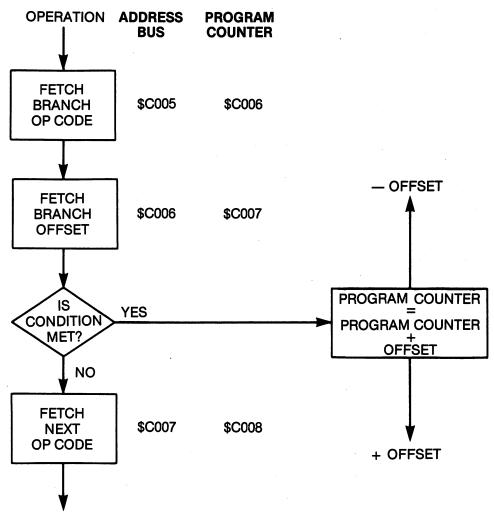

- II. Reviewing the Flags / 93

- III. The Branch Instructions / 94

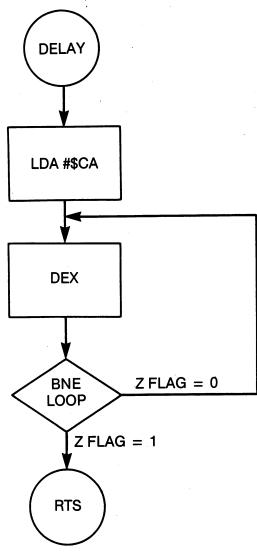

- IV. Loop Counters / 99

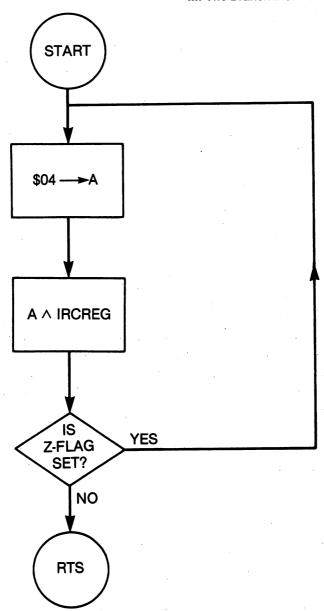

- V. Test Instructions / 101

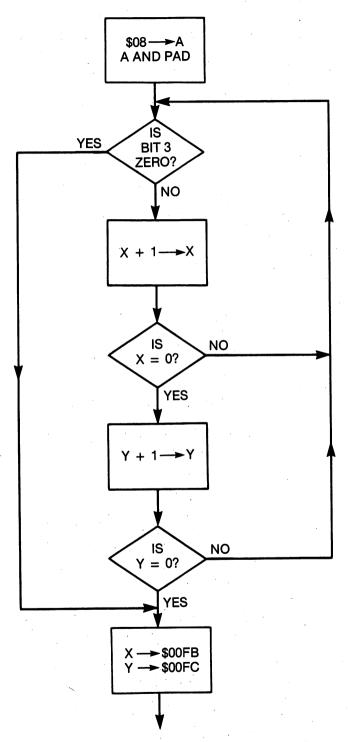

- VI. Programming Examples for Branches and Loops / 103

- VII. Summary / 114

- VIII. Exercises / 115

### 7 Shift and Rotate Routines / 117

- I. Introduction / 117

- II. Definitions of the Shift and Rotate Instructions / 117

- III. Programs that Use the Shift and Rotate Instructions / 119

- A. Code shift / 119

- B. Displaying the code in a memory location / 120

- C. Printing a byte on the screen / 121

- D. Getting a byte from the keyboard / 122

- E. Simple arithmetic with shifts / 124

- F. Watching the clock / 125

- IV. More Advanced Arithmetic Operations / 126\*

- V. Summary / 131

- VI. Exercises / 131

# 8 Indexed Addressing Modes / 133

- I. Introduction / 133

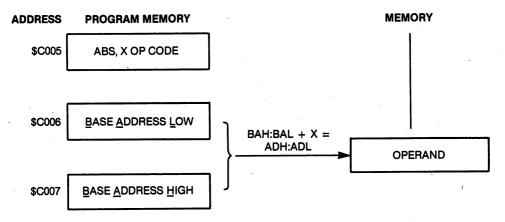

- II. The Absolute Indexed Addressing Modes / 134

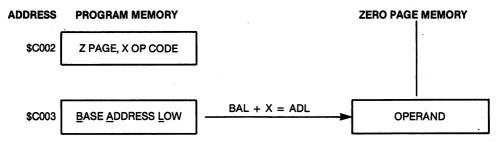

- III. The Zero-Page Indexed Addressing Mode / 138

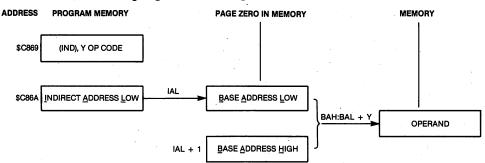

- IV. The Indirect Indexed Addressing Mode / 140

- V. The Indexed Indirect Addressing Mode / 146

- VI. Additional Programming Examples / 146

- VII. Summary / 150

- VIII. Exercises / 150

# 9 Jumps, Subroutine Calls, and Interrupts / 153

- I. Introduction / 153

- II. The JMP Instruction / 155

- III. Subroutine Calls and Returns / 159

- IV. Operation of the Stack / 160

- V. Stack Operation Instructions / 162

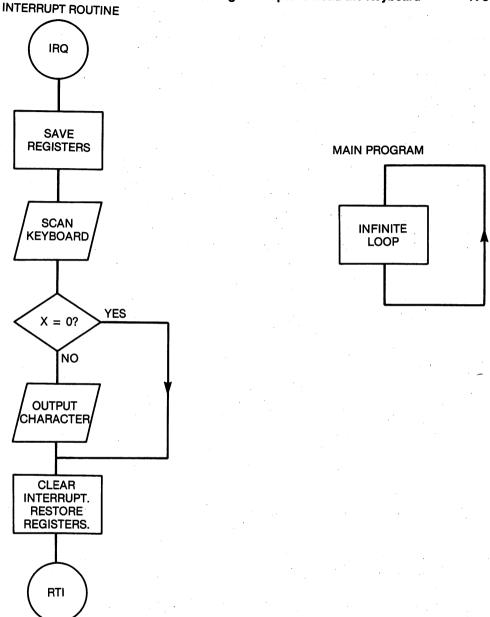

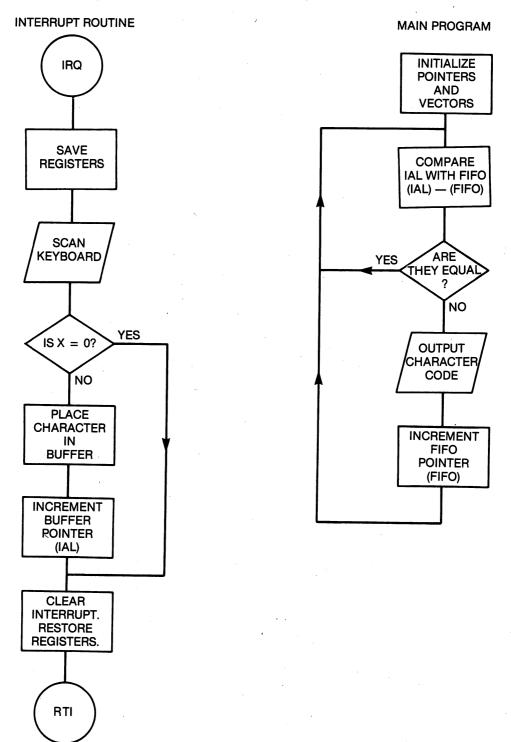

- VI. IRQ-Type Interrupts / 166\*

- VII. The Commodore 64 Interrupt Structure / 169\*

- VIII. Using Interrupts to Read the Keyboard / 171\*

- IX. NMI-Type Interrupts / 175\*

- X. Summary / 176

- XI. Exercises / 176

### 10 Programming the 6581 Sound Interface Device / 179

- I. Introduction / 179

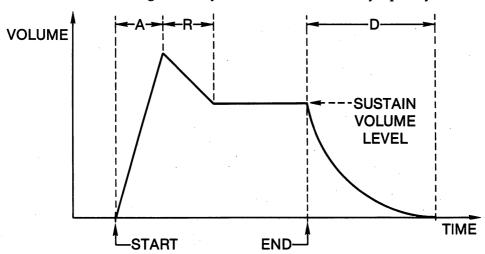

- II. A Brief Introduction to Music Synthesis / 179

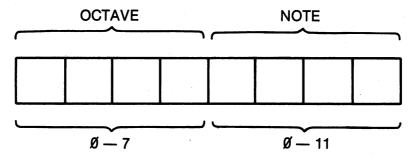

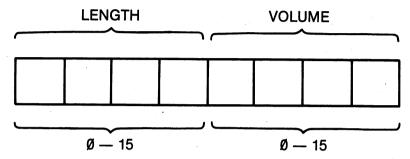

- III. The Registers of the 6581 SID Chip / 184

- IV. Setting the Voice Frequencies / 190

- V. Note Duration and Volume: Gating the SID / 194

- VI. The Program to Play a Song / 196

- VII. A BASIC Music Interpreter / 199

- VIII. Summary / 200

- IX. Exercises / 200

### 11 Applications Using the 6567 Video Interface Chip / 203

- I. Introduction / 203

- II. 6567 VIC Programming Fundamentals / 203

- A. Bank switching the VIC / 203

- B. Screen memory / 204

- C. Color memory / 206

- D. Character memory / 207

- E. Character ROM / 208

- F. A demonstration program / 208

- III. Bit-Mapped Graphics / 210

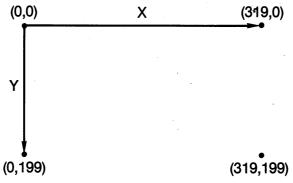

- A. Fundamentals of the bit-mapped graphics mode / 210

- B. Preparing for bit-mapped graphics / 210

- C. Calculating the location of a pixel's bit / 212

- D. Switching out the ROM / 219

- E. Plotting points in the bit-mapped mode / 220

- F. A bit-mapped graphics demonstration routine / 221

- IV. Summary / 223

- V. Exercises / 224

# 12 Input/Output: The 6526 Complex Interface Adapter / 225

- I. Introduction / 225

- II. Input/Output Fundamentals / 226

- A. Input ports / 226

- B. Output ports / 227

- C. Memory-mapped I/O and interfacing / 227

- III. Input/Output with the 6526 CIA / 228

- A. Data-direction registers and I/O ports / 228

- B. A joystick as an input device / 230

- C. A Commodore 64 control port as an output port / 234

- D. More input/output circuits / 238

- IV. Counting and Timing with the 6526 CIA / 242

- A. Counting/timing fundamentals / 242

- B. Counting/timing programming examples / 246

- C. A counting/timing application / 251

- V. Summary / 256

- VI. Exercises / 256

# Appendix A Decimal, Binary, and Hexadecimal Number Systems / 259

- I. Introduction / 259

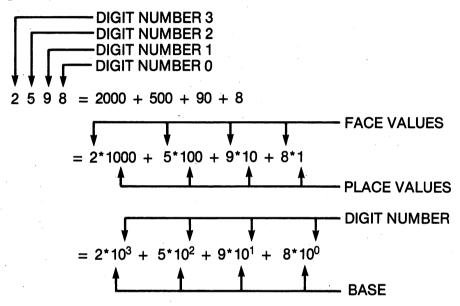

- II. Decimal Numbers / 261

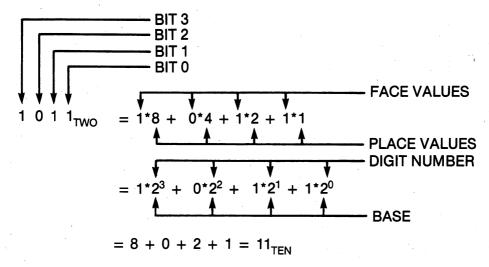

- III. Binary Numbers / 262

- IV. Hexadecimal Numbers / 265

- V. Problems / 268

Appendix B The Computer Assisted Instruction Program / 269

Appendix C The 6510 Instruction Set Summary / 273

Glossary / 279

Index / 287

Documentation for Diskette to Accompany Assembly Language Programming with the Commodore 64 / 293

# **Preface**

Welcome to life in the computer fast lane—programming with assembly language. Programs written with assembly language have the execution speed required to create lively graphics and sounds in games and educational software. Precision measurement, control, and communications applications also require

the speed provided by assembly language programming.

In writing this book, we assumed that you have a beginning knowledge of the BASIC programming language. You do not have to be an expert, but it will help you to learn assembly language if you can write programs in either BASIC or some other high-level language. Most programmers do not begin their programming career by learning assembly language: they begin with a high-level language such as BASIC, FORTRAN, or Pascal. Once you learn assembly language, you will have the best of both worlds: the speed provided by assembly language and the computational ease of BASIC.

We have marked some sections and the contents of this book with an asterisk to indicate that these sections contain more difficult material that may be omitted if you are a beginning programmer. Later, when you have acquired greater programming experience, you may wish to return to these sections to learn these

additional concepts.

How do you learn assembly language? Not simply by reading a book about it. It seems there are several important factors. First, you must become acquainted with the instructions available in assembly language, just as you had to learn the BASIC commands. This implies more than simply memorizing the instruction set of the 6510 microprocessor inside the Commodore 64. It means that you can predict the outcome when instructions are executed. You must eventually be able to think like a microprocessor.

Next, you must study and understand simple programs. It is always educational to attempt to understand how another person's programs work. You will be given many examples in this book so that you can see how each instruction is used. In this context, it is important to have a microcomputer with which to execute the programs. It is probably impossible to learn assembly language in the abstract, that is, without a microcomputer, just as it is impossible to learn to play the piano without actually having a piano on which to practice. We have tried to make the sample programs relevant. That is, you should learn something about your computer as you learn about assembly language program-

### x Preface

ming. Almost all of the programs produce an easily observable result so that you can see immediately if the program is properly executing.

Finally, you must write, debug, and execute programs. We have provided programming exercises and problems to give you this practice, and they are given without answers. Programming problems in the real world also come without answers, and the most important activity you can undertake in learning to write programs is to write your own. If you will pardon the metaphor, sooner or later you have to remove the training wheels. Writing, debugging, and executing assembly language programs provides challenges, frustrations, and rewards just like any other human activity. Expect to make a few mistakes along the way, and expect that your success will be roughly equivalent to your effort. Always avoid writing grandiose programs: at the beginning of the book, be content with writing programs having several lines, moving to programs with 10 to 20 lines near the end of the book. Our examples and exercises should suggest many possible applications. It is up to you to try writing these programs until at last you become an excellent programmer.

Good luck to you.

Marvin L. De Jong Department of Mathematics-Physics The School of the Ozarks February, 1984

# Limits of Liability and Disclaimer of Warranty

The author and publisher of this book have used their best efforts in preparing this book and programs contained in it. These efforts include the development, research, and testing of the programs to determine their effectiveness. The author and the publisher make no warranty of any kind, expressed or implied, with regard to these programs, the text, or the documentation contained in this book. The author and the publisher shall not be liable in any event for claims of incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of the text or the programs. The programs contained in this book are intended for the use of the original purchaser.

# Note to Authors

Do you have a manuscript or software program related to personal computers? Do you have an idea for developing such a project? If so, we would like to hear from you. The Brady Company produces a complete range of books and applications software for the personal computer market. We invite you to write to David Culverwell, Publishing Director, Brady Communications Company, Inc., Bowie, MD 20715.

# Trademarks of Material Mentioned in This Text

Radio Shack is a trademark of Tandy Corporation.

Commodore 64 is a trademark of Commodore Business Machines.

# Dedication

This book is dedicated to the memory of Bones, Fang, Yertaw Wogalbukog, and the Mouse Dog.

# The Commodore 64 Microcomputer System

# I. Introduction

Human language, whether written or spoken, is a mechanism we use to communicate our thoughts to other people. On occasion, these thoughts may be a set of instructions for another person to follow in order to accomplish a specific task. In that sense, human language is very much like a computer programming language. A computer programming language is a mechanism we use to communicate a set of instructions to the computer to make it accomplish a task. With few exceptions, programming languages are written rather than spoken. You are already somewhat familiar with the programming language known as BASIC. It is likely that you began your programming experience on the Commodore 64 by learning the BASIC programming language. Now you are about to learn a new language called assembly language. We will not attempt a one-sentence definition of assembly language at this point. That would be as useful as defining French as that language used by French people. For the moment, think of assembly language as another way of communicating with the computer. This entire book is a definition of assembly language.

It may be worthwhile to point out that many computer programmers feel that learning to use assembly language is more difficult than learning BASIC. A programming language that "approximates" human language is frequently called a high-level language. A high-level language makes use of familiar words like IF...THEN..., GOTO, and PRINT, which most people can understand. BASIC is a high-level language. On the other hand, in assembly language you will encounter more foreign terms like LDA, ROL, and BIT. Assembly language is much closer to the "language" that the components of the microcomputer use to communicate with each other in order to perform a task. Since we tend to regard computers as much lower than ourselves, we call assembly language a low-level language.

Even if you have almost no knowledge of what is happening inside the microcomputer, it is quite easy to write computer programs using a highlevel language such as BASIC. Indeed, that is one of the motivations for using BASIC; you do not have to think in great detail about what is taking place inside the microcomputer. On the other hand, to write assembly language programs you must at least know something about the "brain" of the Commodore 64, its 6510 microprocessor. It is also extremely useful to have an elementary understanding of the structure of the microcomputer and how it works. The purpose of this chapter is to provide you with the information about the microcomputer that will be important to you as you learn assembly language. If you are already mildly familiar with the 6510 microprocessor and you already have an elementary understanding of how the Commodore 64 works, then you can proceed directly to the next chapter; otherwise, it will be profitable to spend some time studying this first chapter. Feel free, however, to experiment with several starting points in the book, especially with any of the first three chapters. Indeed, you may wish to skim these three chapters and then start at what, in your judgment, is the appropriate point.

All BASIC programs are written using familiar base-ten (decimal) numbers. On the other hand, experienced assembly language programmers think and work with *hexadecimal numbers* and *binary numbers*. Hexadecimal numbers have a base of sixteen while binary numbers have a base of two. Appendix A of this book explains these two number systems in more detail. Please refer to this appendix if you have had no experience with hexadecimal or binary numbers.

# II. Components of the Commodore 64

A microcomputer is a system of components including:

- A microprocessor

- ROM (read only memory)

- R/W (read/write) memory

- I/O (input/output) devices

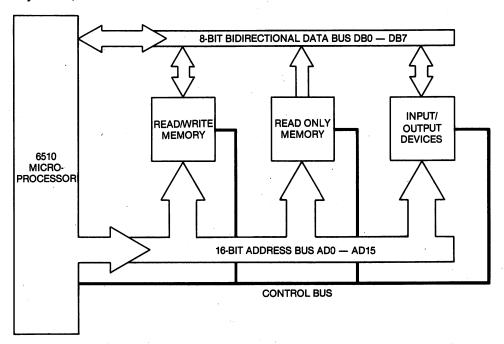

These components are interconnected by three sets of electrical conductors known as *buses*. We will briefly describe the components, then the buses. A sketch of the microcomputer system is shown in Figure 1-1.

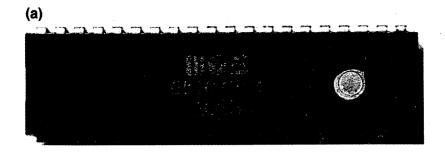

The words "microcomputer" and "microprocessor" are often confused. Your Commodore 64 is a microcomputer consisting of the components mentioned above. On the other hand, the microprocessor is just one component of the microcomputer. The 6510 microprocessor is a 40-pin integrated circuit that is responsible for controlling everything that happens in the microcomputer. Photographs of the 6510 are shown in Figure 1-2. The 6510 microprocessor moves information (data) about in memory, it performs all

the arithmetic operations that take place, and it makes simple decisions based on certain events (for example, depending on which keys are pressed on the keyboard).

Figure 1-1. Simplified block diagram of the Commodore 64 microcomputer system.

Of course, the microprocessor has no will of its own, nor does it think for itself. It operates under the control of *programs* written by human beings. This book will teach you how to control the microprocessor by writing assembly language programs. These programs must be translated into information the microprocessor can understand, and then they must be stored in the *memory* of the microcomputer system. The 6510 microprocessor is capable of identifying 65,536 different memory locations. Each memory location stores eight bits (binary digits) of information. A binary digit has two possible values, one or zero. The eight bits are designated

D7, D6, D5, D4, D3, D2, D1, D0

This means that bit zero, or D0, is the least-significant bit, while bit seven, D7, is the most-significant bit. Just as in the case of decimal numbers where the least-significant digit is the rightmost digit and the most-significant digit is the leftmost digit, a binary number such as

10010100

has its least-significant bit on the right and its most-significant bit on the left. (Computer scientists, unlike other of earth's creatures, always start counting with the number zero rather than the number one. Thus, the eighth bit in a memory location is called "bit seven.")

Figure 1-2. Photograph of the Commodore 6510 microprocessor. (a) The 6510 microprocessor. (b) The 6510 microprocessor inside the Commodore 64.

The eight bits of information in a memory location collectively form an eightbit code or an eight-bit number. The eight-bit code is frequently called a byte of information (or data) or, more simply still, a byte.

There are two types of memory, ROM (read only memory) and R/W (read/ write) memory. The latter form of memory is frequently called RAM (random access memory). As the name implies, the microprocessor cannot modify the information stored in ROM, it can only copy information from this form of memory into the microprocessor. This process is known as a *read* operation.

Two important and lengthy programs have already been written and stored in the ROM inside your computer. These programs are the *operating system* and the *BASIC interpreter*. Both the operating system and the BASIC interpreter are written in the native language of the 6510 microprocessor, namely 6510 machine language. We will shortly describe machine language in more detail. For the time being, simply be aware that it consists of eight-bit codes stored in memory. The 6510 microprocessor is designed and constructed so that when power is first applied, the microprocessor will begin executing a machine-language program stored at a particular location in memory. This location corresponds to the beginning of the operating system. Among many other things, the operating system allows you to enter information on the keyboard, and display and edit information on the screen.

The BASIC interpreter is a machine language program that translates the BASIC commands that you give the computer into its native language. The microprocessor begins to execute programs stored in ROM as soon as you turn on the computer, and the Commodore 64 system moves quickly to the BASIC interpreter when power is first applied, giving you the READY prompt.

Now consider read/write (R/W) memory. The 6510 cannot only read information in R/W memory but it can also transfer information from itself to R/W memory. This process is known as a *write* operation. This form of memory is called "R/W memory" because with it both read and write operations are possible. While information in R/W memory is *volatile*, meaning that it disappears when power is removed, the information in ROM is *nonvolatile*. Removing the power to the microcomputer does not affect the information stored in ROM.

Information from the world outside of the computer is transferred to it by means of *input devices*. The keyboard of the Commodore 64 is the most obvious input device. It is not connected directly to the microprocessor; instead, a special integrated circuit, known as a 6526 CIA (complex interface adapter), is used to connect the 6510 to the keyboard. A device that is connected between the microprocessor and another component of the microcomputer system is known as an *interfacing* device or interfacing adapter. The 6526 VIA is very much like R/W memory in the sense that information can be transferred back and forth between it and the microprocessor. Other input devices include cassette tape players, disk drives, and modems. Again, these devices are not usually connected directly to the microprocessor. It is simpler to interface these input devices to the microprocessor either with additional electronic circuitry or with a 6526 CIA, or both.

Information is transferred from the computer to the world outside it by means of *output devices*. The most obvious output device is the television set or video monitor that you have connected to the Commodore 64. Again, greater simplicity and versatility are achieved when a special integrated circuit, known as the 6567 VIC (video interface chip), is used to interface the 6510 to the video display. Another integrated circuit, the 6581 SID (sound interface device), is used to provide sound output. Information is transferred back

and forth between the 6510 microprocessor and both the 6567 VIC and the 6581 SID in exactly the same way as information is transferred to and from R/W memory. Circuitry on the the 6567 VIC and the 6581 SID transforms this information into video and sound signals, respectively.

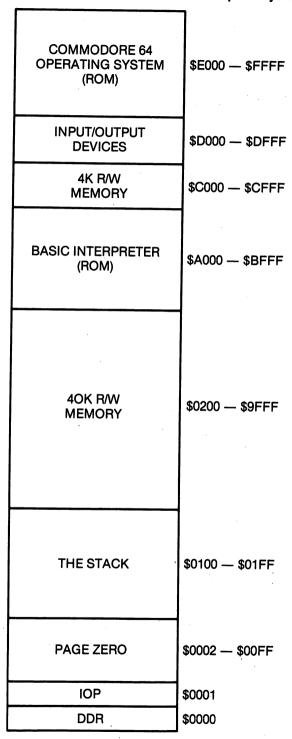

A diagram that shows the addresses of the locations occupied by ROM, R/W memory, and the I/O devices is called a *memory map* of the microcomputer system. A memory map of the Commodore 64 system is shown in Figure 1-3. To show some of the important features of the memory map, Figure 1-3 is not drawn to scale. Because the Commodore 64 microcomputer system switches blocks or *banks* of memory in and out of active use, a technique called *memory management*, it has several possible memory maps. For simplicity, in Figure 1-3 we show only the most common memory map that we will encounter. Notice that the addresses are expressed with hexadecimal numbers. Also note that hexadecimal numbers are prefaced with a "\$" symbol.

# III. Microcomputer System Buses

We turn next to an explanation of how the components of a microcomputer system are interconnected. Refer once again to Figure 1-1. Consider, first, a read operation in which a byte (eight bits of information) is copied from a memory location (or I/O device) into the microprocessor. The 6510 must first *identify* the memory location that it wishes to read. Like your house, a memory location is identified by a number called its *address*. The microprocessor signals the memory location it wishes to read by placing its address on the microcomputer's *address bus*. The address bus is a set of 16 electrical conductors that connect the microprocessor to R/W memory, ROM, and the I/O interfacing circuits.

The microprocessor works in the binary number system; that is, it places either a one or a zero on each of the 16 conductors to produce a 16-bit binary number. Clearly, a number cannot be sent along a wire conductor. However, there is common agreement among the components of a microcomputer—agreement built into it by its designers—that a voltage near five volts corresponds to a binary one, while a voltage near zero volts corresponds to a binary zero. If an address line is to correspond to a "one," then the microprocessor makes the voltage on the address line five volts. If an address line is to correspond to a "zero," then the microprocessor makes the voltage on the line zero.

The 16 address lines are numbered

AD15, AD14, AD13, ..., AD2, AD1, AD0

Imagine these 16 lines as being *ordered* with AD0 on the right and AD15 on the left. Then they can be thought of as representing a 16-bit binary number

Figure 1-3. Memory map of the Commodore 64 microcomputer. To show certain details, this map is not drawn to scale.

where AD0 is the *least-significant bit*, the rightmost bit, and AD15 is the *most-significant bit*, the leftmost bit. Then the available addresses are:

|      | BIN  | NARY |      | DECIMAL | HEXADECIMAL |

|------|------|------|------|---------|-------------|

| ØØØØ | øøøø | ØØØØ | øøøø | Ø       | \$ØØØØ      |

| ØØØØ | øøøø | øøøø | ØØØ1 | 1       | \$ØØØ1      |

| ØØØØ | ØØØØ | ØØØØ | ØØ1Ø | 2       | \$ØØØ2      |

| •    | •    | •    | •    | •       | •           |

| •    | •    | •    | •    | •       | •           |

| 1111 | 1111 | 1111 | 1111 | 65535   | \$FFFF      |

where we have collected the bits into groups of four for easy reading. The smallest address is 0000 0000 0000 0000 and the largest possible address is 1111 1111 1111.

How many memory locations can be identified with this scheme? Suppose you had a dumb computer with only one address line. Then you would have two addresses, namely, zero and one, so you could address two memory locations. If the computer had two address lines, then you could have four addresses, namely, 00, 01, 10, and 11, corresponding to the four binary numbers that you can construct from two binary digits. This, only slightly smarter, computer could address four memory locations. A computer with three address lines could address eight locations. Notice that a pattern develops since

$2^{1}=2^{3}$   $2^{2}=4$   $2^{3}=8$

In other words, the number of memory locations that can be addressed by a microcomputer with n address lines is  $2^n$ . Thus, if a microprocessor had 10 address lines, it could identify  $2^{10}$  or 1,024 memory locations. A group of 1,024 memory locations is commonly called a "K" of memory. If you had 2K of memory you would have 2,048 memory locations. The 6510 microprocessor inside the Commodore 64 has 16 address lines so it can address  $2^{16}$  or 65,536 locations. 65,536 = 64\*1,024 so the Commodore 64 can address 64K of memory.

Actually, the "64" in the name of this computer refers to the amount of R/W memory available in the Commodore 64. With the memory management scheme mentioned earlier, the Commodore can switch in large banks of R/W memory to replace ROM. Large amounts of R/W memory are important for certain tasks, such as word processing. Large amounts of R/W memory are also necessary if you wish to use a high-level language other than BASIC, such as Pascal. When another language is used, the BASIC interpreter in ROM is of no use, and it is extremely useful to be able to replace it with R/W memory.

Suppose the microprocessor identifies the particular memory location it wishes to read by placing the address on the address bus. How do the eight bits of information get from the memory location to the microprocessor? There is another bus that connects the various components in the microcomputer system. This eight-conductor bus is called the *data bus*. The eight data bus conductors are numbered

When a memory location is read, each of the eight bits in a memory location controls the voltage level on a corresponding line of the data bus. The microprocessor interprets the voltage levels as binary ones or zeros, and therefore it knows what eight-bit code is stored in the memory location it identified.

A byte can be transferred from the microprocessor to a R/W memory location in a similar fashion. First, the microprocessor places on the address bus the address of the memory location to which it wishes to write. Then the microprocessor modifies the voltage levels on the data bus to represent the eight-bit code it wishes to transfer to memory. The memory device interprets these voltage levels as binary ones and zeros and stores them.

Notice that information can go in two directions on the data bus. In a read operation, an eight-bit code is transferred from memory to the microprocessor. In a write operation, an eight-bit code is transferred from the microprocessor to memory. This is why the data bus is called a *bidirectional* bus. We have described this in Figure 1-1 by having the arrows on the data bus point in two directions, indicating that information can flow in two directions.

Here are a few more subtle problems to consider. How does a memory location distinguish between read and write operations when it is addressed by the microprocessor? Moreover, how does it know *when* it should respond? The answers lie in additional information that the microprocessor supplies on the *control bus*. One line on the control bus is called the *R/W (read/write) line*. If a read operation is to take place, the microprocessor will place a five-volt signal on the *R/W* line. If a write operation is to take place, the microprocessor will bring the *R/W* line to zero volts.

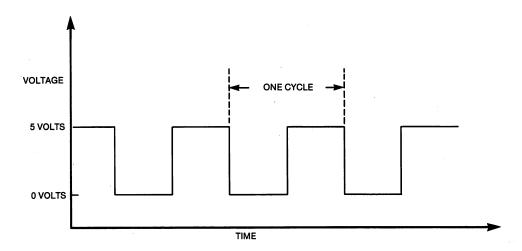

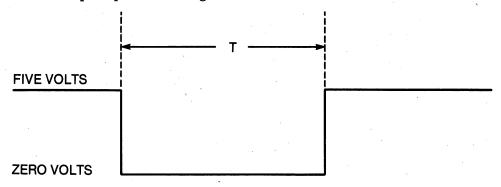

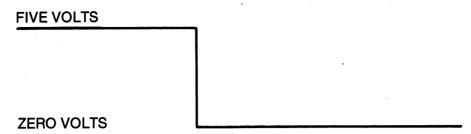

Another line on the control bus carries a *clock signal*. All read and write operations are synchronized with this clock signal so that the various components of the system know when they are to respond. In the Commodore 64 system, the clock ticks at a rate of 1,022,727 times a second. In other words, it takes a little less than one millionth of a second (one microsecond) for a read or write operation to take place. The clock signal actually is a square wave that oscillates back and forth between zero volts and five volts at a regular rate. The clock rate is not described in terms of ticks, but rather in terms of *clock cycles*. A clock cycle is described in Figure 1-4. In the case of the Commodore 64, the clock rate is 1,022,727 cycles per second. A cycle per second is a Hertz, abbreviated Hz. Thus, the clock frequency is 1.022727 MHz (Mega is one million).

# IV. The Microcomputer in Action

You now know how information is moved around inside the microcomputer. Although read and write operations are of the greatest importance to the operation of a microcomputer, very little is accomplished by simply moving eight-bit codes back and forth between the 6510 microprocessor and memory. Information must eventually be *processed*. We turn next to a brief description of some of the processes or operations that can be achieved by the 6510 and an explanation of how they are accomplished.

Figure 1-4. The clock signal of the Commodore 64 microcomputer system. The clock frequency is 1.022727 MHz.

To process information, the 6510 microprocessor was designed and built to carry out a certain number of *instructions*. These instructions make up the *instruction set* of the microprocessor. An instruction consists of one, two, or three eight-bit codes. Because it is difficult for human beings to remember eight-bit codes, the instruction set is also described with a group of three-letter "words" called *mnemonics*. Some examples are LDA, STA, BIT, ROL, and JSR. The mnemonics of the 6510 instruction set and an English-language description of each instruction is given in Table 1-1. This book is, in one sense, an elaboration of Table 1-1. The mnemonics are central to programming in assembly language.

Table 1-1. English-language description of the 6510 instruction set.

| Mnemonic | Description |

|----------|-------------|

|          |             |

### **Data Transfer Instructions**

LDA Copy the code in a memory location into the accumulator.

**LDX** Copy the code in a memory location into the X register.

LDY Copy the code in a memory location into the Y register.

**STA** Transfer the code in the accumulator to a location in memory.

**STX** Transfer the code in the X register to a location in memory.

**STY** Transfer the code in the Y register to a location in memory.

TAX Transfer the code in the accumulator to the X register.

**TXA** Transfer the code in the X register to the accumulator.

**TAY** Transfer the code in the accumulator to the Y register.

TYA Transfer the code in the Y register to the accumulator.

# Table 1-1. English-language description of the 6510 instruction set (continued).

Mnemonic

Description

### **Arithmetic and Logical Instructions**

- ADC Add the number in a memory location to the number in the accumulator. Add the value of the carry flag. Place the sum in the accumulator.

- SBC Subtract the number in a memory location from the number in the accumulator. Complement and subtract the value of the carry flag. Place the difference in the accumulator.

- **AND** Form the logical AND of the code in a memory location and the code in the accumulator. Place the result in the accumulator.

- **ORA** Form the logical OR of the code in a memory location and the code in the accumulator. Place the result in the accumulator.

- **EOR** Form the EXCLUSIVE OR of the code in a memory location and the code in the accumulator. Place the result in the accumulator.

### **Test Instructions**

- **CMP** Subtract the number in a memory location from the number in the accumulator. Modify the flags in the P register.

- **CPX** Subtract the number in a memory location from the number in the X register. Modify the flags in the P register.

- **CPY** Subtract the number in a memory location from the number in the Y register. Modify the flags in the P register.

- BIT Form the logical AND of the code in a memory location and the code in the accumulator. Modify the Z flag. Copy bit seven of the memory location into the N flag. Copy bit six of the memory location into the V flag.

# Register Shift and Modify Instructions

- **INC** Increment the number in a memory location by one.

- **DEC** Decrement the number in a memory location by one.

- **INX** Increment the number in the X register by one.

- **DEX** Decrement the number in the X register by one.

- **INY** Increment the number in the Y register by one.

- **DEY** Decrement the number in the Y register by one.

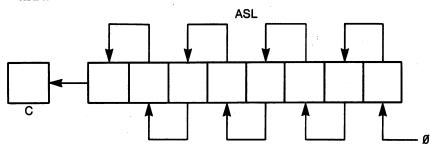

- ASL Shift the code in a memory location or the accumulator left by one bit. Place a 0 in bit zero. Shift bit seven into the carry flag.

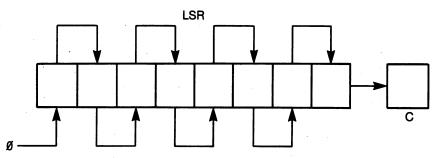

- LSR Shift the code in a memory location or the accumulator right by one bit. Place a 0 in bit seven. Shift bit zero into the carry flag.

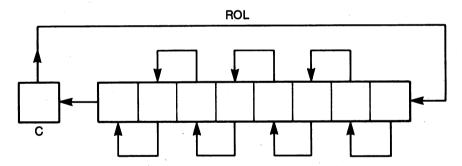

- **ROL** Rotate the code in a memory location or the accumulator left by one bit. Rotate the carry flag into bit zero and bit seven into the carry flag.

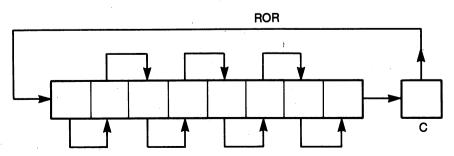

- **ROR** Rotate the code in a memory location or the accumulator right by one bit. Rotate the carry flag into bit seven and bit zero into the carry flag.

| 3. |    |      |

|----|----|------|

| Mn | em | onic |

|    |    |      |

### Description

### Flag Set and Clear Instructions

- **CLC** Clear the carry flag C to zero.

- **SEC** Set the carry flag C to one.

- CLD Clear the decimal mode flag to zero.

- **SED** Set the decimal mode flag to one.

- CLI Clear the interrupt disable flag I to zero.

- **SEI** Set the interrupt disable flag I to one.

- **CLV** Clear the overflow flag V to zero.

### **Branch Instructions**

- **BCC** Branch if the carry flag C is clear.

- **BCS** Branch if the carry flag C is set.

- **BNE** Branch if the zero flag Z is clear.

- **BEQ** Branch if the zero flag Z is set.

- **BPL** Branch if the negative flag N is clear.

- **BMI** Branch if the negative flag N is set.

- **BVC** Branch if the overflow flag V is clear.

- **BVS** Branch if the overflow flag V is set.

# Unconditional Jumps and Returns

- JMP Jump to a new address and continue program execution.

- **JSR** Jump to a subroutine to continue execution.

- RTS Return from a subroutine to the calling program.

- **BRK** Break (jump) to execute the IRQ-type interrupt routine.

- **RTI** Return from the IRQ-type interrupt routine.

# **Stack Operation Instructions**

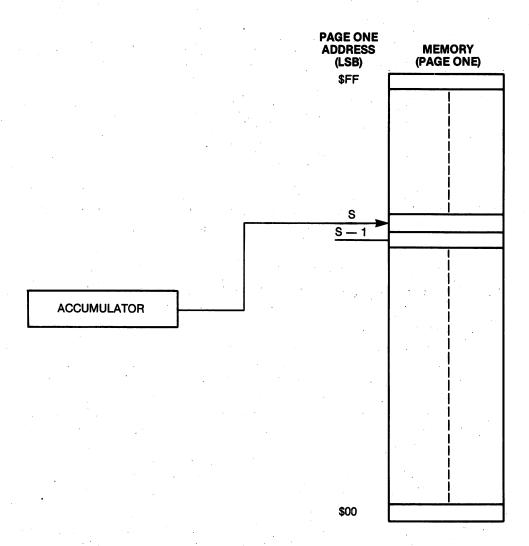

- **PHA** Push the code in the accumulator onto the stack.

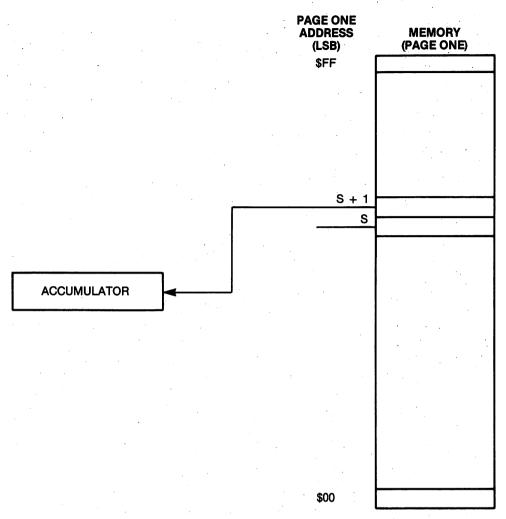

- **PLA** Pull the code from the stack and place it in the accumulator.

- **PHP** Push the code in the P register onto the stack.

- PLP Pull the code from the stack and place it in the P register.

- **TXS** Transfer the number in the X register to the stack pointer S.

- **TSX** Transfer the number in the stack pointer S to the X register.

# No Operation

**NOP** No operation takes place.

Repeating ourselves, the microprocessor accepts instructions in the form of eight-bit codes, not the mnemonics and descriptions given in Table 1-1. Human beings, not the microprocessor, use mnemonics.

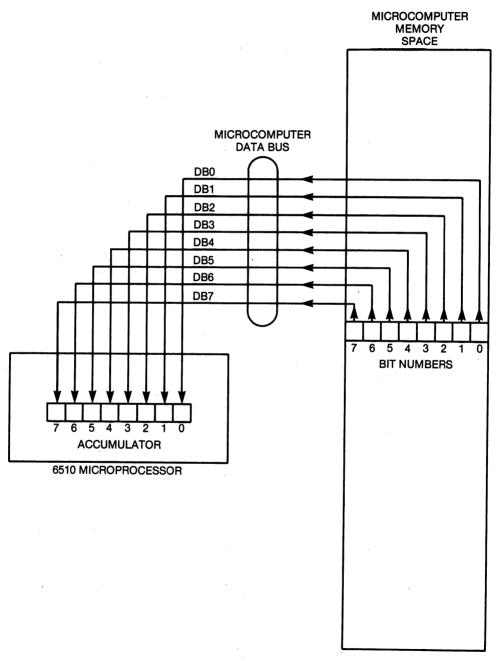

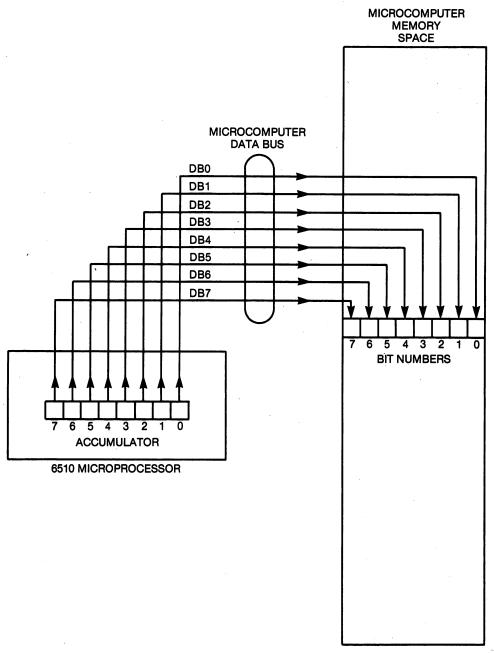

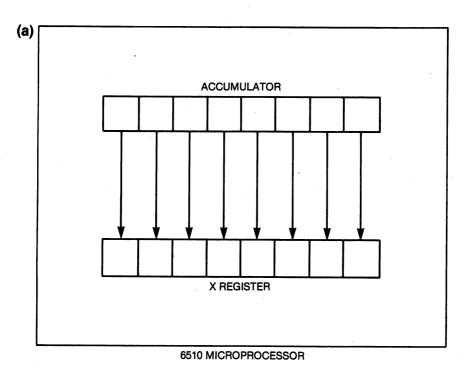

An instruction can also be described with a diagram. We have chosen to describe the LDA and STA instructions in Figures 1-5 and 1-6. In the case of the LDA instruction, an eight-bit code is transferred over the data bus from memory to the 6510 microprocessor, using the ability of the 6510 to *read*, or copy, an eight-bit code in memory. The LDA instruction is analogous to the BASIC language PEEK instruction. In the case of the STA instruction, an eight-bit code is transferred over the data bus from the 6510 microprocessor to memory, using the ability of the 6510 to *write* an eight-bit code to memory. The STA instruction is analogous to the BASIC language POKE instruction.

The eight-bit codes that make up an instruction are stored in sequential memory locations. The addresses of these memory locations serve much the same purpose as line numbers in a BASIC program. A *machine-language program* consists of an ordered set of instructions designed to accomplish a specific objective. In running a machine-language program, the microprocessor reads, in succession, the eight-bit codes that comprise the instructions to be executed, and the microprocessor performs the desired operations in sequence.

It is possible, therefore, to distinguish between two kinds of information that are stored in memory, *programs* and *data*. For example, if you are using a word processing program, the word processing program itself occupies one portion of memory, while the words you type on the keyboard are stored as data in another portion of memory. In the area of memory devoted to the program, the microprocessor is busily engaged in reading and executing machinelanguage instructions. The data it processes is, with some exceptions, stored at another place in memory.

An example of an actual machine-language program should make all this clear. Our program will add two numbers and store the result. First let us load the program, then we will load the data, and then we will execute the program. Following that, we will briefly explain the program. You are now going to load and execute your first machine-language program. We will use BASIC POKE commands to store three instructions of a machine-language program in memory. Although the POKE instruction uses decimal numbers, the BASIC interpreter converts these decimal numbers into binary numbers in order to store them in the memory location specified by the first number in the POKE instruction. Perform the following POKE commands:

```

POKE 49152, 173

POKE 49153, 52

POKE 49154, 194

POKE 49155, 109

POKE 49156, 53

POKE 49157, 194

POKE 49158, 141

POKE 49159, 0

POKE 49160, 207

POKE 49161, 96

```

The machine-language *program* is now in memory. Do not be concerned with the origin of the codes that you POKEed into memory. That mystery will be solved in Chapter 2.

Figure 1-5. Diagram of the LDA instruction.

Now let us POKE the *data* into memory. The data consists of the two numbers to be added. Let us add two and three to get five. One addend goes in location \$C234 (49716) and the other in location \$C235 (49717). Perform these two commands:

POKE 49716, 2 POKE 49717, 3

Figure 1-6. Diagram of the STA instruction.

To execute this machine-language program, perform the BASIC command SYS 49152

which directs BASIC to perform a machine-language program whose instructions begin at the address \$C000 (49152).

The machine-language program stores the answer in memory location \$CF00 (52992). After executing the program, perform the BASIC command

PRINT PEEK(52992)

The PEEK instruction reads a binary number in memory and converts it into a decimal number. You should get an answer of five. (You will get six for an answer if the 6510 still contained a "carry" from a previous addition. More about that later.)

You have just stored and executed a machine-language program. The purpose of this exercise is to begin to acquaint you with the idea that machine-language programs consist of binary codes stored in sequential memory locations. Now let us describe this program in a little more detail.

The program adds an eight-bit number stored in the memory location whose address is \$C234 to an eight-bit number stored in the memory location whose address is \$C235, and it stores the sum of these numbers in the memory location whose address is \$CF00. Using a read operation, the number in location \$C234 is first copied into the eight-bit register in the 6510 microprocessor where all arithmetic operations take place. This eight-bit register is known as the accumulator. An LDA instruction accomplishes this task (refer to Figure 1-5). Next, the microprocessor must add the number just read to the number stored in location \$C235. An ADC instruction accomplishes this. The ADC instruction is analogous to the "+" operation in the BASIC language. Finally, the 6510 must use a write operation to store the sum in location \$CF00. An STA instruction performs this task, completing the program (refer to Figure 1-6).

The machine-language program that achieves this simple programming task is shown in Table 1-2 in binary and hexadecimal. The decimal version was given above in the series of POKE commands. The mnemonics for the instructions are also given, to make the program more understandable. The three instructions have been delineated by spaces for easy identification. Below the program, we have given a simple example of the actual data that we used when we executed the program. Study the machine-language program in Table 1-2. Observe that each of the three instructions in this simple program consists of three bytes. The first byte identifies the nature of the operation that is going to take place. The second and third bytes give the address of the memory location of the data. Notice that the least-significant eight bits of the address are given first and the most-significant eight bits of the address are given last. Although you may think this is awkward, there are good reasons why the microprocessor was designed to work in this way.

It is important to realize that in addition to informing the microprocessor what instruction is desired, the program must specify, by one means or another, where the data is to be found. In the example just illustrated, each instruction specifies the full 16-bit address of the memory location of the data.

| Program<br>Memory        | Mo              | ogram<br>emory          | Assembly-            |

|--------------------------|-----------------|-------------------------|----------------------|

| Address<br>(Hexadecimal) | Co.<br>(Binary) | ntents<br>(Hexadecimal) | Language<br>Mnemonic |

| \$C000                   | 10101101        | \$AD                    | LDA                  |

| C001                     | 00110100        | 34                      |                      |

| C002                     | 10100010        | C2                      |                      |

| C003                     | 00111101        | 6D                      | ADC                  |

| C004                     | 00110101        | 35                      |                      |

| C005                     | 10100010        | C2                      |                      |

| C006                     | 10001101        | 8D                      | STA                  |

| C007                     | 00000000        | 00                      |                      |

| C008                     | 10101111        | CF                      |                      |

| Data                     | 1               | Data Data               |                      |

| Memory                   | Me              | emory                   |                      |

| Address                  | Contents        |                         |                      |

| (Hexadecimal)            | (Binary)        | (Hexadecimal)           |                      |

| \$C234                   | 0000010         | \$02                    |                      |

00000011

00000101

\$C235

**\$CF00**

Here is how the program in Table 1-2 is executed. The 6510 begins by reading the first byte of the LDA instruction. After reading this byte, which takes less than one microsecond, it *interprets* this eight-bit code while it is reading the next program byte. Once it interprets the first code, it knows that the second and third bytes of the LDA instruction are the address of the data it is to read from memory. It takes three clock cycles of the microcomputer system clock to read all three bytes of the instruction. During the next clock cycle, it reads the byte of data stored at location \$C234. Thus, the entire three-byte LDA instruction takes four clock cycles. Three clock cycles were used to read the instruction, and the fourth was used to carry out the intent of the instruction.

\$03

\$05

(after execution)

Next, the microcomputer reads and interprets the first byte of the add (ADC) instruction. Having interpreted the eight-bit code, it knows that the next two program bytes are the address of the memory location of the number it is to add to the number in the accumulator. It reads all three bytes of the instruction in three clock cycles, one for each byte. During the fourth clock cycle, it adds the number in location \$C235 to the number in the accumulator and replaces the number in the accumulator with this sum. The ADC instruction also takes four clock cycles.

Finally, the microprocessor reads and interprets the first byte of the STA instruction. The eight-bit code informs it that it must write the contents of the accumulator to the address given in the next two program bytes. This takes one clock cycle. During the next two clock cycles, it reads both bytes of the address of the destination of the number in the accumulator. During the fourth and final clock cycle, it stores (writes a copy of) the number in the accumulator into location \$CF00, completing the program in 12 clock cycles, or just under 12 microseconds.

Admittedly this is a simple program, and we have taken the liberty of slightly oversimplifying the operation of the microprocessor. By now you should have some inkling of the nature of machine language and the sequence of events associated with the execution of a machine-language program. Also, you are now in an excellent position to proceed to the next section, where we will introduce some of the other registers in the 6510 microprocessor. Furthermore, you are also almost ready to begin programming. In the next few chapters we will describe much more efficient ways of creating, storing, and executing machine-language programs.

# V. An Overview of the 6510 Registers

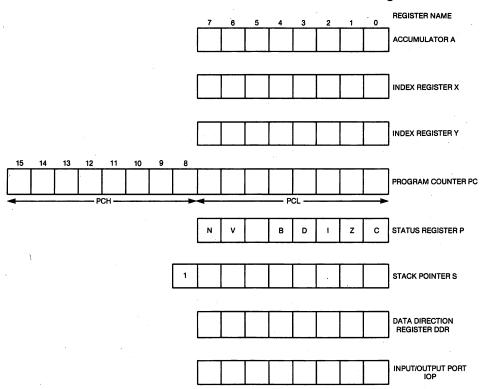

The registers in the 6510 microprocessor that are of interest to the assembly-language programmer are shown in Figure 1-7. The bit numbers are identified at the top of the accumulator and the program counter. We will briefly discuss each of these registers. Think of this as a global view. When you look at a globe you do not see or understand many details. These will become obvious only with more study and the use of the registers in programming examples.

# The Accumulator—A

You have already been introduced to the accumulator. It is used by the assembly-language programmer more often than any other register. When performing an arithmetic operation, such as addition, two numbers called *operands* are combined to form the sum. In performing arithmetic or logical operations with the 6510, one of the two operands *must* be in the accumulator; the other operand will be in memory. The result of the operation is always placed in the accumulator.

Recall that when programming with BASIC you combined *variables* in various arithmetic operations. In assembly-language programming, one of the variables is always A, the symbol for the number in the accumulator. The other variable will be M, a symbol for a number in some memory location. In addition to being used for arithmetic and logical operations, the accumulator may be used for data transfers to and from memory by means of the LDA and STA instructions described in Table 1-1 and Figures 1-5 and 1-6.

Figure 1-7. Register structure of the 6510 microprocessor.

# The X Index Register—X

In the BASIC language, the programming structure known as a *loop* is frequently implemented with a FOR...NEXT... instruction. Some variable serves as a *loop counter*. The variable is incremented by one until it reaches a certain value and then the program exits the loop. In assembly language, the number in the X register will frequently serve as a loop counter.

The BASIC language allows the use of array variables, of the form VAR(I), where I is called a *subscript* or *index*. When programming in assembly language, you will frequently use the number in the X register as a subscript or index. That is why it is called an *index register*.

The X register can also be used for transferring eight-bit codes to and from memory with the LDX and STX instructions (refer to Table 1-1).

# The Y Index Register—Y

The Y register is used in the same way as the X register; that is, used as a loop counter and as a subscript or index. The Y register can also be used for transferring data with the LDY and STY instructions (refer to Table 1-1).

# The Program Counter—PC

A computer program written in any language is an *ordered* set of instructions. The BASIC language uses *line numbers* to order the instructions; how are the instructions ordered in machine-language and assembly-language programs? We have already hinted at the answer. The instructions are stored one after the other in memory and are ordered by the *addresses* of the memory locations that the program occupies.

The program counter is the register in the 6510 microprocessor that keeps track of the address of the next program byte to be read by the 6510. Since addresses are 16-bit numbers, the program counter is a 16-bit register. If you could watch the program counter during the execution of a program, the program counter would appear to count, except when branches or jumps occur: then it would appear to jump forward or backward in its counting.

# The Processor Status Register—P

Refer again to Figure 1-7. Notice that the P register is the only one that has specific bits identified. Each bit (with the exception of bit five, which is not used) is called a *flag* or *condition code*. These flags are modified, set or cleared, by operations and events that take place during program execution. A flag is set if it has the value one, it is clear if it has the value zero. For example, if the addition of two eight-bit numbers produces a *carry*, then the carry flag, C, will be set; otherwise, it will be cleared. If, for example, an AND instruction gives a result of *zero*, then the zero flag, Z, is set; otherwise, it is cleared. So-called *branch instructions* are used to test the flag conditions and force the program to branch to another instruction, very similar to the IF...THEN... instruction in BASIC. The flags will be discussed as the need arises in subsequent chapters.

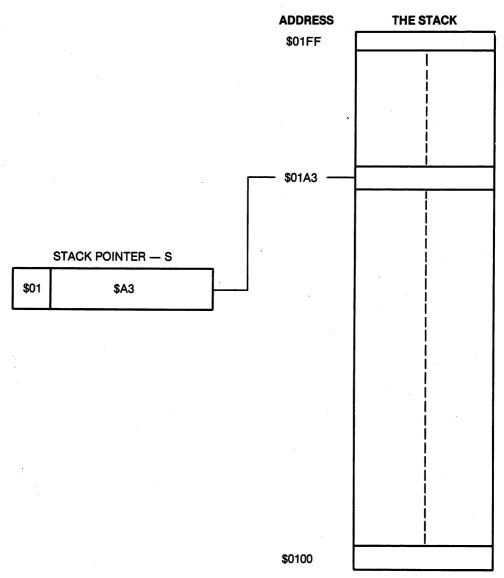

# The Stack Pointer—S

This register is used to *point* to the locations in memory whose addresses lie from \$0100 to \$01FF, called the *stack*. The number in the stack pointer identifies the least-significant byte (\$00 - \$FF) of the address. The most-significant byte of the address is *understood* to be \$01. That is why the "one" appears in bit eight of the stack pointer (refer to Figure 1-7). The stack is used to store information when subroutines and interrupts are executed. It will be described in more detail in Chapter 9.

# The Input/Output Port Registers—DDR and IOP

The 6510 microprocessor is a member of the 6502 family of microprocessors. The 6510 differs from some of the other family members because it has an onboard input/output port. This port can input or output up to eight bits of

information. The address of the I/O port is \$0001. Its data-direction register is located at \$0000. The number in the DDR (data-direction register) simply determines whether a particular bit of the port will be used to input information or to output information. There is a one-to-one correspondence between the bits in the DDR and the bits in the IOP. A one in a particular bit in the DDR makes the corresponding bit in the IOP an *output bit*. A zero in a particular bit in the DDR makes the corresponding bit in the IOP an *input bit*. The Commodore 64 system uses this I/O port to switch ROM in and out of the memory space and to perform cassette read and write operations. It is not considered to be a user port, but in Chapter 11 we will illustrate how it is used to switch banks of memory in and out of active use.

This completes our overview of the structure and operation of the Commodore 64 microcomputer system. You should have a much greater appreciation of how it works. This background will become more and more useful as you begin programming in assembly language, a language in which the programmer is more intimately associated with the operation of the microcomputer than any other language. Clearly, to use BASIC you did not need to know anything about the registers in the microprocessor, but this knowledge is indispensable for assembly-language programming.

# VI. Additional Reading

Since the 6510 microprocessor is a member of the 6502 family of microprocessors, most of the literature associated with the 6502 is useful reading material for Commodore 64 assembly-language programmers. We recommend the following books:

- Commodore 64 Programmer's Reference Guide (PRG). Commodore Business Machines; Indianapolis, Indiana: Howard W. Sams & Co., Inc., 1982. (Indispensable.)

- 6502 Assembly Language Programming. Lance A. Leventhal. Berkeley, California: Osborne/McGraw-Hill, Inc., 1979. (Excellent reference for assembly-language programmers with some experience.)

- 6502 Software Design. Leo J. Scanlon. Indianapolis, Indiana: Howard W. Sams & Co., Inc., 1980. (Excellent source for a variety of 6502 assembly-language routines.)

- 6502 Software Gourmet Guide & Cookbook. Robert Findley. Elmwood, Connecticut: Scelbi Publications, 1979. (Contains a number of valuable 6502 programming examples, including floating-point arithmetic routines.)

- Programming & Interfacing the 6502, With Experiments. Marvin L. De Jong. Indianapolis, Indiana: Howard W. Sams & Co., Inc., 1980. (An introductory text to assembly-language programming and microcomputer hardware.)

# VII. Summary

The Commodore 64 microcomputer consists of a 6510 microprocessor, ROM, R/W memory, and various I/O devices. These are interconnected by the address bus, the data bus, and the control bus. Each of the 65,536 memory

locations is identified by its address. Each memory location stores eight bits of information, called an eight-bit code, an eight-bit number, or a byte. Memory is used to store both data and machine-language programs. The microprocessor can read a code stored in memory, operate on it, or store (write) a code in memory under the direction of a machine-language program. A program is an ordered set of instructions stored sequentially in memory. Instructions consist of eight-bit codes that the microprocessor reads, interprets, and executes. In order to be understood by human beings, the instructions are described by a mnemonic and an English language description. The instruction set of the 6510 consists of 56 different instructions. Six registers inside the 6510 are involved in the execution of these instructions. These registers are the accumulator, X register, Y register, program counter, processor status register, and the stack pointer.

# Writing, Assembling, and Executing Programs

#### I. Introduction

In addition to being challenging and entertaining, learning to program your computer using assembly language is useful. Assembly-language programs are never executed; they are always translated to machine language. In fact, programming with assembly language is simply an easy way to write machine-language programs. Almost every machine-language program is written using assembly language. For certain applications such as animated graphics, music synthesis, and speech recognition, the high execution speed associated with machine-language programs is essential. Programs designed to interface the microcomputer to I/O devices such as printers, modems, and laboratory instruments are usually written using assembly language. Obviously, both the operating system and the BASIC interpreter were written using assembly language. These assembly-language programs were then translated into machine language before being stored in the ROM of the Commodore 64.

To summarize, assembly language is used whenever speed is important, but it is also used in many other programs, such as word processors and spread sheets.

### II. Microcomputer Instructions

A microcomputer machine-language program is an *ordered* set of instructions. An *instruction* consists of one, two, or three eight-bit codes stored in memory, which when read by the microprocessor will cause it to carry out one of the 56 operations listed in Table 1-1.

The *first* eight-bit code of an instruction determines which of the 56 specific operations in the instruction set will be executed. This eight-bit code is called the *operation code* or, more concisely, the *op code* of the instruction. Writing

eight-bit codes is lengthy, and you seldom see the binary representation of the op code. It is more concise to express these codes in hexadecimal. Hexadecimal, a numbering system with a base of 16, is described in more detail in Appendix A. The hexadecimal representations of the op codes are listed in Table 2-1, which summarizes the 6510 instruction set.

As an aid in programming, each instruction is also given a three-letter *mnemonic* that suggests what operation is involved. These instruction mnemonics were listed in Table 1-1 and are given again in Table 2-1. Before very long you will have all 56 mnemonics memorized.

In addition to the English-language description given for each instruction in Table 1-2, we can give the *logical description* of the instruction. The logical description is simply a *symbolic* (and, therefore, concise) description of the instruction. The logical descriptions of each instruction are given in the second column of Table 2-1. In Example 2-1 we summarize the four ways of identifying an instruction for three different instructions, LDA, ADC, and STA.

Example 2-1. Illustrating the Four Ways to Identify an Instruction

| Mnemonic | <b>Logical Expression</b> | Op Code | <b>English Description</b>                                                                                    |

|----------|---------------------------|---------|---------------------------------------------------------------------------------------------------------------|

| LDA      | $M \rightarrow A$         | \$AD    | Copy the code in memory location M into the accumulator A.                                                    |

| ADC      | $A + M + C \rightarrow A$ | \$8D    | Add the number in A, the number in memory location M, and the contents of the carry flag. Store the sum in A. |

| STA      | A→M                       | \$6D    | Write the code in A to memory location M.                                                                     |

Assembly-language programs are written using mnemonics. The process of translating mnemonics and other parts of the assembly-language program to machine language is called *assembling* the program. An *assembler* is a computer program that performs the translation for you. For short programs, hand assembly using pencil, paper, and the instruction set summary in Table 2-1 is perfectly suitable. In my opinion, you can learn a great deal about assembly language *without* the added expense of an assembler. It is also more difficult to try to learn assembly language while trying to understand the idiosyncrasies of the assembler. Although other experienced programmers may disagree, my advice is to wait to purchase an assembler until you have mastered the first half of this book. Later, when you begin to write long programs, you will want to purchase an assembler. We will mention more about assemblers in Chapter 3.

### III. Addressing Modes

As stated earlier, an instruction can consist of up to three eight-bit codes. We have described the function of the first eight-bit code but we have not yet accounted for the other bytes of the instruction. Refer once again to the instruction set summarized in Table 2-1. The instruction mnemonic is found in the first column and the logical description is found in the second column. The next 13 columns contain column headings such as "IMMEDIATE," "ABSOLUTE," "ZERO PAGE," and so on, each of which is a different addressing mode. The addressing mode is related to how the microprocessor locates (in memory) the number involved in the instruction. The "number involved" in the instruction is usually called the operand. The operand is the eight-bit code or number that is the object of the instruction. (Just as every preposition in English grammar must have an object to which it refers, an assembly-language instruction has an object, in this case a number rather than a noun, to which it refers.)

Some simple examples will suffice to illustrate the concept of an operand. In the case of an LDA instruction, the operand is the number copied from memory into the accumulator. In the case of the ADC instruction, the operand is the number that is added to the number in the accumulator. In the case of the STA instruction, the operand is the number that is transferred from the accumulator to memory. Notice that what happens to the operand depends on the instruction. Sometimes it is read (LDA), sometimes it is stored (STA), sometimes it is one of the two numbers involved in an arithmetic operation (ADC or SBC), sometimes it is one of the two codes involved in a logical operation (AND, ORA, EOR), sometimes it is shifted (ASL, LSR), and so forth.

Before describing several of the addressing modes, we must make two simple definitions. Each 16-bit address is composed of two bytes. The least-significant byte of the address, which identifies address bits AD0-AD7, is called the *ADL* (*address low*) of the address. The most-significant byte of the address, which identifies address bits AD8-AD15, is called the *ADH* (*address high*) of the address. Sometimes the ADH is called the high byte of the address and the ADL is called the low byte of the address. Example 2-2 illustrates these ideas.

### Example 2-2. Identifying the ADL and ADH of an Address

Identify the ADL and the ADH of the address \$3C1A.

Solution: The ADL is \$1A and the ADH is \$3C. The least-significant byte of the address is represented by the last two hexadecimal digits, therefore they are the ADL. The most-significant byte of the address is represented by the first two hexadecimal digits, therefore they are the ADH.

Table 2-1. The 6510 instruction set summary. (Reprinted with permission of Semiconductor Products Division of Rockwell International)

|          | INSTRUCTIONS         |          |   | ATE | ABSOLUTE |    | ZERO PAGE |    | A | CCU | M       | IN | APLIE | D  | (IND, X) |   |    | (IND), Y |   |     |   |     |

|----------|----------------------|----------|---|-----|----------|----|-----------|----|---|-----|---------|----|-------|----|----------|---|----|----------|---|-----|---|-----|

| MNEMONIC | OPERATION            | ОР       | n | *   | ОР       | n  | #         | ОР | n | *   | ОР      | n  | *     | ОР | n        | * | ОР | n        | * | ОР  | n |     |

| ADC      | A + M + C → A (4)(1) | 69       | 2 | 2   | 6D.      | 4  | 3         | 65 | 3 | 2   |         |    |       |    |          |   | 61 | 6        | 2 | 71  | 5 | 2   |

| AND      | A ∧ M → A (1)        | 29       | 2 | 2   | 2D       | 4  | 3         | 25 | 3 | 2   |         |    |       |    |          |   | 21 | 6        | 2 | 31. | 5 | 2   |

| ASL      | C - 1 0 - 0          |          |   |     | 0E       | 6  | 3         | 06 | 5 | 2   | OΑ      | 2  | ۱ ا   |    |          |   |    |          |   |     |   |     |

| всс      | BRANCHONC = 0 (2)    | l        | ĺ |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| BCS      | BRANCH ON C = 1 (2)  |          |   |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| BEQ      | BRANCH ON Z = 1 (2)  | Π        |   |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| ВІТ      | A A M                | ı        |   |     | 2C       | 4  | 3         | 24 | 3 | 2   |         |    |       |    |          |   | 1  |          |   |     |   |     |

| ВМІ      | BRANCH ON N = 1 (2)  | 1        |   |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| BNE      | BRANCH ON Z = 0 (2)  | 1        |   |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   | ı   |

| BPL      | BRANCHONN = 0 (2)    |          |   |     |          |    |           |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| BRK      | BREAK                | ľ        |   |     |          |    |           |    |   |     |         |    |       | 00 | 7        | 1 |    |          |   |     |   |     |

| вус      | BRANCH ON V = 0 (2)  |          |   |     |          |    |           |    |   |     |         |    |       |    |          |   | l  |          |   |     |   |     |

| BVS      | BRANCH ON V = 1 (2)  | 1        |   |     |          |    |           |    |   |     |         |    |       |    | Ι.       |   |    |          |   |     |   |     |

| CLC      | 0 → C                | l        |   |     |          |    |           |    |   |     |         |    |       | 18 | 2        | 1 |    |          |   |     |   |     |

| CLD      | 0 <b>→</b> D         |          |   |     |          |    |           |    |   |     |         |    |       | D8 | 2        | 1 |    |          |   |     |   |     |

| CLI      | 0 → 1                | Π        |   |     |          |    |           |    |   |     |         |    |       | 58 | 2        | 1 |    |          |   |     |   |     |

| CLV      | 0 <b>→</b> V         | i        |   |     |          |    |           |    |   |     |         |    | ŀ     | B8 | 2        | 1 |    |          |   |     |   |     |

| CMP      | A M                  | C9       | 2 | 2   | CD       | 4  | 3         | C5 | 3 | 2   |         |    | l     |    |          |   | C1 | 6        | 2 | D1  | 5 | 2   |

| СРХ      | X - M                | ΕO       | 2 | 2   | EC       | 4  | 3         | E4 | 3 | 2   |         |    |       |    |          |   |    |          |   |     |   | i I |

| CPY      | Y - M                | Сυ       | 2 | 2   | СС       | 4  | 3         | C4 | 3 | 2   | L       |    |       |    |          |   |    |          | L |     |   | Ш   |

| DEC      | M = 1 → M            |          |   |     | CE       | 6  | 3         | C6 | 5 | 2   |         |    |       |    |          |   |    |          |   |     |   |     |

| DEX      | X - 1 - X            | 1        |   |     |          |    |           | l  |   |     |         |    |       | CA | 2        | 1 |    |          |   |     |   |     |

| DEY      | Y - 1 → Y            | 1        |   |     |          |    |           | l  |   |     |         |    |       | 88 | 2        | 1 |    |          |   | 1   | 1 |     |

| EOR      | A ¥ M → A (1)        | 49       | 2 | 2   | 4D       | 4  | 3         | 45 | 3 | 2   |         |    | ĺ     |    |          |   | 41 | 6        | 2 | 51  | 5 | 2   |

| INC      | M + 1 →M             | <u> </u> |   |     | EE       | 6  | 3         | E6 | 5 | 2   |         |    |       |    |          |   |    |          |   |     |   | Ш   |

| INX      | X + 1 → X            | Γ        |   |     |          |    |           |    |   |     |         |    |       | E8 | 2        | 1 |    |          |   |     |   |     |

| INY      | Y + 1 → Y            |          |   |     |          |    |           |    |   |     |         |    |       | C8 | 2        | 1 |    |          |   |     |   |     |

| JMP      | JUMP TO NEW LOC      | -        |   |     | 4C       | 3  | 3         |    |   |     |         |    |       |    |          |   |    |          |   |     |   |     |

| JSR      | JUMP SUB             |          |   |     | 20       | -6 | 3         | l  |   |     |         |    |       |    |          |   |    |          |   | 1   |   |     |

| LDA      | M → A (1)            | Α9       | 2 | 2   | ΑD       | 4  | 3         | A5 | 3 | 2   | <u></u> | L  | L     |    | L        |   | A1 | 6        | 2 | В1  | 5 | 2   |

Table 2-1. The 6510 instruction set summary (continued). (Reprinted with permission of Semiconductor Products Division of Rockwell International)

|     |      |     | Г. |     |   | Γ. |     |   | r  |     |    | T  |      |    | _  |      |      | PROCESSOR STATUS |        |   |        |        |    |          |        |          |

|-----|------|-----|----|-----|---|----|-----|---|----|-----|----|----|------|----|----|------|------|------------------|--------|---|--------|--------|----|----------|--------|----------|

| 2.1 | PAGE | , X | _^ | BS. | × |    | BS. | Υ | RE | LAT | VE | IN | DIRE | CT | Z. | PAGE | Ε. Υ |                  |        |   |        |        |    |          |        |          |

| ОР  | n    | #   | ОР | n   | * | ОР | n   | * | ОР | n   | *  | OP | n    | *  | ОР | n    | *    |                  | 6<br>V | 5 | 4<br>B | 3<br>D | 2  | <u>1</u> | o<br>C | MNEMONIC |

| 75  | 4    | 2   | 7D | 4   | 3 | 79 | 4   | 3 |    |     |    |    |      |    |    |      |      | N                | ٧      | • | ٠      | •      | •  | z        | С      | ADC      |

| 35  | 4    | 2   | 3D | 4   | 3 | 39 | 4   | 3 |    |     |    |    |      |    |    |      |      | N                |        | • |        | •      | •  | Z        | •      | AND      |

| 16  | 6    | 2   | 1E | 7   | 3 |    |     |   |    |     |    |    |      |    |    |      |      | N                |        |   | •      |        |    | z        | С      | ASL      |

|     |      |     |    |     |   | l  |     |   | 90 | 2   | 2  |    |      |    |    |      |      |                  |        |   |        | •      |    | •        |        | всс      |

|     |      |     |    |     |   |    |     |   | во | 2   | 2  |    |      |    |    |      |      |                  | •      | • | •      |        | •  | •        | •      | всѕ      |

|     |      |     |    |     |   |    |     |   | F0 | 2   | 2  |    |      |    |    |      |      |                  | •      | • | •      | •      | •  | •        | •      | BEQ      |

|     |      |     |    |     |   | l  |     |   |    |     |    |    |      |    |    |      | ĺ    | м,               | Me     | • | •      | •      | •  | Z        | •      | віт      |

|     |      |     |    |     |   |    |     |   | 30 | 2   | 2  |    |      |    |    |      |      | •                | •      | • | ,•     | •      | •  | •        | •      | ВМІ      |

|     |      |     |    |     |   | l  |     |   | D0 | 2   | 2  |    |      |    |    |      |      |                  | •      | • | •      | •      | •  | •        | •      | BNE      |

|     |      |     |    |     |   |    |     |   | 10 | 2   | 2  |    |      |    |    |      |      |                  | •      | • | •      | •      | •  | •        | •      | BPL      |

|     |      |     |    |     |   |    | ,   |   |    |     |    | Γ  |      |    |    |      |      | ·                | •      | • | 1      | •      | 1  | •        | •      | BRK      |

|     |      |     |    |     |   |    |     |   | 50 | 2   | 2  |    |      |    |    |      |      | •                | •      | • | •      | •      | •  | •        | •      | вус      |

| 1   |      |     |    |     |   |    |     |   | 70 | 2   | 2  |    |      |    |    |      |      |                  | •      | • | •      | •      | •  | •        | •      | BVS      |

|     |      |     |    |     |   |    |     |   |    |     |    |    |      |    |    |      |      | ٠.               | •      | • | •      | •      | •  | •        | 0      | CLC      |

|     |      |     |    |     |   |    |     |   |    |     |    |    |      |    |    |      |      | ·_               | •      | • | •      | 0      | ٠. | •        | •      | CLD      |

|     |      |     |    |     |   |    |     |   |    |     |    |    |      |    |    |      |      |                  | •      |   | •      | •      | 0  | •        | •      | CLI      |

| l   |      |     |    |     |   | -  |     |   | 1  |     |    |    |      |    |    |      |      | •                | 0      | • | •      | •      | •  |          | •      | CLV      |

| D5  | 4    | 2   | DD | 4   | 3 | D9 | 4   | 3 | l  |     |    |    |      |    |    |      |      | N                |        |   | •      | •      |    | Z        | С      | СМР      |

| l   |      |     |    |     |   | 1  |     |   | l  |     |    |    |      |    | '  |      |      | N.               | •      |   | ٠.     | •      | •  | Z        | С      | CPX      |

|     |      |     |    |     |   |    |     |   |    |     |    |    |      |    | L  |      |      | N                |        |   | •      | •      | •  | z        | С      | CPY      |

| D6  | 6    | 2   | DE | 7   | 3 |    |     |   |    |     |    |    |      |    |    |      |      | N                |        |   | •      | •      | •  | Z        |        | DEC      |

|     |      |     |    |     |   | ļ  |     |   | 1  |     |    |    |      |    | İ  |      |      | Ń                |        |   | •      | •      | •  | Z        |        | DEX      |

| 1   |      |     | 1  |     |   | l  |     |   |    |     |    |    |      |    |    |      |      | N                | •      |   | •      | •      | •  | z        |        | DEY      |

| 55  | 4    | 2   | 5D | 4   | 3 | 59 | 4   | 3 |    |     | ļ  | 1  |      |    |    |      |      | N                | •      | • | •      |        | •  | Z        | •      | EOR      |

| F6  | 6    | 2   | FE | 7   | 3 |    |     |   | L  |     | L  |    |      | L  | L  |      | Ĺ    | N                | •      | • | •      |        | .• | Z        | •      | INC      |

|     |      |     | Γ  |     |   | Π  |     |   | Π  |     |    |    |      |    |    |      |      | N                |        | • | •      | •      | •  | z        | •      | INX      |

|     |      |     |    |     |   |    |     |   |    |     |    |    |      |    | 1  |      |      | N                |        |   | •      | •      | •  | Z        | •      | INY      |

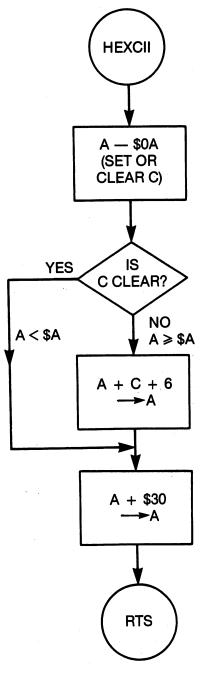

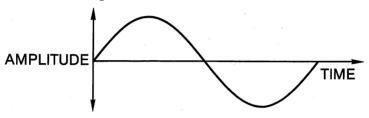

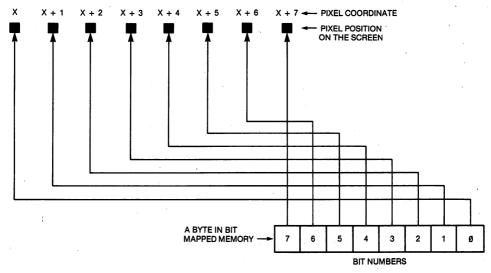

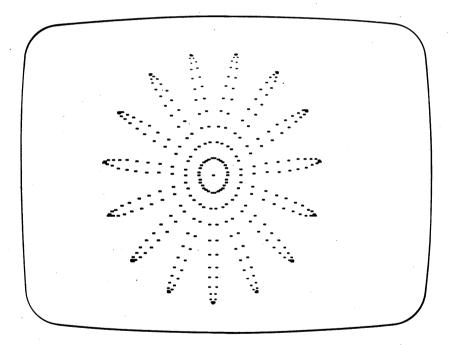

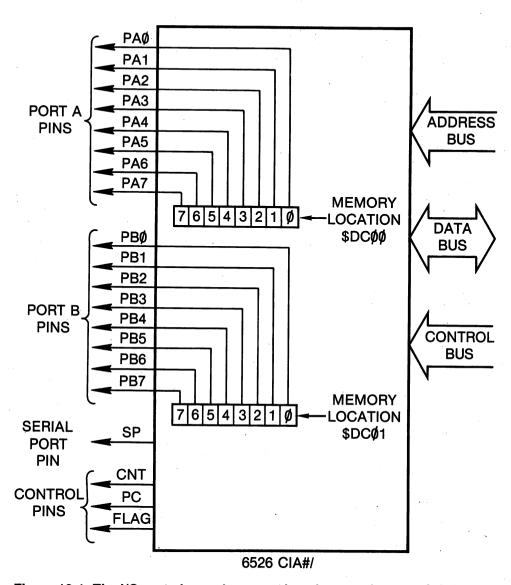

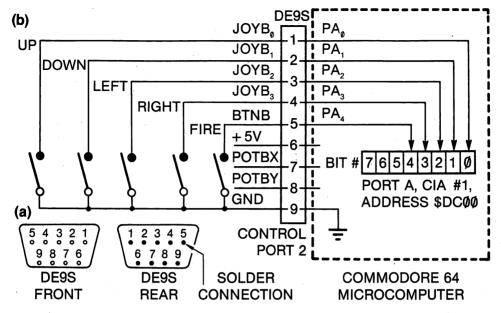

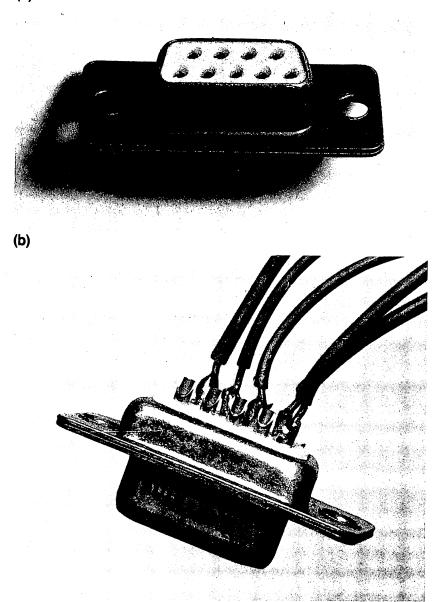

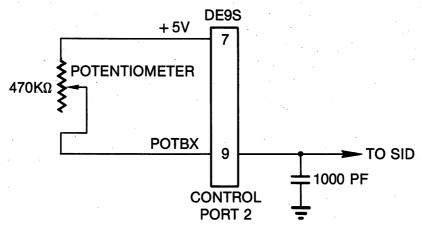

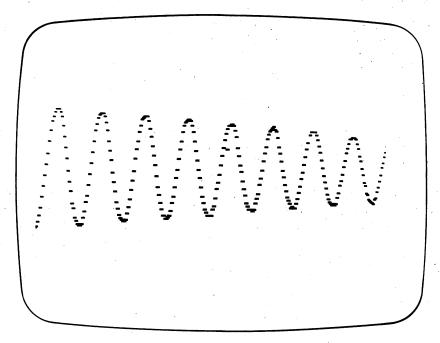

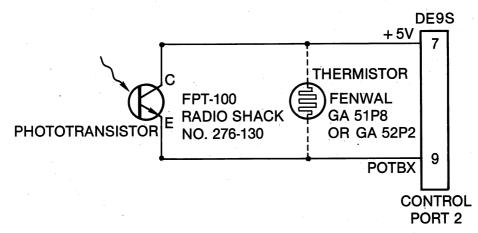

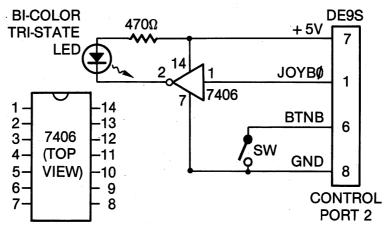

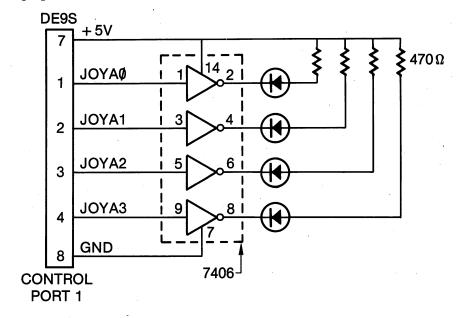

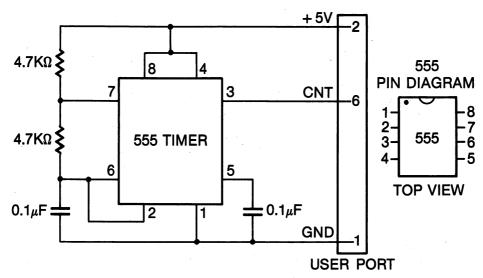

|     |      |     |    |     |   |    |     |   |    |     |    | 6C | 5    | 3  |    |      |      |                  |        | • | •      | •      | •  | •        | •      | JMP      |