AMIGA™

# Hardware Manual

# **AMIGA**

## *HARDWARE MANUAL*

COMMODORE-AMIGA, INC.

The text of this manual was written by Robert Peck, Susan Deyl, and Jay Miner.

#### COPYRIGHT

This manual is copyrighted and all rights are reserved. This document may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine readable form without prior consent, in writing, from Commodore-Amiga, Inc.

#### DISCLAIMER

COMMODORE-AMIGA, INC., ("COMMODORE") MAKES NO WARRANTIES, EITHER EXPRESSED OR IMPLIED, WITH RESPECT TO THE PROGRAM DESCRIBED HEREIN, ITS QUALITY, PERFORMANCE, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. THIS PROGRAM IS SOLD "AS IS." THE ENTIRE RISK AS TO ITS QUALITY AND PERFORMANCE IS WITH THE BUYER. SHOULD THE PROGRAM PROVE DEFECTIVE FOLLOWING ITS PURCHASE, THE BUYER (AND NOT THE CREATOR OF THE PROGRAM, COMMODORE, THEIR DISTRIBUTORS OR THEIR RETAILERS) ASSUMES THE ENTIRE COST OF ALL NECESSARY DAMAGES. IN NO EVENT WILL COMMODORE BE LIABLE FOR DIRECT, INDIRECT, INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT IN THE PROGRAM EVEN IF IT HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. SOME LAWS DO NOT ALLOW THE EXCLUSION OR LIMITATION OF IMPLIED WARRANTIES OR LIABILITIES FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES, SO THE ABOVE LIMITATION OR EXCLUSION MAY NOT APPLY.

Amiga is a trademark of Commodore-Amiga, Inc.

CBM Product Number 327272-01 rev 1.0 8.27.85

## PREFACE

This manual provides information about the Amiga[tm] graphics and audio hardware and about how the Amiga talks to the outside world through peripheral devices. A portion of this manual is a tutorial on writing assembly language programs to directly control the Amiga's graphics and hardware.

This book is intended for the following audiences:

- o Assembly language programmers who need a more direct way of interacting with the system than the routines described in the *Amiga ROM Kernel Manual*. You can find information here to help you make your programs run faster or do things that the ROM kernel routines don't do.

- o Anyone who wants to add new peripherals to the Amiga or just wants to know how the hardware works

We suggest that you use this book according to your level of familiarity with the Amiga system. Here are some suggestions:

- o If this is your initial exposure to the Amiga, Chapter 1 gives a survey of all the hardware features and a brief rundown of graphics and audio effects created by hardware interaction.

- o If you are already familiar with the system and want to acquaint yourself with how the various bits in the hardware registers govern the way the system functions, browse through chapters 2 through 8. Examples are included in these chapters.

- o For advanced users, the Appendices give a concise summary of the entire register set and the uses of the individual bits. Once you are familiar with the effects of changes in the various bits, you may wish to refer more often to the Appendices than to the explanatory chapters.

Here is a brief overview of the contents:

Chapter 1, *Introduction*. An overview of the hardware and survey of the Amiga's graphics and audio features.

Chapter 2, *Coprocessor Hardware*. Using the Copper coprocessor to control the entire graphics and audio system; directing mid-screen modifications in graphics displays and directing register changes during the time between displays.

Chapter 3, *Playfield Hardware*. Creating, displaying and scrolling the playfields, one of the basic display elements of the Amiga; how the Amiga produces multi-color, multi-graphical bit-mapped displays.

Chapter 4, *Sprite Hardware*. Using the 8 sprite direct-memory access (DMA) channels to make sprite movable objects; creating their data structures, displaying and moving them, reusing the DMA channels.

Chapter 5, *Audio Hardware*. Overview of sampled sound; how to produce quality sound, simple and complex sounds, and modulated sounds.

**Chapter 6, *Blitter Hardware*.** Using the blitter DMA channel to create animation effects and draw lines into playfields.

**Chapter 7, *System Control Hardware*.** Using the control registers to define depth arrangement of graphics objects, detect collisions between graphics objects, control direct memory access, and control interrupts.

**Chapter 8, *Interface Hardware*.** How the Amiga talks to the outside world through controller ports, keyboard, audio jacks and video connectors, serial and parallel interfaces; information about the disk controller and RAM expansion slot.

**Appendices.** Alphabetical and address-order listings of all the graphics and audio system registers and the functions of their bits; system memory map; descriptions of internal and external connectors; specifications for the peripheral interface ports; specifications for the expansion connector; and specifications for the keyboard.

**Glossary.** After the appendices, there is a glossary of important terms.

You may wish to look at the following books and manuals for further information about the Amiga:

- o The *Amiga ROM Kernel Manual* contains information about the Exec multi-tasking routines and is the source for all the C language primitives for Amiga graphics, animation, and audio.

- o The following manuals contain information about the AmigaDOS operating system:

- o *AmigaDOS User's Manual*

- o *AmigaDOS Developer's Manual*

- o *AmigaDOS Technical Reference Manual*

It is our policy to make certain that the information contained here is accurate, consistent, and up-to-date. If you should find any material confusing, inaccurate, or incomplete, please feel free to contact Amiga with your questions or comments.

# AMIGA HARDWARE MANUAL

## Table of Contents

|                                                               |            |

|---------------------------------------------------------------|------------|

| <b>Chapter 1 INTRODUCTION .....</b>                           | <b>1-1</b> |

| 1.1. COMPONENTS OF THE AMIGA .....                            | 1-1        |

| 1.2. SYSTEM EXPANDABILITY AND ADAPTABILITY .....              | 1-5        |

| <br>                                                          |            |

| <b>Chapter 2 COPROCESSOR HARDWARE .....</b>                   | <b>2-1</b> |

| 2.1. INTRODUCTION .....                                       | 2-1        |

| 2.2. WHAT IS A COPPER INSTRUCTION? .....                      | 2-3        |

| 2.3. THE MOVE INSTRUCTION .....                               | 2-4        |

| 2.4. THE WAIT INSTRUCTION .....                               | 2-5        |

| 2.5. USING THE COPPER REGISTERS .....                         | 2-7        |

| 2.5.1. Location Registers .....                               | 2-7        |

| 2.5.2. Jump Strobe Address .....                              | 2-8        |

| 2.5.3. Control Register .....                                 | 2-8        |

| 2.6. PUTTING TOGETHER A COPPER INSTRUCTION LIST .....         | 2-9        |

| 2.7. STARTING AND STOPPING THE COPPER .....                   | 2-11       |

| 2.8. ADVANCED TOPICS .....                                    | 2-13       |

| 2.8.1. The SKIP Instruction .....                             | 2-13       |

| 2.8.2. Copper Loops and Branches and Comparison Enable .....  | 2-13       |

| 2.8.3. Using the Copper in Interlace Mode .....               | 2-15       |

| 2.8.4. Using the Copper with the Blitter .....                | 2-16       |

| 2.8.5. The Copper and the 68000 .....                         | 2-16       |

| 2.9. SUMMARY OF COPPER INSTRUCTIONS .....                     | 2-17       |

| <br>                                                          |            |

| <b>Chapter 3 PLAYFIELD HARDWARE .....</b>                     | <b>3-1</b> |

| 3.1. INTRODUCTION .....                                       | 3-1        |

| 3.2. FORMING A BASIC PLAYFIELD .....                          | 3-7        |

| 3.2.1. Height and Width of the Playfield .....                | 3-7        |

| 3.2.2. Bit-Planes and Color .....                             | 3-7        |

| 3.2.3. Selecting Horizontal and Vertical Resolution .....     | 3-10       |

| 3.2.4. Allocating Memory for Bit-Planes .....                 | 3-12       |

| 3.2.5. Coding the Bit-Planes for Correct Coloring .....       | 3-14       |

| 3.2.6. Defining the Size of the Display Window .....          | 3-16       |

| 3.2.7. Telling the System How to Fetch and Display Data ..... | 3-19       |

| 3.2.8. Displaying and Redisplaying the Playfield .....        | 3-22       |

| 3.2.9. Enabling the Color Display .....                       | 3-23       |

|                                                                      |             |

|----------------------------------------------------------------------|-------------|

| 3.2.10. Summary .....                                                | 3-23        |

| <b>3.3. FORMING A DUAL PLAYFIELD DISPLAY .....</b>                   | <b>3-27</b> |

| 3.3.1. How Bit-Planes are Assigned in Dual Playfield Mode .....      | 3-29        |

| 3.3.2. How Color Registers are Assigned in Dual Playfield Mode ..... | 3-31        |

| 3.3.3. Dual Playfield Priority and Control .....                     | 3-32        |

| 3.3.4. Activating Dual Playfield Mode .....                          | 3-33        |

| 3.3.5. Summary .....                                                 | 3-33        |

| <b>3.4. BIT-PLANES AND DISPLAY WINDOWS OF ALL SIZES .....</b>        | <b>3-33</b> |

| 3.4.1. When the Big Picture is Larger than the Display Window .....  | 3-34        |

| 3.4.2. Maximum Display Window Size .....                             | 3-42        |

| <b>3.5. MOVING (SCROLLING) PLAYFIELDS .....</b>                      | <b>3-43</b> |

| 3.5.1. Vertical Scrolling .....                                      | 3-43        |

| 3.5.2. Horizontal Scrolling .....                                    | 3-45        |

| 3.5.3. Summary .....                                                 | 3-50        |

| <b>3.6. ADVANCED TOPICS .....</b>                                    | <b>3-52</b> |

| 3.6.1. Interactions Between Playfields and Other Objects .....       | 3-52        |

| 3.6.2. Hold and Modify Mode .....                                    | 3-52        |

| 3.6.3. Forming a Display with Several Different Playfields .....     | 3-53        |

| 3.6.4. Using an External Video Source .....                          | 3-53        |

| <b>3.7. SUMMARY OF PLAYFIELD REGISTERS .....</b>                     | <b>3-54</b> |

| <b>3.8. SUMMARY OF COLOR SELECTION .....</b>                         | <b>3-56</b> |

| 3.8.1. Color Register Contents .....                                 | 3-56        |

| 3.8.2. Some Sample Color Register Contents .....                     | 3-56        |

| 3.8.3. Color Selection in Low Resolution Mode .....                  | 3-57        |

| 3.8.4. Color Selection in High Resolution Mode .....                 | 3-59        |

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| <b>Chapter 4 SPRITE HARDWARE .....</b>                                 | <b>4-1</b> |

| 4.1. INTRODUCTION .....                                                | 4-1        |

| 4.2. FORMING A SPRITE .....                                            | 4-2        |

| 4.2.1. Screen Position .....                                           | 4-2        |

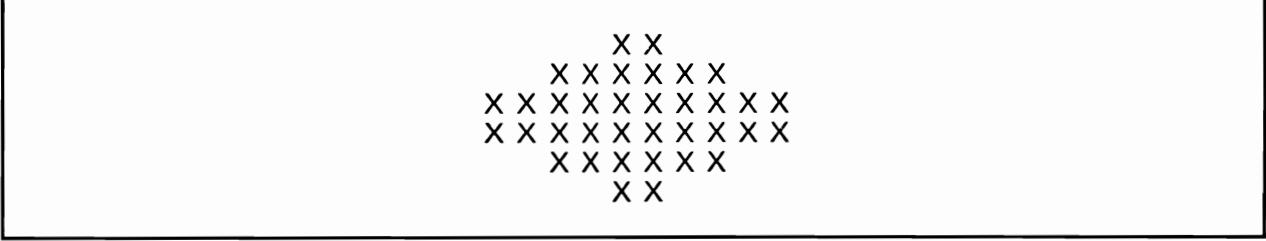

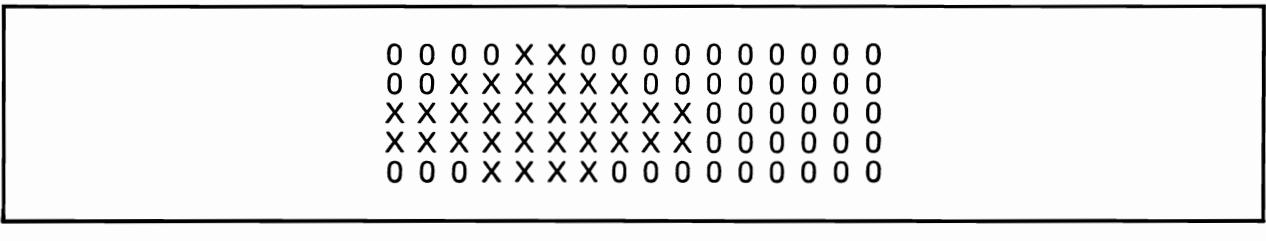

| 4.2.2. Shape of Sprites .....                                          | 4-5        |

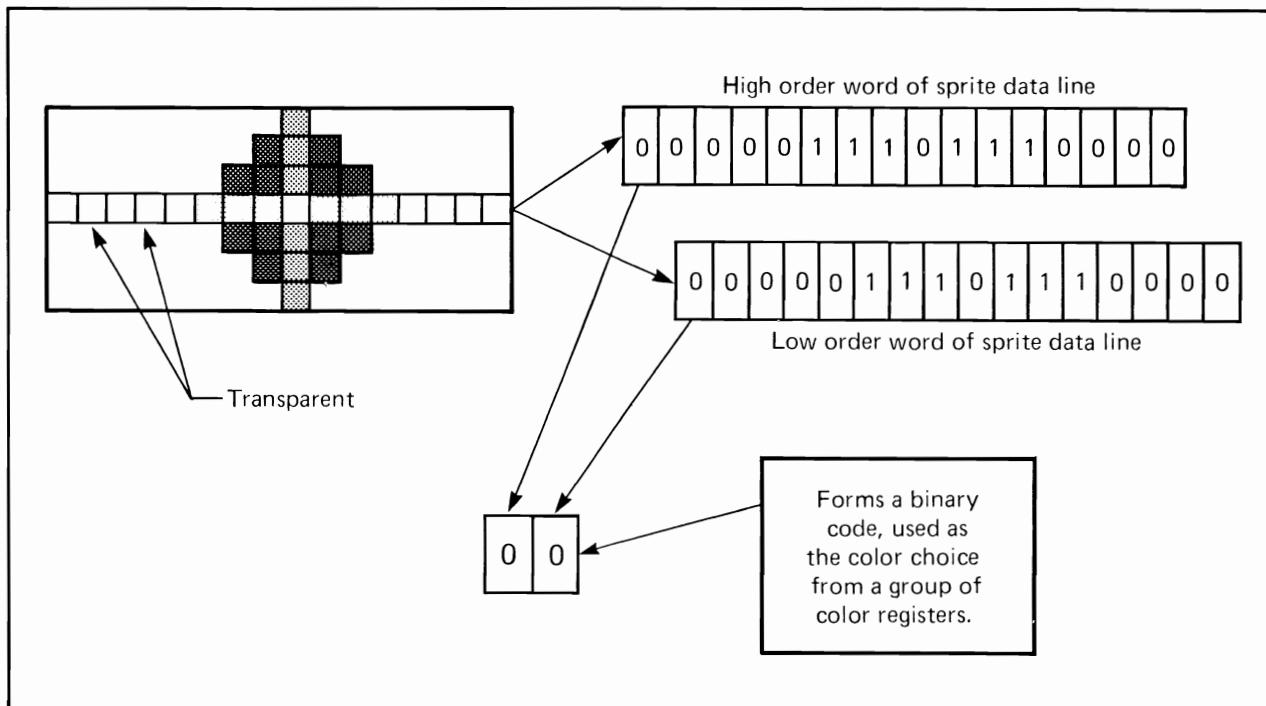

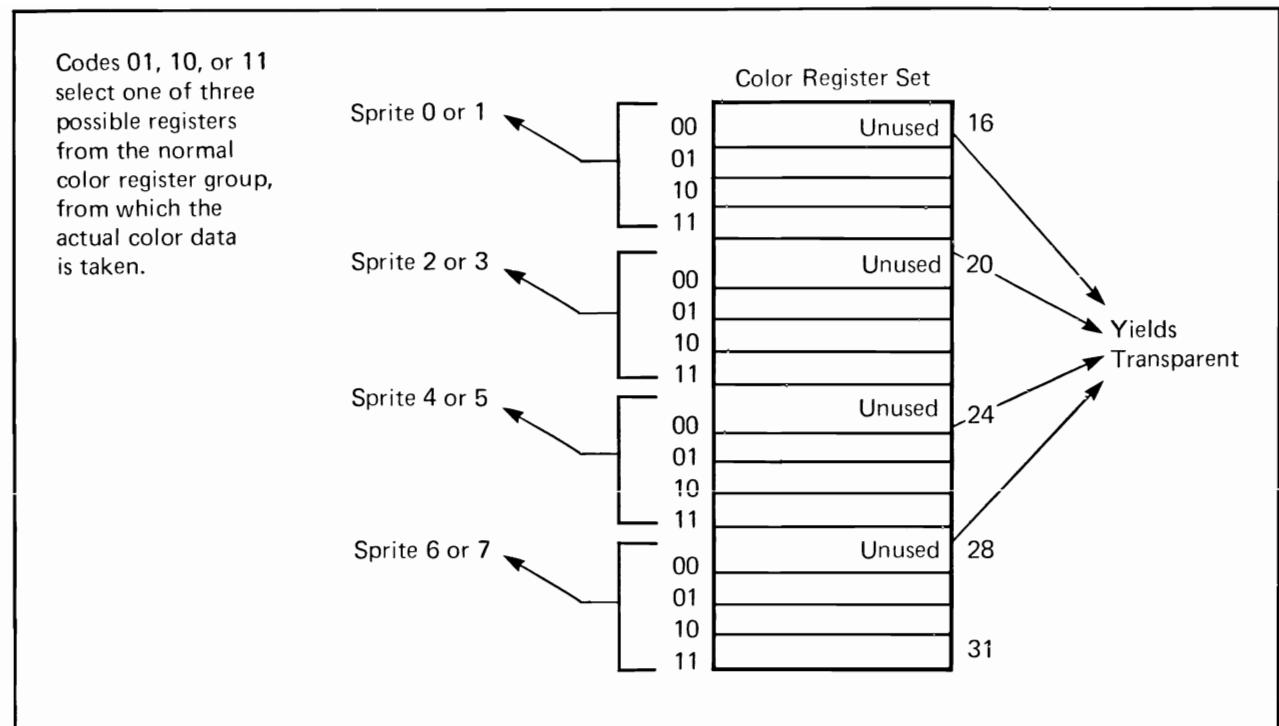

| 4.2.3. Sprite Color .....                                              | 4-7        |

| 4.2.4. Designing a Sprite .....                                        | 4-9        |

| 4.2.5. Building the Data Structure .....                               | 4-9        |

| 4.3. DISPLAYING A SPRITE .....                                         | 4-14       |

| 4.3.1. Selecting the Sprite DMA Channel and Setting the Pointers ..... | 4-14       |

| 4.3.2. Resetting the Address Pointers .....                            | 4-15       |

| 4.4. MOVING A SPRITE .....                                             | 4-15       |

| 4.5. CREATING ADDITIONAL SPRITES .....                                 | 4-16       |

| 4.6. REUSING SPRITE DMA CHANNELS .....                                 | 4-18       |

| 4.7. OVERLAPPED SPRITES .....                                          | 4-20       |

| 4.8. ATTACHED SPRITES .....                                            | 4-23       |

| 4.9. MANUAL MODE .....                                                 | 4-25       |

| 4.10. SPRITE HARDWARE DETAILS .....                                    | 4-25       |

| 4.11. SUMMARY OF SPRITE REGISTERS .....                                | 4-29       |

|                                                            |             |

|------------------------------------------------------------|-------------|

| 4.11.1. Pointers .....                                     | 4-29        |

| 4.11.2. Control Registers .....                            | 4-29        |

| 4.11.3. Data registers .....                               | 4-31        |

| <b>4.12. SUMMARY OF SPRITE COLOR REGISTERS .....</b>       | <b>4-32</b> |

| <br>                                                       |             |

| <b>Chapter 5 AUDIO HARDWARE .....</b>                      | <b>5-1</b>  |

| 5.1. INTRODUCTION .....                                    | 5-1         |

| 5.2. FORMING AND PLAYING A SOUND .....                     | 5-6         |

| 5.2.1. Deciding Which Channel to Use .....                 | 5-6         |

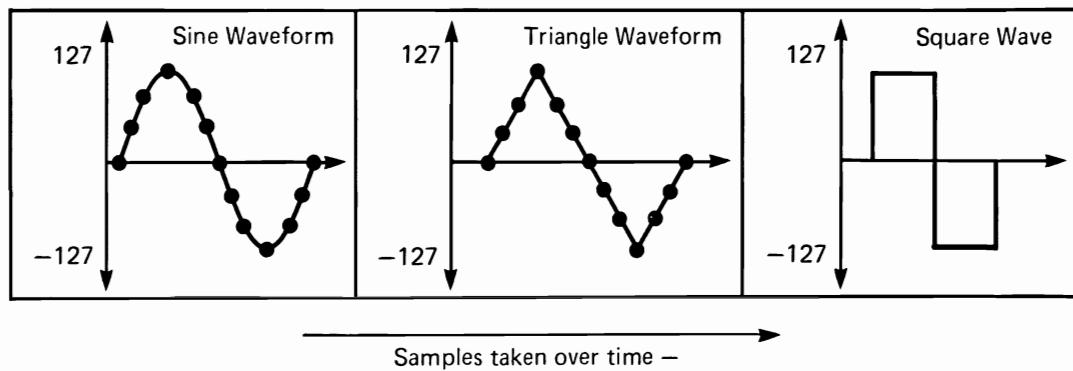

| 5.2.2. Creating the Waveform Data .....                    | 5-6         |

| 5.2.3. Telling the System About the Data .....             | 5-7         |

| 5.2.4. Selecting the Volume .....                          | 5-8         |

| 5.2.5. Selecting the Data Output Rate .....                | 5-9         |

| 5.2.6. Playing the Waveform .....                          | 5-12        |

| 5.2.7. Stopping the Audio DMA .....                        | 5-13        |

| 5.2.8. Summary .....                                       | 5-14        |

| 5.2.9. Example .....                                       | 5-14        |

| 5.3. PRODUCING COMPLEX SOUNDS .....                        | 5-16        |

| 5.3.1. Joining Tones .....                                 | 5-16        |

| 5.3.2. Playing Multiple Tones at the Same Time .....       | 5-17        |

| 5.3.3. Modulating Sound .....                              | 5-18        |

| 5.4. PRODUCING QUALITY SOUND .....                         | 5-21        |

| 5.4.1. Making Waveform Transitions .....                   | 5-21        |

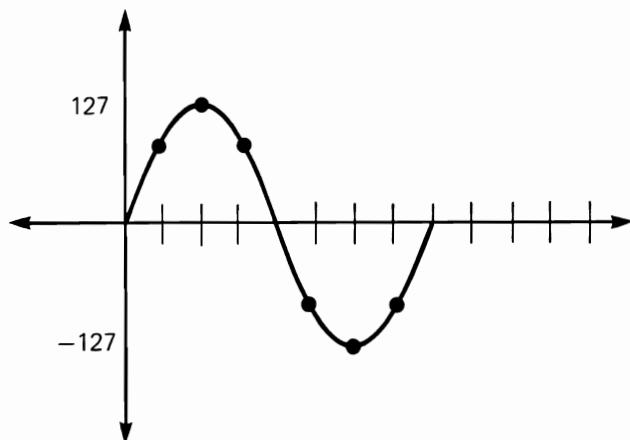

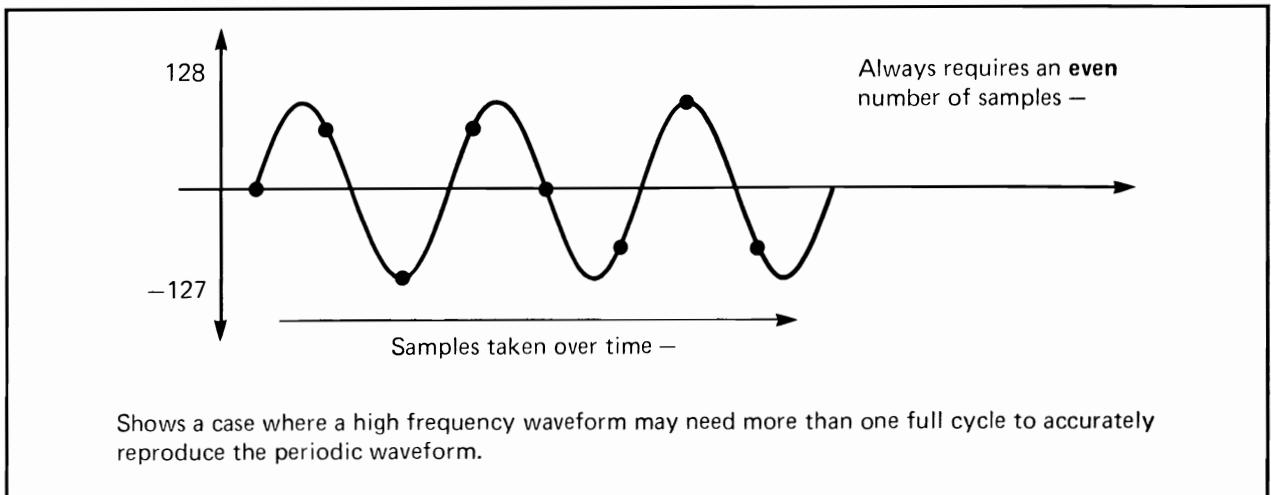

| 5.4.2. Sampling Rate .....                                 | 5-21        |

| 5.4.3. Efficiency .....                                    | 5-22        |

| 5.4.4. Noise Reduction .....                               | 5-23        |

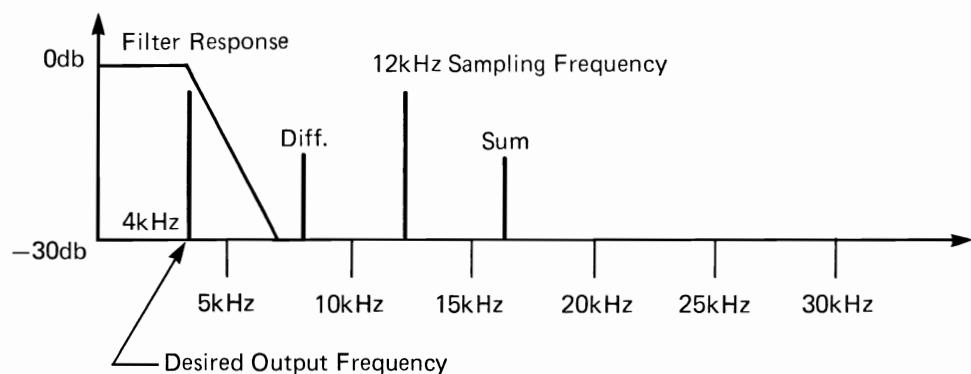

| 5.4.5. Aliasing Distortion .....                           | 5-23        |

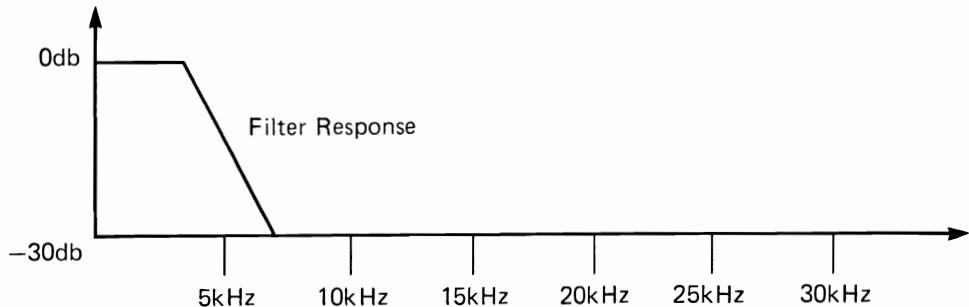

| 5.4.6. Low Pass Filter .....                               | 5-26        |

| 5.5. USING DIRECT (NON-DMA) AUDIO OUTPUT .....             | 5-28        |

| 5.6. THE EQUAL-TEMPERED MUSICAL SCALE .....                | 5-29        |

| 5.7. DECIBEL VALUES FOR VOLUME RANGES .....                | 5-31        |

| <br>                                                       |             |

| <b>Chapter 6 BLITTER HARDWARE .....</b>                    | <b>6-1</b>  |

| 6.1. INTRODUCTION .....                                    | 6-1         |

| 6.2. DATA COPYING .....                                    | 6-2         |

| 6.3. MULTIPLE SOURCES .....                                | 6-3         |

| 6.4. LOGIC OPERATIONS .....                                | 6-3         |

| 6.4.1. Blitter Logic Operations - Combining Minterms ..... | 6-4         |

| 6.4.2. Table of Commonly Used Equations .....              | 6-5         |

| 6.4.3. Equation to Minterm Conversion .....                | 6-6         |

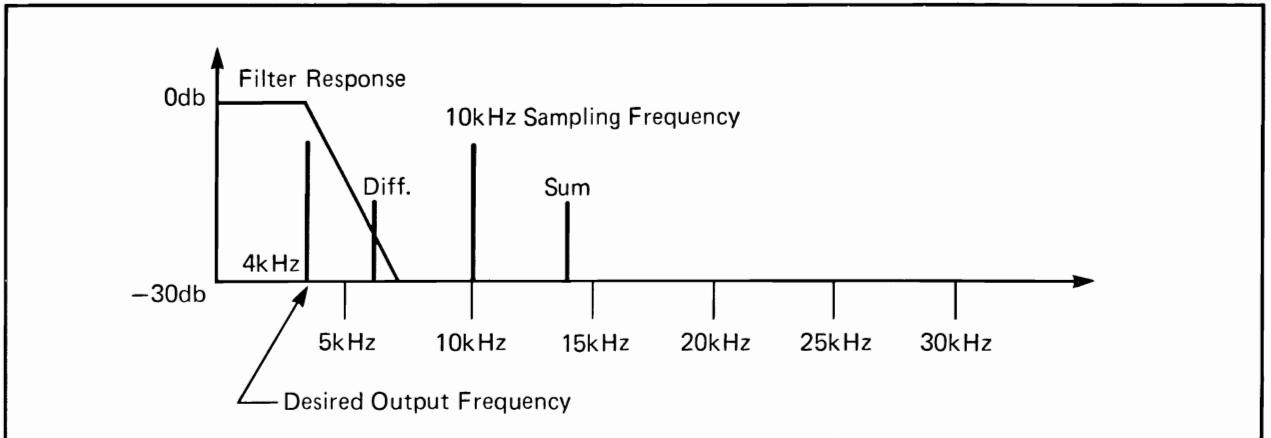

| 6.5. MULTIPLE MODULOS .....                                | 6-7         |

| 6.6. ASCENDING AND DESCENDING ADDRESSING .....             | 6-8         |

| 6.7. SHIFTING .....                                        | 6-8         |

| 6.8. MASKING .....                                         | 6-9         |

| 6.9. ZERO DETECTION .....                                  | 6-10        |

|                                                            |            |

|------------------------------------------------------------|------------|

| 6.10. AREA FILLING .....                                   | 6-10       |

| 6.10.1. Inclusive (Normal) Area Filling .....              | 6-10       |

| 6.10.2. Exclusive Area Filling .....                       | 6-12       |

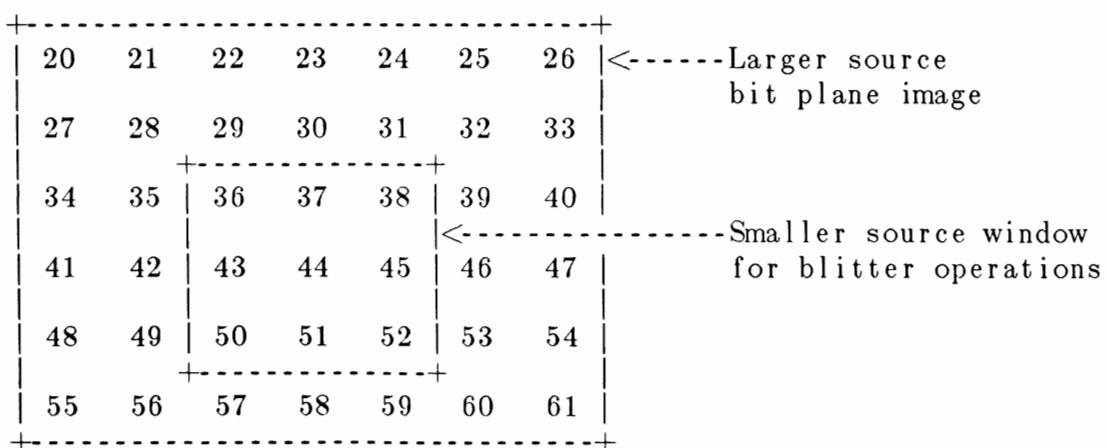

| 6.11. LINE DRAWING .....                                   | 6-13       |

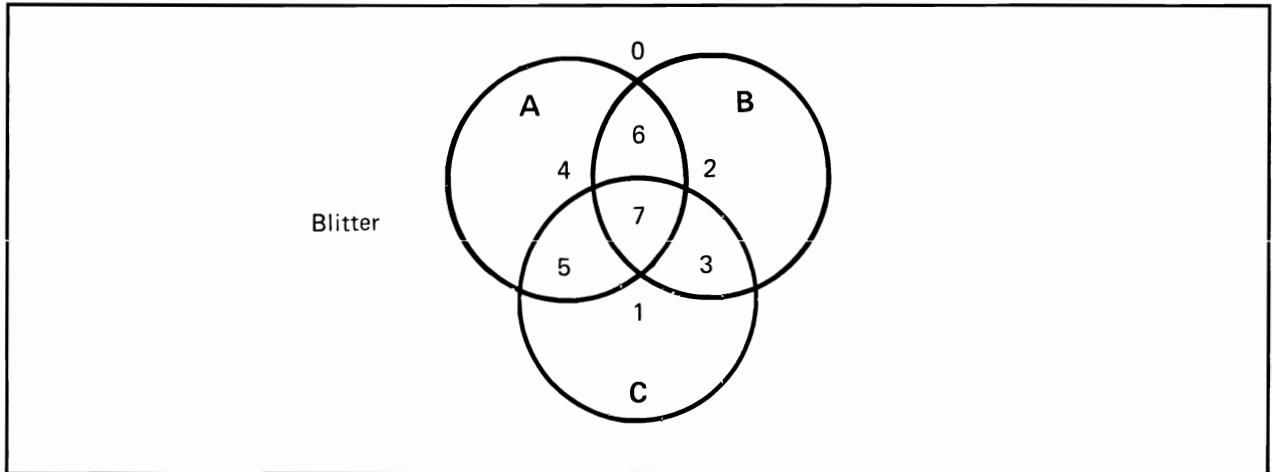

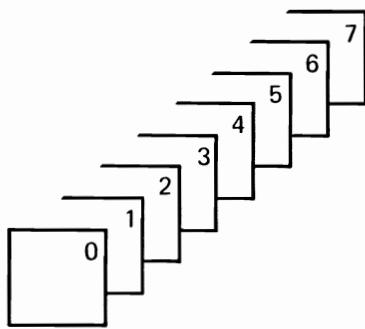

| 6.12. VENN DIAGRAMS .....                                  | 6-16       |

| <b>Chapter 7 SYSTEM CONTROL HARDWARE .....</b>             | <b>7-1</b> |

| 7.1. INTRODUCTION .....                                    | 7-1        |

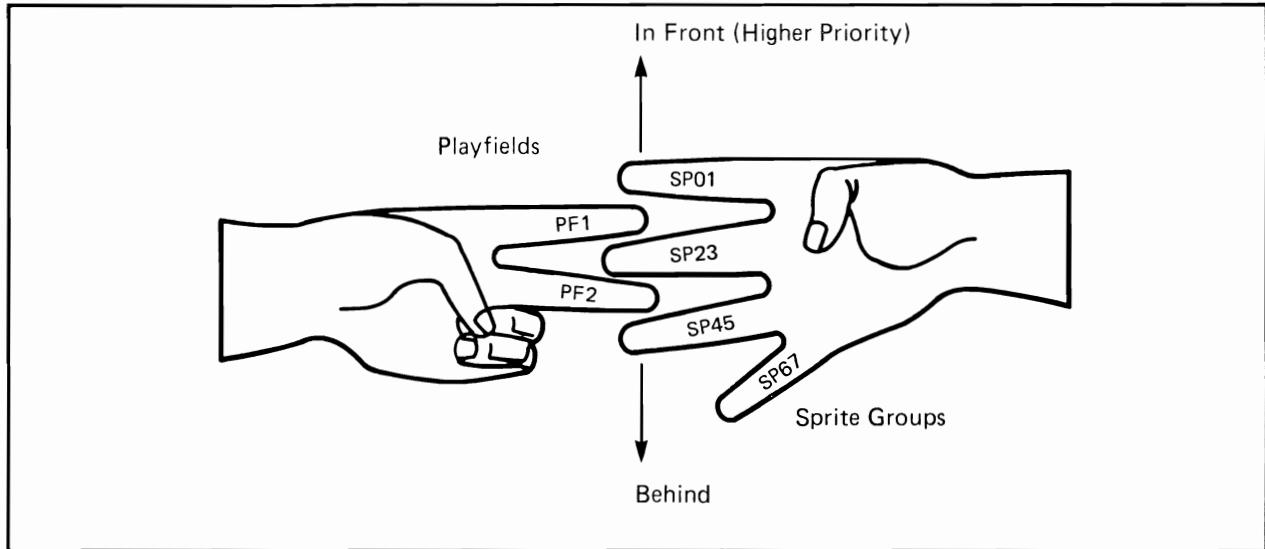

| 7.2. VIDEO PRIORITIES .....                                | 7-1        |

| 7.2.1. Fixed Sprite Priorities .....                       | 7-1        |

| 7.2.2. How Sprites Are Grouped .....                       | 7-2        |

| 7.2.3. Understanding Video Priorities .....                | 7-2        |

| 7.2.4. Setting the Priority Control Register .....         | 7-4        |

| 7.3. COLLISION DETECTION .....                             | 7-6        |

| 7.3.1. How Collisions Are Determined .....                 | 7-6        |

| 7.3.2. How to Interpret the Collision Data .....           | 7-6        |

| 7.3.3. How Collision Detection is Controlled .....         | 7-7        |

| 7.4. BEAM POSITION DETECTION .....                         | 7-9        |

| 7.4.1. Using the Beam Position Counter .....               | 7-9        |

| 7.5. INTERRUPTS .....                                      | 7-10       |

| 7.5.1. Non-Maskable Interrupt .....                        | 7-10       |

| 7.5.2. Maskable Interrupts .....                           | 7-10       |

| 7.5.3. User Interface to the Interrupt System .....        | 7-10       |

| 7.5.4. Interrupt Control Registers .....                   | 7-10       |

| 7.5.5. Setting and Clearing Bits .....                     | 7-11       |

| 7.6. DMA CONTROL .....                                     | 7-15       |

| <b>Chapter 8 INTERFACE HARDWARE .....</b>                  | <b>8-1</b> |

| 8.1. INTRODUCTION .....                                    | 8-1        |

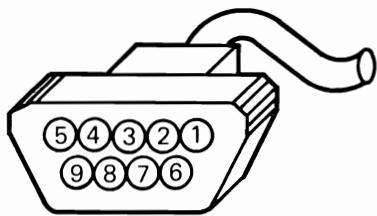

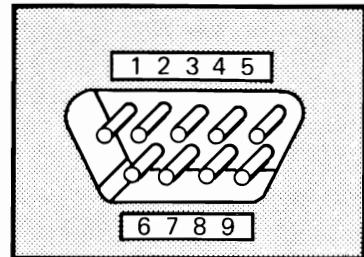

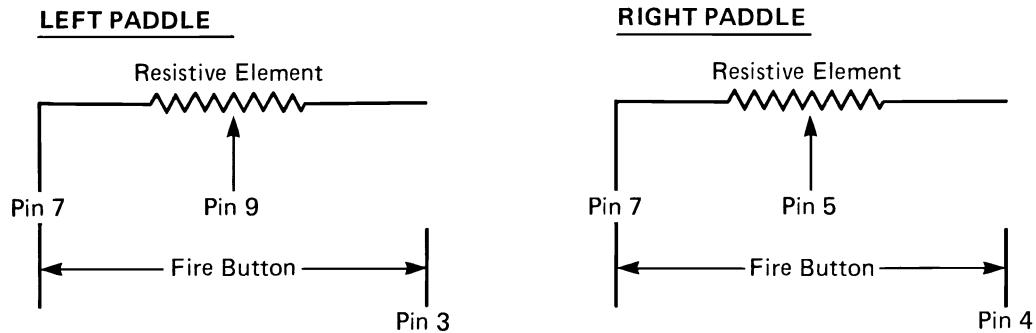

| 8.2. CONTROLLER PORT INTERFACE .....                       | 8-1        |

| 8.2.1. How to Read The Controller Port .....               | 8-2        |

| 8.3. DISK CONTROLLER .....                                 | 8-13       |

| 8.3.1. Disk Selection, Control and Sensing .....           | 8-13       |

| 8.3.2. Other Registers Involved with Disk Operations ..... | 8-16       |

| 8.3.3. Disk Interrupts .....                               | 8-19       |

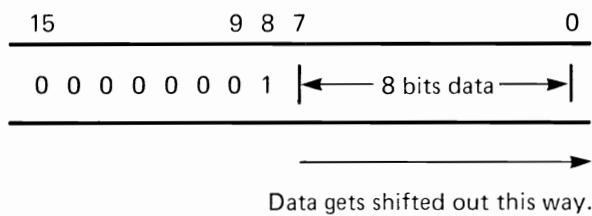

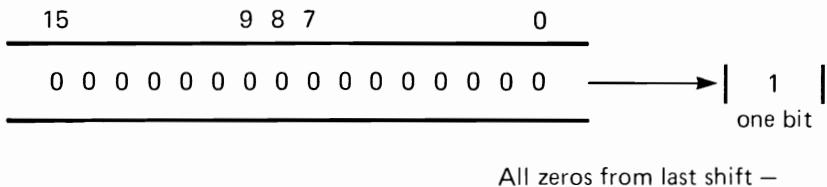

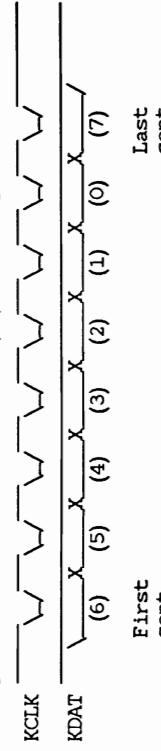

| 8.4. THE KEYBOARD .....                                    | 8-19       |

| 8.4.1. How the Keyboard Data is Received .....             | 8-20       |

| 8.4.2. Type of Data Received .....                         | 8-20       |

| 8.4.3. Limitations of the Keyboard .....                   | 8-23       |

| 8.5. PARALLEL INPUT/OUTPUT INTERFACE .....                 | 8-25       |

| 8.6. SERIAL INTERFACE .....                                | 8-25       |

| 8.6.1. Introduction to Serial Circuitry .....              | 8-25       |

| 8.6.2. Setting the Baud Rate .....                         | 8-25       |

| 8.6.3. Setting the Receive Mode .....                      | 8-25       |

| 8.6.4. Contents of the Receive Data Register .....         | 8-26       |

|                                                                    |                   |

|--------------------------------------------------------------------|-------------------|

| 8.6.5. How Output Data is Transmitted .....                        | 8-27              |

| 8.6.6. How to Specify the Register Contents .....                  | 8-29              |

| 8.7. AUDIO OUTPUT CONNECTIONS .....                                | 8-29              |

| 8.8. DISPLAY OUTPUT CONNECTIONS .....                              | 8-30              |

| <b>Appendix A REGISTER SET SUMMARY -- ALPHABETICAL ORDER .....</b> | <b>A-1</b>        |

| <b>Appendix B REGISTER SET SUMMARY -- ADDRESS ORDER .....</b>      | <b>B-1</b>        |

| <b>Appendix C PIN ALLOCATION LIST .....</b>                        | <b>C-1</b>        |

| <b>Appendix D SYSTEM MEMORY MAP .....</b>                          | <b>D-1</b>        |

| <b>Appendix E INTERFACES .....</b>                                 | <b>E-1</b>        |

| <b>Appendix F PERIPHERAL INTERFACE ADAPTERS .....</b>              | <b>F-1</b>        |

| <b>Appendix G EXPANSION CONNECTOR .....</b>                        | <b>G-1</b>        |

| <b>Appendix H KEYBOARD .....</b>                                   | <b>H-1</b>        |

| <b>GLOSSARY .....</b>                                              | <b>Glossary-1</b> |

# Chapter 1

## INTRODUCTION

The Amiga is a low-cost, high-performance computer with advanced graphics and sound features. This chapter lists and describes the Amiga's hardware components and gives a brief overview of its graphics and sound features.

### 1.1. COMPONENTS OF THE AMIGA

These are the hardware components of the Amiga:

- o Motorola MC 68000 16/32-bit main processor

- o 256K bytes of internal RAM, expandable to 512K

- o 256K bytes of ROM containing a real-time, multi-tasking operating system with sound, graphics, and animation support routines

- o built-in 3 1/2-inch double-sided disk drive

- o expansion disk port for connecting up to 3 additional disk drives, which may be either 3-1/2 inch or 5-1/4 inch, double-sided

- o fully programmable serial port

- o fully programmable parallel port

- o two-button opto-mechanical mouse

- o two reconfigureable controller ports (for mice, joysticks, paddles, or custom controllers)

- o detached 89-key keyboard with calculator pad, function keys, and cursor keys

- o ports for simultaneous composite video, and analog or digital RGB output

- o ports for audio output to left and right stereo channels from 4 special-purpose audio channels

- o expansion connector that allows you to add RAM, additional disk drives (floppy or hard disks), peripherals, or coprocessors

## The MC 68000 and the Special-Purpose Hardware

The Motorola 68000 is a 16/32-bit microprocessor operating at 7.16 megahertz. In the Amiga, the 68000 can address over 8 megabytes of contiguous random access memory (RAM).

Performance of the 68000 is enhanced by a system design that gives it every alternate bus cycle, allowing it to run at full rated speed most of the time. As described in the section below, the special purpose hardware can steal time from the 68000 for jobs it can do more efficiently than the 68000. Even then, such cycle stealing only blocks the 68000's access to the shared memory. When using ROM or external memory, the 68000 always runs at full speed.

Among other functions, the special-purpose hardware provides the following:

- o bit-plane generated high-resolution graphics typically producing 320 by 200 non-interlaced displays and 320 by 400 interlaced displays in 32 colors, and 640 by 200 non-interlaced or 640 by 400 interlaced displays in 16 colors. There is also a special mode that allows you to have up to 4096 colors on-screen simultaneously.

- o a custom display coprocessor, allowing changes to most of the special-purpose registers in synchronization with the position of the video beam. This allows such special effects as mid-screen changes to the color palette, splitting the screen into multiple horizontal slices each having different video resolutions and color depths, beam-synchronized interrupt generation for the 68000, and more. The coprocessor can trigger many times per screen. It can trigger in the middle of lines, as well as at the beginning or during the blanking interval. The coprocessor itself can directly affect most of the registers of the special-purpose hardware, freeing the 68000 for general purpose computing tasks.

- o 32 system color registers, each of which contains a 12-bit number as 4 bits of RED, 4 bits of GREEN, and 4 bits of BLUE intensity information. This allows a system color palette of 4096 different choices of color for each register. Although an RGB monitor provides the best available output for the system graphics, test, and color, the composite video signal has been carefully designed to provide maximum NTSC compatibility. This signal may be video-taped or fed to a standard composite video monitor.

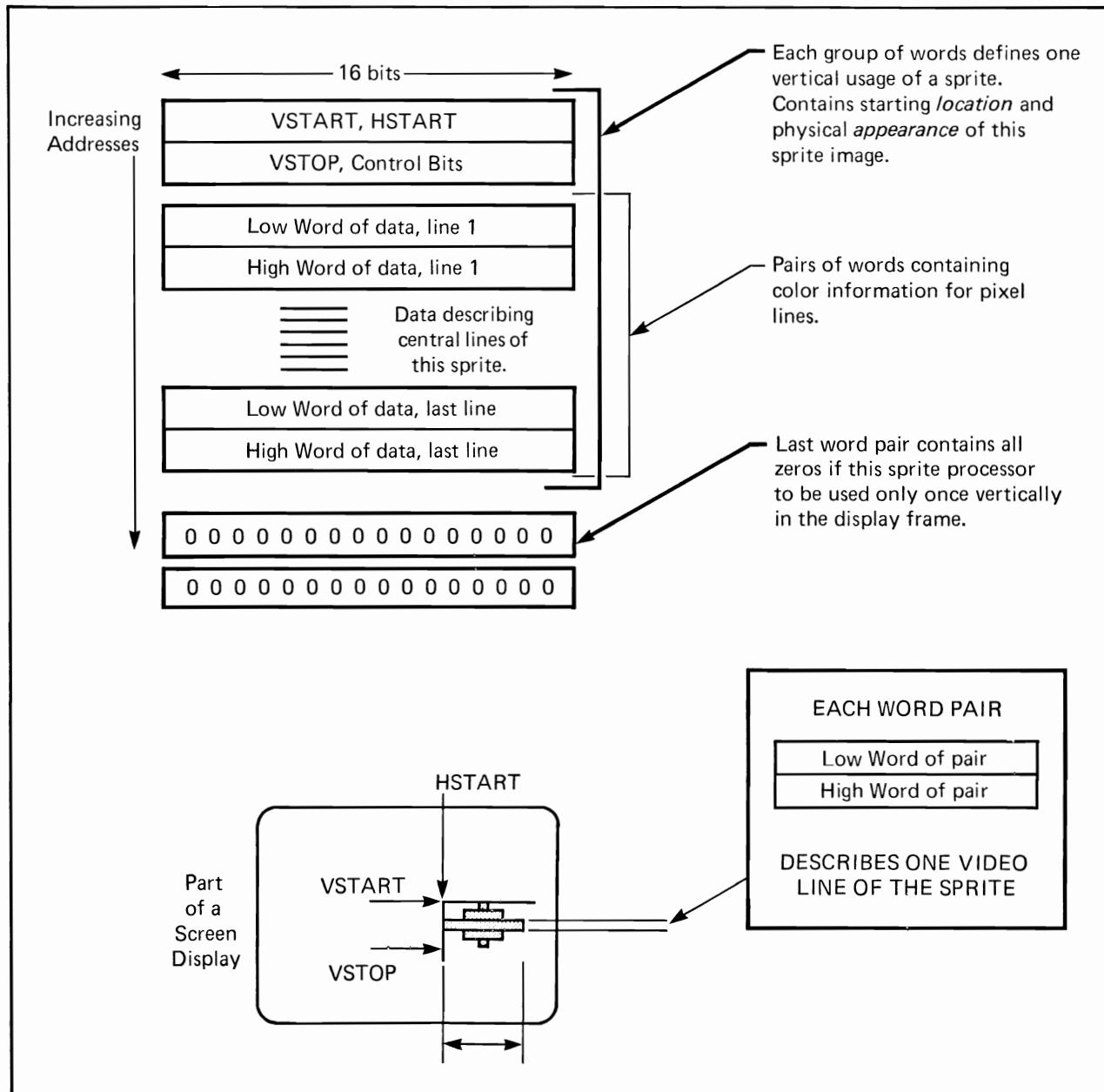

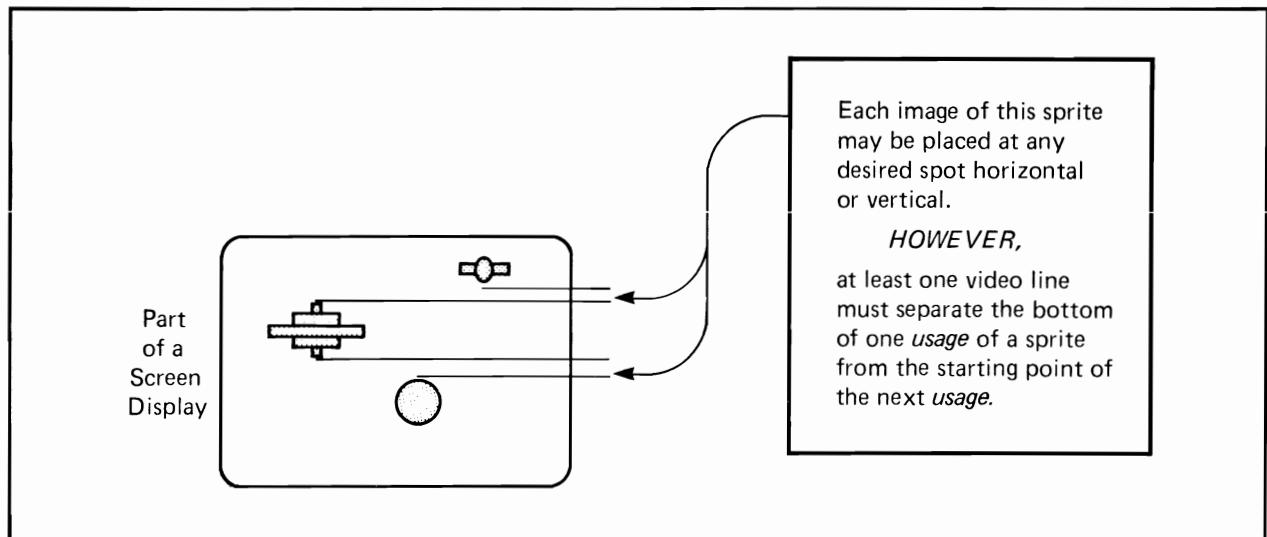

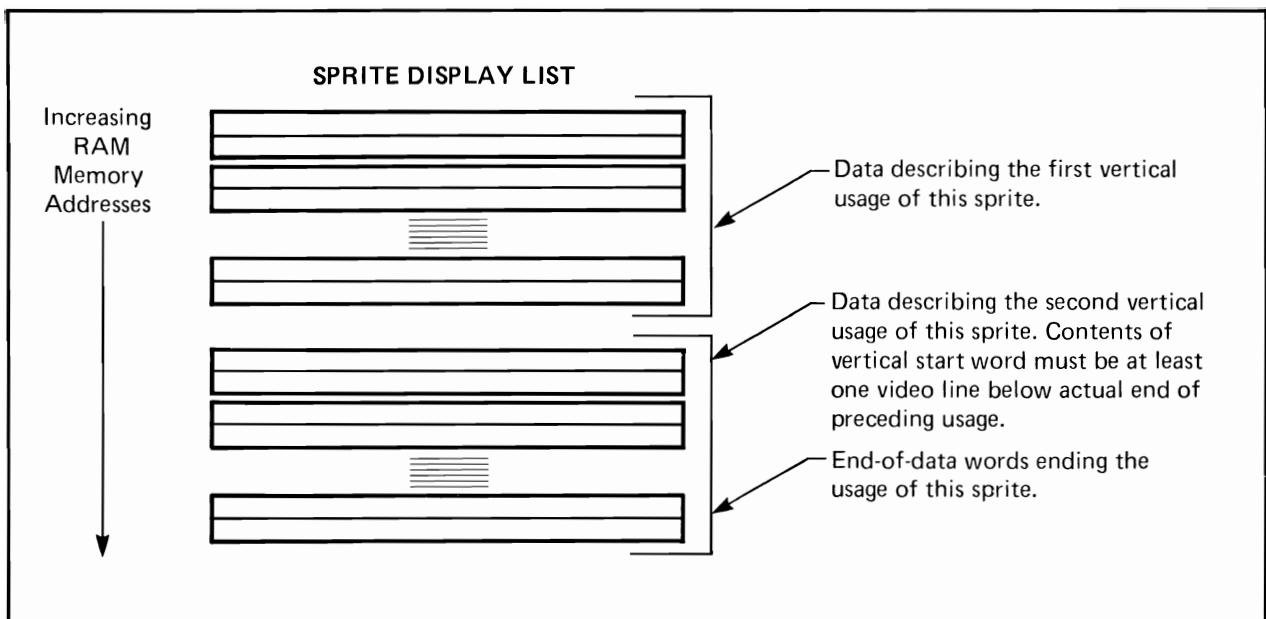

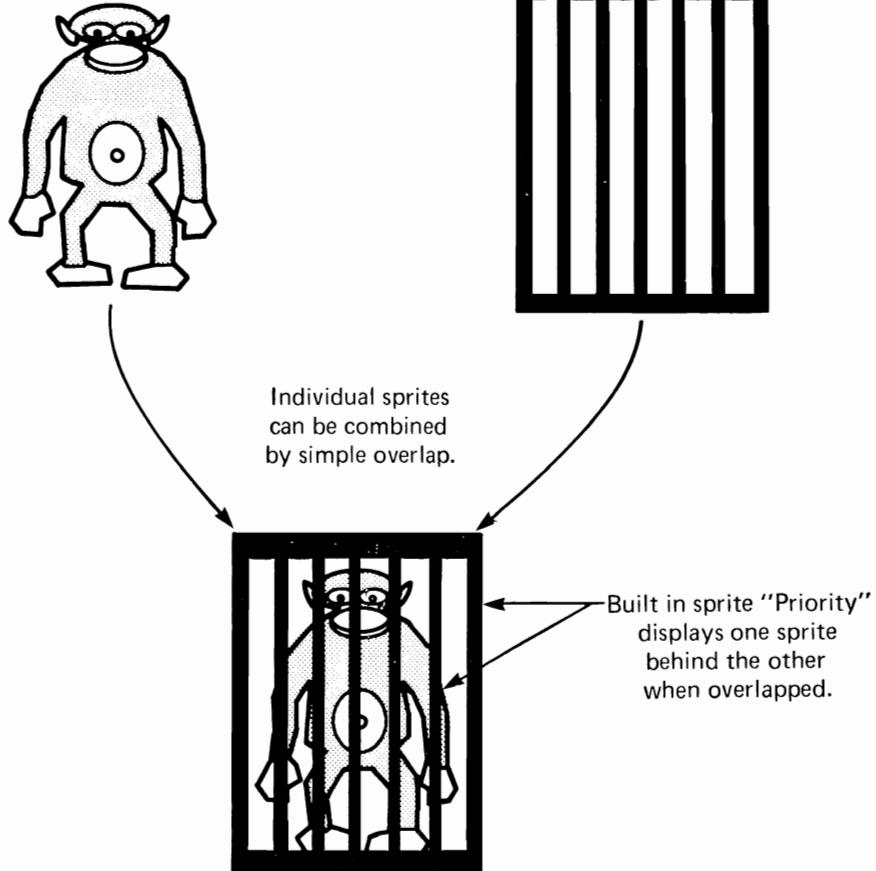

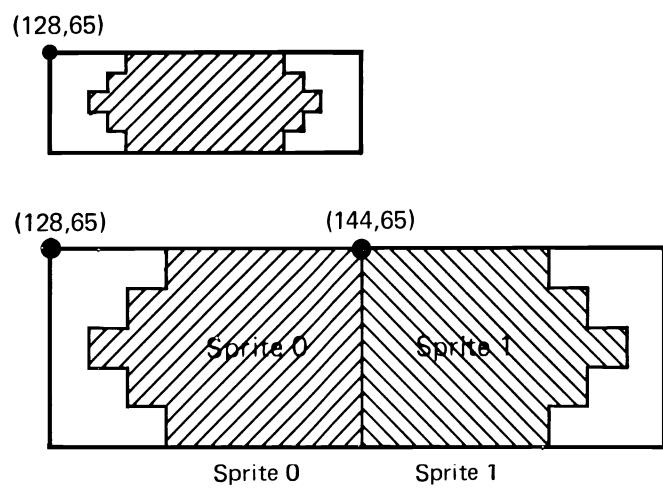

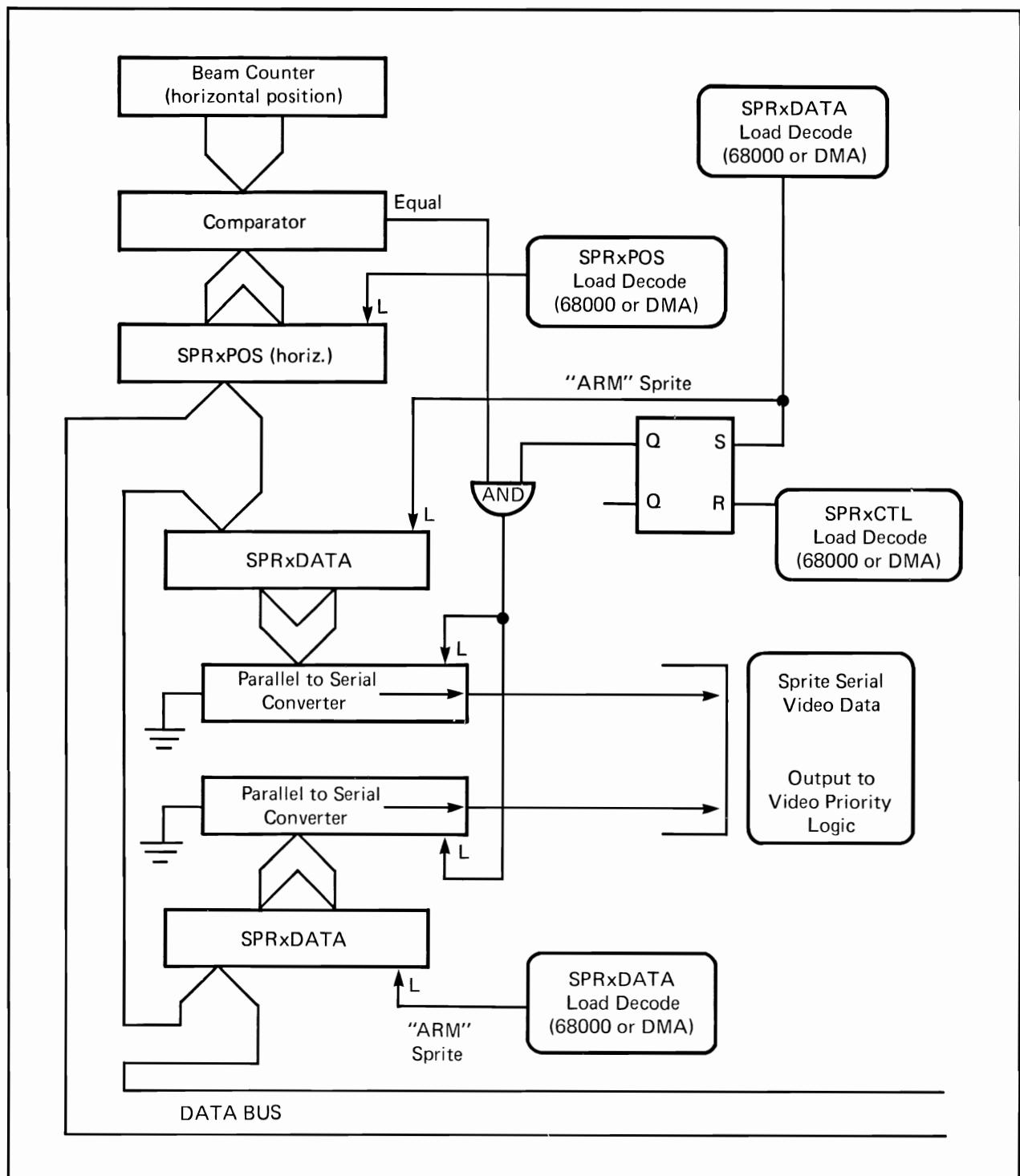

- o 8 reusable 16-bit-wide sprites with up to 15 color choices per sprite pixel (when sprites are paired). A sprite is an easily movable graphics object whose display is entirely independent of the background (called a playfield); sprites can be displayed "over" or "under" this background. A sprite is 16 low-resolution pixels wide and an arbitrary number of lines tall. After producing the last line of a sprite on the screen, a sprite DMA (direct memory access) channel may be used to produce yet another sprite image elsewhere on-screen (with at least one horizontal line between each reuse of a sprite processor). Thus, you can produce many, many small sprites by simply reusing the sprite processors appropriately.

- o dynamically-controllable inter-object priority, with collision detection. This means that the system can dynamically control the video priority between the sprite objects and the bit-plane backgrounds (playfields). You can control which object or objects appear “on top” at any time.

Additionally, you can use system hardware to detect collisions between objects and have your program react to such collisions.

- o custom bit-blitter used for high speed data movement, adaptable to bit-plane animation. The blitter has been designed to efficiently retrieve data from up to 3 sources, combine the data in one of 256 different possible ways, and optionally store the combined data in a destination area. This is one of the situations where the 68000 gives up memory cycles to a DMA channel that can do the job more efficiently. The bit-blitter, in a special mode, draws patterned lines into rectangularly organized memory regions at a speed of about 1 million dots per second; and it can efficiently handle area fill.

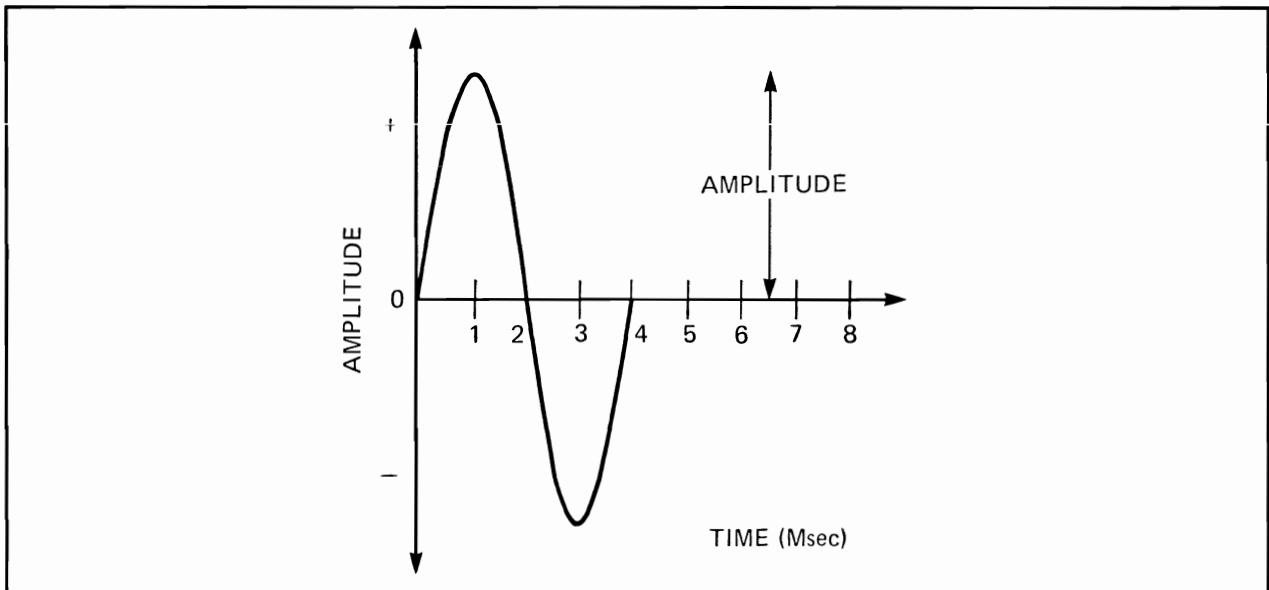

- o audio consisting of 4 low-noise digital channels with independently programmable volume and sampling rate. The audio channels retrieve their control and data via direct memory access. Once started, each channel can automatically play a specified waveform without further processor interaction. Two channels are directed into each of the two stereo audio outputs. The audio channels may be linked together if desired to provide amplitude or frequency modulation or both forms of modulation simultaneously.

- o DMA-controlled floppy disk read and write on a full-track basis. This means that the built-in disk can read something over 5.6K bytes of data in a single disk revolution (11 sectors of 512 bytes each).

All of the special functions described above are produced by three custom-designed VLSI circuits, which work in concert with the 68000. These circuits and the 68000 use the shared memory on a fully interleaved basis. Since the 68000 only needs to access the memory bus during each alternate clock cycle in order to run full-speed, the rest of the time the memory bus is free for other activities.

The special purpose hardware uses the memory bus during these free cycles, effectively allowing the 68000 to run at full rated speed “most of the time”. We say “most of the time” because there are some occasions when the special purpose hardware steals memory cycles from the 68000, but with good reason. Specifically, the coprocessor and the data-moving DMA channel called the blitter can each steal time from the 68000 for jobs they can do better than the 68000. Thus, the system DMA channels are designed with maximum performance in mind, where the job to be done is performed by the most efficient hardware element available. In addition, sprites, audio, and disk DMA also steal cycles when in operation.

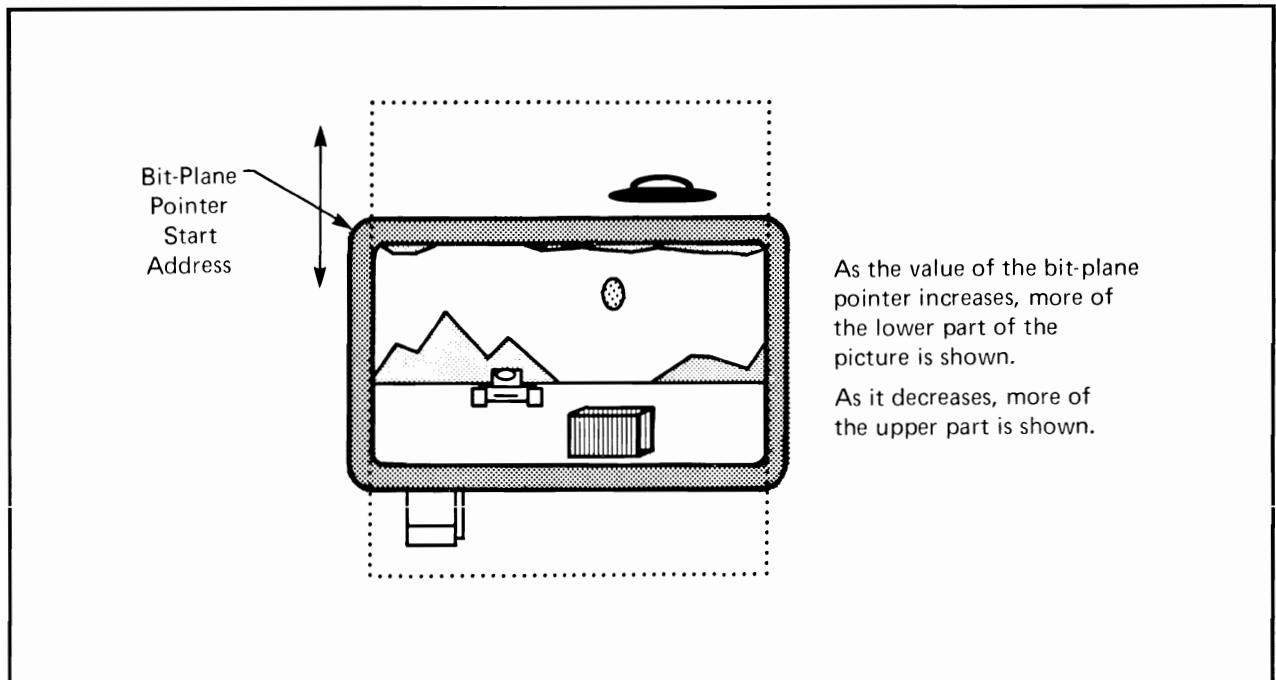

Another primary feature of the Amiga hardware is the ability to dynamically control which part of memory is used for the background display, audio, and sprites. The Amiga is not limited to a small, specific area of RAM for a frame buffer. Instead, the system allows display bit-planes, sprite-processor control lists, coprocessor instruction lists, or audio channel control lists to be located anywhere within the lowest 512K of the memory map.

This same region of memory can be accessed by the bit-blitter. This means, for example, that the user can store partial images at scattered areas of memory and use these images for animation effects by means of rapid replacement of on-screen material while saving and

restoring background images. In fact, the Amiga includes firmware support for display definition and control as well as support for animated objects embedded within playfields.

## **VCR and Direct Camera Interface**

In addition to the connections for NTSC composite Amiga video, and both digital and analog RGB monitors, the system can be expanded to include a VCR or camera interface. This system is capable of synchronizing with an external video source and replacing the system background color with the external image. This allows for the development of fully integrated video images with computer-generated graphics. Laser disk input is accepted in the same manner.

## **Primary and Secondary Memory**

Primary memory in the Amiga consists of 256K bytes of ROM and 256K bytes of RAM. A RAM expansion cartridge is available as an option. Secondary memory is provided by a built-in 3 1/2-inch floppy disk drive. Disks are 80-track, double-sided, formatted as 11 sectors per track, 512 bytes per sector (over 900,000 bytes per disk). A special utility can read and write disk files compatible with the Apple II[tm]. In addition, the disk controller can read and write 320/360K IBM PC[tm] formatted disks. External 3 1/2-inch or 5 1/4-inch disk drives can be added to the system through the expansion connector.

## **Peripherals**

Circuitry for some of the peripherals resides on one of the custom chips; other chips handle various signals not specifically assigned to any of the custom chips, including modem controls, disk status sensing, disk motor and stepping controls, ROM enable, parallel input/output interface, and keyboard interface.

The Amiga includes a standard RS-232 serial port for external serial input/output devices.

A detached, professional quality keyboard is included in the base system. You can store the keyboard beneath the system cabinet. For maximum flexibility, both key-down and key-up signals are sent.

For those who prefer incremental cursor control, there are cursor keys on the keyboard. You can attach many other types of controllers through the two controller ports on the side of

the base unit. You can use a mouse, joystick, keypad, trackball, or steering wheel controller in either of the controller ports. (A light pen can be attached to Port 0.)

## **1.2. SYSTEM EXPANDABILITY AND ADAPTABILITY**

You can add peripheral devices to the Amiga's expansion connector, and add additional external RAM on the same expansion connector or upgrade internal RAM to 512K. Additional disk units may be daisy-chained from a connector at the rear of the unit for a total of 3 extra drives.

The system software, as well, is highly adaptable to other host operating systems. The Amiga's graphics support routines are designed to make the user interface as friendly as possible. New peripheral devices are recognized and used by system software through a well defined, well documented linking procedure.

## Chapter 2

# COPROCESSOR HARDWARE

### 2.1. INTRODUCTION

The Copper is a general purpose coprocessor which resides in one of the Amiga's custom chips. It retrieves its instructions via direct memory access (DMA). The Copper can control nearly the entire graphics system, freeing the 68000 to execute program logic; and it can directly affect the contents of most of the chip control registers. It is a very powerful tool for directing mid-screen modifications in graphics displays and for directing the register changes that must occur during the vertical blanking periods. Among other things, it can control register updates, reposition sprites, change the color palette, update the audio channels, and control the blitter.

One of the features of the Copper is its ability to WAIT for a specific video beam position, then MOVE data into a system register. During the WAIT period, the Copper examines the contents of the video beam position counter directly. This means that while the Copper is waiting for the beam to reach a specific position, it does not use the memory bus at all. Therefore, the bus is freed for use by the other DMA channels or by the 68000.

When the WAIT condition has been satisfied, the Copper steals memory cycles from either the blitter or the 68000 to move the specified data into the selected special-purpose register.

The Copper is a 2-cycle processor that requests the bus only during odd-numbered memory cycles. This prevents collision with audio, disk, refresh, sprites, and most low-resolution display DMA access, all of which use only the even-numbered memory cycles. The Copper, therefore, only needs priority over the 68000 and the blitter (DMA channel that handles animation, line drawing, and polygon filling).

As with all the other DMA channels in the Amiga system, the Copper can only retrieve its instructions from the lowest 512K of system memory.

### About This Chapter

In this chapter, you will learn how to use the special Copper instruction set to organize mid-screen register value modifications and pointer register setup during the vertical blanking interval. The chapter shows how to organize Copper instructions into Copper lists, how to use Copper lists in interlace mode, and how to use the Copper with the blitter. The Copper is discussed in this chapter in a general fashion. The chapters that deal with playfields,

sprites, audio, and the blitter contain more specific suggestions for using the Copper.

## 2.2. WHAT IS A COPPER INSTRUCTION?

As a coprocessor, the Copper adds its own instruction set to the instructions already provided by the 68000. The Copper has only three instructions, but you can do a lot with them:

- o WAIT for a specific screen position specified as x and y coordinates.

- o MOVE an intermediate value into one of the special purpose registers.

- o SKIP the next instruction if the video beam has already reached a specified screen position.

All Copper instructions consist of two 16-bit words in sequential memory locations. Each time the Copper fetches an instruction, it fetches both words. The MOVE and SKIP instructions require 2 memory cycles and 2 instruction words. Since only the odd memory cycles are requested by the Copper, 4 memory cycle times are required per instruction. The WAIT instruction requires 3 memory cycles and 6 memory cycle times; it takes one extra memory cycle to wake up.

Although the copper can directly affect only machine registers, it can affect the memory by setting up a blitter operation. More information about how to use the Copper in controlling the blitter can be found in the sections called “Control Register” and “Using the Copper with the Blitter”.

The WAIT and MOVE instructions are described below. The SKIP instruction is described in the “Advanced Topics” section.

## 2.3. THE MOVE INSTRUCTION

The MOVE instruction transfers data from RAM to a register destination. The transferred data is contained in the second word of the MOVE instruction; the first word contains the address of the destination register. This is shown in detail in the section called “Summary of Copper Instructions”.

### FIRST INSTRUCTION WORD (IR1)

|             |                                       |

|-------------|---------------------------------------|

| Bit 0       | Always set to 0.                      |

| Bits 8 - 1  | Register destination address (DA8-1). |

| Bits 15 - 9 | Not used, but should be set to 0.     |

### SECOND INSTRUCTION WORD (IR2)

|             |                                                                        |

|-------------|------------------------------------------------------------------------|

| Bits 15 - 0 | 16 bits of data to be transferred (moved) to the register destination. |

|-------------|------------------------------------------------------------------------|

The Copper can store data into the following registers:

- o Any register whose address is hex 20 or above.

- o Any register whose address is between hex 10 and hex 20 if the Copper danger bit is a 1. The Copper danger bit is in the Copper’s control register, COPCON, which is described in the “Control Register” section.

- o The Copper cannot write into any register whose address is lower than hex 10.

Appendix B at the end of this manual contains all the machine register addresses.

## 2.4. THE WAIT INSTRUCTION

The WAIT instruction causes the Copper to wait until the video beam counters are equal to (or greater than) the coordinates specified in the instruction. While waiting, the Copper is off the bus and not using memory cycles.

The first instruction word contains the vertical and horizontal coordinates of the beam position. The second word contains enable bits that are used to form a “mask” that tells the system which bits of the beam position to use in making the comparison.

### FIRST INSTRUCTION WORD (IR1)

|             |                                       |

|-------------|---------------------------------------|

| Bit 0       | Always set to 1.                      |

| Bits 15 - 8 | Vertical beam position (called VP).   |

| Bits 7 - 1  | Horizontal beam position (called HP). |

### SECOND INSTRUCTION WORD (IR2)

|             |                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------|

| Bit 0       | Always set to 0.                                                                                              |

| Bit 15      | The Blitter Finished Disable bit.<br>Normally, this bit is a 1.<br>(See the “Advanced Topics” section below.) |

| Bits 14 - 8 | Vertical position compare enable bits (called VE).                                                            |

| Bits 7 - 1  | Horizontal position compare enable bits (called HE).                                                          |

The following notes apply to both the WAIT instruction and to the SKIP instruction, which is described below in the “Advanced Topics” section.

### Horizontal Beam Position

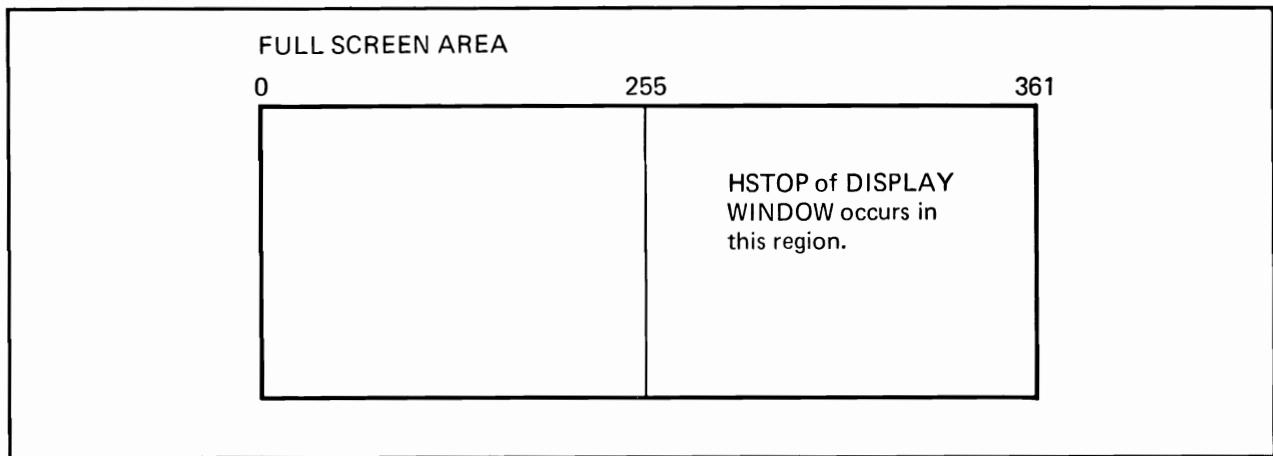

The horizontal beam position has a value of \$0 to \$E2 (hex).<sup>1</sup> The least significant bit is not used in the comparison, so there are 113 positions available for Copper operations. This corresponds to 4 pixels in low resolution and 8 pixels in high resolution. Horizontal blanking falls in the range of \$0F to \$35. The standard screen (320 pixels wide) has an unused horizontal portion of \$04 to \$47 (during which only the background color is displayed).

---

<sup>1</sup> In this manual hexadecimal numbers are distinguished from decimal numbers by the \$ prefix.

## Vertical Beam Position

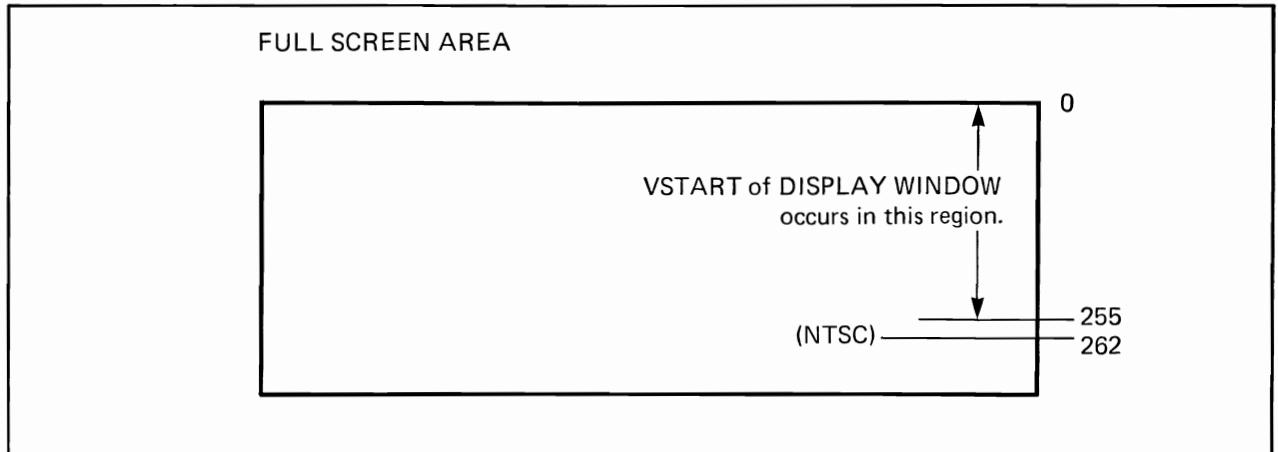

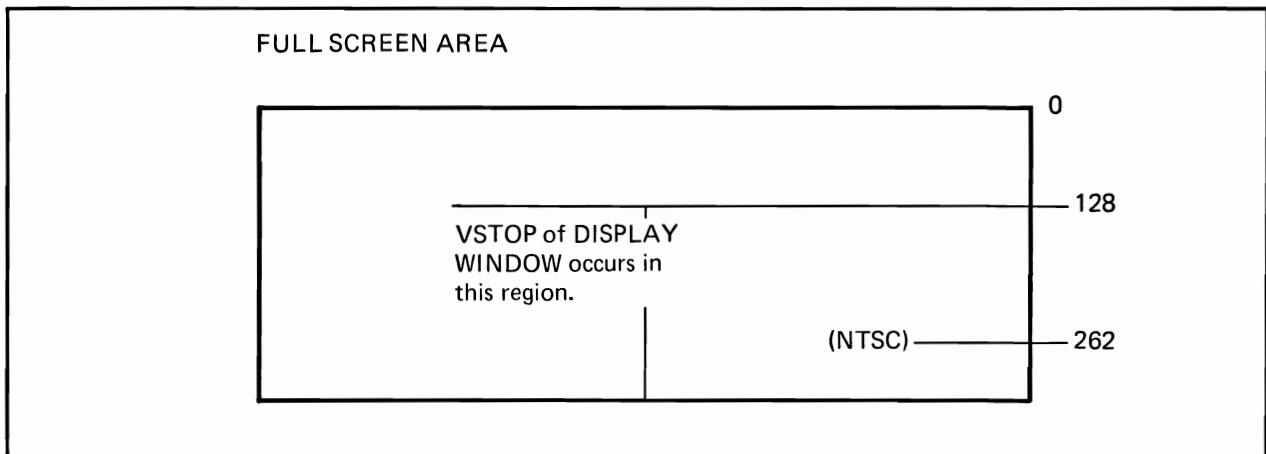

The vertical beam position can be resolved to 1 line, with a maximum value of 255. There are actually 262 possible vertical positions. Some minor complications can occur if you want something to happen within these last 6 or 7 scan lines. Since there are only 8 bits of resolution for vertical beam position (allowing 256 different positions), one of the simplest ways to handle this is shown in the Copper sequence below.

| INSTRUCTION                                                                                                                                 | EXPLANATION                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| [ ... other instructions ... ]                                                                                                              |                                                                                                                                                  |

| WAIT for position (0,255)                                                                                                                   | <i>At this point, the vertical counter appears to wrap to 0, since the comparison works on the least significant bits of the vertical count.</i> |

| WAIT for any horizontal position with vertical position 0 through 6, covering the last 6 lines of the scan before vertical blanking occurs. | <i>Thus the total of <math>256 + 6 = 262</math> lines of video beam travel during which Copper instructions can be executed.</i>                 |

## The Comparison Enable Bits

Bits 14-1 are normally set to all 1's. The use of the comparison enable bits is described later in the "Advanced Topics" section.

## 2.5. USING THE COPPER REGISTERS

There are several machine registers and strobe addresses dedicated to the Copper:

- o Location registers

- o Jump address strobes

- o Control register

### 2.5.1 Location Registers

The Copper has two sets of location registers, which are:

|         |                                           |

|---------|-------------------------------------------|

| COP1LCH | High 3 bits of first Copper list address  |

| COP1LCL | Low 16 bits of first Copper list address  |

| COP2LCH | High 3 bits of second Copper list address |

| COP2LCL | Low 16 bits of second Copper list address |

In accessing the hardware directly, you often have to write to a pair of registers that contain the address of some data. The register with the lower address always has a name ending in "H" and contains the most significant data, or high 3 bits of the address. The register with the higher address has a name ending in "L" and contains the least significant data, or low 15 bits of the address. Therefore, you write the 18-bit address by moving one long word to the register whose name ends in "H". This is because when you write long words with the 68000, the most significant word goes in the lower addressed word.

In the case of the copper location registers, you write the address to COP1LCH. In the following text, for simplicity, both addresses are referred to as COP1LC or COP2LC.

The copper location registers contain the two indirect jump addresses used by the Copper. The Copper fetches its instructions by using its program counter and increments the program counter after each fetch. When a jump address strobe is written, the corresponding location register is loaded into the Copper program counter. This causes the Copper to jump to a new location from which its next instruction will be fetched. Instruction fetch continues sequentially until the Copper is interrupted by another jump address strobe.

#### NOTE

At the start of each vertical blanking interval, COP1LC is automatically used to start the program counter. That is, no matter what the Copper is doing, when vertical blanking reset occurs, the Copper is automatically freed to restart its operations at the address contained in COP1LC.

## 2.5.2. Jump Strobe Address

When you write to a strobe address, the Copper reloads its program counter from the corresponding location register. The Copper can write its own location registers to perform programmed jumps. For instance, you might MOVE an indirect address into the COP2LC location register. Then, any MOVE instruction that addresses COPJMP2, loads this indirect address into into the program counter.

There are two jump strobe addresses:

|         |                                                 |

|---------|-------------------------------------------------|

| COPJMP1 | Restart Copper from address contained in COP1LC |

| COPJMP2 | Restart Copper from address contained in COP2LC |

## 2.5.3. Control Register

The Copper can access:

- A. Some special-purpose registers all of the time,

- B. Some registers only when a special control bit is set to a 1,

- C. Some registers not at all.

The registers that the Copper can always affect are numbered from \$20 through \$FF inclusive. Those it cannot affect at all are numbered from \$00 to \$0F inclusive. (See Appendix B at the end of this manual for a list of registers in address order.) The Copper control register is within this third, always protected, group. This means that it takes deliberate action on the part of the 68000 to allow the Copper to write into a specific range of the special-purpose registers.

The Copper control register, called COPCON, contains only one bit, Bit #1. This bit, called CDANG (for Copper Danger Bit) protects all registers numbered between \$10 and \$1F inclusive. This includes the blitter control registers. When CDANG is a 0, these registers cannot be written by the Copper. When CDANG is a 1, these registers can be written by the Copper. Preventing the Copper from accessing the blitter control registers prevents a “runaway” Copper (caused by a poorly formed instruction list), from accidentally affecting system memory.

### NOTE

The CDANG bit is cleared after a reset.

## 2.6. PUTTING TOGETHER A COPPER INSTRUCTION LIST

The Copper instruction list contains all the register resetting done during the vertical blanking interval and the register modifications necessary for making mid-screen alterations. As you are planning what will happen during each display field, you may find it easier to think of each aspect of the display as a separate subsystem, such as playfields, sprites, audio, interrupts, and so on. Then you can build a separate list of things that must be done for each subsystem individually at each video beam position.

When you have created all these intermediate lists of things to be done, you must merge them together into a single instruction list to be executed by the Copper once for each display frame. The alternative is to create this all-inclusive list directly, without the intermediate steps.

For example, the bit-plane pointers used in playfield displays and the sprite pointers must be rewritten during the vertical blanking interval so the data will be properly retrieved when the screen display starts again. This can be done with a Copper instruction list that does the following:

```

WAIT until first line of the display

MOVE data to bit-plane pointer 1

MOVE data to bit-plane pointer 2

MOVE data to sprite pointer 1

and so on

```

As a further example, the sprite DMA channels that create movable objects can be reused multiple times during the same display field. You can change the size and shape of the multiple reuses of a sprite; however, every reuse will normally use the same set of colors during a full display frame. You can change sprite colors mid-screen with a Copper instruction list that waits until the last line of the first use of the sprite processor and changes the colors before the first line of the next use of the same sprite processor:

```

WAIT for first line of display

MOVE firstcolor1 to COLOR17

MOVE firstcolor2 to COLOR18

MOVE firstcolor3 to COLOR19

WAIT for last line +1 of sprite's first use

MOVE secondcolor1 to COLOR17

MOVE secondcolor2 to COLOR18

MOVE secondcolor3 to COLOR19

and so on

```

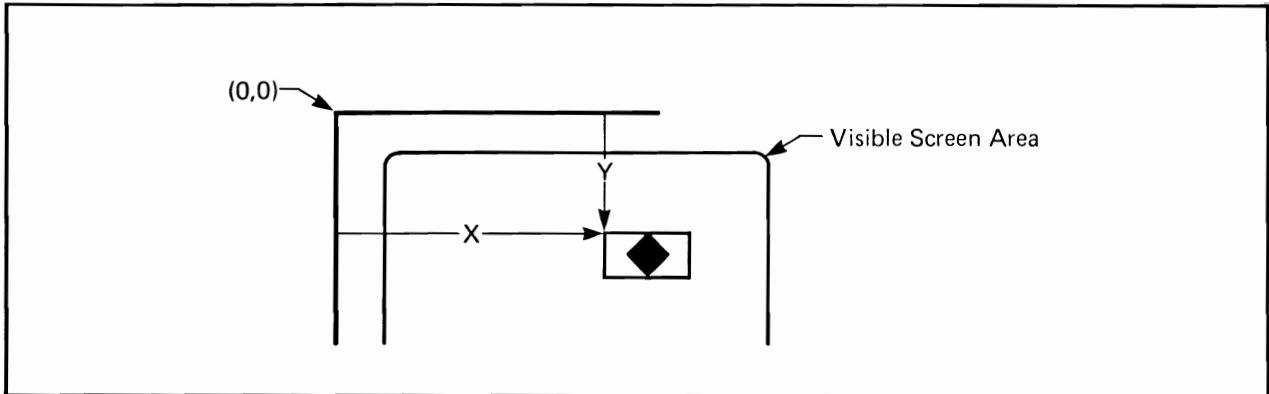

As you create Copper instruction lists, note that the final list must be in the same order as the order in which the video beam creates the display. The video beam traverses the screen from position (0,0) in the upper left hand corner of the screen to the end of the display (226,263) in the lower right hand corner. The first 0 in (0,0) represents the x, position. The second 0 represents the y position. For example, an instruction that does something at

position (0,100) should come after an instruction that affects the display at position (0,60). Note that because of the form of the WAIT instruction, you can sometimes get away with not sorting the list in strict video beam order. The WAIT instruction causes the Copper to wait until the value in the beam counter is equal to or greater than the value in the instruction. This means, for example, if you have instructions following each other like this:

WAIT for position (64,64)

MOVE data

WAIT for position (60,60)

MOVE data

the Copper will perform both moves, even though the instructions are out of sequence. The reason for the “greater than” specification is to prevent the Copper from locking up if the beam has already passed the specified position. A side effect is that the second MOVE below will be performed:

WAIT for position (60,60)

MOVE data

WAIT for position (60,60)

MOVE data

At the time of the second WAIT in this sequence, the beam counters will be greater than the position shown in the instructions. Therefore, the second MOVE will also be performed.

Note also that the above sequence of instructions can just as easily be:

WAIT for position (60,60)

MOVE data

MOVE data

MOVE data

since multiple moves can follow a single WAIT.

## Loops and Branches

Loops and branches in Copper lists are covered in the “Advanced Topics” section below.

## 2.7. STARTING AND STOPPING THE COPPER

### Starting the Copper After Reset

At power-on or reset time, you must initialize one of the copper location registers (COP1LC or COP2LC) and write to its strobe address before Copper DMA is turned on. This ensures a known start address and known state. Usually, COP1LC is used because this particular register is reused each vertical blanking time. The following sequence of 68000 assembly instructions shows how to initialize a location register.

```

move.l mycoplist, a0          ;It is assumed that the

move.l a0, COP1LCH            ;user has already created

move.w COPJMP1, d0            ;correct Copper instruction

;list at location "mycoplist"

move.w #SETBIT + COPPERDMA, d0 ;Write both COP1LCH and COP1LCL

move.w d0, DMACONW           ;Any access to this location forces

;load from COP1LC to Copper

;program counter

;Enable Copper DMA

```

Now, if the contents of COP1LC are not changed, every time vertical blanking occurs the Copper will restart at the same location for each subsequent video screen. This forms a repeatable loop which, if the list is correctly formulated, will cause the displayed screen to be stable.

### Stopping the Copper

There is no stop instruction provided for the Copper. To ensure that it will stop and do nothing until the screen display ends and the program counter starts again at the top of the instruction list, the last instruction should be to WAIT for an event that cannot occur. A typical instruction is to WAIT for VP = \$FF and HP = \$FE. An HP of greater than \$E2 is not possible. When the screen display ends and vertical blanking starts, the Copper will automatically be pointed to the top of its instruction list and this final WAIT instruction never finishes.

You can also stop the Copper by disabling its ability to use DMA for retrieving instructions or placing data. The register called DMACON controls all of the DMA channels. Bit 7,

COPEN, enables Copper DMA when set to 1.

For information about controlling the DMA, see Chapter 7, “System Control Hardware”.

## 2.8. ADVANCED TOPICS

### 2.8.1. The SKIP Instruction

The SKIP instruction causes the Copper to skip the next instruction if the video beam counters are equal to, or greater than, the value given in the instruction.

The contents of the SKIP instruction's words are shown below. They are identical to the WAIT instruction, except that bit 0 of the second instruction word is a 1 to identify this as a SKIP instruction.

#### FIRST INSTRUCTION WORD (IR1)

|             |                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------|

| Bit 0       | Always set to 1.                                                                              |

| Bits 15 - 8 | Vertical position (called VP).                                                                |

| Bits 7 - 1  | Horizontal position (called HP).                                                              |

|             | Skip if the beam counter is equal to or greater than these combined bits (bits 15 through 1). |

#### SECOND INSTRUCTION WORD (IR2)

|             |                                                                                       |

|-------------|---------------------------------------------------------------------------------------|

| Bit 0       | Always set to 1.                                                                      |

| Bit 15      | The Blitter Finished Disable bit.<br>(See "Using the Copper with the Blitter" below.) |

| Bits 14 - 8 | Vertical position compare enable bits (called VE).                                    |

| Bits 7 - 1  | Horizontal position compare enable bits (called HE).                                  |

The notes about horizontal and vertical beam position found in the discussion of the WAIT instruction apply also to the SKIP instruction.

### 2.8.2. Copper Loops and Branches and Comparison Enable

You can change the value in the location registers at any time and use this value to construct loops in the instruction list. Before the next vertical blanking time, however, the COP1LC registers must be repointed to the beginning of the appropriate Copper list. The value in the COP1LC location registers will be restored to the Copper's program counter at the start of the vertical blanking period.

Bits 14-1 of instruction word 2 in the WAIT and SKIP instructions specify which bits of the horizontal and vertical position are to be used for the beam counter comparison. The

position in instruction word 1 and the compare enable bits in instruction word 2 are tested against the actual beam counters before any further action is taken. A position bit in instruction word 1 is used in comparing the positions with the actual beam counters if and only if the corresponding enable bit in instruction word 2 is set to 1. If the corresponding enable bit is 0, the comparison is always true. For instance, if you only care about the value in the last 4 bits of the vertical position, you only set the last 4 compare enable bits, bits (11-8) in instruction word 2.

As another example, suppose you want to issue an interrupt each time a total of 16 vertical scan lines has occurred. In addition, you want the interrupts only between lines 80 and 160. Here is a Copper instruction sequence which would do this. The enable “masks” are specified with the instructions.

Before the Copper is told to begin this set of instructions, you use the 68000 to write the address of LOOP to COP2LC.

The Copper instruction stream for the interrupt example includes instructions to do the following:

|          |          |                                                                |

|----------|----------|----------------------------------------------------------------|

| (Word 1) | WAIT for | Vertical Position (VP) = 80<br>Horizontal Position (HP) = 0.   |

| (Word 2) |          | Mask for vertical = 111111<br>Mask for horizontal = 111111     |

|          |          | <i>All bits of the mask are important;<br/>we want y = 80.</i> |

LOOP:

|          |          |                                                                                       |

|----------|----------|---------------------------------------------------------------------------------------|

| (Word 1) | WAIT for | VP = 0<br>HP = 0                                                                      |

| (Word 2) |          | Mask for VP = 001111<br>Mask for HP = 000000                                          |

|          |          | <i>Only the lowest 4 bits are important;<br/>we want an interrupt every 16 lines.</i> |

|          |         |                                          |

|----------|---------|------------------------------------------|

| (Word 1) | MOVE to | (INTREQ)                                 |

| (Word 2) |         | Interrupt word contents                  |

|          |         | <i>Issue an interrupt to the 68000..</i> |

|          |      |                                                                      |

|----------|------|----------------------------------------------------------------------|

| (Word 1) | SKIP | (next instruction if)<br>VP = 160<br>HP = 0                          |

| (Word 2) |      | Mask for VP = 111111<br>Mask for HP = 000000                         |

|          |      | <i>We want this loop executed only between<br/>lines 80 and 160.</i> |

|          |         |            |

|----------|---------|------------|

| (Word 1) | MOVE to | COPJMP2    |

| (Word 2) |         | (anything) |

*Program counter set to address of loop.*

### 2.8.3. Using the Copper in Interlace Mode

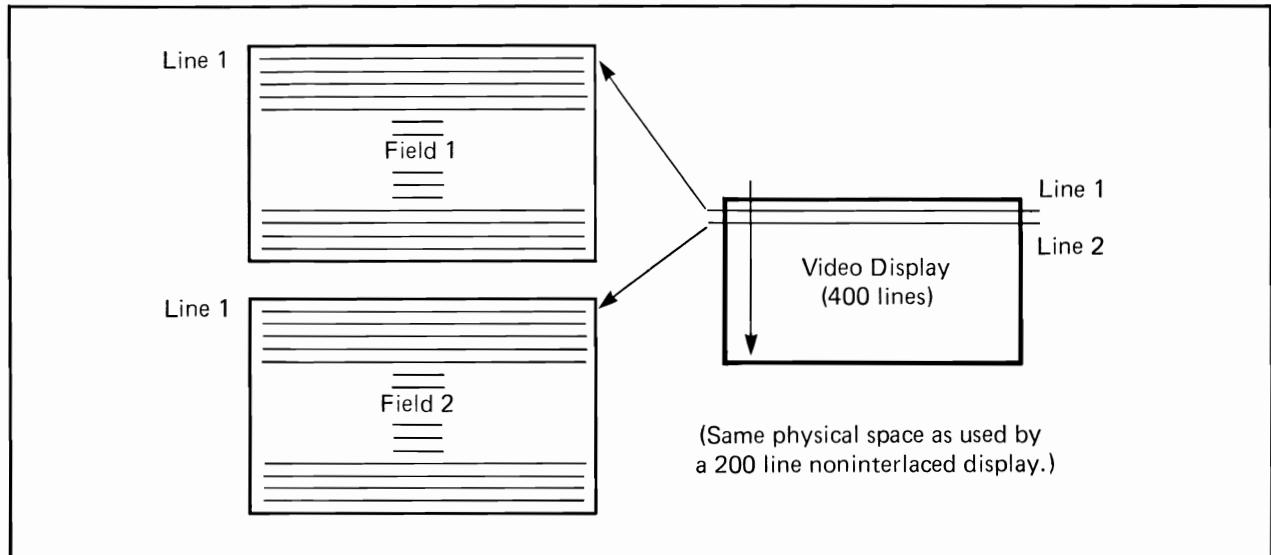

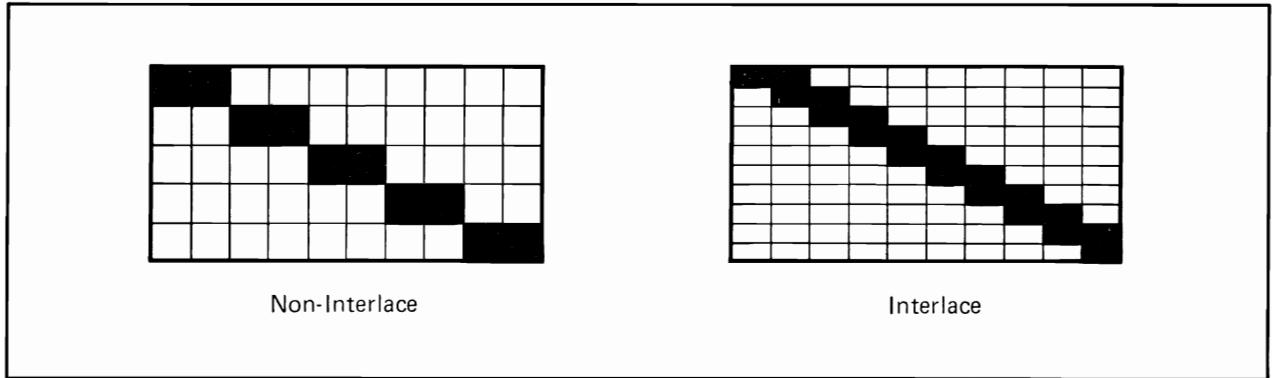

An interlaced bit-plane display has twice the normal number of vertical lines on the screen. Whereas a normal display has 200 lines, an interlaced display has 400 lines. In interlace mode, the video beam scans the screen twice from top to bottom, displaying 200 lines at a time. During the first scan, the odd-numbered lines are displayed. During the second scan, the even-numbered lines are displayed and interlaced with the odd-numbered ones. The scanning circuitry thus treats an interlaced display as two display fields, one containing the even-numbered lines and one containing the odd-numbered lines. The diagram below shows how an interlaced display is stored in memory.

| DATA AS<br>DISPLAYED | DATA<br>IN MEMORY |

|----------------------|-------------------|

| odd field            | line 1            |

| even field           | line 2            |

| odd field            | line 3            |

| even field           | line 4            |

| .                    | .                 |

| .                    | .                 |

| .                    | .                 |

| odd field            | line 399          |

| even field           | line 400          |

Figure 2-1: Interlaced Bit-Plane in RAM - 400 Lines Long

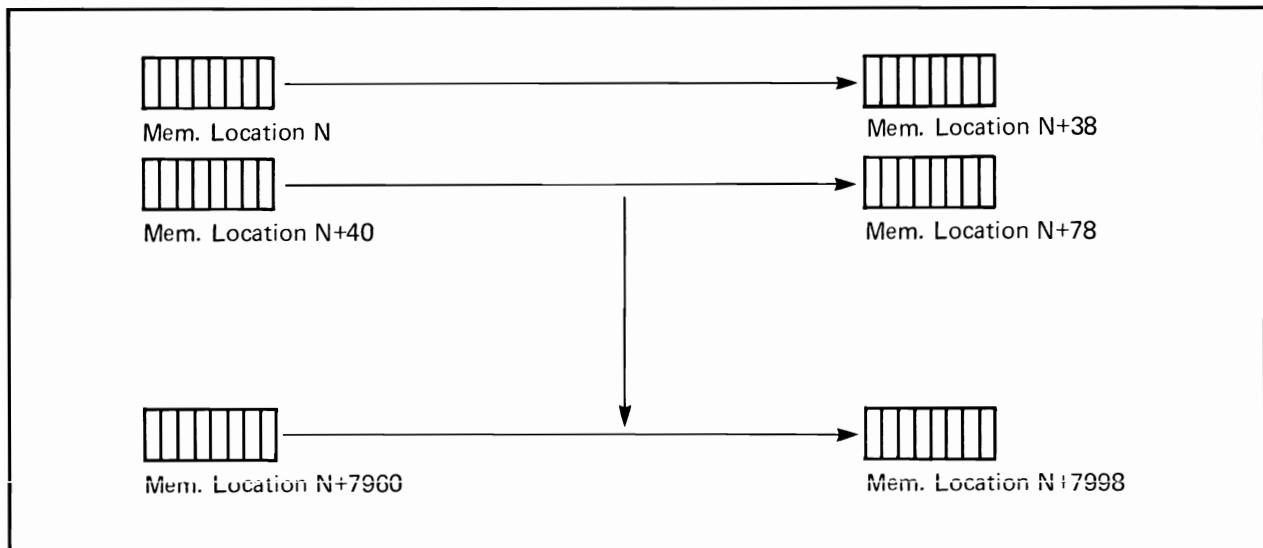

The system retrieves data for bit-plane displays by using pointers to the starting address of the data in memory. As you can see, the starting address for the even-numbered fields is one line greater than the starting address for the odd-numbered fields. Therefore, the bit-plane pointer must contain a different value for alternate fields of the interlaced display. This means that two separate Copper instruction lists are required.

To get the Copper to execute the correct list, you set an interrupt to the 68000 just after the first line of the display. When the interrupt is executed, you change the contents of the COP1LC location register to point to the second list. Then, during the vertical blanking interval, COP1LC will be automatically reset to point to the original list.

For more information about interlaced displays, see Chapter 3, “Playfield Hardware”.

## 2.8.4. Using the Copper with the Blitter

If the Copper is used to start up a sequence of blitter operations, it must wait for the blitter-finished interrupt before starting another blitter operation. Changing blitter registers while the blitter is operating causes unpredictable results. For just this purpose, the WAIT instruction includes an additional control bit, called BFD (for blitter finished disable). Normally, this bit is a 1 and only the beam counter comparisons control the WAIT.

When the BFD bit is a 0, the logic of the Copper WAIT instruction is modified. The Copper will WAIT until the beam counter comparison is true and the blitter has finished. The blitter has finished when the Blitter Finish flag is set. This bit should be unset with caution. It could possibly prevent some screen displays or prevent objects from being displayed correctly.

For more information about using the blitter, see Chapter 6, “Blitter Hardware”.

## 2.8.5. The Copper and the 68000

On those occasions when the Copper’s instructions do not suffice, you can interrupt the 68000 and use its instruction set instead. The 68000 can poll for interrupt flags set in the INTREQ register by various devices. To interrupt the 68000, use the copper MOVE instruction to store a 1 into the following bits of INTREQ:

| BIT NUMBER | NAME    | FUNCTION                                                                       |

|------------|---------|--------------------------------------------------------------------------------|

| 15         | SET/CLR | Set/Clear control bit. Determines if bits written with a 1 get set or cleared. |

| 4          | COPEN   | Coprocessor interrupting 68000.                                                |

See Chapter 7, “System Control Hardware”, for more information about interrupts.

## 2.9. SUMMARY OF COPPER INSTRUCTIONS

The table below shows a summary of the bit positions for each of the Copper instructions.

| BIT# | MOVE |      | WAIT |     | SKIP |     |

|------|------|------|------|-----|------|-----|

|      | IR1  | IR2  | IR1  | IR2 | IR1  | IR2 |

| 15   | X    | RD15 | VP7  | BFD | VP7  | BFD |

| 14   | X    | RD14 | VP6  | VE6 | VP6  | VE6 |

| 13   | X    | RD13 | VP5  | VE5 | VP5  | VE5 |

| 12   | X    | RD12 | VP4  | VE4 | VP4  | VE4 |

| 11   | X    | RD11 | VP3  | VE3 | VP3  | VE3 |

| 10   | X    | RD10 | VP2  | VE2 | VP2  | VE2 |

| 09   | X    | RD09 | VP1  | VE1 | VP1  | VE1 |

| 08   | DA8  | RD08 | VP0  | VE0 | VP0  | VE0 |

| 07   | DA7  | RD07 | HP8  | HE8 | HP8  | HE8 |

| 06   | DA6  | RD06 | HP7  | HE7 | HP7  | HE7 |

| 05   | DA5  | RD05 | HP6  | HE6 | HP6  | HE6 |

| 04   | DA4  | RD04 | HP5  | HE5 | HP5  | HE5 |

| 03   | DA3  | RD03 | HP4  | HE4 | HP4  | HE4 |

| 02   | DA2  | RD02 | HP3  | HE3 | HP3  | HE3 |

| 01   | DA1  | RD01 | HP2  | HE2 | HP2  | HE2 |

| 00   | 0    | RD00 | 1    | 0   | 1    | 1   |

X = don't care, but should be a 0 for upward compatibility

IR1 = first instruction word

IR2 = second instruction word

DA = destination address

RD = RAM data to be moved to destination register

VP = vertical beam position bit

HP = horizontal beam position bit

VE = enable comparison (mask bit)

HE = enable comparison (mask bit)

BFD = blitter-finished disable

# Chapter 3

## PLAYFIELD HARDWARE

### 3.1. INTRODUCTION

The screen display of the Amiga consists of two basic parts—playfields, which are sometimes called backgrounds, and sprites, which are easily movable graphics objects. This chapter describes how to directly access hardware registers to form playfields.

#### About this Chapter

This chapter begins with a brief overview of playfield features, including definitions of some fundamental terms, and continues with the following major topics:

- Forming a single “basic” playfield, which is a playfield the same size as the display screen. This section includes concepts that are fundamental to forming any playfield.

- Forming a dual-playfield display, where one playfield is superimposed upon another. This differs from a basic playfield in some of the details.

- Forming playfields of various sizes, and displaying only part of a larger playfield.

- Moving playfields by scrolling them vertically and horizontally.

- Advanced topics to help you use playfields in special situations.

The following topics are relevant to playfields and are discussed elsewhere. For information about the movable sprite objects, see Chapter 4, “Sprite Hardware”. There are also movable playfield objects, which are subsections of a playfield. To move portions of a playfield, you use a technique called playfield animation, which is described in Chapter 6, “Blitter Hardware”.

## Playfield Features

This section gives an overview of playfield features and how playfields are displayed and colored.

The Amiga produces its video displays with raster display techniques. You create a graphic display by defining one or more bit-planes in memory and filling them with 1's and 0's to determine the colors in your display. The picture you see on the screen is made up of a series of horizontal video lines displayed one after the other.

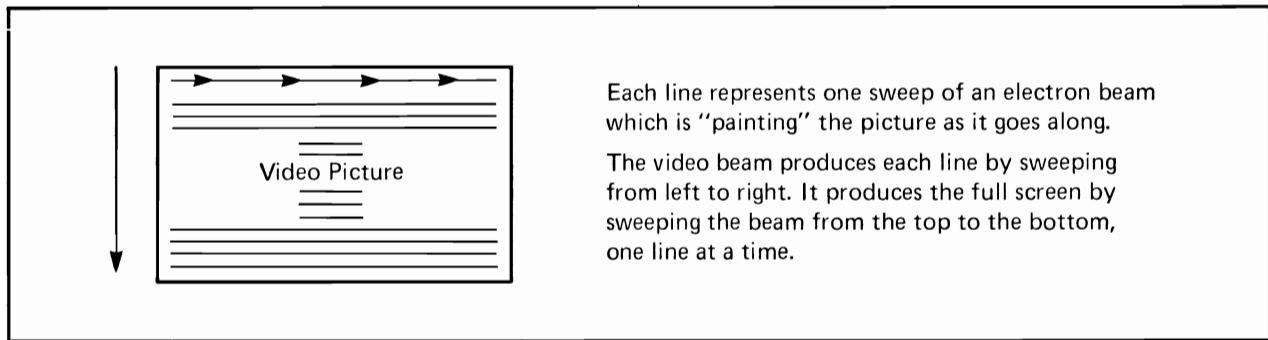

Figure 3-1: How the Video Display Picture is Produced

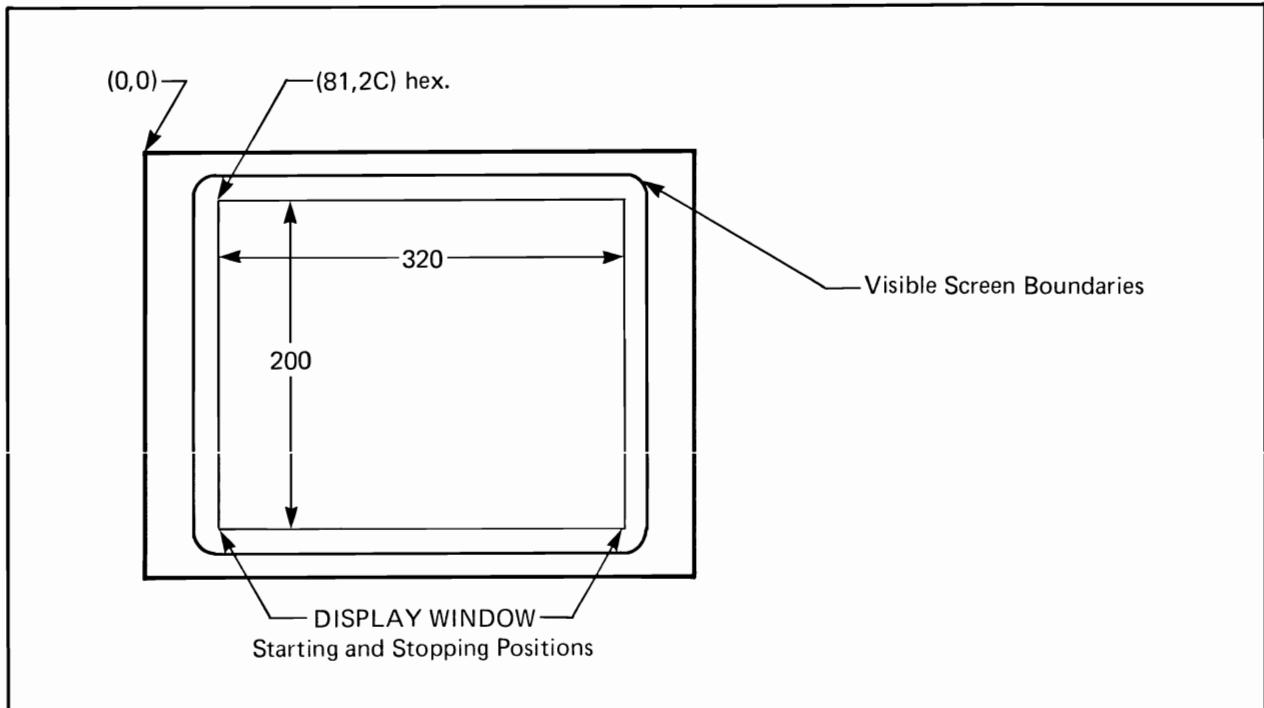

The video beam produces about 262 video lines from top to bottom, of which about 200 normally are visible on the screen. Each complete set of 262 lines is called a display field. A complete display field is produced in approximately 1/60th of a second; this is known as the field time. Between display fields, the video beam is traversing the lines you don't see and is returning to the top of the screen to produce another display field.

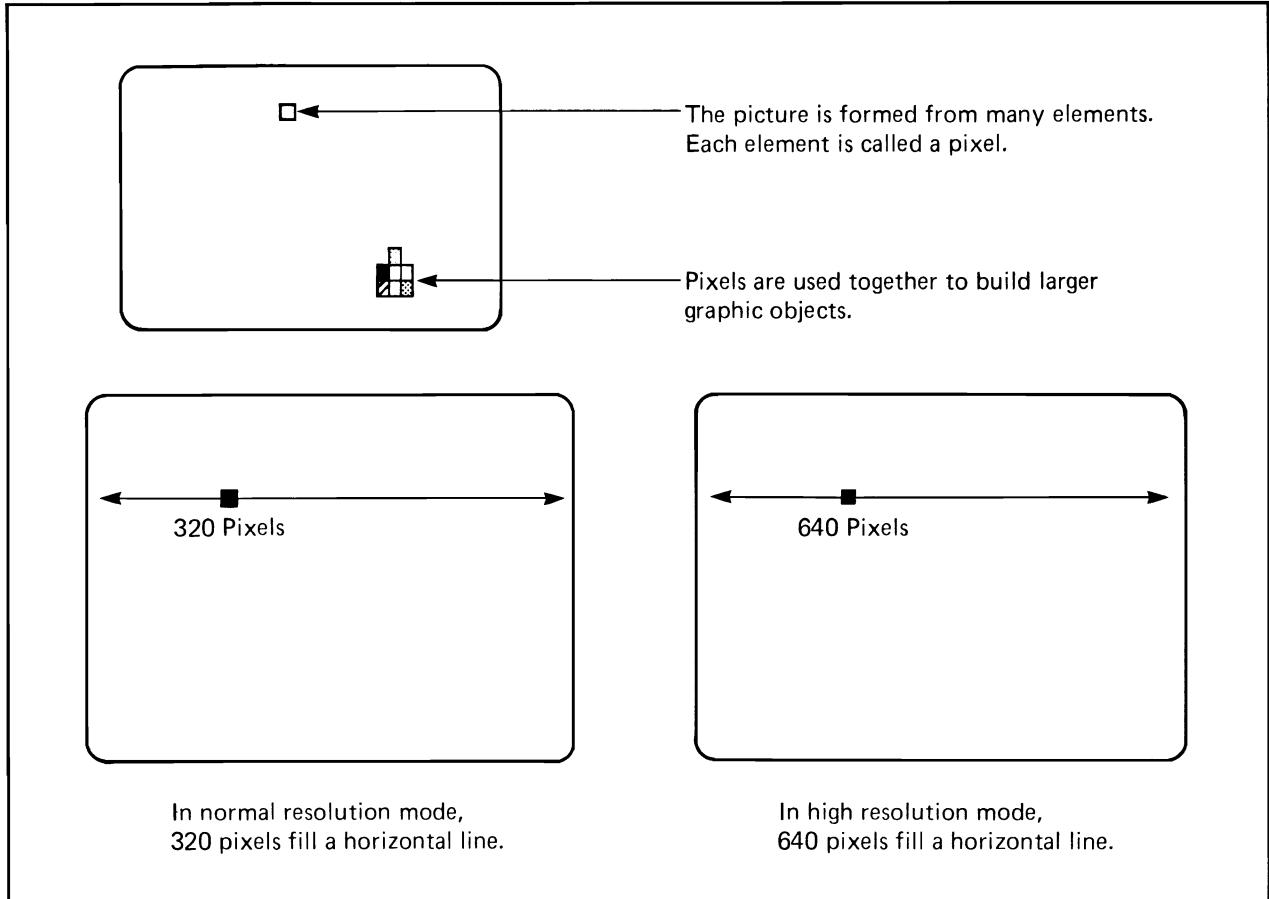

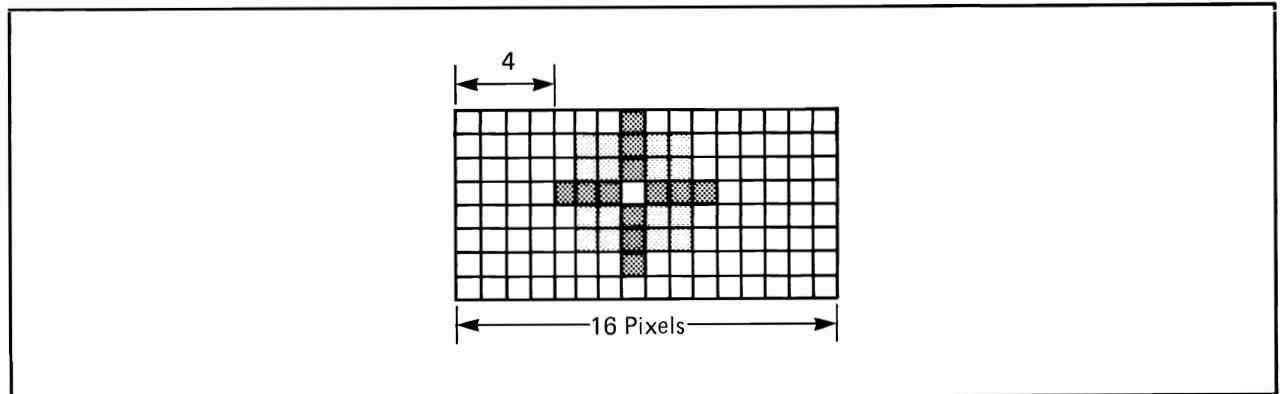

The display area is defined as a grid of pixels. A pixel is a single picture element, the smallest addressable part of a screen display. The drawings below show what a pixel is and how pixels form displays.

Figure 3-2: What is a Pixel

The Amiga has four basic display modes — interlace, non-interlace, low resolution, and high resolution. In non-interlace mode, the normal playfield has a height of 200 video lines. Interlace mode gives finer vertical resolution — 400 lines in the same physical display area. In low resolution mode, the normal playfield has a width of 320 pixels. High resolution mode gives finer horizontal resolution — 640 pixels in the same physical display area. These modes can be combined so you can have, for instance, an interlace, high resolution display.

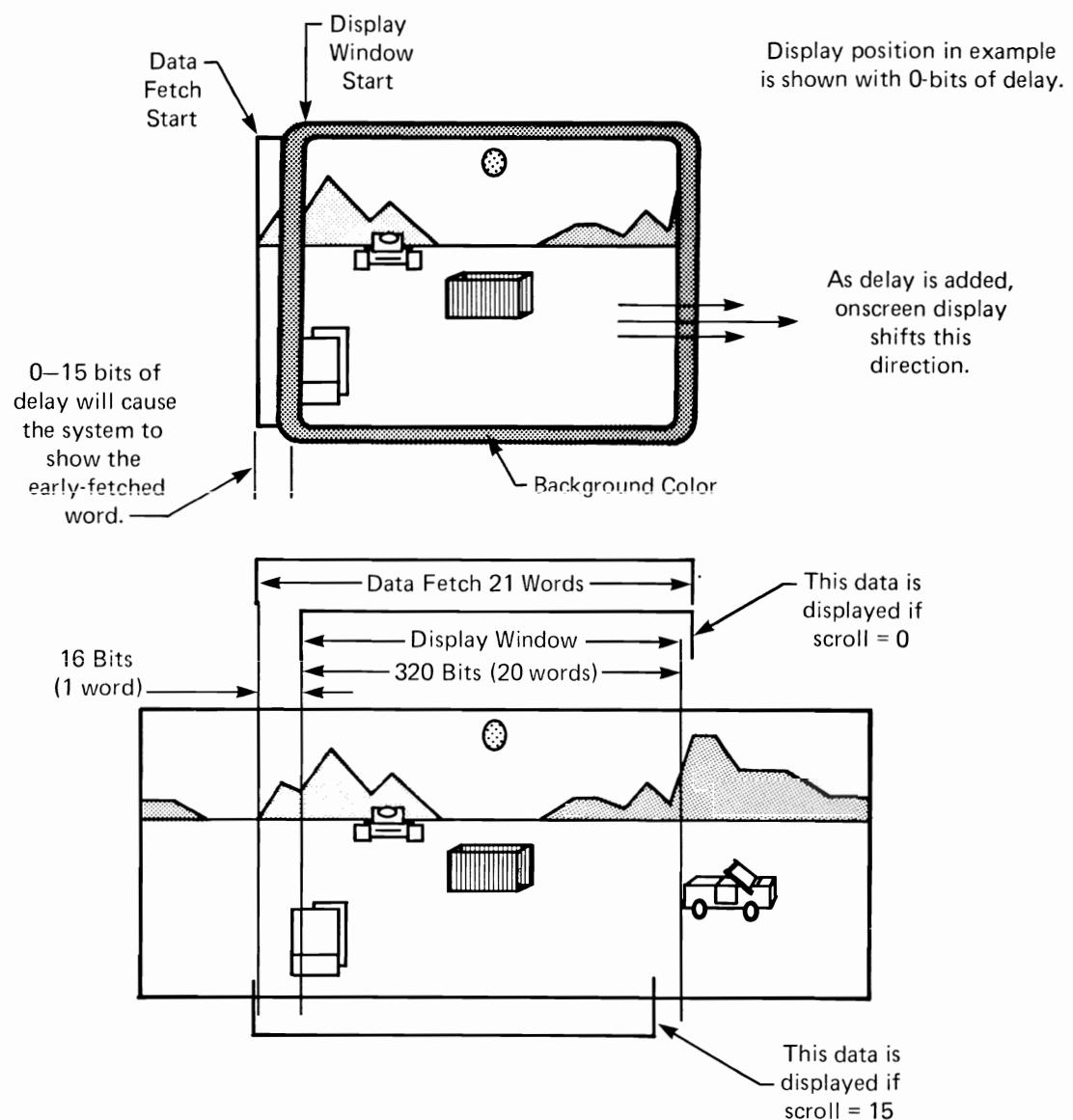

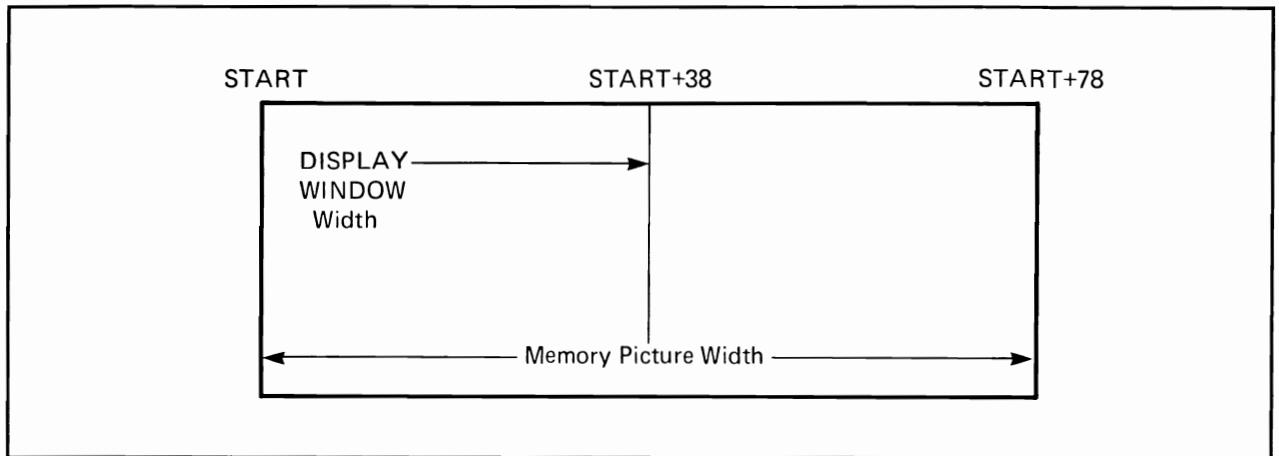

Note that the dimensions referred to as “normal” in the previous paragraph are nominal dimensions and represent the normal values you should expect to use. Actually, you can display larger playfields; the maximum dimensions are given in the section called “Bit-Planes and Playfields of All Sizes”. Also, the dimensions of the playfield in memory are often larger than the playfield displayed on the screen. You chose which part of this larger memory

picture to display by specifying a different size for the display window.

A playfield taller than the screen can be scrolled, or moved smoothly, up or down. A playfield wider than the screen can be scrolled horizontally, from left to right or right to left. Scrolling is described in the section called "Moving (Scrolling) Playfields".

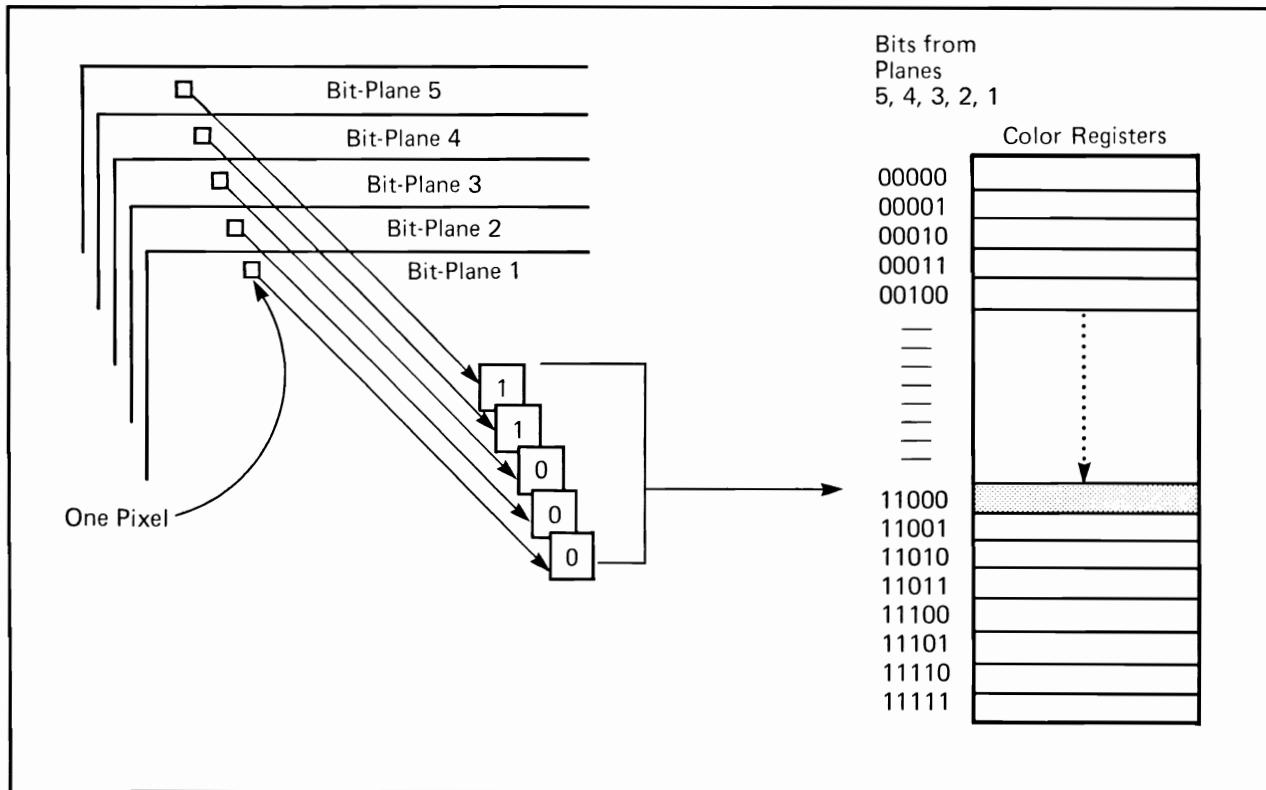

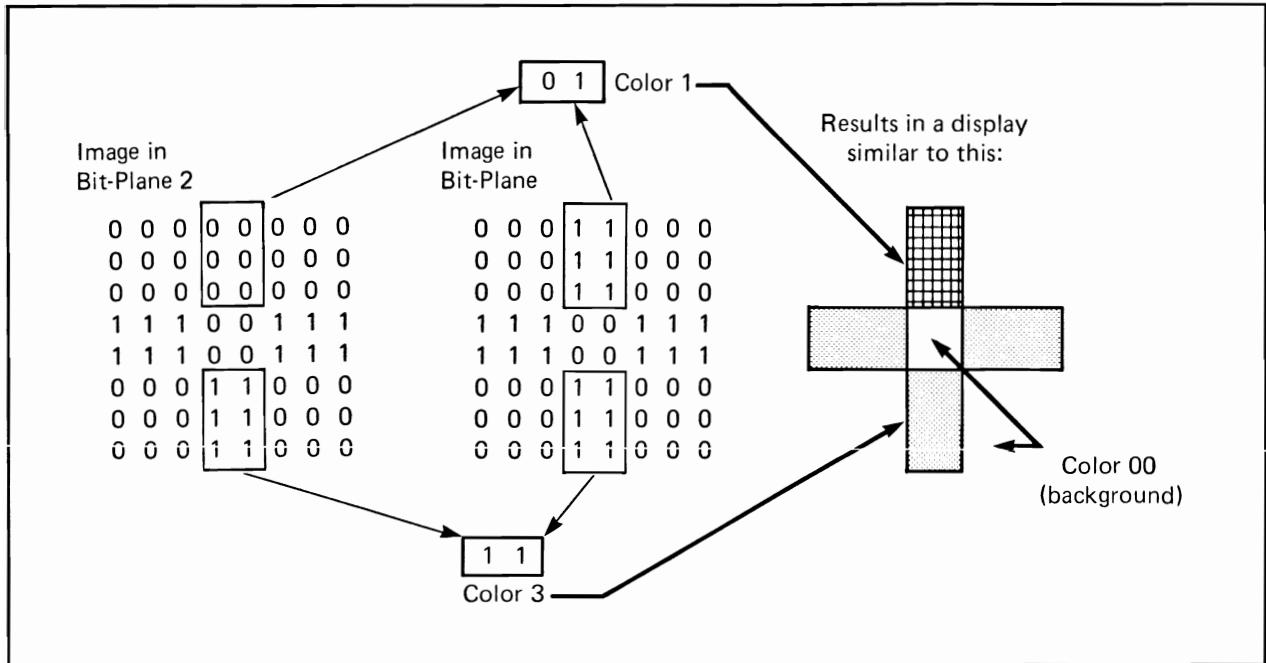

In the Amiga graphics system, you can have up to 32 different colors in a single playfield, using normal display methods. You can control the color of each individual pixel in the playfield display by setting the bit or bits that control each pixel. A display formed in this way is called a bit-mapped display. For instance, in a 2-color display, the color of each pixel is determined by whether a single bit is on or off. If the bit is a 0, the pixel is one user-defined color; if the bit is a 1, the pixel is another color. For a 4-color display, you build two bit-planes in memory. When the playfield is displayed, the two bit-planes are overlapped, which means that each pixel is now 2 bits deep. You can combine up to 5 bit-planes in this way. Displays made up of 3, 4, or 5 bit-planes allow a choice of 8, 16, or 32 colors, respectively.

The color of a pixel is always determined by the binary combination of the bits that define it. When the system combines bit-planes for display, the combination of bits formed for each pixel corresponds to the number of a color register. This method of coloring pixels is called color indirection. The Amiga has 32 color registers, each containing bits defining a user-selected color (from a total of 4,096 possible colors).

Figure 3-3 shows how the combination of up to 5 bit-planes forms a code that selects which one of the 32 registers to use to display the color of a playfield pixel.

Figure 3-3: How Bit-Planes Select a Color

Values in the highest numbered bit-plane have the highest significance in the binary number. As shown in Figure 3-4, the value in each pixel in the highest-numbered bit-plane forms the leftmost digit of the number. The value in the next highest-numbered bit-plane forms the next bit, and so on.

Sample Data for 4 Pixels

|   |   |   |   |                                         |

|---|---|---|---|-----------------------------------------|

| 1 | 1 | 0 | 0 | Data in Bit-Plane 5 – Most Significant  |

| 1 | 0 | 1 | 0 | Data in Bit-Plane 4                     |

| 1 | 0 | 0 | 1 | Data in Bit-Plane 3                     |

| 0 | 1 | 1 | 1 | Data in Bit-Plane 2                     |

| 0 | 0 | 1 | 0 | Data in Bit-Plane 1 – Least Significant |

Value 6 – COLOR6

Value 11 – COLOR11

Value 18 – COLOR18

Value 28 – COLOR28

Figure 3-4: Significance of Bit-Plane Data in Selecting Colors

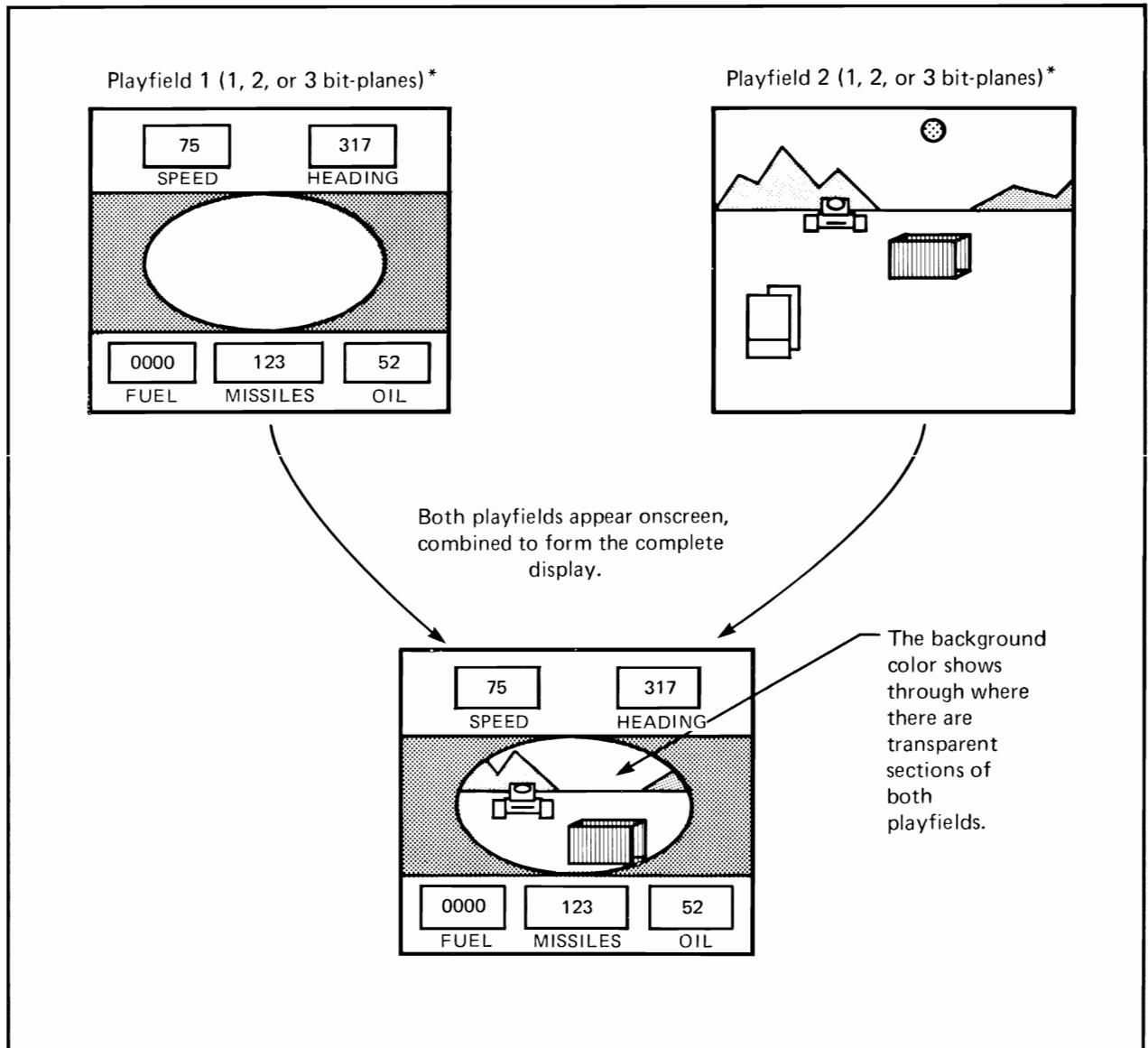

You also have the choice of defining 2 separate playfields, each formed from up to 3 bit-planes. Each of the two playfields uses a separate set of 8 different colors. This is called dual playfield mode.

## 3.2. FORMING A BASIC PLAYFIELD

To get you started, this section describes how to directly access hardware registers to form a single basic playfield that is the same size as the video screen. Here, “same size” means that the playfield is the same size as the actual display window. This will leave a small border between the playfield and the edge of the video screen. The playfield usually does not extend all the way to the edge.

To form a playfield, you need to define these characteristics:

- o height and width of the playfield and size of the display window (that is, how much of the playfield actually appears on the screen)

- o color of each pixel in the playfield

- o horizontal resolution

- o vertical resolution, or interlacing

- o data fetch and modulo, which tell the system how much data to put on a horizontal line and how to fetch data from memory to the screen

In addition, you need to allocate memory to store the playfield, set pointers to tell the system where to find the data in memory, and (optionally) write a Copper routine to handle redisplay of the playfield.

All these topics are described in this section, and some of them are expanded upon in the more specialized sections that follow. At the end of this section there is a short summary of all the steps and there are two examples showing how to form a playfield that is the same size as the screen.

### 3.2.1. Height and Width of the Playfield

Because this is a basic playfield that is the same size as the screen, the width is either 320 pixels or 640 pixels, depending upon the resolution you choose. The height is either 200 lines or 400 lines, depending upon whether or not you choose interlace mode.

### 3.2.2. Bit-Planes and Color

You define playfield color by:

1. Deciding how many colors you need and how you want to color each pixel.

2. Loading the colors into the color registers.

3. Allocating memory for the number of bit-planes you need and setting a pointer to each bit-plane.

4. Writing instructions to place a value in each bit in the bit-planes to give you the correct color.

Table 3-1 shows how many bit-planes to use for the color selection you need.

Table 3-1: Colors in a Single Playfield

| NUMBER OF<br>COLORS | NUMBER OF<br>BIT-PLANES |

|---------------------|-------------------------|

| 1 - 2               | 1                       |

| 3 - 4               | 2                       |

| 5 - 8               | 3                       |

| 9 - 16              | 4                       |

| 17 - 32             | 5                       |

### The Color Table

The color table contains 32 registers and you may load a different color into each of the registers. Here is a condensed view of the contents of the color table:

Table 3-2: Portion of the Color Table

| REGISTER NAME | CONTENTS | MEANING                                                                                                 |

|---------------|----------|---------------------------------------------------------------------------------------------------------|

| COLOR0        | 12 bits  | User defined — color for the background area and borders.                                               |

| COLOR1        | 12 bits  | User defined color number 1.<br>(For example, the alternate color selection for a two-color playfield.) |

| COLOR2        | 12 bits  | User defined color number 2.                                                                            |

| .             | .        |                                                                                                         |

| .             | .        |                                                                                                         |

| COLOR31       | 12 bits  | User defined color number 31.                                                                           |

COLOR0 is always reserved for the background color. The background color shows in any area on the display where there is no other object present and is also displayed outside the defined display window, in the border area.

If you are using the optional genlock board for video input from a camera, VCR, or laser disk, the background color will be replaced by the incoming video display.

Twelve bits of color selection allow you to define, for each of the 32 registers, one of 4096 possible colors as shown below.

Table 3-3: Contents of the Color Registers

#### CONTENTS OF EACH COLOR REGISTER

|              |        |

|--------------|--------|

| Bits 15 - 12 | Unused |

| Bits 11 - 8  | Red    |

| Bits 7 - 4   | Green  |

| Bits 3 - 0   | Blue   |

Here are some sample color register bit assignments and the resulting colors. At the end of the chapter is a more extensive list.

Table 3-4: Sample Color Register Contents

| CONTENTS OF THE COLOR REGISTER | RESULTING COLOR |

|--------------------------------|-----------------|

| \$FFF                          | white           |

| \$6FE                          | sky blue        |

| \$DB9                          | tan             |

| \$000                          | black           |

Some sample instructions for loading the color registers are shown below:

```

lea COLOR0, a0      ;get address of color register 0 into a0

move.w #$FFF, (a0)  ;load white into color register 0

move.w #$6FE, 2(a0) ;load sky blue into color register 1

```

Note that the color registers are write-only. Only by looking at the screen can you find out the contents of each color register. As a standard practice, then, for these and certain other write-only registers, you may wish to keep a “backup” RAM copy. As you write to the color register itself, you should update this RAM copy. In this way, you will always know what value each register contains.

#### Selecting Number of Bit-Planes

After deciding how many colors you want and how many bit-planes are required to give you those colors, you tell the system how many bit-planes to use.

You select the number of bit-planes by writing the number into the register BPLCON0 (for Bit Plane Control Register 0). The relevant bits are bits 14, 13, 12, named BPU2, BPU1, BPU0 (for Bit Planes Used). The table below shows the values to write to these bits, and how the system assigns bit-plane numbers.

Table 3-5: Setting the Number of Bit-Planes

| VALUE | NUMBER OF<br>BIT-PLANES | NAME(S) OF<br>BIT PLANES |

|-------|-------------------------|--------------------------|

| 000   | None *                  |                          |

| 001   | 1                       | PLANE 1                  |

| 010   | 2                       | PLANES 1 and 2           |