### **CULTURA E TEMPOS LIVRES**

- 1. ABC do Xadrez, Petar Trifunovitch e Sava Vukovitch

- Fisher/Spassky Campeonato Mundial de Xadrez de 1972, Petar Trifunocitch

- 4. ABC do Bridge, Pierre Juis e H. Lahana

- 5. Guia Prático da Fotografia, W. D. Emanuel

- ABC do Judo, E. J. Harrison

Como Fazer Cinema, Paul Petzold

- 8. Bridge Moderno, Pierre Jais e H. Lahana

- 9. Fotografia Técnicas e Truques I, Edwin Smith

- 10. Estilos do Mobiliário, A. Aussel

- 11. Fotografia Técnicas e Truques II, Edwin Smith

- 12. A Pesca Submarina, António Ribera

- 13. Teoria dos Finais de Partida, Yuri Averbach

- 14. Aprenda Rádio, B. Fighiera

- 15. Guia do Cão, Louise Laliberté-Robert e Jean-Pierre Robert

- 16. ABC do Aquário, Anthony Evans

- 17. Iniciação à Electricidade e à Electrónica, Fernand Huré

- 18. Os Transistores, Fernand Huré

- 19. Karaté I, Albrecht Pflüger

- 20. Iniciação ao Radiocomando dos Modelos Reduzidos, C. Péricone

- 21. Construa o seu Receptor, B. Fighiera

- 22. Montagens Electrónicas, B. Fighiera

- 23. O Berbequim Eléctrico, Villy Dreier

- 24. Cactos, J. Nilaus Jensen

- 25. Iniciação à Alta Fidelidade, Peter Turner

- 26. O A Tário de Água Doce, Paulo de Oliveira

- 27. ABC do Ténis, Fonseca Vaz

- 28. Karaté II, Albrecht Pflüger

- 29. ABC d Criação de Canários, Curt Af Anehjelm

- 30. Ginástica Feminina, Sonja Helmer Jensen

- 31. Cartomancia, Phea Koch

- 32. Calculadoras Electrónicas de Bolso, E. Dam Ravn

- 33. O Pastor Alemão, Gilles Legrand

- 34. Xadrez Teoria do Meio Jogo, I. Bondarevsky

- 35. Manual do Super 8 I, Myron A. Matzkin

- 36. ABC da Criação de Periquitos, Cyril H. Rogers

- 37. O Livro dos Gate, Bärbel Gerber e Horst Bielfeld

- 38. Manual do Super 8 II, Myron A. Matzkin

- 39. ABC do Mergulho Desportivo, Walter Mattes

- 40. Circuitos Integrados/Anlicações Práticas, F. Bergtold

- 41. A Apicultura, H. R. C. Riches

- 42. ABC do Cultivo das Plantas, H. G. Witham Fogg

- 43. ABC da Criação de Pombos, Kai R. Dahl

- 44. Construção de Caixas Acústicas de Alta Fidelidade, R. Brault

- 45. Raças de Canários, Klaus Speicher

- 46. Jogos de Cartas, Graciano Dolma

- 47. Cocker Spaniels, H. S. Lloyd

- 48. ABC da Caça, Fabián Abril

- 49. Aprenda Televisão, Gordon J. King

- 50. Iniciação à Pesca, Juan Nadal

- 51. Basquetebol, Marius Norregard

- 52. Caes de Caca, Santiago Pons

- 53. Aprenda Electrónica, T. L. Squires e C. M. Deason

- 54. A Avicultura, Jim Worthington

- 55. A Produção de Coelhos, P. Surdeau e R. Henaff

- 56. ABC dos Computadores, T. F. Fry

- 57. Natação para Crianças, John Idorn

- 58. O Boxer, Anni Mortensen

- 59. Voleibol, Ole Hansen e Per-Göran Persson

- 60. Iniciação à Vela, Donald Law

- 61. ABC da Filatelia, Jacqueline Caurat

- 62. A Pesca à Beira-Mar, J.-M. Boëlle e B. Doyen

- 63. Enxerto de Árvores de Fruto, Alejo Rigau

- 64. A Cultura do Morangueiro, Luís Alsina Grau

- 65. Emissores-Receptores (Walkies-Talkies), P. Duranton

- 66. Iniciação à Fotoelectrónica, Heinz Richter

- 67. Doces e Conservas de Fruta, Robin Howe

- 68. A Criação de Hamsters, C. F. Snow

- 69. A Criação de Porcos, Roy Genders

- 70. Calendário do Horticultor, Luís Alsina Grau

- 71. Jogos Electrónicos, F. G. Rayer

- 72. Cultivo de Cogumelos e Trufas, Alejo Rigau

- 73. Aprenda Televisão a Cores, Gordon J. King

- 74. Gravação em Fita Magnética, Ian R. Sinclair

- 75. Poda de Ávores e Arbustos, Roy Genders

- 76. Como Treinar o Seu Cão, E. Fitch Daglish

- 77. Instrumentos de Medida e Verificação. Heinrich Stöckle

- 78. A Criação de Caracóis, Matías Josa

- 79. Rádio Fundamentos e Técnicas, Gordon J. King

- 80. Como Fazer Gelados, Sylvie Thiébault

- 81. Iniciação à Jardinagem, Noel Clarasó

- 82. A Congelação dos Alimentos, Suzanne Lapointe

- 83. Windsurf Prancha à Vela, Ernstfried Prade

- 84. Raças de Cães, O. Hasselfeldt

- 85. Rummy e Canasta, Claus D. Grupp

- 86. A Encadernação, Annie Persuy

- 87. Aprenda Electricidade, Heinz Richter

- 88. Taxidermia, Embalsamamento de Aves e Mamíferos, Harry Hjortaa

- 89. Jogging Correr para Manter a Forma, Werner Sonntag

- 90. ABC da Cozinha Chinesa, Sonya Richmond

- 91. Jogos T. V., C. Tavernier

- 92. Amplificadores de Som, Richard Zierl

- 93. O Livro do Poker, Claus D. Grupp

- 94. Aprenda a Desenhar, Rose-Marie de Prémont e Nicole Philippi

- 95. O Minitrampolim na Escola, Sonja Helmer Jensen e Klaus Dano

- 96. Jogos de Luzes e Efeitos Sonoros para Guitarras, B. Fighiera

- 97. O Cultivo do Tomate, Louis N. Flawn

- 98. Pilhas Solares, F. Juster

- 99. A Criação Doméstica de Coelhos, C. F. Snow

- 100. Iniciação ao Futebol, Wieland Männle e Heinz Arnold

- 101. Horóscopos Chineses, Georg Haddenbach

- 102. Guia Prático de Marcenaria, Charles H. Hayward

- 103. Andebol, Fritz e Peter Hattig

- 104. Dispositivos Anti-Roubo, H. Schreiber

- 105. Perus, Pintadas e Codornizes, Jerome Sauze

- 106. Crepes Doces e Salgados, Florence Arzel

- 107. Aperitivos e Entradas, Myrette Tiano

- 108. Ténis de Mesa, Leslie Woollard

- 109. Aprenda Surf, R. Abbott e M. Baker

- 110. Futebol Técnica e Táctica, Kurt Lavall

- 111. A Vaca Leiteira, Colin T. Whittemore

- 112. O Cubo Mágico, Josef Trajber

- 113. O Perdigueiro Português, José M. Correia

- 114. Pizzas e Massas à Italiana, Marieanne Ränk

- 115. O Cubo Para Ouem Já o Faz. Josef Traiber

- 116. A Pirâmide Mágica, A Torre, O Barril do Diabo,

- M. Mrowka-W. J. Weber

117. Gansos e Patos. Marie Mourthe

- 118. Iniciação ao Kung Fu, A. P. Harrington

- 119. Electrónica e Fotografia, Hanns-Peter Siebert

- 120. O Livro da Fortuna. Douglas Hill

- 121. Construção de um Alimentador de Corrente, Waldemar Baitingu

- 122. Hóquei em Patins, Francisco Velasco

- 123. Técnicas de Tiro, Anton Kovacic

- 124. Aprenda a Tricotar, Uta Mix

- 125. ABC da Patinagem, Christa-Maria e Richard Kerler

- 126. A Pesca e os seus Segredos, Armand Deschamps

- 127. O Osciloscópio, R. Rateau

- 128. Guia Prático da Banda do Cidadão, T. M. Normand

- 129. Sumos e Batidos, Manfred Donderski

- 130. Introdução à Programação de Microcomputadores, Peter C. Sanderson

- 131. Aprenda Croché, Uta Mix

- 132. ABC do Microprocessador, P. Mélusson

### P. MÉLUSSON

# ABC DO MICROPROCESSADOR

Título original:

INICIATION À LA MICROINFORMATIQUE:

LE MICROPROCESSEUR

Copyright by Editions Techniques et Scientifiques Françaises Tradução de Conceição Jardim e Lúcio Nogueira Fotografia da capa gentilmente cedida pela LANDRY, Engenheiros Consul-

Fotografia da capa gentilmente cedida pela LANDRY, Engenheiros Consultores, Lda, — LISBOA

Reservados todos os direitos para a língua portuguesa à EDITORIAL PRESENÇA, LDA. Rua Augusto Gil, 35-A — 1000 LISBOA

### 1 INTRODUÇÃO

# Da Máquina de Calcular ao Computador Do Computador ao Microcomputador

A ciência informática é actualmente, nas suas aplicações essenciais, o domínio das *Calculadoras* e dos *Computadores*.

Uma rápida observação da evolução passada desta ciência permitirá situar melhor o seu contexto de desenvolvimento. Encontra-se evidentemente ligada à evolução de certas técnicas, que vamos apresentar por ordem cronológica:

## 1. A ÉPOCA DA MECÂNICA PURA

Já anteriormente à era cristã, cerca de 500 anos antes de Jesus Cristo, os chineses inventaram o primeiro instrumento para realização de cálculos: o ábaco. Este instrumento permitiu-lhes contar rapidamente e com rigor. O ábaco ainda hoje é empregado na nossa época em certos locais do planeta. Serve de suporte material ao homem para a realização de um cálculo. Para o utilizar judiciosamente o homem deve empregar a sua força muscular e a sua inteligência.

Já não acontece o mesmo quando em 1642 Blaise Pascal inventa a primeira máquina de calcular que contém o seu

próprio mecanismo de funcionamento.

No mesmo século Jacquard inventa o tear programado por cartões perfurados. Esta ideia de programação é já um prelúdio do funcionamento de certas unidades periféricas actualmente utilizadas nos computadores.

### 2. A ÉPOCA DOS MECANISMOS ELÉCTRICOS

Em 1924 o engenheiro norueguês *Bull* deposita uma patente de um conjunto electro-mecânico, e em 1936 os americanos utilizam uma máquina de calcular cujo automatismo é assegurado por *relés electro-mecânicos*.

### 3. A ÉPOCA DA ELECTRÓNICA

Esta época pode ser dividida em três fases sucessivas, em função dos componentes existentes:

- a) Fase das válvulas. Iniciar-se-á em 1950, com o nascimento do *Univac 1*. É o primeiro computador comercial. Distingue-se do calculador por possuir um jogo de instruções que asseguram a possibilidade de utilizar numerosos programas. A elaboração de programas permite, com efeito, à máquina resolver problemas de tipos diferentes.

- b) **Fase dos semicondutores** (díodos e transístores): Inicia-se por volta de 1960, data em que surgem no mercado os primeiros computadores completamente transistorizados. Incluem geralmente entre 5000 e 10 000 transístores e um número equivalente de díodos.

### c) Fase dos circuitos integrados.

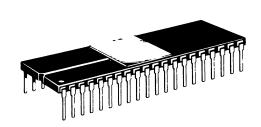

Trata-se em particular dos circuitos designados por LSI, ou seja, «large scale integration». Podem conter, cada um deles, entre 15 000 e 20 000 junções difundidas numa pastilha de salício com algumas dezenas de milímetros quadrados de superfície.

Graças a estes circuitos vai-se poder passar do domínio da informática para o da microinformática. Surge primeiramente a era da máquina de calcular de algibeira, e em seguida a actual, ainda nos seus inícios mas já evoluída, do microcomputador.

A alma deste microcomputador é o microprocessador. É o órgão encarregue de resolver as operações aritméticas e as funções lógicas de acordo com informações tratadas de maneira sequencial.

Em 1971 surge o primeiro microprocessador no mercado. Em 1973 aparece o primeiro microcomputador equipado com um microprocessador: o *Micral*, da firma francesa **R2E**.

O computador é uma máquina de grandes dimensões

cujo preço de custo é bastante elevado. É-lhe no entanto possível reduzir com facilidade a quantidades e a qualidades os mais diversos problemas, devendo ainda, para ser rentável, funcionar regularmente em pleno rendimento e evitar os tempos mortos. Por estas razões, só pode ser usado por firmas comerciais, industriais ou financeiras de grandes dimensões.

Nas firmas menos importantes, podem-se instalar terminais. Estes terminais encontram-se ligados ao computador central através de linhas convenientemente montadas, alugadas por essas firmas ao possuidor do computador central. Neste caso os terminais trabalham em tempo partilhado ou, como se diz em inglês, em regime de time sharing.

Os terminais tomam, segundo uma ordem de prioridades estabelecida em função da urgência e da qualidade das suas necessidades, uma parte do tempo do computador central.

No entanto, é ainda necessário, admitir aqui que um tal sistema de exploração exige no seu conjunto uma organizacão massiva e cara.

O microcomputador é pelo contrário, quando comparado ao computador de grandes dimensões, um modelo de preço de custo claramente inferior, graças, em particular, à flexibilidade da organização das suas estruturas, que se podem adaptar com facilidade, depois de um estudo sério, às necessidades específicas de cada empresa.

As suas pequenas dimensões e a sua faculdade de adaptação economicamente muito vantajosas, baseadas na simplicidade dos seus circuitos, devem permitir nos próximos anos um desenvolvimento sem precedentes em todos os domínios da electrónica, tanto no dos circuitos lógicos como no âmbito profissional das telecomunicações, dos automatismos industriais, da televisão, dos electrodomésticos e em muitos outros sectores a que ao longo dos tempos serão aplicados.

### O CÉREBRO HUMANO E O CÓMPUTADOR: CÉREBRO ROBOT

O computador é um cérebro robot que apresenta analogias com o cérebro humano.

A fim de os definir, é portanto necessário imaginar o que é o cérebro humano e estabelecer paralelismo entre este e o cérebro robot de um computador.

É o que iremos tentar fazer.

No plano material, é um órgão. É a parte hardware do cérebro ou, por outras palavras, a parte concreta e palpável do cérebro.

Devemos agora tentar compreender a maneira como, neste órgão, neste «hardware», são encaminhadas as ideias, se elabora o raciocínio que conduz ao comando do nosso corpo.

Toda esta elaboração das ideias constitui o software do cérebro, ou seja a sua parte abstracta, não palpável.

Assim, para o técnico de informática:

O concreto, ou seja o circuito, tudo o que se pode ver, tocar, é o hardware;

O abstracto, ou seja a parte imaterial da ciência, a matéria cinzenta, é o software.

O pensamento humano, para se forjar e exprimir tem necessidade de dois centros constitutivos distintos:

**O primeiro centro** é a *memória*. É o lugar onde todas as informações adquiridas são classificadas em «pequenos compartimentos» perfeitamente bem ordenados.

A capacidade total da memória é «variável» mas não «infinita».

Além disso, certas informações, ou dados, ou ainda, em inglês, data, devem ser armazenados definitivamente, sem nunca serem limpos da memória. Estes «dados» serão cuidadosamente «empilhados» numa memória ROM(Read Only Memory). Trata-se de uma memória apenas de leitura, indestrutível.

Esta memória fixa é por vezes designada por memória morta.

Pelo contrário, outras informações, que não constituem dados principais, mas apenas resultados da composição ordenada daqueles, não têm necessidade de ficarem eternamente guardadas; podem até só ser necessárias uma vez. Deve portanto ser possível:

### Servir-nos delas:

2. Apagá-las de modo a deixar livres os compartimentos necessários à acumulação de novos dados.

Todas estas informações fugitivas ou temporárias serão escritas e depois apagadas nas RAM (Random Access Memory).

Por vezes, estas memórias são também chamadas, por

oposição às memórias mortas, memórias vivas.

Encontram-se no cérebro robot, sendo memórias de onde se pode extrair os dados para os ler, apagando-os em seguida a fim de deixar espaço livre que será em seguida utilizado para armazenar novas informações.

A leitura de um dado extraído ou a escrita de um dado introduzido realiza-se graças à função Read/Write do compu-

tador.

O segundo centro do nosso cérebro é o do raciocínio. É nele que se elabora o tratamento das ideias. Este centro é capaz de efectuar:

Úm raciocínio lógico (resolve os problemas relativos

às funções lógicas);

— um raciocínio de cálculo que os informáticos designam por *algoritmo* (um processo de cálculo). Resolve os problemas relativos às *operações aritméticas*.

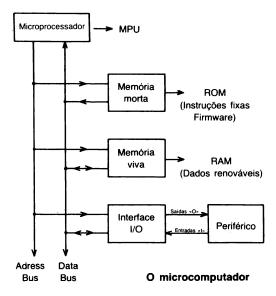

Este centro é designado no microcomputador, ou seja no nosso cérebro robot, por *microprocessador*.

As abreviaturas usadas para o designar, são:

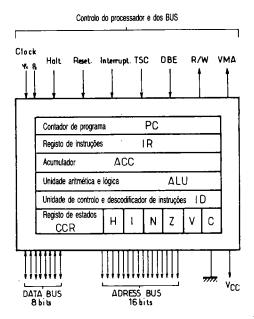

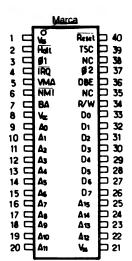

A **CPU** (Central Processing Unit), ou seja, a unidade central de tratamento do computador, ou ainda a **MPU** (microprocessing Unit), ou seja, unidade de tratamento do microcomputador.

O centro do próprio microprocessador, onde se executa verdadeiramente a resolução dos problemas lógicos e aritméticos, designa-se pelo termo **ALU** (Arithmetic and Logic Unit).

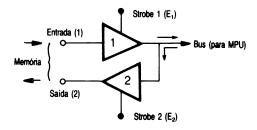

Para efectuar um raciocínio, por exemplo a operação aritmética (4 + 5), o centro de raciocínio (o microprocessador do nosso cérebro robot) deve procurar nas memórias as informações 4 e 5, e finalmente a *instrução* (+). Para tal é necessário que existam fibras condutoras entre o MPU e os locais das memórias onde estão armazenados os diferentes dados. Estas fibras são designadas **BUS**, ou também *feixes de linhas*.

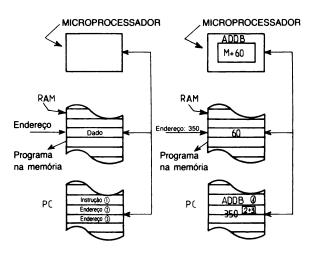

### 1. O Adress Bus e o Data Bus

O Adress Bus (bus de endereços) é o feixe de linhas que liga o MPU aos endereços onde estão contidos na memória os dados procurados.

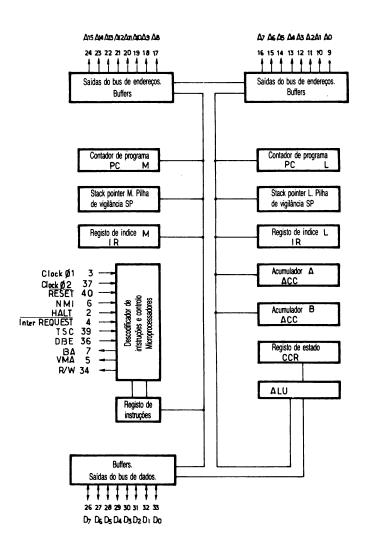

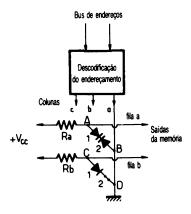

Figura 1

13

O Adress Bus é geralmente *unilateral*, ou seja, os dados só se movimentam nas suas linhas num único sentido:

### MPU - MEMÓRIA

O Data Bus (bus de dados) é geralmente bilateral, ou seja, pode funcionar em ambos os sentidos: MEMÓRIA --> MPU quando a informação foi procurada pelo MPU no seu endereço, ou ainda no sentido MPU --- MEMÓRIA quando acaba de ser obtido na unidade central de tratamento o resultado de uma operação e se pretende guardá-lo num endereço livre de uma memória RAM.

Na nossa operação, 4 e 5 são os «data», ou dados aritméticos. O «algoritmo» ou «processo de cálculo» é definido pelos sinais + e =. Estes sinais constituem a «instrução» do cálculo a efectuar. A organização do trabalho do computador é feita por *instruções*. O conjunto das instruções de um microprocessador pode ser designado por *jogo de instruções*.

O conjunto das instruções necessárias para resolver uma

função chama-se programa.

Certos programas são complexos. A fim de os simplificar, pode-se dividi-los em *sub-rotinas* típicas. Aquele que concebe um programa é designado por *programador*. Todas as operações indicadas num programa são realizadas sequencialmente segundo uma ordem bem estabelecida.

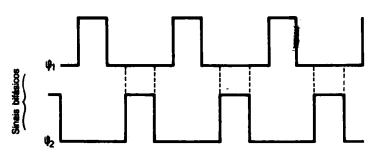

A execução das instruções é sintonizada temporalmente e controlada por sinais de relógio ou clock que podem ser

obtidos a partir de um «quartzo».

Os órgãos de comando ou de controlo das operações podem ser activados por sinais a eles conduzidos por um «bus» designado por bus de comando ou de controlo.

Toda esta organização de um microcomputador tem como suporte o sistema binário que se presta facilmente à utilização de um sinal eléctrico que trabalha no regime de tudo ou nada.

As funções lógicas e os cálculos podem ser expressas neste sistema, que apenas utiliza os algarismos 1 e 0 («tudo») ou «nada») para designar todo o conteúdo de um dado programa.

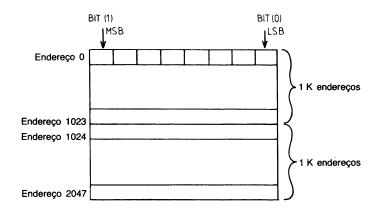

A informação elementar do sistema binário é designada pela palavra bit (Binary Digit).

Uma palavra é composta por um certo número de bits. Quanto mais bits puder comportar maior é o seu rigor.

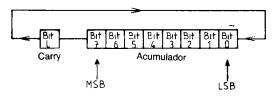

Na inscrição de uma palavra na memória, o bit da direita é o **LSB** (Less Significant Bit), ou seja, o bit menos significativo.

O bit mais à esquerda é o MSB (Most Significant Bit), ou seja, o bit mais significativo.

Os microprocessadores comportam em geral palavras de 4 a 8 ou 16 bits. Actualmente, a maior parte destas máquinas são estruturadas com palavras de 8 bits.

Uma palavra de 8 bits é designada por byte ou ainda octeto.

Finalmente, nenhum cérebro robot pode viver apenas em circuito fechado, tal como de resto o cérebro humano.

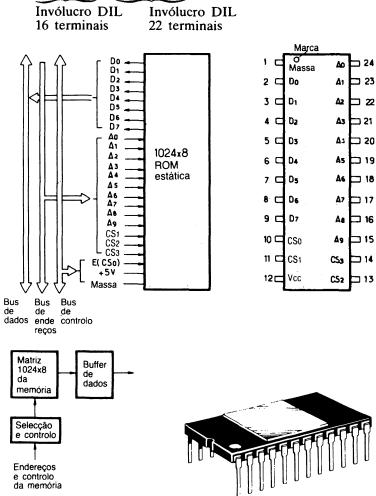

Figura 2 — Representação de uma memória de 2 K palavras de 8 bits.

Com efeito, este último necessita de trocar as suas ideias com os seus semelhantes. Relativamente a cada um de nós, os nossos vizinhos constituem «periféricos». Quando alguém nos põe uma questão, esta surge-nos como o resultado do seu próprio pensamento. Este não pode ser completamente igual ao nosso, e para podermos compreender e relacionar o

seu tratamento lógico ao nosso, necessitamos de uma interface entre o nosso centro de raciocínio, ou seja o nosso CPU, e o do periférico, a qual adapta o nosso sistema de raciocínio ao do nosso interlocutor.

Esta interface pode ter vários nomes:

É o I/O (input/output, entrada/saída) de:

Input = entrada dos dados provenientes de um periférico.

Qutput = saída dos dados para um periférico.

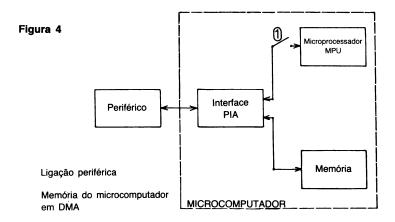

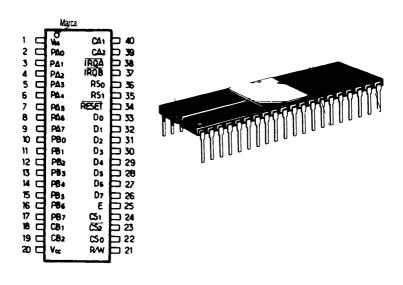

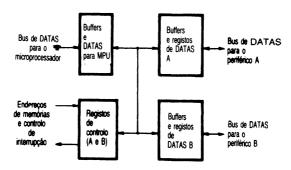

É ainda o PIA (Peripheral Interface Adapter)

Recebemos normalmente de um periférico um pedido

de dados ou um pedido de cálculo ou de «lógica».

Se se trata de um simples pedido de dados, o nosso cérebro robot pode ter a possibilidade de colocar em posição de entrada — **Three state control** (TSC) — o CPU, ou seja, pôr a entrada em estado de impedância infinita. Pelo contrário, o PIA liga-se directamente à memória de um microcomputador que inclui os dados exigidos. Diz-se então que o PIA trabalha em **DMA** (Direct Memory Access), ou seja, em acesso directo à memória.

Se se trata de um pedido de cálculo ou de lógica, o PIA

é ligado directamente ao nosso MPU.

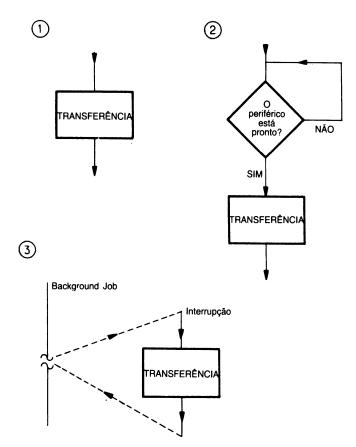

No momento em que o nosso MPU recebe um pedido proveniente do periférico através do PIA e está já a executar um programa, podem ser consideradas duas soluções:

Solução 1. O problema que está a ser resolvido é mais importante do que o pedido exterior. Continua portanto a ser executado normalmente até ser terminado, e o pedido exterior fica à espera durante algum tempo.

Solução 2. O pedido proveniente do exterior é mais urgente do que a resolução do programa actualmente tratado

no MPU.

Neste caso, produz-se uma interrupção. O programa que está ser resolvido pára. O ponto onde se chegou pode ser guardado na memória a fim de ser conservado numa memória especial designada **LIFO** (last in, first out), isto é, a última informação a entrar é a primeira a sair. O pedido exterior é então tratado, sendo o programa anterior retomado no ponto onde estava quando o pedido exterior acaba de ser satisfeito.

E já que comparámos o homem à máquina, resumamos em algumas palavras esta analogia:

1 - em TSC (Impedância infinita)

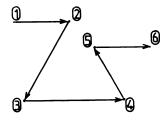

Figura 3

- 1 programa em tratamento;2 intervenção de um fenó-

- meno exterior exigindo uma interrupção;

- 3 o programa é interrompido;

- 4 a interrupção é tratada;

- 5 volta-se ao programa 1.

- 6 o programa 1 é retomado, terminando-se o seu tratamento.

17

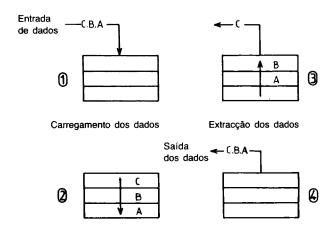

Figura 5 — A última informação introduzida é a primeira extraída, pois os dados são «empilhados» arbitrariamente por cima e esvaziados igualmente por cima.

Diz-se assim que uma memória LIFO é uma «pilha», ou ainda um registo de empilhamento.

Suponhamos que se pretende realizar a soma de vários números:

O órgão periférico do microcomputador neste sistema pode ser assimilado à folha de papel onde está inscrita a lista dos números a adicionar.

A folha de papel é com efeito a *fonte* dos dados a tratar. Quando o resultado for escrito por baixo, essa folha será igualmente o local de *destino*.

Os olhos que observam os dados a tratar e a mão que escreve o resultado constituem o sistema de interface (1/0).

Os olhos conduzem os números à memória

As memórias, quer se trate da do homem ou da do computador, desempenham o mesmo papel. Contêm ambas o algoritmo da soma.

A porção do cérebro que realiza a soma é o seu centro de raciocínio; o CPU do computador realiza a mesma função.

E no entanto, existe entre o homem e a máquina duas diferenças essenciais:

1. A máquina tem a possibilidade de resolver sem cansaço e a grandes velocidades tarefas repetitivas, o que o homen a se a cala faces.

mem não pode fazer.

2. O homem tem a ideia de criação graças à sua intuição e à sua imaginação. A máquina encontra-se completamente desprovida desta ideia, o que obriga o homem a ditar-lhe um programa em todos os detalhes. Assim, a máquina encontra-se ainda a um nível bastante inferior ao do homem.

## COMPUTADOR — CALCULADORA MICROPROCESSADOR O QUE É VOCÊ?

Um computador é uma máquina capaz de tomar decisões e realizar operações aritméticas ou lógicas disponíveis na sua saída de acordo com os programas apresentados à sua entrada.

Podem-se distinguir três tipos diferentes de computadores:

### 1. OS COMPUTADORES ANALÓGICOS

Nestes computadores, a informação é apresentada e tratada sob forma analógica.

Exemplo de uma forma analógica:

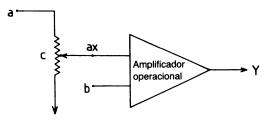

Pretende-se resolver a função: y = ax + b.

Figura 6

O esquema da figura 6 riostra o circuito (hardware) de computador que permite resolver a função numa única sequência. A variável é x, e a amplitude eléctrica do seu sinal é proporcional à determinação da posição do contacto do potenciómetro (ponto C).

Pode-se portanto afirmar que existe uma proporcionalidade entre o valor calculado da função y e o da amplitude do sinal eléctrico que lhe corresponde.

### 2. OS COMPUTADORES DIGITAIS

Nestes computadores, a informação é apresentada e tratada numa forma digital (sequência de níveis eléctricos B (baixo) e H (alto) definidos pelos números binários 0 e 1).

Nos parágrafos seguintes serão dados exemplos de tratamento em forma binária.

### 3. COMPUTADORES HÍBRIDOS

Nestes computadores encontram-se combinados os dois tipos de informações eléctricas (analógico e digital).

### 4. COMPUTADORES E CALCULADORAS DIGITAIS

Um computador, tal como uma calculadora, de tipo «digital», é capaz de armazenar e tratar em forma binária as informações.

Interessa portanto definir mais claramente a diferença que existe entre a calculadora e o computador.

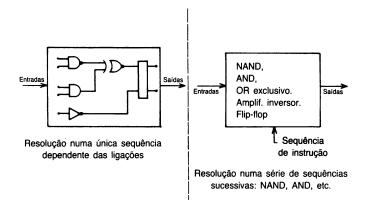

Uma calculadora realiza apenas a função que lhe foi atribuída, de forma repetitiva, ao serem montados os circuitos que possui. É um sistema hardware.

As suas ligações internas, associando um certo número de circuitos digitais elementares, portas e flip-flops, constitui o que se pode designar por uma lógica por fios condutores.

Esta lógica obtida por simples ligações eléctricas é realizada geralmente num circuito impresso.

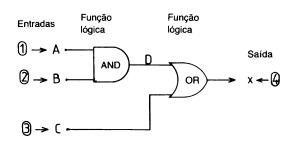

Exemplo deste tipo de lógica: pretende-se resolver numa calculadora digital a função Y = A.B + C.

O esquema da figura 7 mostra o circuito lógico que permite resolver esta função numa única sequência.

Se se apresentam nas entradas 1, 2 e 3, num modo para-

lelo, ou seja, simultaneamente, as informações A, B e C, obter-se-á na saída 4 o valor Y procurado.

Um computador pode realizar qualquer tarefa ditada

por uma série de instruções (sistema software).

É esta a diferença principal entre ele e uma calculadora. Por outro lado, a sua utilização torna-se mais complicada pelo facto de, para programar uma sequência de instruções, se tornar anteriormente necessário conhecer a linguagem assimilada pelo computador.

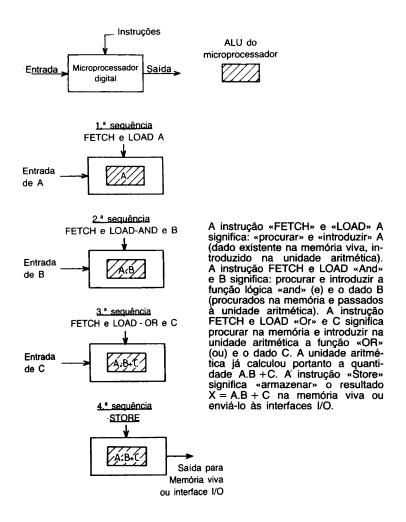

Exemplo de sequências de instruções programadas:

Retomemos a nossa função X = A.B + C, e procuremos resolvê-la utilizando um computador.

O esquema sinóptico das sequências de instruções da figura 8 mostra-nos como é resolvido este problema.

Figura 8

Através do esquema da figura 9 é possível resumir de uma maneira muito simples a diferença essencial de funcionamento entre a «lógica por ligações eléctricas» e um computador.

Figura 9 — À esquerda, exemplo de lógica hardware. À direita, exemplo de lógica software.

No comércio encontram-se três tipos de computadores digitais, classificados em função das aplicações consideradas:

- os grandes computadores;

- os minicomputadores;

- -- os microcomputadores

Todos têm a mesma estrutura principal, e o que os diferencia entre si é essencialmente a sua dimensão, ou seja:

- a sua capacidade de memória;

- a dimensão de palavra que aceitam (número de bits de uma palavra).

- o número e a qualidade das instruções neles disponíveis.

- a velocidade de execução das instruções.

Figura 10

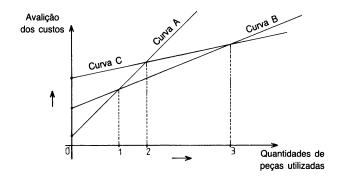

Distinguimos as abcissas:

Na zona 0, 1 — Preferência pela lógica por ligações eléctricas (A)

Na zona 1, 3 — Preferência pelo microprocessador (B)

Na zona acima de 3 — Preferência pelo Custom Design (C)

Deve-se notar que na zona 1, 2, se de facto é aconselhado o microprocessador, pode-se no entanto optar por uma lógica por ligações, mais barata que o custom design.

Estas diferentes potencialidades conduzem a grandes variações de preços e de campo de aplicações entre as três categorias.

Iremos considerar sobretudo, neste livro, os microprocessadores digitais, que são aqui objecto de um pequeno curso de iniciação.

Falemos portanto do microprocessador, alma do microcomputador.

É importante fornecer agora uma definição mais rigorosa que a anteriormente dada.

Á França propôs à Comissão Electrónica Internacional a seguinte definição, bastante completa:

«Um microprocessador de circuito integrado é um circuito integrado numérico capaz de, após identificação de uma sequência de operações, efectuar operações de tratamento da informação».

Um microprocessador:

- 1. Aceita informações de dados codificados para tratamento e/ou armazenamento.

- 2. Efectua o conjunto das operações lógicas, aritméticas e de movimento sobre as informações de entrada e/ou sobre todas as informações guardadas em memória.

- 3. Restitui na saída as informações codificadas resultantes do tratamento efectuado.

- 4. Pode receber e/ou fornecer informações relativas ao seu funcionamento ou ao seu estado.

Para terminar este capítulo, definamos através de um gráfico uma comparação interessante dos custos entre:

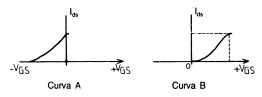

Curva A — Uma lógica por ligações eléctricas, com elementos «standard»: operadores, básculas, registos simples, etc.

Curva B — Um microprocessador

Curva C — Uma lógica particular, estudada especialmente para um cliente e tendo em conta as suas necessidades específicas. Trata-se de um Custom Design.

Esta comparação, realizada na figura 10, entre os vários preços de custo é realizada em função do número de peças a negociar.

Tudo isto leva-nos a pensar que, antes de tomar uma decisão sobre o emprego de um destes três tipos de equipamento, se torna necessário um estudo prévio de rentabilidade.

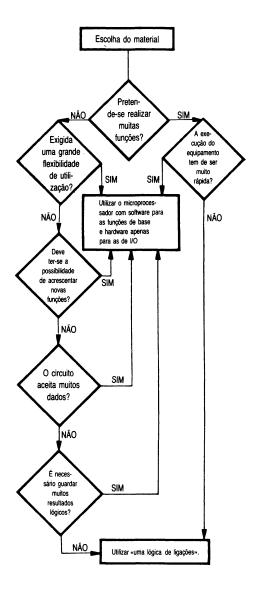

Na figura 11 apresenta-se um quarto sinóptico que nos permite realizar, em função de critérios relacionados com o nosso tipo de utilização, uma escolha judiciosa entre a lógica por ligações e o microprocessador.

Figura 11

## AS LINGUAGENS DOS COMPUTADORES OS APARELHOS DE DESCODIFICAÇÃO DAS LINGUAGENS EM «BINÁRIO PURO»

Repitamos aqui uma vez mais que o computador só conhece a linguagem binária pura, também designada por binária natural, que se traduz por uma sucessão de zeros e de uns, utilizados tanto para receber pedidos como para efectuar operações aritméticas ou funções lógicas.

Se se impusesse ao programador a realização das instruções a dar ao computador directamente em binário natural, certamente que ao fim de alinhar alguns milhares de zeros e uns se enganaria e o trabalho se tornaria bastante aborrecido.

Imaginaram-se portanto tipos de linguagens que traduzem estas sucessões de zeros e uns de uma maneira mais sugestiva e fácil de utilizar pelo programador.

Estas linguagens são introduzidas numa máquina, a qual as traduzirá em binário natural a fim de ser digerido pelo computador.

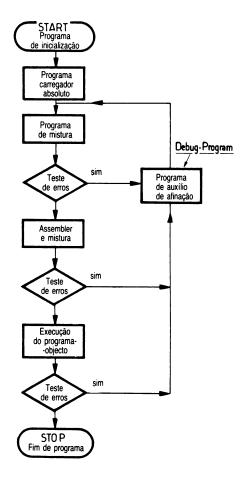

O programa elaborado pelo programador é designado por *programa-fonte*.

Este programa é descodificado em binário natural pela máquina, constituindo ao entrar no computador o chamado programa-objecto.

O quadro seguinte mostra-nos algumas das linguagens de programação, cujas definições e diferenças essenciais iremos definir.

Neste quadro, em 1, os programas-fonte relativamente curtos são codificados em octal, em hexadecimal ou em BCD (decimais codificados em binário). Explicaremos o seu funcionamento no capítulo seguinte, dedicado ao sistema de cálculo binário.

### QUADRO DAS PRINCIPAIS LINGUAGENS DE PROGRAMAÇÃO

| Programa | Codificação ou<br>Linguagem |         | Aparelho tradutor<br>em linguagem máquina |                          |

|----------|-----------------------------|---------|-------------------------------------------|--------------------------|

| Programa |                             |         | Interno ao<br>computador                  | Externo ao<br>computador |

| ı ı      | Octal Hexadecimal B.C.D.    |         |                                           |                          |

| Curto    |                             |         |                                           |                          |

| Curto    |                             |         |                                           |                          |

|          | Mnemónica ou<br>simbólica   |         | Assembler residente                       | Cross-<br>-assembler     |

| 2        |                             | Algol   | Compilador                                |                          |

| Comprido | Linguagem<br>evoluída       | Fortran |                                           |                          |

|          |                             | Cobol   |                                           |                          |

|          |                             | PL1-APL |                                           |                          |

|          | Linguagem<br>interpretada   | Basic   | Intérprete                                |                          |

Em 2, os programas-fonte relativamente compridos são tratados, para não se tornarem fastidiosos, em linguagem mnemónica ou simbólica, em linguagem evoluída ou ainda em linguagem interpretada.

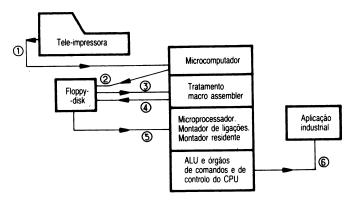

A máquina encarregue de definir o programa-objecto a partir do programa-fonte é designada, no caso de uma linguagem mnemónica, assembler, e o programa especial encarregue da tradução, programa assembler.

Quando a tradução em binário natural é executada directamente pelo computador ao qual é destinado o programa, o assembler é muitas vezes designado por assembler residente.

Quando a tradução em binário natural (código-máquina) é executada por um outro computador mais potente que aquele a que se destina o programa, é designado «cross-assembler».

O computador assim utilizado deve, neste caso, respeitar as regras de tradução aceites pelo computador destinatário.

Deve-se notar que existem *pseudo-instruções*, ou seja, *ordens* que não são directamente explorados pelo computador, mas que podem no entanto provocar uma sequência especial no assembler, destinada a operações de organização no computador, como por exemplo a reserva de zonas na memória, a definição de endereços, etc.

Finalmente, existe uma grande variedade de assemblers, como seja:

O macro assembler, no qual cada instrução da linguagem fonte define uma operação mais completa decomposta numa série de sequências de instruções.

O assembler translativo («relocatable assembler»), que trata os endereços relativos.

O assembler absoluto, encarregue de calcular os endereços absolutos ou directos das informações nas memórias.

Quando se trata de uma linguagem evoluída, a máquina encarregue de a traduzir é designada compilador. A tradução é então designada por compilação.

No nosso quadro citámos algumas linguagens evoluídas a título de exemplo. Vejamos a utilização específica de cada uma delas.

Linguagens de tipo universal: PL1 e APL

Linguagens de tipo científico: Algol e Fortran

Linguagens orientadas para a resolução de probemas de gestão: Cobol.

A linguagem mnemónica, tal como as codificações «octal», hexadecimal, BCD são linguagens elementares, por oposição à linguagem evoluída.

Assim, para efectuar uma operação simples, será necessária em linguagem mnemónica toda uma série de sequências de instruções que obrigam já a um conhecimento íntimo do funcionamento do computador, enquanto que no caso da linguagem evoluída bastará escrever o que se pretende utilizando os termos da linguagem em causa.

Um microcomputador equipado com um microprocessador só pode actualmente utilizar uma linguagem mnemónica.

No capítulo 3 dá-se um exemplo, sendo **FETCH** e **LOAD** exemplos de instruções simbólicas.

A linguagem empregue obriga a dispender mais tempo na programação do que no caso das linguagens evoluídas, mas necessita de menos espaço em memória.

Dever-se-á então economizar no tempo de programação e empregar uma linguagem evoluída?

Ou deve-se economizar nas dimensões das memórias e utilizar uma linguagem assembler?

É óbvio que o segundo caso se torna mais interessante na medida em que os microprocessadores tinham um baixo preço de custo e sejam aplicados em utilizações específicas que obrigam a empregar apenas um programa ou pequeno número deles que possam ser considerados simples.

A linguagem interpretada Basic traduz no intérprete as instruções do programa-fonte uma a uma, procedendo imediatamente à sua execução passo a passo.

O tempo de execução do programa é portanto obrigatoriamente maior do que no caso de uma linguagem assembler ou compilada.

Por outro lado, este método convém pefeitamente ao ensino da programação, pois é então possível obter resultados assim que se executa cada etapa de instrução.

### 5

# O CÁLCULO BINÁRIO AS CODIFICAÇÕES: OCTAL, HEXADECIMAL E BCD

Para efectuar as operações aritméticas, é indispensável definir em primeiro lugar a maneira de escrever os números qualquer que seja a base do sistema de numeração adoptado.

Ésta maneira de escrever os números resume-se numa fórmula que indicaremos depois de a ter demonstrado tomando como exemplo-um número do sistema de base 10 (sistema decimal).

Considere-se o número, com três algarismos, 825.

Pode ser escrito  $(8 \times 10^2) + (2 \times 10^1) + (5 \times 10^0)$ .

Ou seja, 800 + 20 + 5.

8 — algarismo das centenas

2 — algarismo das dezenas.

5 — algarismo das unidades.

Sendo a base de 10, a fórmula geral decomposta, é:

$$N = a \times 10^2 + b \times 10^1 + c \times 10^0$$

Substituindo agora os coeficientes a (das centenas), b (das dezenas) e c (das unidades) por um coeficiente geral  $\alpha$  dotado de um índice (n) que representa a ordem mais elevada no número, e a base 10 pela letra B, obtemos a seguinte fórmula genérica:

$N = \alpha_n B^{n-1} + \alpha_{n-1} B^{n-2} + \alpha_1 B^0$

Esta fórmula pode então ser aplicada a todos os números (N), qualquer que seja a base (B) do sistema de numeração escolhido.

Na prática de cálculo corrente, adoptou-se o sistema de-

cimal na maior parte dos países do mundo.

Em informática, por razões de comodidade de tradução do cálculo em sinais eléctricos trabalhando no sistema *tudo ou nada*, adoptou-se o sistema binário, que se exprime em *bits* (0 ou 1).

Como se utilizam muitas vezes, particularmente em microinformática, números com quatro algarismos binários, com oito algarismos binários (8 bits = 1 byte) até de 16 algarismos binários, servimo-nos dos sistemas:

- BCD (Binary Coded Decimal)

- Octal (de base 8)

- Hexadecimal (de base 16).

Os dois quadros seguintes mostram-nos a correspondência entre estes sistemas de numeração muito úteis em informática.

Observando estes dois quadros pode-se concluir:

- que é necessário um grupo de 3 bits para traduzir em binário todos os algarismos de um número (0 a 7) lido no sistema octal;

- que é necessário um grupo de 4 bits para descrever em binário todos os algarismos de um número (0 a F) lido no sistema hexadecimal. Neste sistema representam-se os valores decimais 10 a 15 pelas primeiras letras do alfabeto: A, B, C, D, E, F.

- Que é necessário um grupo de quatro bits para traduzir em binário cada ordem (unidades, dezenas, centenas, etc.) de um número codificado em BCD.

Daremos aliás um exemplo de codificação binária, octal e hexadecimal no final do capítulo.

Vejamos como se deve passar de um sistema para outro. Em primeiro lugar vejamos como se deve passar um número escrito no sistema binário para o número correspondente escrito no sistema decimal.

Para efectuar uma tal operação, basta recordar a fórmula precedente (N), que acabamos de desenvolver nestes quadros.

# Quadro das correspondências entre o sistema decimal e os sistemas octal, hexadecimal e binário natural

|                                                                                          |                                                                                                | Codificação octal                                                                          |                                                                            |                                                                                                  | Codificação hexadecimal            |                                                                                                              |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Valor Codificação<br>decimal binária                                                     | Valor<br>octal                                                                                 | Codificação em<br>grupo binário                                                            |                                                                            | Valor<br>hexadec.                                                                                | Codificação em<br>grupo<br>binário |                                                                                                              |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 0<br>1<br>10<br>11<br>100<br>101<br>110<br>111<br>1000<br>1001<br>1010<br>1101<br>1110<br>1111 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>20 | gr. 2<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>001<br>001<br>00 | gr. 1<br>000<br>001<br>010<br>101<br>110<br>111<br>000<br>001<br>010<br>011<br>100<br>111<br>110 | 01234567 89ABCDEF0                 | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1011<br>1100<br>1111<br>1110<br>1111 |

# Quadro da correspondência entre o sistema decimal e os sistemas binário natural e BCD

| Valor<br>decimal                                     | Codificação<br>binária natural                                         | Sistema BCD<br>Codificação em grupos binários                        |                                                                                                                       |  |

|------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                                                      |                                                                        | Dezenas                                                              | Unidades                                                                                                              |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | 0<br>1<br>10<br>11<br>100<br>101<br>110<br>111<br>1000<br>1001<br>1010 | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0001 | 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0<br>0 1 1 1<br>1 0 0 0<br>1 0 0 1<br>0 0 0 0 |  |

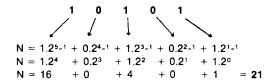

Considere-se por exemplo o número binário 10101, que deve ser escrito 10101<sub>2</sub> (número 10101 na base 2).

Desenvolve-se a fórmula (N) da seguinte maneira:

21 é portanto o número decimal correspondente ao número binário de 5 bits  $10101_2$ .

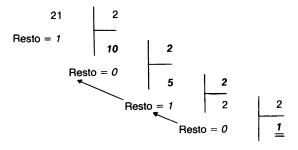

Consideremos agora a passagem de um número escrito no sistema decimal a um número correspondente escrito no sistema binário.

A conversão pode efectuar-se da seguinte maneira.

Conversão de um número: Sistema decimal/sistema binário

Para escrever o número  $21_{10}$  em sistema binário, sobe-se no sentido da seta considerando o último quociente (1) como unidade binária mais significativa do número que é em seguida constituído com os restos das sucessivas divisões.

Obtém-se portanto  $21_{10} = 10101_2$ .

Até agora discutimos apenas os números inteiros. Vejamos agora como se deve passar os números fraccionários de um sistema para outro.

A fórmula que permite definir a parte fraccionária de um número é:

$$N = \alpha_1 B^{-1} + \alpha_2 B^{-2} ... + \alpha_n B^{-n}$$

Recordemos que

$$B^{-1}$$

é a representação de  $\frac{1}{B^1}$   $B^{-2}$  é a representação de  $\frac{1}{B^2}$   $B^{-n}$  é a representação de  $\frac{1}{B^n}$

Vamos agora poder passar de um número escrito no sistema binário para o número correspondente do sistema decimal.

Suponhamos que se pretende converter  $0.101_2$  para o sistema decimal.

Segundo a fórmula teremos:

$$0,101 = 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$$

=  $1/2^{1} + 0 + 1/2^{3}$

=  $0,5 + 0 + 0,125$

=  $0,625_{10}$

Note-se que o número  $10101,101_2 = 21,625_{10}$

Para realizar a conversão inversa de decimal fraccionário para o sistema binário, efectuam-se as seguintes multiplicações sucessivas:

Pretende converter 0,625<sub>10</sub> em binários naturais.

$$0,625 \times 2 = 1,250 \longrightarrow \text{obt\'em-se } 1 \longrightarrow \text{resto } 0,250$$

$$0,250 \times 2 = 0,500 \longrightarrow \text{obtém-se } 0 \longrightarrow \text{resto } 0,500$$

$$0.500 \times 2 = 1.000 \longrightarrow \text{obtém-se } 1 \longrightarrow \text{resto } 0$$

Os resultados sucessivos, considerando como valor mais à esquerda do número o resultado da primeira multiplicação efectuada, constituem o número fraccionário procurado.

Neste caso,

$$0.625_{10} = 0.101_2$$

Um número algébrico pode ser negativo ou positivo. O seu valor absoluto, em números binários, deve portanto ser precedido de um BIT de sinal. Existem várias ma-

neiras de codificar um sinal.

Normalmente emprega-se um 0 para indicar o sinal + e um 1 para indicar o sinal -.

Vamos agora passar em revista a maneira como se deve actuar para realizar as quatro operações principais no sistema binário.

#### 1. A ADIÇÃO

O processo de adição binária baseia-se nas regras seguintes:

$$\begin{array}{l} 0+0=0\\ 0+1=1\\ 1+0=1\\ 1+1=0,\ e\ vai\ 1.\\ \text{Exemplo:} & 1101_2\\ & & 10010_2 \end{array}$$

No nosso exemplo adicionámos dois números de 4 bits.

O resultado surge sob a forma de um número de 5 bits.

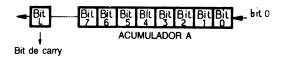

Se o tratamento é realizado com palavras de 4 bits, existe aqui um quinto (correspondente ao «e vai um») que pode normalmente ser registado pelo computador num flip-flop especial, previsto para este efeito, designado pelos americanos de *carry* ou *link*.

# 2. A SUBTRACÇÃO

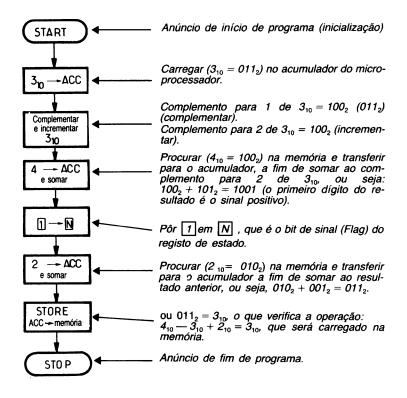

Existem várias maneiras de a efectuar. Estudaremos aqui a que nos parece mais normal em informática e que consiste em trabalhar por complementaridade.

Deve-se somar ao primeiro número binário dado o complemento para 2, designado por *complemento verdadeiro*, do segundo número a subtrair.

O complemento para 2 de um número obtém-se acrescentando  $1_2$  ao complemento para 1 ou complemento restrito desse número.

O complemento para 1 de um número obtém-se transformando todos os zeros em uns e os uns em zeros no número dado.

Assim, pretende-se subtrair  $0101_2$  de  $1010_2$ . O complemento de  $0101_2$  para 1 é  $1010_2$ .

- O complemento para 2 de 0101<sub>2</sub> é 1011<sub>2</sub>.

- O resultado da subtracção é portanto.

$$\begin{array}{r}

1010_2 \\

+ 1011_2 \\

= 10101_2

\end{array}$$

Elimina-se agora o último algarismo da esquerda do resultado desta operação, que no caso considerado é 1. O resultado da subtracção binária é  $0101_2$ , o que se pode verificar fazendo as contas em decimal:

Quando o algarismo da esquerda retirado no cálculo em binário é 1, como acontece neste caso, o resultado da subtracção é um número de sinal positivo.

Se nao existe este algarismo à esquerda do número, ou seja, quando existe um zero, o resultado é um número de sinal negativo.

# 3. A MULTIPLICAÇÃO

Estudaremos duas maneiras simples de proceder:

a) A multiplicação por adições sucessivas.

Considere-se  $12 \times 3$ , na base 10, que em binário será  $1100 \times 0011$ :

$$\begin{array}{r}

1100 \\

+ 1100 \\

+ 1100 \\

\hline

100100$$

Adicionam-se três vezes o multiplicando, isto é, efectua-se uma soma contendo o multiplicando tantas vezes quanto o número de unidades existentes no multiplicador.

b) A multiplicação por deslocamento e soma.

Executa-se a multiplicação binária da mesma maneira que se procederia no caso de uma multiplicação decimal.

Exemplo:

$$\begin{array}{r}

1100 \\

\times 11 \\

\hline

1100 \\

1100

\end{array}$$

$$= 100100_{2}$$

#### 4. A DIVISÃO

A divisão é efectuada da mesma maneira que a divisão decimal:

$$\begin{array}{c|c}

100100 \\

-00 \downarrow \\

100 \\

-11 \\

0011 \\

-11 \\

0000

\end{array}$$

$$\begin{array}{c|c}

11 \\

01100 \\

-11 \\

0000

\end{array}$$

Acabamos de efectuar as quatro operações aritméticas essenciais em «sistema binário natural». É a única codificação ou *programa-objecto* ou ainda *código-máquina* que o computador ou o microcomputador conhece.

O programador pode por outro lado escrever um programa-fonte mais simples em código octal ou código hexadecimal. Damos em seguida um exemplo:

A instrução «CLEAR 64» dada ao minicomputador «PDP11» leva a zero todo o conteúdo da posição de endereço 64.

Esta instrução é codificada em duas palavras de 16 bits da seguinte maneira (em binário natural):

Em codificação **octal**, traduzir-se-á cada grupo de 3 bits a partir da direita, o que dará:

Em código **hexadecimal**, traduzir-se-á cada grupo de 4 bits a partir da direita, o que dará:

| CLEAR | $\underbrace{0000}$ | 1010                | $\underbrace{0001}$    | 1111                                       |

|-------|---------------------|---------------------|------------------------|--------------------------------------------|

|       | 0                   | Α                   | 1                      | $\mathbf{F} = 0\mathbf{A}1\mathbf{F}_{16}$ |

| 64    | $\underbrace{0000}$ | $\underbrace{0000}$ | $\underbrace{0100}_{}$ | 0000                                       |

|       | 0                   | 0                   | 4                      | $0 = 0040_{16}$                            |

O comprimento de palavra que pode ser tratado num computador pode por vezes ser insuficiente para o rigor pretendido.

Quando se ultrapassa o número de bits de precisão simples, dispõe-se do recurso a uma segunda palavra para tratar a mesma informação. Empregam-se duas palavras para a informação, ao que corresponde à precisão dupla, por oposição à precisão simples utilizado quando cada informação é contida numa única palavra.

Quando se diz que um microprocessador é de 8 bits, isto significa que ele recebe simultaneamente, ou seja em paralelo, nas suas 8 entradas, os 8 bits de cada palavra que compõe um programa-objecto. Neste caso cada palavra pode portanto ter  $2^8 = 256$  combinações possíveis de uns e de zeros, o que imediatamente nos dá uma ideia da precisão ou riqueza da linguagem deste computador.

Finalmente, para terminar este capítulo dedicado ao cálculo no sistema binário, consideremos um número binário qualquer e procuremos traduzi-lo nos diferentes sistemas que acabamos de estudar. O futuro programador pode encarar este divertimento como um exercício.

Considere-se o número binário de 8 bits  $10010111_2$ . Se se trata de um *número binário natural*; equivale a  $151_{10}$ .

Se se trata de um número com sinal (complemento para 1), é igual a  $-104_{10}$ .

Se se trata de um número com sinal (complemento para 2), é igual a  $-105_{10}$ .

Se se trata de um número BCD (2 grupos de 4 bits), é igual a 97<sub>10</sub>.

Se se trata de um *número octal* (por grupos de 3 bits), é igual 227<sub>8</sub>.

Se se trata de um *número hexadecimal* (por grupos de 4 bits), é igual a 97<sub>16</sub>.

Finalmente, nada impede que este número binário com 8 bits seja a tradução de uma instrução de um programa-fonte codificado em linguagem mnemónica e simbólica.

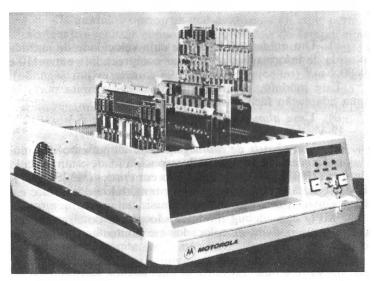

Exemplo: Este número binário corresponde no microprocessador MC6800 da Motorola à instrução em linguagem mnemónica:

#### STAA,

que significa guardar no acumulador A. O termo acumulador será objecto de uma explicação no capítulo consagrado ao microprocessador.

# 6 AS FUNÇÕES LÓGICAS

O jogo de instruções de um microprocessador comporta geralmente, a fim de resolver os problemas que lhe são postos, instruções de funções lógicas.

Muitas vezes trata-se de simples operadores, como as portas E, OU inclusivo ou exclusivo, NAND, NOR, etc.

Além disso, é interessante ter uma ideia sobre a própria concepção dos circuitos de *memorização*, como as *básculas bi-estáveis* e os *registos* que participam na organização de um computador ou um microcomputador e estruturam em parte o seu *processador* ou *microprocessador*.

É por esta razão que iremos consagrar este capítulo aos circuitos lógicos e às respectivas funções.

Os circuitos lógicos necessários às funções correspondentes comportam bornes de entrada e de saída.

O técnico aplica tensões aos bornes de entrada e obtém outras nos bornes de saída, que são função das combinações das tensões aplicadas e dos circuitos empregues.

Todas estas tensões podem apenas tomar dois valores bem definidos.

- 1. O nível alto símbolo H, correspondente à maior tensão.

- 2. O nível baixo símbolo B, correspondente à tensão mais fraca.

Entre estes dois níveis, o técnico despreza as variações físicas das tensões.

No seu raciocínio, o técnico apoia-se em duas convenções simbólicas opostas:

# 1.ª CONVENÇÃO LÓGICA

Trata-se da lógica positiva.

Uma afirmação traduz-se pelo «1» do sistema binário, e define a presença do nível «H».

Uma negação traduz-se pelo «0» do sistema binário e define a presença do nível «B».

# 2.ª CONVENÇÃO LÓGICA

Trata-se da lógica negativa.

Uma afirmação traduz-se pelo «0» do sistema binário e define a presença do nível «H».

Uma negação traduz-se pelo «l» do sistema binário e de-

fine a presença do nível lógico «B».

Por razões mnemónicas bem evidentes, é hoje habitual raciocinar de preferência em «lógica positiva».

A fim de ilustrar as nossas afirmações, tomemos a título de exemplo a função lógica NÃO (normalmente designada pela palavra inglesa **NOT**).

É definida de tal modo que, ao aplicar-se à entrada um sinal H, se obtém na saída um sinal B, ou quando aplicando à entrada um sinal B se obtém na saída um nível H.

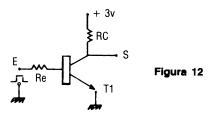

A fim de obter este resultado, imaginemos (figura 12) um transístor que fazemos trabalhar alternadamente em regime saturado e em regime bloqueado. Este transístor é montado de acordo com esta figura tendo ligada em série à sua alimentação de colector uma resistência «Rc». Por outro lado, «Re» impede que a junção emissor-base fique em curto-circuito.

1. Aplica-se um impulso positivo de + 3 V em (E). Este impulso em (E) corresponde ao nível H, igual a 1 em lógica positiva.

O transístor (T1) está saturado. No terminal S do circuito obtém-se uma tensão de + 0,3 V, igual à tensão de saturação de T1. Esta tensão de + 0,3 V relativamente à massa determina o nível B, igual ao «O» em lógica positiva.

2. Aplica-se agora uma tensão nula em «Ē», ou seja a tensão da massa de referência. Esta representa o nível B, correspondente ao valor lógico 0 no caso da lógica posisitva.

O transístor T1 fica bloqueado. No terminal S obtém-se uma tensão de + 3 V igual à tensão de alimentação do transístor. Esta tensão representa o nível H, correspondente ao nível lógico 1 no caso da lógica positiva.

Poderíamos raciocinar da mesma maneira no caso da lógica negativa, mas os uns e os zeros lógicos seriam invertidos, ou seja, a cada nível H corresponderia um 0 lógico e a cada nível B corresponderia o 1 lógico.

O fabricante tem o hábito de resumir as características de níveis lógicos dos seus circuitos naquilo que se designa por *Tabelas de verdade*. A título de exemplo, apresentamos na figura 13 a tabela de verdade da função NOT.

| Níveis     |   | Tabela de verdade |   |                 |   |

|------------|---|-------------------|---|-----------------|---|

| eléctricos |   | Lógica positiva   |   | Lógica negativa |   |

| E          | S | E S               |   | Е               | S |

| Н          | В | 1                 | 0 | 0               | 1 |

| В          | н | 0                 | 1 | 1               | 0 |

Figura 13 — Tabela de verdade da função NOT

Existem dois grandes tipos de funções lógicas:

1. A classe das funções lógicas combinatórias. Nesta classe, o sinal recolhido no borne «S» de um circuito só depende exclusivamente da combinação dos sinais aplicados no mesmo instante nos bornes de entrada (E) deste circuito.

Veremos que a álgebra de Boole é particularmente cómoda para todos os circuitos de lógica combinatória.

2. A classe das funções lógicas sequenciais.

O sinal recolhido no borne S de um circuito já não depende exclusivamente da combinação de sinais aplicada no mesmo instante aos bornes de entrada E, mas também do estado anterior em que o circuito se encontrava quando estes sinais foram aplicados.

Trata-se portanto de funções que possuem uma qualidade de *memorização* dos estados anteriores no instante considerado.

Têm em conta a sequência completa dos dados anteriores.

A álgebra de Boole já não é então utilizável, raciocinando-se a partir de diagramas de tempo, de tabelas de verdade ou ainda de tabelas de fases, cujas colunas permitem distinguir os níveis nos bornes de saída antes do instante em que são aplicados os sinais de entrada.

# AS FUNÇÕES LÓGICAS COMBINATÓRIAS

Estas funções podem ser divididas em três grandes categorias hierarquizadas segundo o respectivo grau de complexidade.

| A — As funções elementares:                    | NOT (NÃO)<br>OR (OU)<br>AND (E)                      |

|------------------------------------------------|------------------------------------------------------|

| B — As funções de funções<br>de primeiro grau: | NOR (NOT-OR)<br>NAND (NOT-AND)                       |

| C — As funções de funções<br>complexas         | OR exclusivo AND-OR-NOT Circuitos de soma e de CARRY |

#### AS FUNÇÕES LÓGICAS SEQUENCIAIS

Estas funções podem ser divididas em duas grandes ca-

tegorias hierarquizadas conforme o respectivo grau de complexidade.

| A — As básculas bi-estáveis,<br>elementos simples de<br>memorização com duas<br>portas estáveis. | Básculas simples — <i>tipo</i> <b>RS</b> Básculas sincronizáveis: R <sub>T</sub> S <sub>T</sub> e J <sub>T</sub> K <sub>T</sub> D <sub>T</sub> e <b>Master</b> — <b>Slave</b> |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| B — Os circuitos sequenciais                                                                     | Registos<br>Contadores de impulsos<br>e divisores de frequência                                                                                                               |  |  |

Iremos examinar primeiramente as funções elementares da lógica combinatória.

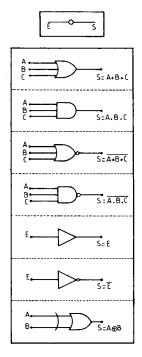

Figura 14 — Portas que realizam as funções (de cima para baixo) NOT, OR, AND, NOR, NAND, «BUFFER», «BUFFER-INVERSOR», OR Exclusivo:

#### 1. FUNÇÃO NOT

Já demos a definição anteriormente. Esta função é também designada por função complementar ou função inversa.

Em álgebra booleana a função escrever-se-á

$$S = \bar{E}$$

,

pronunciando-se S = E barra, ou ainda S = E complementado.

A figura 14 representa o simbolismo esquemático utilizado para esta função (em cima).

# 2. FUNÇÃO OR

O circuito utilizado inclui vários terminais de entrada A, B, C, etc., e um único terminal de saída S.

Em lógica positiva, uma afirmação na saída (1 lógico) significa que vai aplicado um sinal de lógica 1 em qualquer dos terminais de entrada do circuito.

Em álgebra booleana, a equação da função OR escreve-se:

$$S = A + B + C$$

e lê-se

$$S = A ou B ou C$$

O sinal + indica o termo ou (em inglês, or). Esta operação é chamada soma lógica.

Na figura 14 representa-se o símbolo esquemático empregue para designar esta função.

No caso presente, representámos um «operador» ou «porta» de três entradas, cuja tabela de verdade indicamos na figura 15.

| Função OR |   |   |   |  |  |

|-----------|---|---|---|--|--|

| Α         | В | C | S |  |  |

| 1         | 1 | 1 | 1 |  |  |

| 1         | 1 | 0 | 1 |  |  |

| 1         | 0 | 1 | 1 |  |  |

| 0         | 1 | 1 | 1 |  |  |

| 1         | 0 | 0 | 1 |  |  |

| 0         | 1 | 0 | 1 |  |  |

| 0         | 0 | 1 | 1 |  |  |

| 0         | 0 | 0 | 0 |  |  |

Figura 15 — Tabela de verdade da função OR executada por uma porta com três entradas.

# 3. FUNÇÃO AND

O circuito utilizado inclui diversos terminais de entrada A, B, C, etc., e uma única saída S.

Em lógica positiva só será recolhida uma afirmação na saída (1 lógico), quando todos os terminais de entrada se encontram a esse nível lógico.

Em álgebra booleana, a equação da função AND é escrita do seguinte modo:

$$S = A \times B \times C$$

e lê-se

$$S = A e B e C$$

O sinal  $\times$  indica o termo e (and). Esta operação é designada por produto lógico.

Na figura 14 representa-se o símbolo esquemático usado para definir a função AND.

Neste caso considerámos uma porta AND de três entradas, e damos na figura 16 a tabela de verdade desta função.

| Função AND |   |   |   |  |  |

|------------|---|---|---|--|--|

| А          | В | C | S |  |  |

| 1          | 1 | 1 | 1 |  |  |

| 1          | 1 | 0 | 0 |  |  |

| 1          | 0 | 1 | 0 |  |  |

| 0          | 1 | 1 | 0 |  |  |

| 1          | 0 | 0 | 0 |  |  |

| 0          | 1 | 0 | 0 |  |  |

| 0          | 0 | 1 | 0 |  |  |

| 0          | 0 | 0 | 0 |  |  |

Figura 16 — Tabela de verdade da função AND no caso de uma porta com três entradas.

Examinemos seguidamente «as funções de funções de primeiro grau» da lógica combinatória.

# 1. Função NOR (NOT-OR)

# 2. Função NAND (NOT-AND)

Os circuitos utilizados têm uma implantação dos terminais de entrada e de saída igual à dos circuitos usados nas funções OR e AND.

As suas tabelas de verdade são obtidas a partir das fornecidas para as funções OR e AND, por um lado, e da correspondente à função NOT, por outro.

Dizendo por outras palavras, basta substituir nas tabelas de verdade das funções OR e AND todos os valores da coluna S pelos seus valores complementares, ou seja, substituir os uns por zeros e os zeros por uns.

Em álgebra booleana a equação da função NOR é escrita do seguinte modo:

$$S = \overline{A} + \overline{B} + \overline{C}$$

e lê-se:

$$Sx = \overline{A}$$

ou  $\overline{B}$  ou  $\overline{C}$

Do mesmo modo, a equação da função NAND escreve-se:

$$S = \overline{A} \times \overline{B} = \overline{C}$$

e lê-se:

$$S = \overline{A} e \overline{B} e \overline{C}$$

Na figura 14 representa-se o símbolo esquemático utilizado para definir uma destas funções.

Estes símbolos esquemáticos recordam portanto, como se pode observar, a sequência das duas operações (OR seguida de NOT e AND seguida de NOT).

Poder-se-ia ainda citar além das funções elementares e das funções de funções elementares, os circuitos encarregues apenas de amplificar os sinais utilizados para as comunicações em linhas que apresentam perdas fortes. Estes circuitos são designados por circuitos BUFFER (no caso dos amplificadores simples) ou ainda circuitos BUFFER-INVERSOR no caso dos amplificadores inversores de sinais.

Na figura 14 indica-se uma vez mais o símbolo utilizado para representar cada uma destas funções.

Finalmente, para terminar este pequeno curso sobre

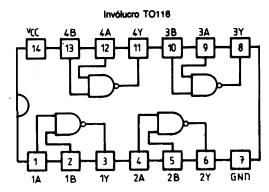

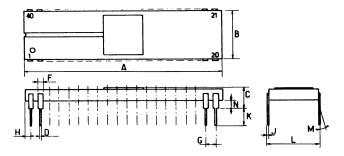

funções elementares e funções de funções do primeiro grau, daremos na figura 17 o esquema de uma realização prática. Trata-se de um circuito lógico integrado da família TTL 74 (tecnologia bipolar: lógica completamente transistorizada) designado por 7400, que compreende uma porta NAND quádrupla de duas entradas montada numa cápsula DIL (Dual in Line) cujas ligações são em número de 14 e se encontram dispostas em duas fiadas paralelas (daí o nome Dual-in-line). A cápsula é em plástico e tem a referência normalizada TO116.

Figura 17 — Circuito TO116

Examinemos, para terminar este estudo sobre as funções da lógica combinatória, as funções de funções complexas.

# 1. FUNÇÃO OR EXCLUSIVO

A função OR, que já estudámos, é também designada por função OR inclusivo, o que significa que numa porta com duas entradas A e B a saída tem o valor 1 se ambas as entradas, ou pelo menos uma delas, apresentarem o valor 1.

Na função OR exclusivo, a saída encontra-se ao nível lógico 1 se pelo menos uma das entradas se encontra a esse nível, mas passa ao nível lógico 0 se for aplicado a todas as entradas o valor lógico 1.

Na figura 18 podemos observar a tabela de verdade da função OR exclusivo.

| Função OR exclusivo |   |   |  |  |  |

|---------------------|---|---|--|--|--|

| Α                   | В | S |  |  |  |

| 1                   | 1 | 0 |  |  |  |

| 0                   | 1 | 1 |  |  |  |

| 1                   | 0 | 1 |  |  |  |

| 0                   | 0 | 0 |  |  |  |

Figura 18 — Função OR exclusivo no caso de uma porta com apenas duas entradas.

Lendo esta tabela verificamos que quando

$$S = 1$$

.

teremos

A≠B:

quando

S = O

teremos

A = B.

Imagina-se já «uma primeira aplicação» da função «Or exclusivo». Esta função pode servir para comparar sinais lógicos.

O operador OR exclusivo permite verificar os **estados** de coincidência ou **não** coincidência dos sinais lógicos.

Uma segunda aplicação que iremos descrever adiante é a de elemento constitutivo na concepção de um somador binário.

Na figura 14 representa-se uma vez mais de maneira simbólica o esquema de um circuito OR exclusivo.

A função escreve-se:

$$S = A \oplus B$$

e lê-se

S = A ou B exclusivo.

O sinal + rodeado por um círculo indica a função escrita OR exclusivo. Em álgebra booleana demonstra-se que:

$$S = A \oplus B = A \times B + B \times A$$

# 2. FUNÇÃO AND-OR-NOT

Esta função de funções é geralmente obtida utilizando um circuito constituído pela combinação de operadores AND, OR e NOT.

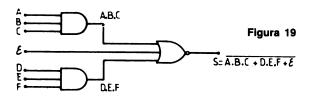

A título de exemplo, apresentamos na figura 19 um esquema possível de realização desta função.

# 3. FUNÇÃO DE SOMA BINÁRIA E «CARRY»

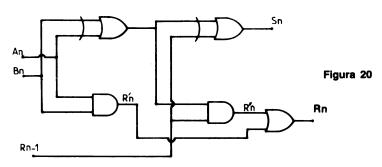

Trata-se neste caso de uma verdadeira lógica por ligações, incluindo dois circuitos semi-somadores formados por um operador OR exclusivo e uma porta AND. Não daremos aqui nenhuma explicação sobre o funcionamento deste circuito, pois essa explicação ultrapassa o âmbito da nossa exposição. Digamos apenas que é necessário somar um número binário  $A_n$  a outro número  $B_n$  (ver a figura 20).

A adição aos números precedentes  $A_{n-1}$  e  $B_{n-1}$  deu lugar a uma quantidade de ordem superior ao primeiro algarismo da esquerda (do tipo «e vai um»),  $R_{n-1}$ , que deve ser igualmente adicionada a  $A_n + B_n$ . O resultado da adição é  $S_n$ , e pode incluir igualmente um algarismo de ordem superior  $R_n$ .

Iremos abordar agora as funções lógicas sequenciais. Estudaremos apenas as básculas ou flip-flops e os registos, a fim de adquirirmos uma ideia elementar da estrutura das memórias.

Começaremos esta exposição pelas básculas bi-estáveis. Examinemos sucessivamente as básculas simples **RS** e em seguida as básculas sincronizáveis:  $\mathbf{R}_{\mathsf{T}}\mathbf{S}_{\mathsf{T}} - \mathbf{J}_{\mathsf{T}}\mathbf{K}_{\mathsf{T}} - \mathbf{D}_{\mathsf{T}}$  e as do tipo piloto-pilotada (master-slave).

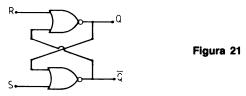

#### 1. BÁSCULAS «RS»

As mais simples são constituídas por duas portas NOR e NAND (ver a figura 21).

| N.º<br>de<br>estados | R             | s           | œ      | ā      | Observações sobre as<br>saídas                                               | Esquema<br>simbólico |

|----------------------|---------------|-------------|--------|--------|------------------------------------------------------------------------------|----------------------|

| 1 2                  | ℋ<br>ℬ        | ŀ           |        |        | Estado indeterminado     se o estado anterior     era 2                      | Ro——oQ               |

| 3 4                  | £<br>€<br>€   | Æ<br>ℋ<br>ℬ | B<br>H | H<br>B | Estado determinado<br>mas sem variação se o<br>estado anterior<br>era 3 ou 4 | 5 <b>0</b> ——        |

| 3 4                  | <i>B</i><br>H | Ж<br>ЯВ     | H<br>B | B<br>K |                                                                              | Ro                   |

|                      |               |             |        |        |                                                                              | 50-400               |

Figura 22

Estas básculas, também designadas por flip-flop, são do tipo RS (Reset e Set — remarcar e marcar). A sua representação simbólica é semelhante a um rectângulo como se indica na figura 22, na qual é igualmente incluída a respectiva tabela de verdade.

Uma báscula encontra-se no estado 1 ou estado activo quando

Q = 1 (nível H em lógica positiva)

Encontra-se no estado 0 ou estado inactivo quando

Q = 0 (nível B em lógica positiva)  $\overline{Q} = 1$

# 2. BÁSCULAS SINCRONIZÁVEIS

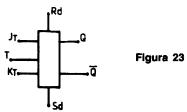

Primeiramente consideramos as básculas R<sub>T</sub>S<sub>T</sub> e J<sub>T</sub>K<sub>T</sub> A figura 23 fornece as respectivas representações simbólicas.

$J_T$  e  $K_T$  (ou  $R_T$  e  $S_T$ ) são os terminais de entrada em que se aplicam os estados lógicos que devem definir o estado futuro da báscula.

T ou  $C_n$  é o terminal onde se aplica o sinal de sincronização qué dá a ordem decisiva de mudança de estado. Este sinal é designado por sinal de relógio. T significa trigger e C, clock pulse.

Q e Q são os terminais de saída. Os níveis obtidos em

Q e Q são portanto sempre complementares.

$R_d$  e  $S_d$  são terminais que servem para impor o estado da báscula instantaneamente e independentemente de T.

Para estabelecer a tabela de fases que indica o funcionamento de uma báscula sincronizável, quer seja a R<sub>T</sub>S<sub>T</sub> ou a J<sub>T</sub>K<sub>T</sub>, é necessário considerar o tempo t<sub>n</sub> após a aplicação da última ordem de mudança de estado e o tempo t<sub>n+1</sub> depois da execução desta ordem.

| Tipo de básculas                         | RT <sub>tn</sub> | ST <sub>tn</sub> | <b>Q</b> <sub>tn + 1</sub>          | $\overline{Q}_{tn+1}$                        |

|------------------------------------------|------------------|------------------|-------------------------------------|----------------------------------------------|

| Báscula<br>R <sub>T</sub> S <sub>T</sub> | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 | Estados inde $1 \\ 0 \\ Q_{tn}$     | terminados $0 \ 1 \ \overline{Q}_{tn}$       |

| Báscula<br>J <sub>T</sub> K <sub>T</sub> | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 | Q <sub>tn</sub> 1 0 Q <sub>tn</sub> | Q <sub>tn</sub><br>0<br>1<br>Q <sub>tn</sub> |

Figura 24 — Tabela de fases das básculas  $R_TS_T$  e  $J_TK_T$

Observando as tabelas de fase S (figura 24), verificamos que a diferença entre as básculas  $R_TS_T$  e  $J_TK_T$  reside no facto de a indeterminação dos estados de saída ser eliminada na báscula  $J_TK_T$  quando se aplicam às duas entradas dois níveis 1 em lógica positiva. Além disto, constata-se neste caso uma mudança dos níveis das saídas nas báscula  $J_TK_T$ . Não há mudança de estado no caso de entradas ao nível lógico 0, em qualquer dos dois tipos de básculas.

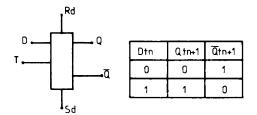

Examinemos em seguida as básculas do tipo D<sub>T</sub>.

Trata-se de uma báscula sincronizável simplificada, pois possui apenas uma entrada.

Figura 25 — À direita, a tabela de fases da báscula D<sub>T</sub>.

Representamos na figura 25 o esquema simbólico desta báscula e a sua tabela de fases.

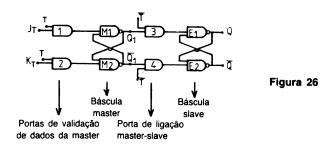

Vejamos finalmente a báscula do tipo master-slave.

O esquema da figura 26 mostra-nos a configuração sofisticada deste tipo de báscula.

- Os circuitos M<sub>1</sub> e M<sub>2</sub> definem a báscula «master».

- Os circuitos E<sub>1</sub> e E<sub>2</sub> definem a báscula «slave».

- As portas 1, 2, 3 e 4 são consideradas abertas quando transmitem à saída a informação presente nas respectivas entradas. No caso contrário, são consideradas fechadas.

Se T=B e  $\overline{T}=H$ , as portas 3 e 4 encontram-se abertas. A báscula master impõe então os níveis  $Q_1$  e  $Q_1$  à báscula slave.

As portas 1 e 2 encontram-se então fechadas. A báscula master encontra-se *bloqueada* e não recebe as instruções dadas em  $J_T$  e  $K_T$ .

Se T = H e  $\overline{T} = B$ , as portas 3 e 4 encontram-se fechadas. A báscula slave fica isolada da master, mantendo-se no estado que lhe foi anteriormente imposto por esta.

As portas  $\hat{1}$  e 2 encontram-se abertas. As informações existentes em  $J_T$  e  $K_T$  impõem à báscula master o seu novo estado.

Depois de examinar as básculas simples RS e as básculas sincronizáveis iremos abordar o estudo dos registos que fazem parte do conjunto de circuitos sequenciais de funções elaboradas.

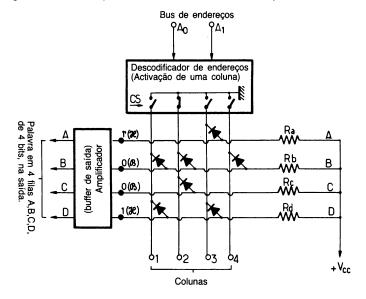

Os registos são órgãos de memória que podem ser divididos em 3 partes distintas:

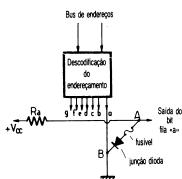

- a) Os órgãos de entrada, validados através de uma ordem de inscrição (ou de escrita). A validação (por exemplo um 1 lógico) autoriza a escrita de uma informação na memória.

- b) Os órgãos de memorização. Cada báscula pode por exemplo conservar um bit (mantém-se num dado estado num determinado momento).

- c) Os órgãos de saída, validados graças a uma ordem de leitura. A validação (por exemplo um 1 lógico) autoriza a leitura de uma informação armazenada em cada báscula correspondente da memória.

Podem distinguir-se, conforme a respectiva estrutura de ligações, quatro tipos de registos.

- a) Os registos de escrita e de leitura dos bits em paralelo.

- b) Os registos de escrita e leitura dos bits em série.

- c) Os registos de escrita dos bits em série e de leitura em paralelo.

- d) Os registos de escrita dos bits em paralelo e de leitura em série.

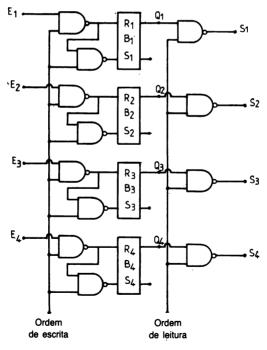

A título de exemplo para compreender melhor o que acabamos de dizer sobre os registos, damos nas figuras 27 e 28 dois esquemas de realizações simples de registos de diferentes estruturas de ligações.

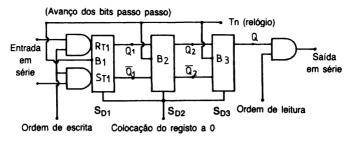

# 1. ESQUEMA DE UM REGISTO DE ESCRITA E LEI-TURA DOS BITS EM SÉRIE (ver figura 27)

Neste registo as básculas  $B_1$ ,  $B_2$ , e  $B_3$  encontram-se ligadas em série. Em qualquer momento podem-se colocar as básculas ao nível 0 antes de proceder a uma nova *inscrição* utilizando uma *ordem de passagem do registo para 0*, que é aplicada nos terminais  $S_{D1}$ ,  $S_{D2}$  e  $S_{D3}$  de cada uma das básculas do registo.

Na entrada em série envia-se então o 1.º bit de informação, assim como a ordem de escrita. Esta é imposta à báscula  $B_1$  no momento do disparo do sinal de relógio  $T_n$ .

No momento  $T_{n+1}$ , o bit é *enviado* para a báscula  $B_2$  e se for dada nova ordem de escrita pode-se igualmente enviar

Figura 27 — Registo de escrita e leitura dos bits em série

Figura 28 -- Registo de escrita e leitura dos bits em paralelo

para  $B_1$  um 2.º bit de informação. No momento  $T_{n+2}$  desloca-se novamente o registo.

- O 1.º bit é então armazenado em B<sub>3</sub> (MSB)

- O 2.° bit passa para B<sub>2</sub> e em B<sub>1</sub> surge o 3.° bit (LSB)

Graças a este deslocamento dos bits um a um consegue-se formar uma palavra de 3 bits.

Se se dá então ao registo uma ordem de leitura, poder-se-á ler igualmente na saída, sucessivamente, a série dos 3 bits desta palavra, nos momentos  $T_{n+3}$ ,  $T_{n+4}$  e  $T_{n+5}$ , sendo esta leitura assegurada pelos disparos sucessivos dos sinais de relógio.

## 2. ESQUEMA DE UM REGISTO DE ESCRITA E LEI-TURA DOS BITS EM PARALELO (ver a figura 28)

Trata-se neste caso de um registo-memória para palavras de 4 bits de escrita e leitura paralela. A ordem de escrita e a ordem de leitura actuam portanto simultaneamente sobre os quatro bits que compõem cada palavra desta memória.

É fácil compreender que um registo de memória é lido ou escrito mais rapidamente quando os bits que compõem as palavras têm um acesso em paralelo, sendo então escritos ou lidos todos os bits simultaneamente, ou seja, num mesmo momento t<sub>n</sub>.

Examinámos assim os principais registos dos circuitos sequenciais de funções elaboradas. Citámos entre estas funções elaboradas circuitos diferentes dos registos, mas não os estudaremos aqui pois não é necessário conhecê-los no nosso curso de iniciação sobre microcomputadores. Foram aliás editadas muitas obras sobre este assunto, e convidamos os leitores curiosos a consultarem-nas.

#### A TECNOLOGIA DOS MICROPROCESSADORES

Como já vimos, o microprocessador pôde nascer graças ao desenvolvimento das tecnologias de difusão aplicadas aos circuitos integrados **LSI** (Large scale integration).

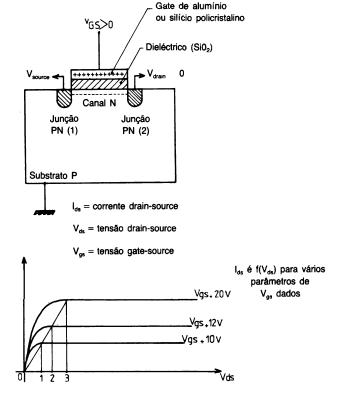

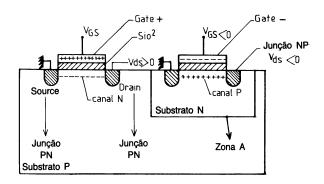

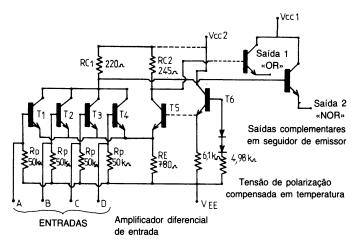

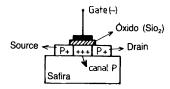

As tecnologias melhor adaptadas a estes tipos de circuitos são sem dúvida alguma as tecnologias MOS (N-MOS ou P-MOS) e C-MOS.

Contam-se actualmente no mercado mais de 25 microprocessadores utilizando estes métodos de fabrico.

Estas tecnologias permitem a qualquer microprocessador executar somas em tempos da ordem de um a dois microsegundos.