# A Z-80 Workshop Manual

E.A. PARR

# A Z-80 WORKSHOP MANUAL

by E. A. PARR B.Sc., C.Eng., M.I.E.E.

BERNARD BABANI (publishing) LTD

THE GRAMPIANS

SHEPHERDS BUSH ROAD

LONDON W6 7NF

ENGLAND

#### PLEASE NOTE

Although every care has been taken with the production of this book to ensure that any projects, designs, modifications and/or programs etc. contained herein, operate in a correct and safe manner and also that any components specified are normally available in Great Britain, the Publishers do not accept responsibility in any way for the failure, including fault in design, of any project, design, modification or program to work correctly or to cause damage to any other equipment that it may be connected to or used in conjunction with, or in respect of any other damage or injury that may be so caused, nor do the Publishers accept responsibility in any way for the failure to obtain specified components.

Notice is also given that if equipment that is still under warranty is modified in any way or used or connected with home-built equipment

then that warranty may be void.

#### © 1983 BERNARD BABANI (publishing) LTD

First Published – July 1983 Reprinted – July 1986 Reprinted – October 1989

## **British Library Cataloguing in Publication Data**

Parr, E. A.

A Z-80 workshop manual. - (BP112)

1. INTEL Z-80 (Computer)

I. Title 001.64'04

QA76.8.I/

ISBN 0 85934 087 2

#### INTRODUCTION

Although there are many contenders for the title of "most successful micro", the Z-80 has been universally acclaimed as the most powerful and versatile 8 bit microprocessor. It is found in many popular microcomputers, including the Nascom, TRS-80, ZX-80/81, Spectrum, Video Genie, Sharp MZ-80K and Cromenco machines.

This book has been written for owners of Z-80 based machines who have become reasonably proficient in BASIC, and wish to progress to machine code and assembler language programming. This can be a rather daunting task, as most Z-80 literature has been designed for computer professionals and is not readily understandable.

The book has also been designed to be a general introduction to machine code programming. All the popular microprocessors such as the 6502, 6800 etc. use similar techniques to the Z-80. Once the Z-80 has been mastered, the reader will have little problem with its simpler cousins. It is therefore hoped that the book will also prove useful to anyone who is simply interested in computing.

#### **ACKNOWLEDGEMENTS**

This book is about the Zilog Z-80 microprocessor, and contains all the detail necessary for the average enthusiast to gain insight into any Z-80 based microcomputer. It follows that much of the information given has been obtained from Zilog, and their assistance is greatly appreciated.

It should be noted that Zilog, Z-80 and the various microcomputers and assembler/monitor names referred to in the

text are registered trade marks.

My wife Alison, has, as usual, been long suffering; not only putting up with the computers in the house, but also doing my typing despite a house move over the length of the United Kingdom.

Andrew Parr. Minster, Isle of Sheppey.

# CONTENTS

|                                                       | Page  |

|-------------------------------------------------------|-------|

| Chapter One: THE MICROCOMPUTER                        | 1     |

| 1.1 Introduction                                      | 1     |

| 1.2 Computer Architecture                             | 1     |

| 1.3 The Store                                         | 2     |

| 1.4 The Central Processor Unit (or CPU)               | 5     |

| 1.5 Input and Output                                  | 9     |

| 1.6 Instructions and Programs                         | .11   |

| 1.6.1 Fetch                                           | .12   |

| 1.6.2 Store                                           | .12   |

| 1.6.3 Add                                             | .12   |

| 1.6.4 Subtract                                        | .12   |

| 1.6.5 Logical                                         |       |

| 1.6.6 Shifts                                          | .12   |

| 1.6.7 Jumps                                           |       |

| 1.6.8 Conditional Jump                                |       |

| 1.6.9 Subroutine Call and Return                      | .13   |

| 1.6.10 Input/Output Instructions                      | .13   |

| 1.6.11 Control Instructions                           |       |

| 1.7 Why Machine Code?                                 |       |

| 1.8 Machine Code and Assemblers                       |       |

| 1.9 Further Reading                                   | .16   |

| Chapter Two: Z-80 ARCHITECTURE                        | .17   |

| 2.1 Introduction                                      | .17   |

| 2.2 General Architecture                              | .17   |

| 2.2.1 The Z-80 Registers                              | .17   |

| 2.2.2 Flag Registers (F)                              | .20   |

| 2.2.3 General Purpose Registers (B, C, D, E, H, L)    |       |

| 2.2.4 Special Purpose Registers (I, R, PC, IX, IY, SI | ') 23 |

| 2.3 External Connections                              |       |

| 2.3.1 Address Bus                                     |       |

| 2.3.2 Data Bus                                        |       |

| 2.3.3 Control Bus Outputs                             | .27   |

| 2.3.4 Control Bus Inputs                              | .30   |

| 2.3.5 Bus Control                                     |       |

| 2.3.6 Other Signals                                   |       |

| 2.4 Bus Timing                                        |       |

| Chapter Three: INTRODUCTION TO Z-80 SOFTWARE          |       |

| 3.1 Introduction                                      |       |

| 3.2 Hex Representation                                |       |

| 3.3 Address Modes                                     | .36   |

|                                          | Page |

|------------------------------------------|------|

| 3.3.1 Introduction                       |      |

| 3.3.2 Register Addressing                | 38   |

| 3.3.3 Immediate Addressing               | 38   |

| 3.3.4 Extended Addressing                | 39   |

| 3.3.5 Immediate Extended Addressing      | 39   |

| 3.3.6 Register Indirect Addressing       | 40   |

| 3.3.7 Indexed Addressing                 | 40   |

| 3.3.8 Relative Addressing                | 42   |

| 3.3.9 Modified Page Zero Addressing      | 43   |

| 3.3.10 Implied Addressing                |      |

| 3.3.11 Bit Addressing                    | 43   |

| 3.3.12 General Observations              |      |

| 3.4 Instruction Types                    |      |

| 3.4.1 Introduction                       | . 44 |

| 3.4.2 Load Instructions                  |      |

| 3.4.3 Arithmetic and Logic Instructions  | . 45 |

| 3.4.4 Jumps and Subroutine Calls         | 48   |

| 3.4.5 Rotates and Shifts                 |      |

| 3.4.6 Block Transfer                     | 52   |

| 3.4.7 Bit Manipulation                   |      |

| 3.4.8 Input/Output                       |      |

| 3.4.9 Control Instructions               | 57   |

| 3.4.10 General Observations              | 57   |

| 3.5 Symbolic Representation              |      |

| 3.6 Conclusion                           |      |

|                                          |      |

| Chapter Four: THE Z-80 INSTRUCTION SET   |      |

| 4.1 Introduction                         | 60   |

| 4.2 Load Instructions                    | 61   |

| 4.2.1 8 Bit Loads                        |      |

| 4.2.2 16 Bit Loads                       |      |

| 4.2.3 Exchanges                          | 65   |

| 4.3 Arithmetic and Logic Instructions    |      |

| 4.3.1 8 Bit Instructions                 | 66   |

| 4.3.2 General Purpose Operations on AF   |      |

| 4.3.2.1 Decimal Adjust Accumulator (DAA) |      |

| 4.3.2.2 Complement Accumulator (CPL)     |      |

| 4.3.2.3 Negate Accumulator (NEG)         | 68   |

| 4.3.2.4 Complement Carry Flag (CCF),     |      |

| Set Carry Flag (SCF)                     | 68   |

| 4.3.3 16 Bit Arithmetic                  | 69   |

| 4.4 Jump Call and Return Group           | 69   |

| 4.5 Shifts and Rotates                   | 71   |

| 4.6 Block Transfers and Searches         | 75   |

|                                       | Page  |

|---------------------------------------|-------|

| 4.7 Bit Manipulation                  |       |

| 4.8 Input and Output Group            | 76    |

| 4.9 Restarts                          | 83    |

| 4.10 Control Instructions             |       |

| 4.11 General Observations             | 85    |

| Chapter Five: ASSEMBLY LANGUAGE       |       |

| PROGRAMMING                           | 86    |

| 5.1 Introduction                      | . 86  |

| 5.2 The Source Program                | 88    |

| 5.2.1 Introduction                    |       |

| 5.2.2 Line Numbers                    | 88    |

| 5.2.3 Labels                          |       |

| 5.2.4 Instruction Mnemonic            |       |

| 5.2.5 Comments                        |       |

| 5.3 Pseudo Op Codes                   | 93    |

| 5.4 Assembler Directives              | 95    |

| 5.5 Using an Assembler                | 96    |

| 5.6 Monitors and Bugs                 | . 102 |

| 5.6.1 Introduction                    | . 102 |

| 5.6.2 Modify                          | . 103 |

| 5.6.3 Execute                         | . 103 |

| 5.6.4 Breakpoint                      | . 103 |

| 5.6.5 Tabulate                        | . 104 |

| 5.6.6 Single Step                     | . 104 |

| 5.6.7 Conclusion                      | . 105 |

| 5.7 Testing a Machine Code Program    | . 105 |

| 5.8 Conclusion                        | . 113 |

| Chapter Six: INTERFACING THE Z-80     | 114   |

| 6.1 Introduction                      |       |

| 6.2 Serial and Parallel Communication | 114   |

| 6.3 Port Addressing and Logic         | 116   |

| 6.4 Interrupts                        | 120   |

| 6.4.1 Introduction                    | 120   |

| 6.4.2 Servicing an Interrupt          | . 121 |

| 6.4.3 Z-80 Interrupts                 | . 121 |

| 6.4.4 Interrupt Priority              | . 126 |

| 6.5 The Z-80 PIO                      | . 126 |

| 6.5.1 Introduction                    | . 126 |

| 6.5.2 Set Up Data                     | . 130 |

| 6.5.3 Handshaking                     | . 132 |

| 6.5.4 Interrupts                      | . 135 |

| 6.5.5 Set Up Summary                  | . 138 |

| 6.5.6 Power Up Problems               |       |

|                                            | Page |

|--------------------------------------------|------|

| 6.5.7 Pinning                              | 138  |

| 6.6 Serial Communication &UARTS            | 141  |

| 6.6.1 Introduction                         |      |

| 6.6.2 Signals and Standards                | 141  |

| 6.6.3 UARTs                                |      |

| 6.6.4 The Z-80 SIO                         |      |

| 6.7 Counter Timer Chip (CTC)               | 148  |

| 6.7.1 Introduction                         |      |

| 6.7.2 Channel Operation                    |      |

| 6.7.3 Programming the CTC                  | 151  |

| 6.7.4 Interrupts                           |      |

| 6.7.5 Pin Connections                      |      |

| 6.8 Analog Interfacing                     |      |

| 6.8.1 Introduction                         | 156  |

| 6.8.2 Digital to Analog Converter (DAC)    | 156  |

| 6.8.3 Analog to Digital Converter (ADC)    | 156  |

| 6.8.4 General Observations                 | 159  |

| 6.9 Keyboards                              |      |

| 6.10 VDUs                                  |      |

| Chapter Seven: A MISCELLANY OF DATA        |      |

|                                            |      |

| 7.1 Introduction                           |      |

| 7.2 Support Chips                          | 164  |

| 7.2.1 Z-00 CFU                             | 1104 |

| 7.2.2 PIO                                  | 164  |

| 7.2.4 SIO                                  |      |

| 7.2.5 SIO/9                                |      |

| 7.2.6 DART                                 | 165  |

| 7.2.7 DMA Controller                       | 165  |

| 7.2.7 DMA CONTROLLER                       | 165  |

| 7.2.8 FIFO Buffer                          | 103  |

| 7.2.9 CIO/U                                | 165  |

| 7.2.10 Future Developments                 | 165  |

| 7.2.11 Speed                               | 166  |

| 7.3 Manufacturers                          | 166  |

| 7.4 Technical Publications                 | 166  |

| 7.5 Z-80 Based Microcomputers              | 166  |

| 7.6 Writing a Program                      | 167  |

| 7.7 BASIC and PEEK and POKE                | 168  |

| 7.8 The INTEL 8080                         |      |

| Appendix A: Binary and Hexadecimal Numbers | 171  |

| Appendix B: Z-80 Instruction Set           | 177  |

| Appendix C: ASCII Character Codes          | 183  |

## Chapter One

### THE MICROCOMPUTER

#### 1.1 INTRODUCTION

A computer based on the Z-80 operates in the same manner as any other machine be it micro, mini or mainframe. Before we can discuss the Z-80 and its use in any detail, it is first necessary to describe the operation of a typical microcomputer. This will serve to define the terms used in the rest of the book, and place the Z-80 in its role as the central processor of a powerful, but conventional computer.

#### 1.2 COMPUTER ARCHITECTURE

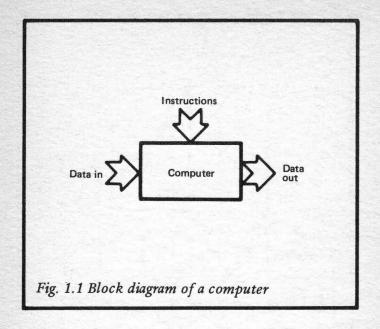

All computers can be represented by the block diagram of Fig.1.1, and can be considered as manipulators of data. The actual form of the data will depend on the application. In commercial computing the data will be VAT returns, sales figures, bank accounts and similar information. In industrial control, the data will be plant sensors and actuators. In a computer game the data will be the players hand controls and the video display. The data can be split into input data, which is to be processed, and the output data, which is the result of the processing. To produce the output data, the computer follows a set of procedures, called instructions, which define the operations that are to be performed on the input data.

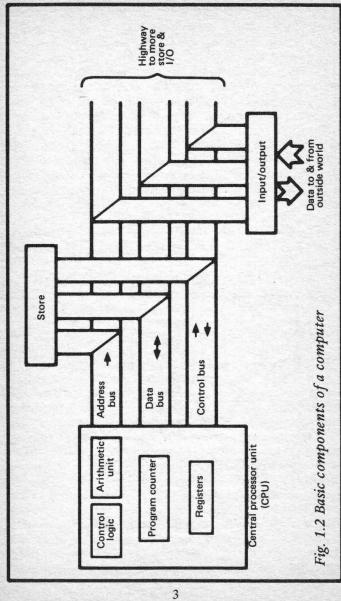

The computer can be represented in more detail by Fig.1.2, and can be considered to consist of three basic units; a store, an input/output unit and a central processor unit, all interconnected by a common highway. The input and output unit obviously receives and transmits data from and to the outside world. The store is used to hold instructions and data. The central processor unit controls the operation of the machine, and performs the logic and arithmetic operations required by the instructions.

## 1.3 THE STORE

The store is used to hold the instructions and temporary data in the form of numbers. It can best be considered as an array of pigeon holes, each of which can hold one number called (rather confusingly) a Word. Each pigeon hole is known as a store location, and has a unique address (similar to a house address) by which it can be identified. We can thus say, for example, "store location 3220 contains 127". This means that the pigeon hole whose address is 3220 has the number 127 stored in it.

A typical microcomputer will have over 16000 store locations (although small machines may have less than 1000). All common microprocessors deal basically with 8 bit numbers, often called Bytes. The numbers stored will therefore be in the range 0 to 255. As will be seen later, this is not the restriction that it might at first appear.

The store does not differentiate between instructions and data; both are held in exactly the same form. The central processor unit determines whether the number in a particular store location is considered to be an instruction or data.

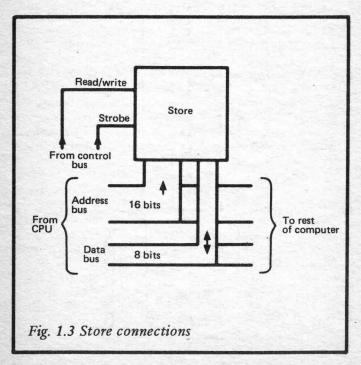

The store connects to the rest of the computer in a manner similar to Fig.1.3. The three groups of signals are known as the address bus, the data bus and the control bus. (The term bus is short for busbar, sometimes the term highway is used.)

The address bus is used by the central processor to identify which store address is to be accessed. Usually, up to 65,536 (called 64K) locations can be used with a microprocessor, necessitating a 16 bit address bus.

The data bus is used to transfer data and instruction between the store and the central processor unit. Movement

can take place from store to CPU, or CPU to store, so the data bus is bidirectional. All common microprocessors use an 8 bit data bus.

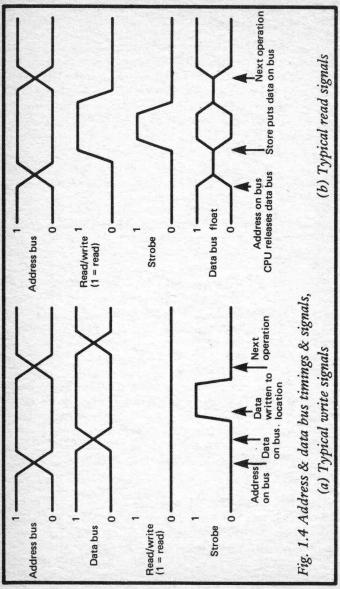

The control bus contains the timing signals to sequence the movement of data or instructions. In the majority of systems there are basically two signals. A read/write line is used to indicate if a number is to be loaded into or read from, the addressed location, and a strobe signal indicates when the number on the data bus is valid (i.e. the transients due to different propagation delays, reflections etc. have died away). Different microprocessors use slightly different signals.

Fig.1.4a summarises the signals used to write a store location, and Fig.1.4b the signals used to read from a store location.

When a number is written to a store location, the previous contents are obviously overwritten. When a number is read from a store location, the store location contents are unaltered; the number put onto the data bus is merely a *COPY* of the store contents.

The store in Fig.1.3 is known as a RAM or Random Access Memory. This is a term that causes some confusion, but simply means that each store location can be accessed in exactly the same time. Bulk storage devices, such as tapes and discs, have a variable access time which depends on where the information is stored and where the tape or disc currently is when the information is needed.

Another form of storage commonly encountered is a ROM, for Read Only Memory. This is a conventional store whose contents are fixed and cannot be altered by the computer. Usually a ROM is used to hold a fixed program (such as the BASIC interpreter or an Assembler as described later). To the central processor, a ROM behaves in exactly the same manner as the rest of the store.

## 1.4 THE CENTRAL PROCESSOR UNIT (or CPU)

The computer follows instructions held in the store (in the form of numbers). Normally, instructions are held in

sequential store locations. To obey an instruction we must go through the following steps:

- i. Address the store to get the next instruction.

- ii. Decode the instruction to decide what needs to be done

- iii. Obey the instruction. This will usually involve the store again to read, or write, data and will often require simple arithmetic operations

- iv. Decide where the next instruction is held in the store, and go back to step i.

Most instructions therefore require two operations on the store; the first to read the instruction, the second to read the data to be used or write a result back to the store. Sometimes the operations above are referred to as three steps:-

Fetch cycle (instruction is fetched, steps i and ii)

Execute cycle (instruction is obeyed, step iii)

Reset cycle (the internal logic is reset for the next instruction, step iv)

The FER sequence has been called the heartbeat of a computer.

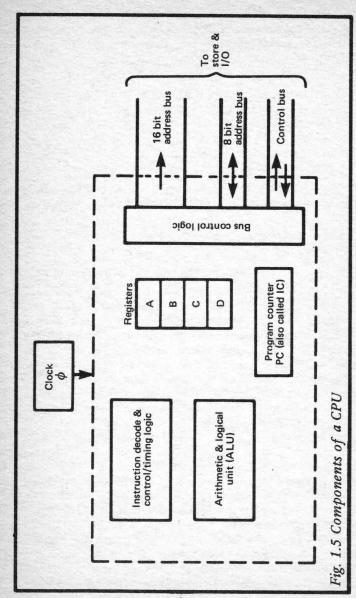

The component parts of a central processor unit are shown on Fig.1.5. For simplification, internal connections are omitted.

The program counter (PC, also known as an instruction counter, IC) holds the address of the current instruction. Because most microcomputers can address up to 64K, the PC will usually be a 16 bit register. With the exception of JUMP instructions (the machine code equivalent of a BASIC GOTO instruction), the program will be held in sequential store locations. This means that the PC can literally be a counter which is pulsed by the control logic at step iv above.

In addition to the storage provided by the RAM, fast storage (for temporary scribbling pad purposes) is provided by registers in the CPU. These can hold one number to the same word length as the store (8 bits for all common micros). Some microprocessors (such as the 6502) have only one register, whereas some (such as the Z-80) have as many as sixteen. Fig. 1.5 shows four registers for illustrative purposes.

The use of registers will be described later.

Associated with the registers is the Arithmetic and Logic Unit (or ALU). There are actually very few machine code instructions; as we shall see later, most are variations on:

Fetch a number from a store location (or input port) to a register

Write a number to a store location (or output port) from a register

Add (or subtract) a number from a store location to a register, result to a register.

The ALU performs the arithmetical operations (and some logical operations such as AND, OR) required by the instructions.

Finally, we have the block labelled control/timing logic. This contains the logic to decode the instructions and sequence the steps i to iv above. This involves selecting routes between the store, the ALU, the registers and the highways. The control/timing logic is usually the most complex part of a computer.

Associated with the control logic is a simple clock oscillator which provides the basic timing pulses. Usually this is a crystal oscillator in the range 1 to 4MHz.

A microprocessor is often thought of as a computer, but is, in fact, simply the CPU of a computer. A microprocessor contains the elements of Fig.1.5, but needs external RAM/ROM and Input/Output equipment to be useful.

#### 1.5 INPUT AND OUTPUT

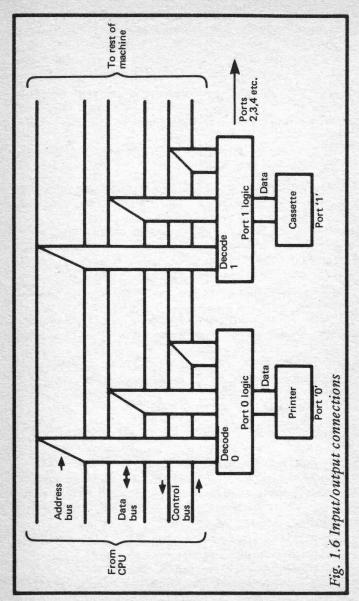

A computer connects to a variety of I/O equipment, printers, keyboards, VDUs, cassette recorders etc. These connect to the computer highway as shown on Fig.1.6. Each I/O device is identified by an address. I/O addresses are commonly known as 'Ports', so we could have, say, a printer connected to Port 3 and a keyboard to Port 5.

Data is transferred to and from an I/O port via the highway. The port address is placed on the address highway, the read/

write control line used to identify the direction of the transfer, and the I/O control line used to signify that the address is a port address, not a store address. Data transfer then takes place via the data highway. Some microprocessors (such as the 6800) do not have an I/O control line and literally deal with I/O addresses in the same ways and with the same instructions, as store addresses. With these microprocessors a store and a port cannot have the same address.

Most microprocessors allow data to be transferred between I/O ports and registers or between I/O ports and store locations. We shall discuss later the techniques used to resolve the vast difference in speed between slow speed devices (such as printers) and the computer itself.

## 1.6 INSTRUCTIONS AND PROGRAMS

As anyone who has written a program in BASIC will know, a computer simply obeys a sequence of instructions called a program. In a high level language such as BASIC or PASCAL, these instructions are written in 'English'. A computer actually obeys instructions represented by numbers called a machine code program. When a high level program is obeyed, a special program built into the computer (called a compiler or an interpreter) converts the high level language program to an equivalent machine code program. This action is invisible to the high level language user.

A machine code instruction must specify:

- i. What is to be done (e.g. Add, fetch data, store data, etc.)

- ii. Where the data is to be found, and where the result is to be placed (e.g. "Fetch the data from store location 2000 to Register B", or "Add the data in store location 1575 to the data in Register A putting the result in Register A").

In following chapters we will see how these ideas are actually specified given the limitations of an 8 bit word.

There are actually a very limited set of instructions in a computer, and most are variations on:

#### 1.6.1 Fetch

"Fetch data from a specified store location (or register) to a specified register".

#### 1.6.2 Store

"Store data from a specified register to a specified store location". Sometimes Fetch and Store are collectively called "Moves" or "Loads".

## 1.6.3 Add

"Add data from a specified store location (or register) to the data in another specified store location (or register) the result to go to a specified store location (or register)".

Usually Adds take the simpler form, "Add data from a specified store location to the data in register A, the result to go to Register A".

#### 1.6.4 Subtract

As 1.6.3 but subtraction is performed. Note that multiplication and division are not available on any common microprocessor.

# 1.6.5 Logical

As 1.6.3, but logical operations such as AND, OR, NEV are performed between the data.

## 1.6.6 Shifts

Data in a microprocessor is held as 8 bit binary numbers. A shift instruction moves the data in a register up, or down by one place. If we have the bit pattern 10110101, a simple shift up would produce 01101010, and simple shift down would produce 01011010. A shift up multiplies a number by two, a shift down divides by two. As will be seen later, there are

many variations on the shift instruction.

## 1.6.7 Jumps

Normally, instructions are held in sequential store locations. A Jump instruction is the machine code equivalent of the BASIC GOTO, and specifies where the next instruction is to be found (e.g. Jump to location 3220).

## 1.6.8 Conditional Jump

A conditional jump tests the condition of a register, the results of which determine if a jump instruction is to be obeyed (e.g. Jump to 4057 if register A is zero). This is the machine code equivalent to the BASIC IF condition THEN GOTO (line number).

#### 1.6.9 Subroutine Call and Return

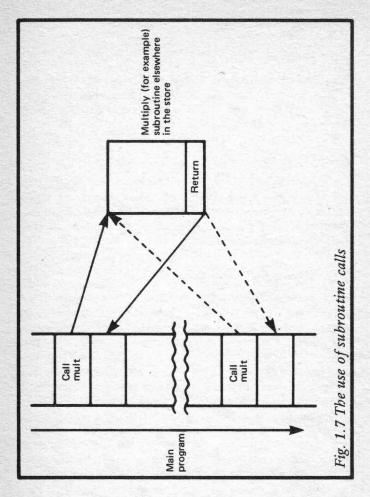

Programmers in BASIC will be familiar with the concept of a subroutine with the GOSUB and RETURN instructions. A subroutine allows a piece of program that is used frequently to be written once and called when needed by the rest of the program. This is best shown by Fig.1.7. Machine code subroutine calls work in exactly the same way. A subroutine call acts like a jump to the start of the subroutine (e.g. Call 7087 would take us to the subroutine starting at location 7087). A Return instruction is placed at the end of the subroutine, to take us back to the location in the main program immediately after the subroutine call. Subroutines can call subroutines (called Nesting). A Binary to BCD subroutine, for example, would need to use multiplication and division subroutines. In most microprocessors, conditional subroutine calls, and conditional returns are provided as well as the simple call and return described above.

# 1.6.10 Input/Output Instructions

Input/output instructions must specify the I/O port address,

the direction (in or out) and the source (or destination) of the data (i.e. which register or which store location).

## 1.6.11 Control Instructions

Most microprocessors have a small number of control instruc-

tions such as STOP, Disable Interrupts and similar operations. These do not involve data.

At first sight, the vast array of instructions available on a microprocessor can be rather awe inspiring (the Z-80 has 158 different instruction types). Much of the inevitable feeling of confusion can be assuaged by remembering that most instructions are simple variations of the ten types outlined above.

#### 1.7 WHY MACHINE CODE?

Programming in BASIC is simple and straightforward, so it is not unreasonable to ask why one should bother with the trials, tribulations and complexity of machine code programming. There are really three reasons.

The first is that it is possible to perform operations in machine code that are impossible (or difficult) to achieve in BASIC. Control of external items like a model railway would be difficult in simple BASIC for example.

The second reason concerns speed. BASIC is notoriously slow, and is quite unsuited to, say dynamic video games. Machine code programs operate many times faster than BASIC programs.

The final and most compelling, reason is that machine code programming is an intellectual challenge akin to chess or bridge. The mental exercise of programming (in any form) is very addictive and this is particularly true of machine code programs.

#### 1.8 MACHINE CODE AND ASSEMBLERS

The instructions a computer actually obeys are held in the form of binary numbers. To assist human beings to read these numbers, it is usual to express them in Hex, so 1010 0111 becomes A7 (see Appendix A).

A machine code program therefore looks something like:

## F5 C5 D6 64 3E Z0 D3 00 etc.

which is still fairly incomprehensible.

It is easier to follow a machine code program if simple mnemonics are used to represent the instructions. The actual mnemonics used on the Z-80 will be described later, but in general they are simple to understand. A program written in mnemonics is said to be written in Assembler Language, and looks more understandable.

> LD A. 33 INC HL JP NZ, LOOP

Each of these corresponds directly to a single machine code intruction, LD A,33 for example, means put the number 33 into register A.

The program written in Assembler Mnemonics is converted to machine code by a program called (surprise, surprise) an Assembler. The Assembler has editing facilities similar to those found in BASIC and makes machine code programming much less infuriating. In later chapters, examples of Assembler programs will be given. Assemblers are not usually provided with computers, and have to be purchased separately.

## 1.9 FURTHER READING

The description of computer architecture in this chapter has, of necessity, been rather brief. More detailed discussions can be found in the following books also published by Bernard Babani (publishing) Ltd:

Book No. BP72 - A Microprocessor Primer

Book No. BP78 - Practical Computer Experiments

Book No. BP66 - Beginners Guide to Microprocessors Book No. BP77 - Elements of Electronics - Book 4,

Microprocessing Systems and Circuits

## Chapter Two

## **Z-80 ARCHITECTURE**

#### 2.1 INTRODUCTION

This chapter introduces the Z-80 microprocessor, describing its architecture and role in the construction of a microcomputer. The Z-80, like all microprocessors, is the CPU of a perfectly conventional computer, and needs store and I/O before it can be useful. The connection of these items is discussed. This chapter is therefore concerned with equipment. Chapter 3 will describe the Z-80 instruction set and will be concerned with software.

### 2.2 GENERAL ARCHITECTURE

## 2.2.1 The Z-80 registers

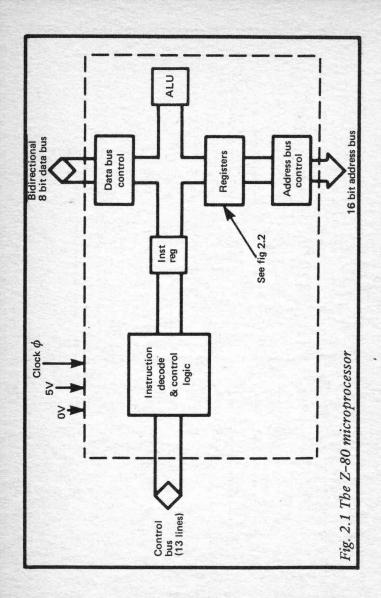

The Z-80 can be represented by the block diagram of Fig.2.1 which is very similar to the generalised CPU diagram of Fig.1.5 in Chapter 1. The Z-80 is an 8 bit microprocessor, and can address 64K of store. It therefore utilises an 8 bit data bus and a 16 bit address bus. There are also 13 control signals in the control bus.

The registers, PC, instruction decode, ALU and control fulfill the same functions as described for Fig.1.5. The instruction register simply holds the instruction currently being obeyed.

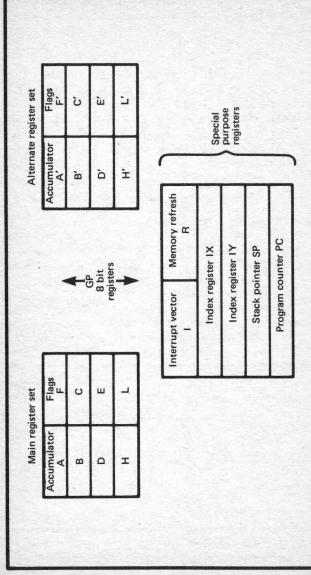

The user of the Z-80 is interested in the block labelled "registers". This is shown expanded on Fig.2.2. The Z-80 has an impressive array of registers, 17 8 bit registers, one 7 bit register and 4 16 bit registers. The first point of note is that these registers are in three groups, main register set, alternate register set, and special purpose.

The main register set and alternate register set are identical. The programmer chooses which set he wishes to work with at

Fig. 2.2 The Z-80 registers

any time by the use of "Exchange" instructions which switch sets. This is, admittedly, a bit of a nuisance but it is necessary to allow access to the 16 registers whilst minimising the number of instructions in the Z-80. Full access would have nearly doubled the size of the Z-80 instruction set.

Each register set has an 8 bit accumulator (A), an 8 bit flag register (F) and six 8 bit general purpose registers (B,C,D,E,H, L). The accumulators are used for arithmetic and logic purposes; the other 6 G.P. registers cannot (with a few exceptions) be used with the ALU and simply provide fast temporary storage. The results of almost all arithmetic operations go to the accumulators.

## 2.2.2 Flag Registers (F)

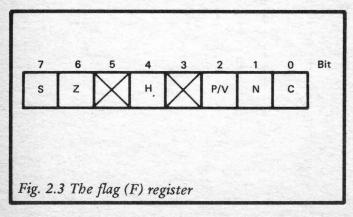

The flag registers are 8 bit registers used to indicate certain conditions that arise in arithmetic and logical operations. These are used as tests for conditional jumps. Each condition is represented by a bit, as shown on Fig.2.3. The flags operate as below.

The carry flag (C) is simply the carry from the highest bit of the accumulator, and is set if a "carry" is generated during an add, or a "borrow" during a subtraction. The carry bit is also altered by some shift operations. If twos complement

arithmetic (see Appendix A) is being used, the carry does not necessarily indicate if an overflow has occurred. The P/V flag should be used for this purpose.

The zero flag (Z) is set when the last instruction affecting the flags resulted in zero contents of the accumulator. Any non zero contents resets the flag.

The sign flag (S) is used with twos complement arithmetic, and simply indicates if the accumulator is positive (S=0) or negative (S=1), because bit 7 of an 8 bit twos complement number indicates the sign. The S flag is simply a copy of bit 7. Note that zero is a positive number.

The parity/overflow flag (P/V) serves two purposes. After a logical operation (AND, OR, Exclusive OR) the flag indicates the parity of the result, being set for an even parity and reset for an odd parity. The second use requires a little more explanation. If twos complement arithmetic is being used, an 8 bit word represents a SIGNED number in the range -128 to +127. Bit 7 indicates the sign, being 0 for positive numbers and 1 for negative numbers. With twos complement arithmetic, the carry bit does not reliably indicate if an overflow has occurred. Consider the two examples below:

$$\begin{array}{rcl}

123 & = & 0111 & 1011 \\

+ 106 & = & \underline{0110} & \underline{1010} \\

\text{C=0} & & \underline{1110} & 0101 & = & -91

\end{array}$$

The result is an incorrect negative number, but the carry bit has not been set.

In this case, the result is correct, but the carry bit has been set.

The P/V flag indicates correctly if an overflow has occurred during a twos complement arithmetical operation. In the two above examples, the P/V flag would be set for the first (overflow has occurred) and reset for the second (overflow has not occurred). It follows that the carry flag is used for unsigned 8

bit arithmetic, and the P/V flag for signed twos complement arithmetic.

The C, Z, S, P/V flags are used with conditional jumps and conditional subroutine calls. The Z-80 uses the following conditions.

| Carry         | C = 1   |

|---------------|---------|

| Non Carry     | C = 0   |

| Zero          | Z = 1   |

| Non Zero      | Z = 0   |

| Parity Even   | P/V = 1 |

| Parity Odd    | P/V = 0 |

| Sign Negative | S = 1   |

| Sign Positive | S = 0   |

The four flags above can be used directly for conditional jumps. There are also two flags which are used by the internal logic of the Z-80 when BCD operations are being performed. These cannot be used directly in conditional jumps, but can be accessed as any other bit in any other register.

The first of these flags is the half carry (H) used to indicate the BCD carry or borrow result from the least significant four bits of the accumulator. This flag is used by the Decimal Adjust instruction, described later.

The Add/Subtract flag (N) indicates if the last instruction was an addition or subtraction. The algorithm used by the Decimal Adjust instruction is different for addition or subtraction, the correct algorithm being selected by the N flag.

The flags are not altered by all instructions. In general, the flags are altered by all arithmetical and logical operations. Load instructions (store reads and writes and inter register transfers) leave the flags unaffected.

## 2.2.3 General Purpose Registers (B, C, D, E, H, L)

Each register set has six general purpose registers (B, C, D, E, H, L). These provide fast temporary storage. They can also be grouped as 16 bit register pairs (BC, DE, HL) providing 16 bit arithmetic facilities and a powerful method of addressing

known as register indirect (to be described later in section 3.3.6).

## 2.2.4 Special Purpose Registers (I, R, PC, IX, IY, SP)

There are six special purpose registers, denoted I, R, PC, IX, IY, SP. Although these are usually dedicated to one task they can, in general, be accessed like any other register.

PC is the 16 bit program counter, operating exactly as described in Chapter 1. A 16 bit program counter is necessary to address 64K of store.

IX and IY are two 16 bit registers used in a useful method of addressing the store known as Indexed Addressing. This is described further in section 3.3.7.

SP stands for Stack Pointer, and is another 16 bit register. To understand the use of the stack pointer we must first describe the concept of the "stack". We described the idea of subroutines in the previous chapter. When a subroutine is called, we must somehow save the contents of the PC, and substitute the address of the subroutine. At the end of the subroutine we must reinstate the PC to its original value.

To achieve this, an area of store is designated to hold PC addresses during subroutine calls. Normally the stack starts at the top of the store and comes down. The SP holds the current position of the end of the stack. Because addresses are 16 bits, each address takes two store locations on the stack.

The operation of the stack is best demonstrated by an example. Let us assume we are obeying the instruction at location 0C50, and it is a call to a subroutine at 1D00. The stack pointer is currently at 2F05, indicating that the stack ends at 2F05. The sequence below is then followed:

- i. PC contents are put into 2F05 and 2F04. (i.e. the address of the subroutine call is put onto the stack)

- ii. PC contents are replaced by 1D00 (the address of the subroutine)

- iii. The SP is decremented to 2F03 (to allow for nesting of subroutines. The stack can be of any length)

- iv. The subroutine is obeyed.

At the end of the subroutine, a return instruction initiates the following sequence:

- i. The SP is incremented and used to bring a 16 bit number back from the stack to the PC. If addresses have been placed and read from the stack in sequence, this will bring 0C50 back to the PC.

- ii. The PC is incremented to step onto the instruction following the subroutine call.

- iii. The main program continues.

Putting an address onto the stack is known as a PUSH. Getting an address from the stack is known as a PULL. The important point to remember about a stack is Last In, First Out.

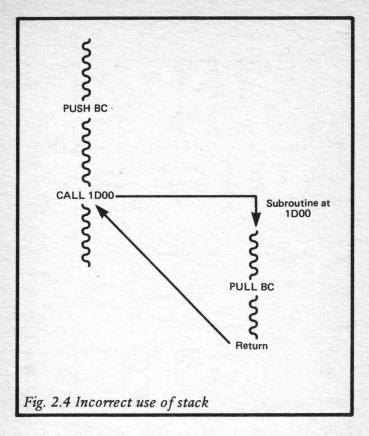

The stack can also be used to store data from register pairs. This must be done with care, as the programmer must ensure that the data comes off the stack in the expected order. The sequence in Fig.2.4 will NOT work as expected because the data brought to BC will be the last data pushed onto the stack; the address of the instruction calling the subroutine call. The address replaced in the PC by the return instruction will be the contents of BC pushed onto the stack earlier. Remember, Last In, First Out.

The two final registers are denoted I (for interrupt) and R (for refresh). The I register is known as the Interrupt Page Address Register, and is used when the Z-80 is controlling external devices. There is a vast difference in speed between computers and peripheral devices, which is reconciled by a technique known as Interrupts. This will be described in detail in Chapter 6, but for the present an interrupt can best be considered as a subroutine call initiated by an external device. The device supplies the low byte of the subroutine address, the I register supplies the high byte.

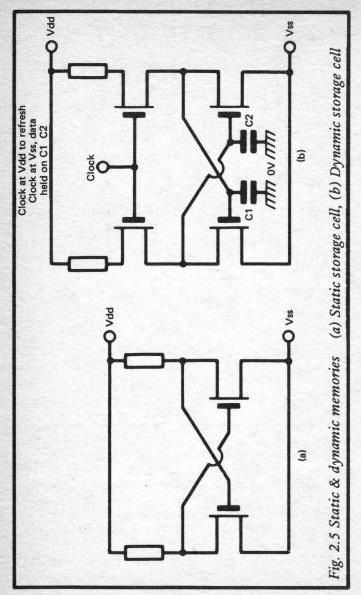

The 7 bit R register is used when the store is constructed with dynamic memory ICs. (Such as the popular 4116). These store the data as charges on capacitors (see Fig.2.5) which have to be refreshed every few milliseconds. Normally this refreshing is performed by external logic which grabs control of the highway at regular intervals to perform the refresh operation. The

Z-80 is unique amongst micros in containing its own refresh logic. The R register contains the current refresh address. The contents of the R register are placed on the lower 7 bits of the address bus along with a refresh signal on the control bus when the bus is free. After each refresh the R register is automatically incremented. The whole refresh operation is totally invisible to the user.

Chapter 3 will describe how data is moved and manipulated in the registers and store.

#### 2.3 EXTERNAL CONNECTIONS

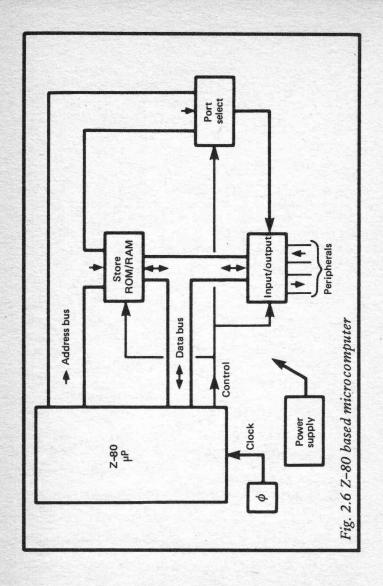

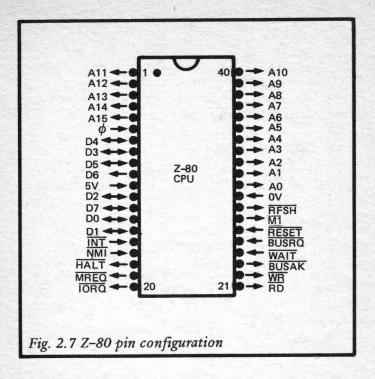

A typical small Z-80 system is shown on Fig.2.6. This should be compared with Fig.1.2. The Z-80 itself is a standard 40 pin dual in line IC with connections shown on Fig.2.7. It will be seen that the connections form the address bus, data bus and control bus described earlier.

#### 2.3.1 Address Bus

The address bus is A0-A15, A0 being the least significant bit and A15 the most significant bit. The address bus can address up to 64K of store. The least significant 8 bits (A0 - A7) are also used to address I/O ports, allowing up to 256 I/O addresses. The address highway conveys the address in "true" form.

#### 2.3.2 Data Bus

The data bus is D0 - D7, D0 being the least significant bit. This is a bidirectional highway, conveying data between store, I/O ports and the Z-80.

# 2.3.3 Control Bus Outputs

The control bus contains 13 signals; 8 outputs and 5 inputs. The first of these is RD, memory read. This indicates that the CPU wants to read data from a memory location or I/O port. The signal is active low, and is present whilst the address bus holds a valid address. RD is used by the addressed location or port to gate data onto the data bus.

WR, write, indicates that the CPU requires to send data to a store location or I/O port. The signal is active low, and is present whilst the address bus holds a valid address and the data bus valid data. WR and RD are effectively strobe signals similar to those on Fig.1.3.

MREQ, memory request, is an active low signal indicating that the address bus holds a valid address. MREQ appears in conjunction with RD or WR.

$\overline{IORQ}$  denotes input/output. This active low signal indicates that the address on A0 - A7 is the address of an  $\overline{I/O}$  port, and an input/output transfer is to be performed.  $\overline{IORQ}$  allows memory locations and  $\overline{I/O}$  ports to share the same address.  $\overline{IORQ}$  appears with  $\overline{RD}$  or  $\overline{WR}$  to indicate if data is to be input or output.  $\overline{IORQ}$  is also used in the timing of interrupts, to be described later in section 6.4.

$\overline{\text{RFSH}}$  stands for refresh and is an active low signal indicating that A0 - A6 contain an address that can be used to refresh dynamic memories.  $\overline{\text{MREQ}}$  appears with  $\overline{\text{RFSH}}$ .

HALT indicates simply that the CPU has halted following a HALT instruction. The signal is active low. The memory refresh for dynamic memories continues even though the processor is halted.

M1 stands for machine cycle one. It was explained in Chapter 1 that obeying an instruction consists of a fetch of the instruction from the store followed by a data read and/or a data write. In the Z-80 the instruction fetch is known as M1. the memory read as M2 and the memory write as M3.  $\overline{\text{M1}}$  is an active low signal indicating that the CPU is in the M1 state. The signal is used in timing some I/O operations.

# 2.3.4 Control Bus Inputs

The first control input is the WAIT signal. The Z-80 is faster than some memory and I/O control devices, particularly when a 4MHz clock is used. The WAIT signal is used by an addressed memory or I/O port to indicate that the required data transfer can not yet take place. On receipt of a WAIT signal the CPU simply pauses. The WAIT signal is active low. During the WAIT state the memory refresh is not maintained.

RESET is used to force the CPU to a known state, and is normally used at power up or to regain control if a program has gone off the rails. The RESET input is active low and has the following effects.

i. PC, I and R are reset to zero

ii. Interrupts are disabled and interrupt Mode 0 is set.

Interrupts are described later in section 6.4. Resetting the PC has the effect of an unconditional jump to location zero.

INT is also an interrupt request from an external device.

A "low" on this line initiates the interrupt sequence.

NMI is also an interrupt request, but is a higher priority than INT. The CPU can ignore the INT signal, but NMI, standing for Non Maskable Interrupt, is always recognised. NMI effects a subroutine call to location Hex 66. The NMI is negative edge triggered.

#### 2.3.5 **Bus Control**

In large systems, the address data and control buses can be shared with another CPU or devices such as disc controllers which require access to the memory without the CPU. Under these circumstances, the CPU is occasionally required to release the buses for use by the other devices requesting access. This is achieved by two signals on the control bus.

BUSRQ (Bus request) is an input from an external device requesting control of the buses. The signal is active low. On receipt of BUSRQ the Z-80 sets all its bus signals to a high impedance state, allowing the requesting device to use the buses. The Z-80 then takes BUSAK to a 'low' to indicate that the requesting device can use the buses. Whilst the Z-80 has released the buses, memory refreshing obviously ceases.

# 2.3.6 Other Signals

The Z-80 needs a 5 volt supply (Vcc and 0V) and a clock  $(\phi)$ . The clock is usually provided by a simple crystal oscillator and can be 1, 2, or 4MHz dependent on the version of Z-80 and the application.

#### 2.4 BUS TIMING

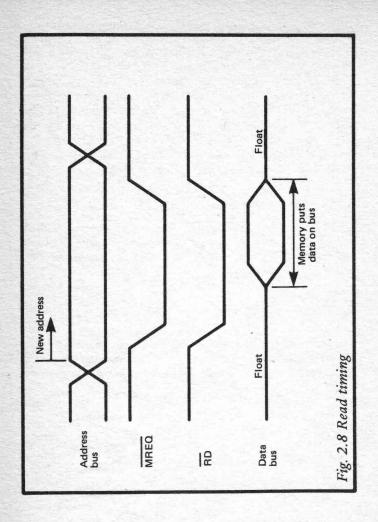

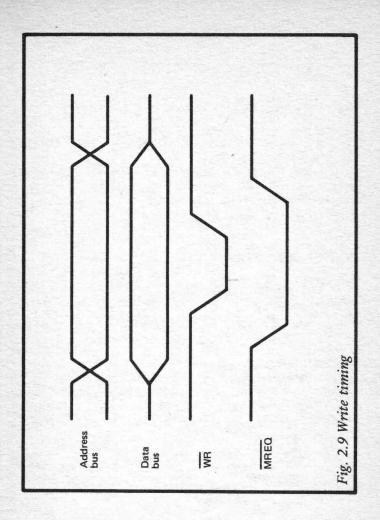

The actual timing of the bus signals is usually of little concern to the amateur. Fig. 2.8 and 2.9 show, somewhat simplified, the timing of a memory read and a memory write operation.

# Chapter Three

### **INTRODUCTION TO Z-80 SOFTWARE**

#### 3.1 INTRODUCTION

The previous chapters have been largely concerned with the mechanics of a Z-80 based microcomputer. We can now start to discuss how programs are written for the Z-80. This chapter will describe the Z-80 instruction set in general terms and explain the various terms used in later sections. Chapter 4 will describe the Z-80 instruction set in detail.

#### 3.2 HEX REPRESENTATION

The Z-80 deals with 8 bit numbers; each store location and GP register can hold a number in the range 0 to 255. The numbers are in binary, so a typical register could hold the number

which at first sight, means little to anyone. We could, with a little trouble, convert it to decimal (167 actually) but it is usually preferable to represent a store location and register contents in a form that can easily be converted back to binary. Most microprocessors, including the Z-80, use a system called Hex (for hexadecimal).

Hex is based on four bits, which can represent a number in the rage 0 to 15. These are represented by the symbols 0 to 9 followed by A to F

| Binary | Hex | Decimal |

|--------|-----|---------|

| 0000   | 0   | 0       |

| 0001   | 1   | 1       |

| 0010   | 2   | 2       |

| 0011   | 3   | 3       |

| 0100   | 4   | 4       |

| 0101   | 5   | 5       |

| Binary | Hex | Decimal |

|--------|-----|---------|

| 0110   | 6   | 6       |

| 0111   | 7   | 7       |

| 1000   | 8   | 8       |

| 1001   | 9   | 9       |

| 1010   | A   | 10      |

| 1011   | В   | 11      |

| 1100   | C   | 12      |

| 1101   | D   | 13      |

| 1110   | E   | 14      |

| 1111   | F   | 15      |

To represent a binary number in Hex, you simply split it into 4 bit chunks, and put the Hex equivalent underneath. For example:

|         | 1010 | 00111 |

|---------|------|-------|

| becomes | 1010 | 0111  |

| giving  | A    | 7     |

So the binary word 1 0 1 0 0 1 1 1 is A7 in Hex.

| Another example | 01001 | 100  |

|-----------------|-------|------|

| becomes         | 0100  | 1100 |

| giving          | 4     | C    |

It is equally easy to go from Hex to binary. The four bit pattern for the Hex number is simply written underneath. For example D2 becomes

giving 1 1 0 1 0 0 1 0 as the binary equivalent of Hex D2.

| Another example | F    | A    |

|-----------------|------|------|

| gives           | 1111 | 1010 |

The Z-80 instruction set is given in Chapter 4 in Hex form. 8A, for example, is the instruction that will make the Z-80 add the contents of register D to the Accumulator.

Hex representation can also be used on 16 bit numbers such as store addresses), for example:

| becomes    | 1110<br>E | 0101 | 1010<br>A | 1001 |

|------------|-----------|------|-----------|------|

| and in rev | erse      |      |           |      |

|            | 0         | C    | 5         | 7    |

| hacamas    | 0000      | 1100 | 0101      | 0111 |

Store addresses in Z-80 microcomputers are usually given in Hex.

Hex can be a bit daunting at first, but it should be remembered that it is just a convenient shorthand method of representing binary numbers. With a little practice, binary to Hex and Hex to binary becomes second nature.

#### 3.3 ADDRESS MODES

#### 3.3.1 Introduction

An instruction will normally involve data in one or two locations or registers. This data will be moved or manipulated in some form (e.g. Add Subtract, etc.). An instruction therefore must usually specify two things:

- i. What is to be done (e.g. move, add, subtract)

- ii. Where the data is to be found (e.g. Register A, location 3220)

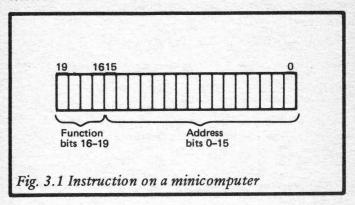

In older computers, which used a 16 bit word length, it was common to allocate the op code (specifying what is to be done) to the top few bits, and the address of the data to the remainder of the word as shown on Fig.3.1. This is known as direct addressing, because the number representing the instruction directly indicates the store location where the data is to be found or stored.

There is a problem, however, with all 8 bit microprocessors. An 8 bit word can represent a number in the range of 0-255. The Z-80 has 158 different instructions, so it will take all 8 bits of a microprocessor word simply to specify the Op Code. To specify a 64K address requires an additional 16 bits.

Obviously direct addressing cannot be used, at least not in the simple form of Fig.3.1. All 8 bit microprocessors use a collection of ingenious methods called address modes to address the store.

The first, slightly confusing, idea is the use of different lengths of instruction. A Z-80 instruction can be 8, 16, 24 or 32 bits in length (occupying respectively 1, 2, 3 and 4 store locations). The first location will always be an Op Code. Subsequent locations define where the data is to be found. The following are typical Hex coded Z-80 instructions:

| 7A          | Move the contents of register D to                                          |

|-------------|-----------------------------------------------------------------------------|

| 06 FF       | the accumulator Put the Hex value FF into Register B                        |

| C3 50 0C    | Jump to location 0C50                                                       |

| ED 43 FE IF | Store the 16 bit number in Register<br>Pair BC to store locations IF FE and |

|             | IF FF                                                                       |

In each case the first 8 bits define the Op Code (7A, 06, C3, ED). In the latter case the full Op Code actually occupies two locations (ED 43) but the ED portion specifies the form of the instruction, and 43 the register pair.

If the 4 instructions above were stored from location Hex 1000 we would have:

| Location | Contents |

|----------|----------|

| 1000     | 7A       |

| 1001     | 06       |

| 1002     | FF       |

| 1003     | C3       |

| 1004     | 50       |

| 1005     | 0C       |

| 1006     | ED       |

| 1007     | 43       |

| 1008     | FE       |

| 1009     | IF .     |

There are many different address modes used in computers in general, and microprocessors in particular. The Z-80 uses ten different address modes.

### 3.3.2 Register Addressing

Many instructions in the Z-80 set only involve data held in the registers. Examples are "move the contents of Register B to Register A" or "Move the contents of Register D to Register C". These, and similar instructions are said to use Register Addressing. Most of these instructions are a single byte (8 bits) in length and occupy one location. The Op Code for "Move the contents of Register B to Register A" is the single byte instruction 78.

# 3.3.3 Immediate Addressing

Immediate addressing is used where the data to be manipulated is fixed. For example "Load Register B with 42" or "Add 7 to Register A". These instructions take the form:

Op Code One or two bytes Data

"Add 7 to Register A" is actually C6 07, C6 being the Op Code and 07 the data.

### 3.3.4 Extended Addressing

Extended addressing is almost identical to direct addressing described earlier. The store address for the data is given in full 16 bits in the instruction. Examples are "Move the contents of store location 0C50 to Register A" or "Call the subroutine at location 1DF5". The address occupies two locations in the instruction, and the Op Code one or two locations. Extended Address instructions therefore occupy three or four locations:

Op Code One or two bytes

Address Bottom 8 bits

Address Top 8 bits

The Z-80 code for "Call the subroutine at location 1DF5" is CD F5 1D. CD is the Op Code and F5 1D indicates the address 1DF5. It might seem more logical to have the instruction written CD 1D F5, but consider how the instruction is stored:

Location Contents

N CD

N+1 F5 address low byte Address 1DF5

N+2 1D address high byte

The address is stored in two locations, N+1, N+2. The low byte of the address is simply stored in the low byte of the instruction (N+1) and the high byte of the address in the high byte of the instruction (N+2).

# 3.3.5 Immediate Extended Addressing

This addressing mode is used with 16 bit data in two successive store locations, register pairs (BC, DE, HL) and the index registers. For example, we could have "Load register pair BC with 0C50". An immediate extended instruction takes the form of a three of four location instructions:

Op Code (one or two bytes) Data Low Byte Data High Byte "Load register BC with 0C50" is actually 01 50 0C with 01 the Op Code and 0C50 the data. As with extended Addressing, it might be thought more logical to have coded this 01 0C 50, but in fact the low byte of the data goes to the low byte of the instruction.

When register pairs are used, high and low bytes are allocated

| High | Low |

|------|-----|

| В    | C   |

| D    | E   |

| H    | L   |

# 3.3.6 Register Indirect Addressing

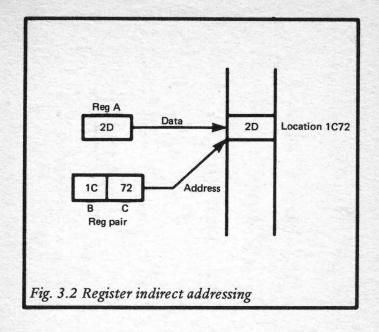

A register pair, being 16 bits in length, can hold a 16 bit address and therefore can be used to indicate a store location. In register indirect addressing a register pair is used to indicate the store location for the data. An example would be "Store the contents of register A in store location whose address is to be found in register pair BC". Suppose A contains 2D (in Hex) and BC contains 1C72 (B is high byte, C is low byte). The number 2D would be stored in location 1C72. This is summarised by Fig.3.2.

Because the address is provided by a register pair, a register direct instruction consists only of an Op Code one or two bytes in length. The code for "Store the contents of A in the store location whose address is to be found in register pair BC" is actually 02.

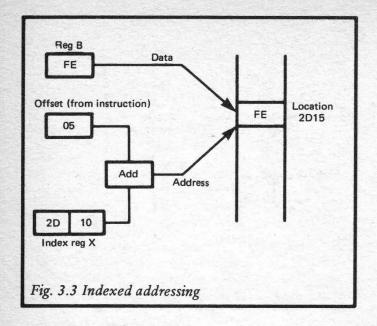

### 3.3.7 Indexed Addressing

Indexed addressing is a special form of register indirect addressing that is particularly useful where tables of data held in successive store locations have to be processed. The Z-80 has two index registers, each 16 bits in length, which provide a base 16 bit address. The instruction contains a two complement offset known as the displacement (in the range -127 to +128) which is added to the base address in an index register

to give the address to be used for the data. For example, we could have "Store register B, index addressed with IX, displacement 05". Let us assume register B contains FE, index register X contains 2D10. The instruction would store FE in location 2D15.

An index address instruction always occupies three locations and consists of a 2 byte Op Code and a 1 Byte displacement:

Op Code (two bytes)

Displacement (one byte)

The coding for "Store register B, index addresses with IX, displace 05" is actually DD 70 05. DD 70 is the Op code, 05 the displacement. (See Fig. 3.3)

### 3.3.8 Relative Addressing

Relative addressing is used only for jumps in the Z-80. The current instruction address is used as a base address, and the instruction contains a twos complement displacement (in the range -128 to +127) to give the jump destination. In the Z-80, slightly confusingly the base address is actually the current location +2. A typical relative addressed instruction is "Jump relative +16" (remember, the displacement 16 is Hex). If we were at location 0C50, the base address is 0C52 and we would jump to the instruction at 0C68. Note that because a twos complement displacement is used we can jump both forward and backward from the current location. All relative addressed instructions use two locations, one for the Op Code and one for the displacement:

Op Code One byte

Displacement One byte

The code for "Jump Relative +16" is 18 16, with 18 the Op Code and 16 the displacement.

Relative addressing is very useful. Apart from being a neat and compact way of writing jumps, it allows programs to be written that can be placed anywhere in the store. These are known as relocatable programs. Usually a programmer builds up a library of relocatable subroutines for common items such as multiplication, division, outputs to printers etc. which can be plugged into each new program as needed. The disadvantage of relative addressing is the tedious recalculation of the displacements if debugging requires the insertion or removal of instructions.

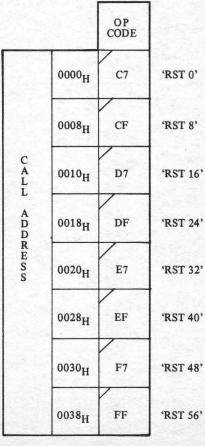

# 3.3.9 Modified Page Zero Addressing

There are 8 page zero addressed instructions. All are subroutine calls known as restarts to addresses below Hex 100. All consist of a single byte Op Code. DF, for example, is "Call subroutine at location Hex 18". The 8 Restart subroutine calls are a very compact way of calling frequently used subroutines.

### 3.3.10 Implied Addressing

Some instructions inherently imply where the data is to be found. Exchange instructions (which switch register sets) are typical implied instructions.

# 3.3.11 Bit Addressing

In data processing and control engineering, single bits in an 8 bit word are used to indicate an event being present or not. A bit could be used, for example, to represent a limit switch being open or closed. In file applications a bit could represent the sex of a person; '1' for male, '0' for female.

The Z-80 has a comprehensive range of bit addressed instructions that allow a single bit in a register or store location to be set, reset or tested (via the flag register, F).

#### 3.3.12 General Observations

We have described ten different address modes, and it is quite possible that the reader is feeling a bit punchdrunk. For completeness, we will list them:

- i. Register Addressing

- ii. Immediate Addressing

- iii. Extended Addressing

- iv. Immediate Extended Addressing

- v. Register Indirect Addressing

- vi. Indexed Addressing

- vii. Relative Addressing

- viii. Modified Page Zero Addressing

- ix. Implied Addressing

- x. Bit Addressing

It is worth noting that almost any program can be written using only the first four modes, and most programs using the first three. The resulting program will certainly not be elegant, fast, or short, but it will work. It is suggested that the would-be programmer simply masters the first three modes, and writes simple programs using them until he (or she) is reasonably competent. At that point mastery of the remainder of the addressing modes should be quite easy, and the programmer can produce more elegant programs.

Not every addressing mode is available on every instruction, so the tables in Chapter 4 should be consulted until the reader

is familiar with the Z-80 instruction set.

#### 3.4 INSTRUCTION TYPES

### 3.4.1 Introduction

Chapter 4 gives the complete Z-80 instruction set in tabular form. This section describes the types of instruction available in a less formal manner. There are just 8 groups of instruction in the Z-80:

- i. Loads

- ii. Arithmetic and Logic

- iii. Jumps and Subroutine calls

- iv. Shifts

- v. Block Transfers

- vi. Bit Manipulation

- vii. Input/Output

- viii. Control

These 8 groups of instructions are combined with the addressing modes described in section 3.3 to give the 158 different instruction types available on the Z-80.

#### 3.4.2 Load Instructions

In Chapter 1 we described the read and write instructions which moved data between registers and the store. In the Z-80, read and write operations and data movements between individual registers are collectively known as "Loads". The following are therefore examples of "Load instructions".

Store the data from register A into store location 0C50. Read the data from store location 12FA to register A. Store the data from register B into the store location whose address is held in register pair HL. Move the data in register D to register C.

# 3.4.3 Arithmetic and Logic Instructions

Almost all Z-80 arithmetic instructions are performed on data in Register A (the accumulator) and data in a store or another register. The result invariably goes to register A. The Z-80 can perform the following 8 bit operations:

- i. Add

- ii. Add with Carry (ADC)

- iii. Subtract

- iv. Sub with Carry (SBC)

- v. AND

vi. Exclusive OR (XOR)

vii. Compare (CP)

viii. Increment

ix. Decrement

Add and Subtract with carry include the carry flag in the operation. Suppose we obey "Add register B to Register A with carry", and register A contains 0101 1010 (5A in Hex), register B contains 0010 0011 (23 in Hex) with the carry flag set we would get:

| 0101 | 1010 | Α           |

|------|------|-------------|

| 0010 | 0011 | В           |

|      | 1    | Carry flag  |

| 0111 | 1110 | Result to A |

If the carry flag is not set we would get:

| 0101 | 1010 | A           |

|------|------|-------------|

| 0010 | 0011 | В           |

|      | 0    | Carry flag  |

| 0111 | 1101 | Result to A |

Incorporating the carry flag into the operation simplifies the writing of the programs with 16 bit numbers.

The simple Add and Subtract instructions ignore the state of the carry flag, and just operate on the two 8 bit words.

All arithmetic operations set (or reset) the S, Z, H, V, N, C flags according to the result of the operations. The P/V flag works on the overflow.

The logical operations AND, OR and XOR are performed bit by bit between data in register A and data in another register, Suppose we have:

| 1010 | 0101 | Register A | (A5 in Hex) |

|------|------|------------|-------------|

| 1001 | 1101 | Register B | (9D in Hex) |

the result of AND is 1 0 0 0 0 1 0 1 (85 in Hex) the result of OR is 1 0 1 1 1 1 0 1 (BD in Hex) the result of XOR is 0 0 1 1 1 0 0 0 (38 in Hex)

In all three operations the result goes to register A, and the

S, Z and P/V flags are set or reset according to the result. The P/V flag works on the parity of the result.

The compare operations is used to compare the data in register A with some other specified data. The operations does not affect the data itself, but sets (or resets) the S, Z, H, V and C flags according to the result (Contents A – Specified Data). If we ask for the instruction Compare Register A, Register B for the data below the flags set would be:

| A  | В  | Flags | Comments. |

|----|----|-------|-----------|

| 06 | 07 | SHNC  | A < B     |

| 07 | 06 | N     | A > B     |

| 06 | 06 | ZN    | A = B     |

Care should be taken if one of the numbers is using bit 8 as a sign bit e.g.

| A  | В  | Flags |

|----|----|-------|

| FF | 01 | SN    |

| 01 | FF | HNC   |

Usually the compare instruction is used to test for equality (e.g. the Z flag set) and is invariably followed by a conditional jump or subroutine call on the state of the Z flag.

Increment and Decrement are useful instructions. Increment takes some specified data, adds '1' to it and places the result back again. Decrement operates in a similar manner except that '1' is subtracted. The data can be obtained from any register or (using register indirect or indexed addressing) any store location. The following are typical increment instructions:

Add 1 to Register C

Add 1 to the contents of the store location whose address is in HL

The following are typical decrement instructions:

Subtract 1 from Register E

Subtract 1 from the contents of the store location (index register X + 5)

Note that unlike all other arithmetic operations, the result goes back to the source of the data and *NOT* to register A. Increment and decrement instructions are a convenient way of counting events.

### 3.4.4 Jumps and Subroutine Calls

The idea of jump instructions and subroutine calls was introduced in Chapter 1. The Z-80 has a very useful range of conditional jumps and subroutine calls and returns. The conditions tested are based on the flags in the F register and are:

Carry Set, Carry Not Set, Accumulator Zero, Accumulator Non Zero, Parity Even, Parity Odd, Sign Negative, Sign Positive.

The majority of these instructions use extended addressing (e.g. CC 70 0F, call subroutine starting at location 0F 70 if the accumulator is zero). There are also a few jump instructions using relative addressing and three unconditional jump instructions using register indirect addressing.

Subroutine calls use the stack pointer to store the current value of the program counter, and return instructions reinstate the value from the stack back to the program counter at the end of the subroutine. The stack operation was described in section 2.2.4.

#### 3.4.5 Rotates and Shifts

A shift instruction simply moves the bit pattern in a register one place to the left or right. Suppose we had

1010 0111 (A7 in Hex)

A simple shift to the left would give

0100 1110 (4E in Hex)

A simple shift to the right would give

0101 0011 (53 in Hex)

In each case the bit pushed off the end is "lost", and a zero

placed at the other end. These are known as a logical shift.

Consider the simple bit pattern 0101, which is five in decimal. If the pattern is shifted one place to the left (called shifting up) we get 1010 which is ten in decimal. A shift up is equivalent to multiplying by two providing the top bit is not shifted off the end.

Similarly, if we have the bit pattern 1100, which is twelve in decimal and shift it one place to the right (called shifting down) we get 0110 which is six in decimal. A shift down is equivalent to a division by two.

A simple shift will, however, give the wrong result on signed number. If twos complement representation is used, bit 7 represents the sign, being a '1' for negative numbers and '0' for positive numbers. We thus have:

| 1111 | 1000 | (-8 decimal) |

|------|------|--------------|

| 1111 | 1100 | (-4 decimal) |

| 1111 | 1110 | (-2 decimal) |

| 1111 | 1111 | (-1 decimal) |

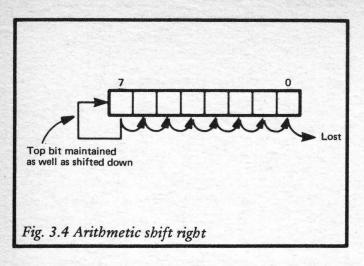

Although we are dividing by two by shifting to the right, it is not a simple shift because the sign bit must be maintained. This is known as an arithmetic shift, and can be summarised by Fig. 3.4.

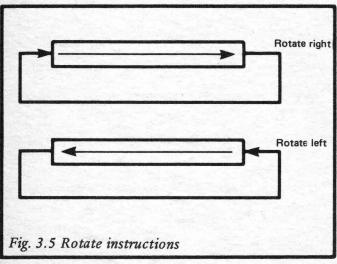

Rotate instructions are very similar to shifts. In a rotate instruction the 'lost' bit is simply fed into the opposite end of the register as shown on Fig.3.5. The effect of successive rotate rights would therefore be:

| start        | 0110 | 0101 |

|--------------|------|------|

| rotate right | 1011 | 0010 |

| rotate right | 0101 | 1001 |

| rotate right | 1010 | 1100 |

| etc          |      |      |

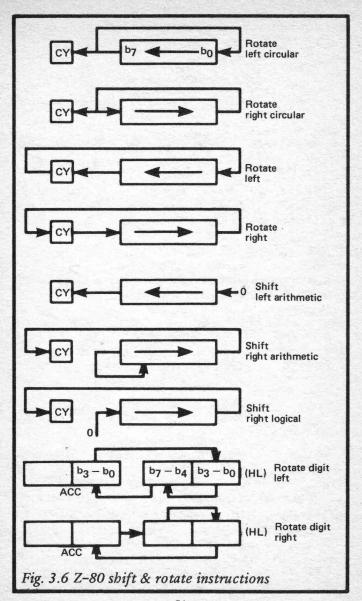

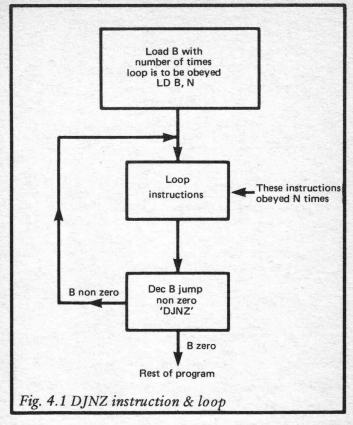

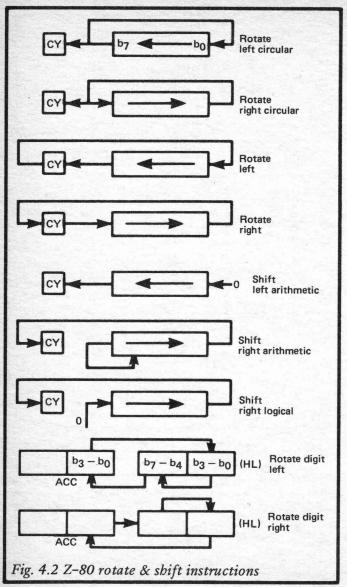

The Z-80 has seven types of rotate and shift instructions. These all incorporate the carry flag as shown on Fig.3.6. These operations can be performed on every general purpose register and (using register indirect or indexed addressing) on store contents.

Shift instructions are the basis for writing multiplication

and division routines, and both shifts and rotates are widely used where individual bits are used to represent data in control applications or data processing as described in section 3.3.11.

'0' = zero

CY = carry flag

(HL) = store location whose

address is held in HL

ACC = register A (i.e. Accumulator)

Fig. 3.6 (b)

#### 3.4.6 Block Transfer

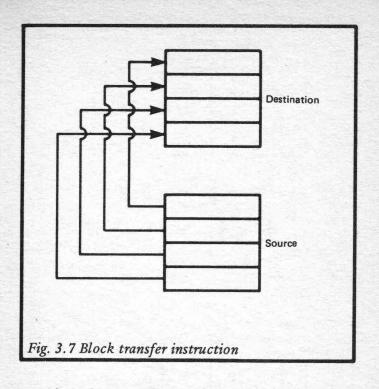

The Z-80 has a unique set of block transfer instructions. These allow "blocks" of data to be moved around the store with just a few instructions. These instructions all involve the register pairs HL, DE, BC.

Register pair HL contains the 16 bit address where the first item of data is to be found.

Register pair DE contains the 16 bit address where the first item is to be stored.

Register pair BC is a 16 bit counter used to define how many words are to be moved.

If HL contained, say, 0C50, DE, 2000 and BC 100, a block transfer instruction would move 100 (Hex) words from 0C50 to 2000 and succeeding locations as summarised on Fig.3.7.

The contents of 0C50 would go to 2000

0C51 to 2001

0C52 to 2002 and so on for 100

locations.

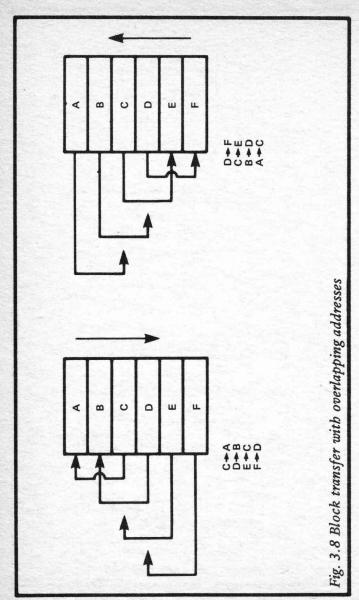

There are four block transfer instructions. The first two operate as above, and are known as "load increment repeat, (LDIR)" and "load decrement repeat, (LDDR)". These operate as above, except LDIR works up the store and LDDR works down the store allowing data to be transferred between overlapping locations as shown on Fig. 3.8.

The two remaining block transfer instructions transfer one word each time the instruction is obeyed, but set up HL, DE and BC ready for the next transfer. These allow other instructions to be incorporated in the block transfer operation. An

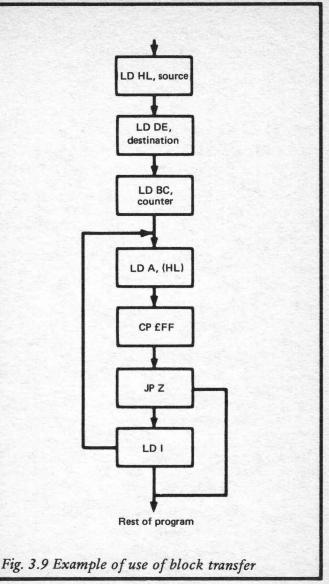

example is shown on Fig.3.9 which is a flow chart for an operation which transfers a block of data, terminating either when the full block is transferred or a word containing "FF" (Hex) is found. As before, an incrementing and decrementing instruction is provided to allow data to be transferred between overlapping locations. The instructions are known as "Load decrement (LDD)" and "Load increment (LDI)".

The Z-80 also has four powerful block search instructions which allow an area of store to be compared with the accumulator contents. HL contains the start address, and BC is a counter indicating the number of locations to be searched. As before, the search can be conducted up or down the store, and can be conducted one word at a time (compare increment (CPI) and compare decrement (CPD)) or at one go with one

instruction (compare increment repeat (CPIR) and compare decrement repeat (CPDR)). If a match is found, HL indicates the address.

The block transfer and search instructions are a somewhat advanced technique, but are very useful for handling files and text.

# 3.4.7 Bit Manipulation

The Z-80 has a comprehensive range of instructions to allow individual bits in registers and store locations to be set, reset and tested. These instructions are particularly useful in control and data handling applications. Register indirect (using HL) and indexed addressing is used for accessing store locations. Bit tests set or reset the zero flag in the F register (Z flag set if tested bit is zero). An example of a bit manipulation instruction is CB 5E which tests bit 3 in the store location whose address is held in register pair HL.

# 3.4.8 Input/Output

The basis of input/output instructions were described in section 1.5. In a Z-80 based microcomputer, up to 256 I/O ports can be addressed. An I/O instruction has to define:

- i. The port address (8 bits)

- ii. The direction (input or output)

- iii. The store location or register which is the source (or destination) of the data.

The Z-80 uses direct addressing and register indirect addressing to specify the port number. D3 05, for example is "output one word to port 5 from register A" (using direct addressing). All indirect addressing is done with register C holding the address. An example of an indirect addressed I/O instruction is ED 60 which is "Input one word from the port whose address is held in register C to register H".

There are also a useful range of block transfer I/O instructions which transfer large chunks of data between sequential store locations and an I/O port. These operate in a similar

manner to the block transfer instructions described previously in section 3.4.6.

Register pair HL contains the store address Register B contains the byte counter Register C contains the port address

The block transfer instructions are particularly useful for inputting data from (say) a tape recorder or sending data to a printer.

We will return to I/O instructions again in Chapter 6 where I/O support devices are described and section 6.4 where the operation of interrupts is discussed.

#### 3.4.9 Control Instructions

There are six Z-80 control instructions. Four of these are concerned with the operations of interrupts (described further in section 6.4). The remaining two are "Halt" and the dummy "No operation".

#### 3.4.10 General Observations

We have described the Z-80 instructions in very general terms. In Chapter 4 the full instructions set is given in a formal manner.

### 3.5 SYMBOLIC REPRESENTATION

It is very laborious to describe instructions in a descriptive manner such as "Fetch to register A the contents of the store location whose address is held in register pair HL". A simple, logical symbolism is used to represent instructions in the Z-80 (and other) microprocessors. Typical instructions are represented as.

$$A \leftarrow A + 1$$

$A \leftarrow A + (HL)$

Let us see what these symbols mean, and how they

represent an instruction.

Registers are represented by their letters (A, B, C, etc.). Numbers are simply represented by their hex equivalent; 19, C5 for example. The arrow  $\leftarrow$  shows the data movement, so:

$A \leftarrow B$  means move the contents of register B to register A

C ← 37 means load register C with the hex number 37 (immediate addressing)

Arithmetic operations are represented by these symbols:

+ addition

subtraction

$\wedge$  and

V or

⊕ exclusive or

We can thus write:

A ← A + 1 Add 1 to the contents of register A A ← A + B Add the contents of register A and B, result to register A

The contents of store locations are represented by brackets ( ). We therefore interpret (0C50) to mean the contents of store location 0C50. Care should be taken, since FFE1 means a 16 bit humber as in:

HL ← FFE1 means load register pair HL with hex number FFE1 (immediate addressing)

(FFE1)means the contents of store location FFE1 as in:

(FFE1) ← B which is store the contents of register B in store location FFE1.

Register indirect and indexed addressing are also represented by () since they refer to store locations. For example:

B ← (HL) is bring contents of the store location whose address is held in register pair HL to register B (register indirect addressing) A ← A + (IX + 3) Add the contents of register A to the contents of the store location whose address is given by adding 3 to the contents of the index register, the result to go to register A.

The last example shows the simplicity of the symbolism!

Even jump instructions can be represented. A simple jump is:

PC ← 1DAF Jump to location 1DAF (PC stands for program counter)

A subroutine call to a subroutine at F6000 is represented by the three symbols:

$$(SP-1) \leftarrow PC_H$$

,  $(SP-2) \leftarrow PC_L$  ;  $PC \leftarrow F6000$

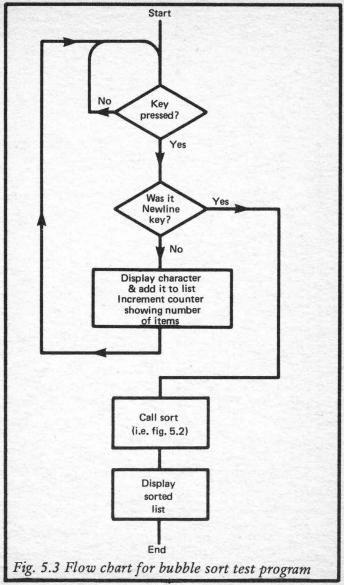

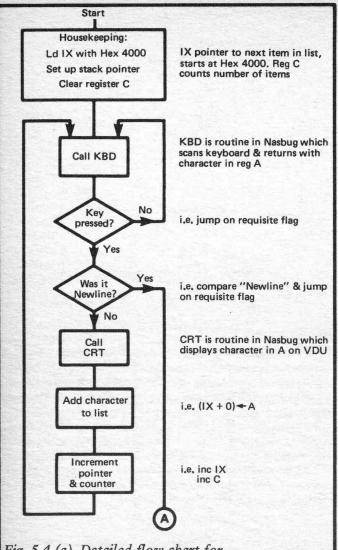

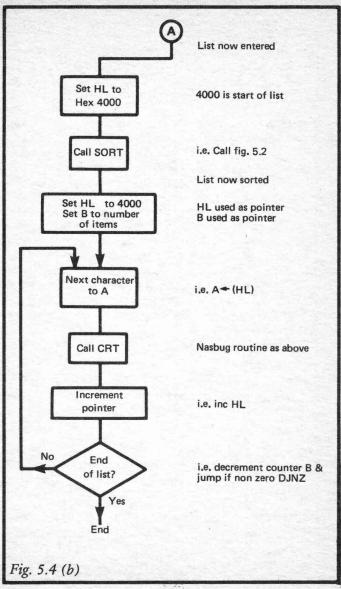

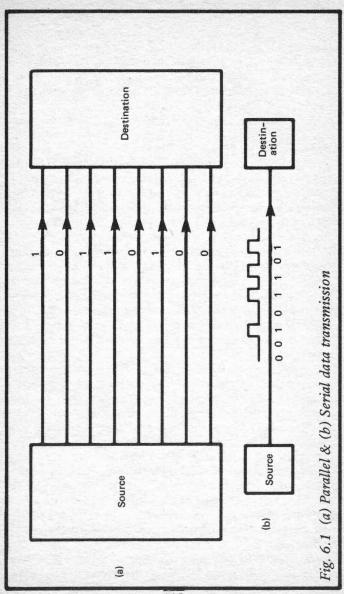

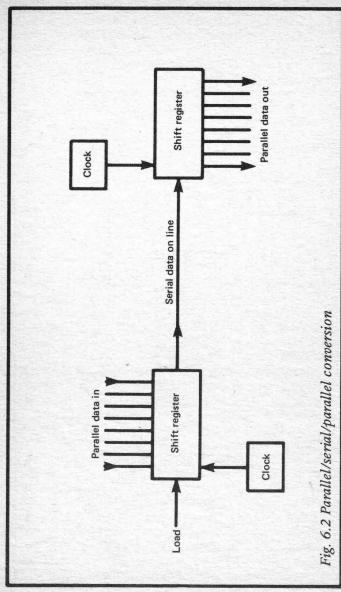

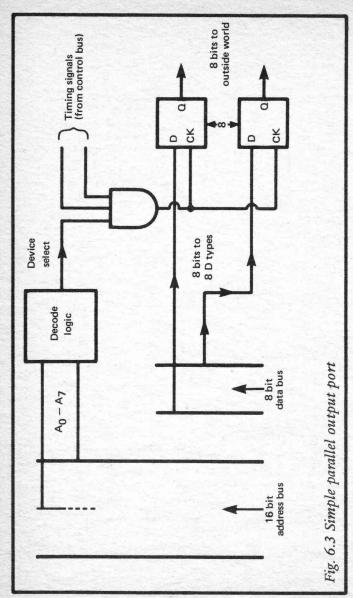

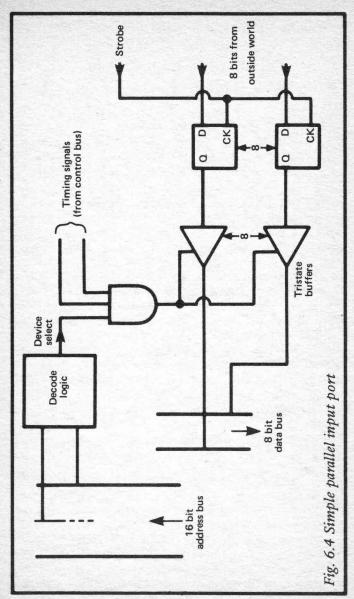

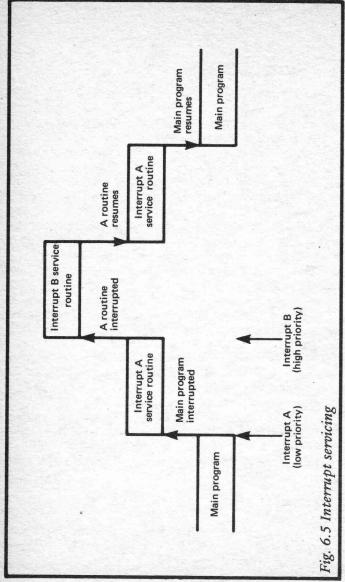

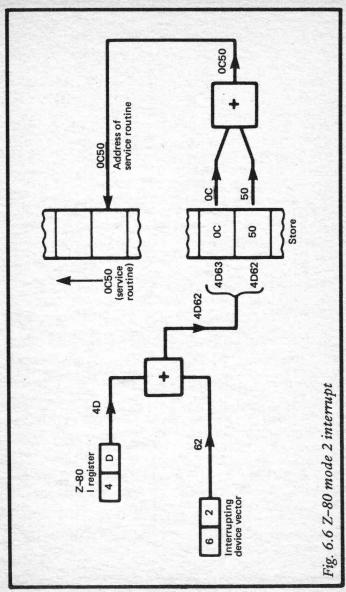

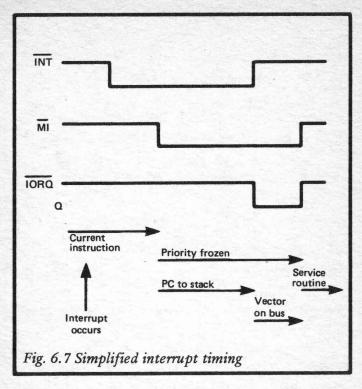

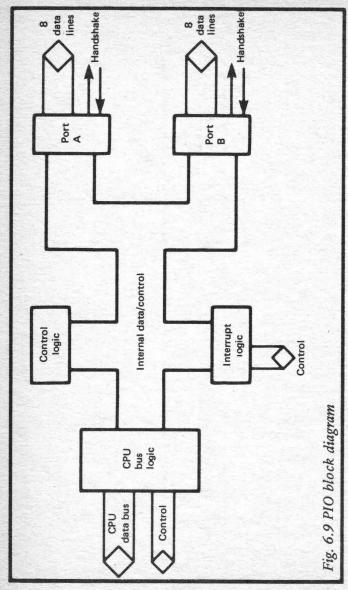

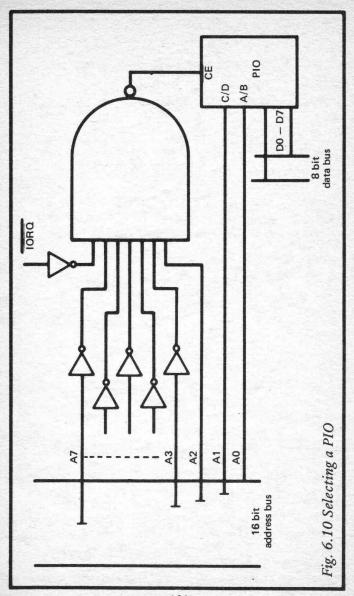

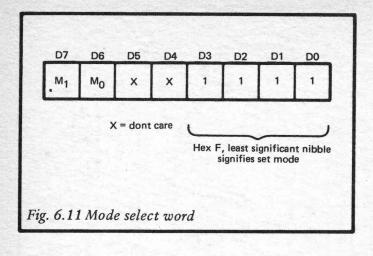

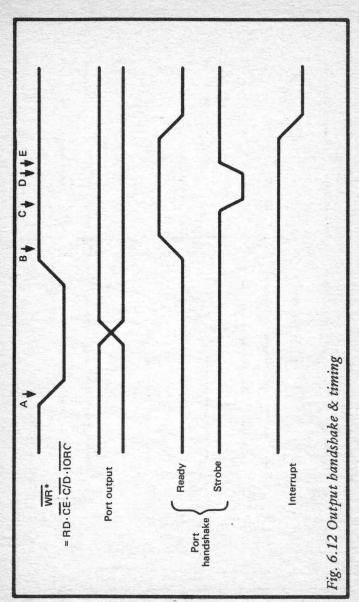

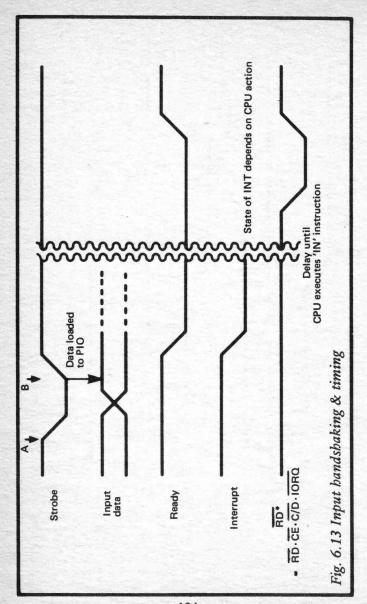

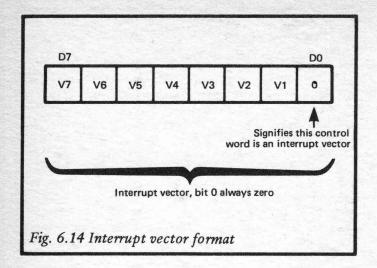

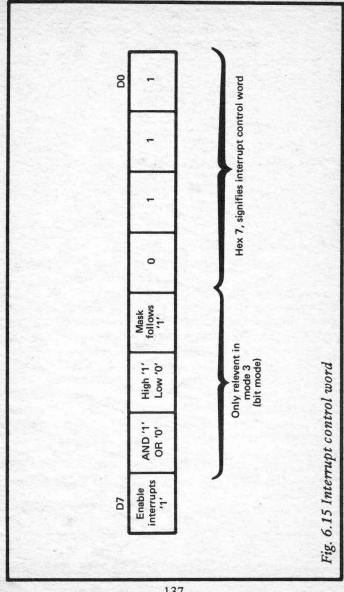

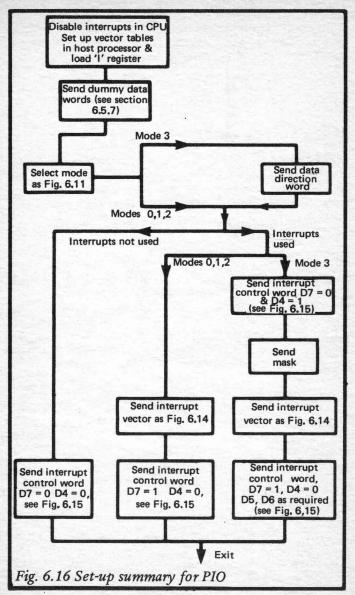

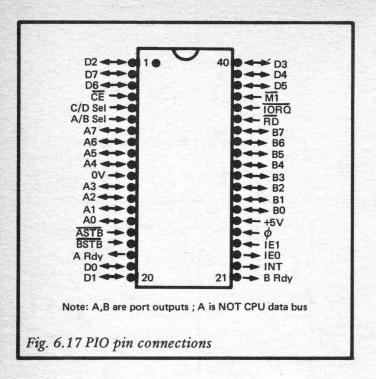

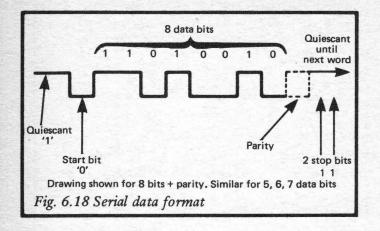

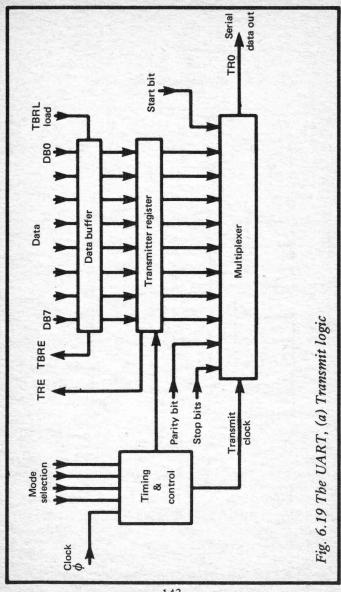

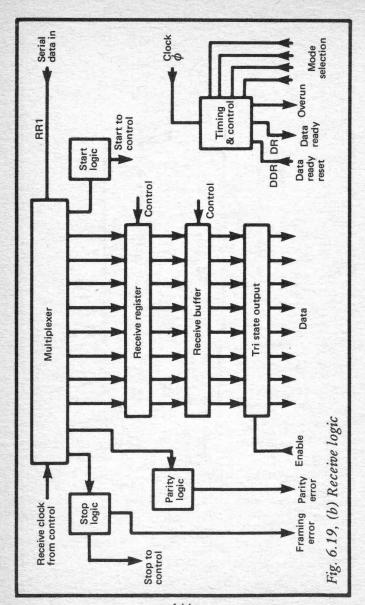

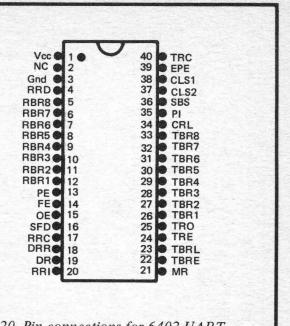

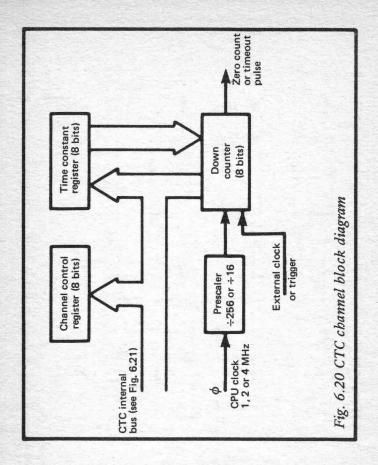

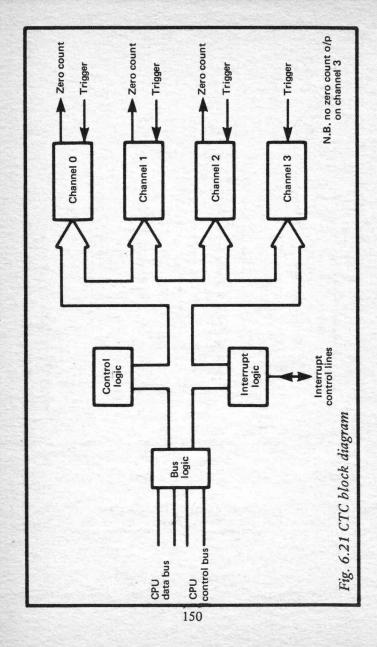

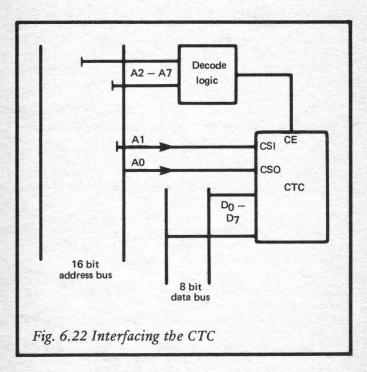

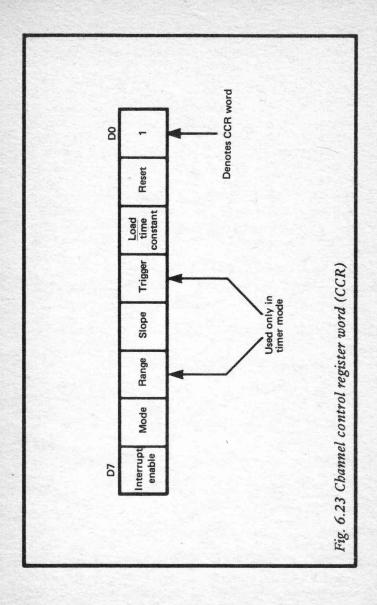

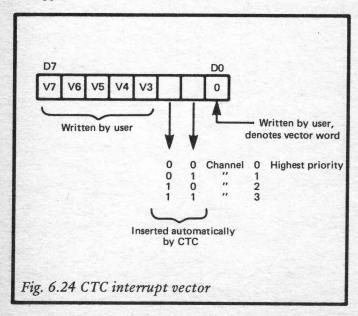

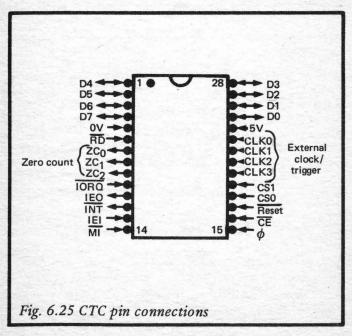

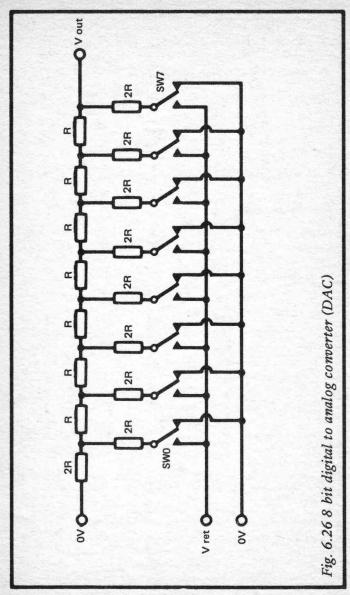

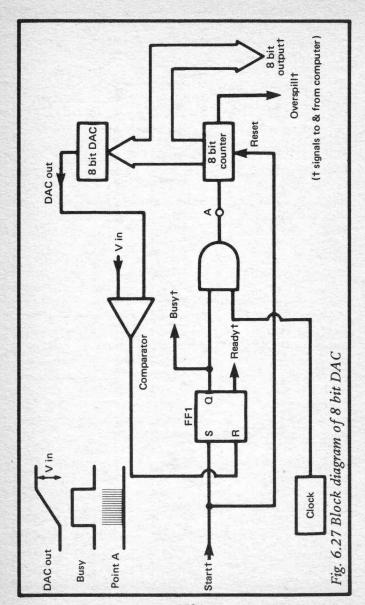

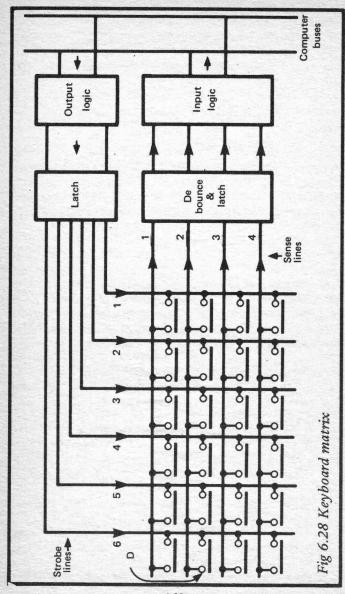

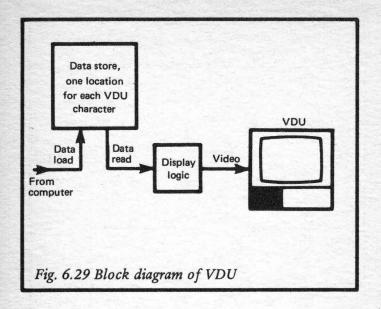

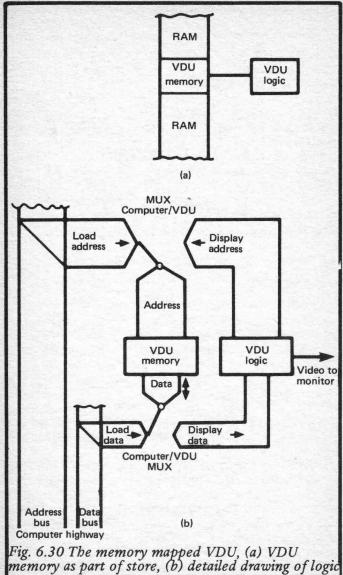

SP refers to the stack pointer, PC<sub>H</sub> is the high byte of the program counter, PC<sub>L</sub> is the low byte of the program counter.