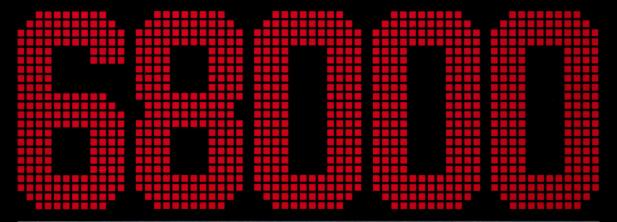

# 68000 ASSEMBLY LANGUAGE PROGRAMMING BY GERRY KANE, DOUG HAWKINS & LANCE LEVENTHAL

PREÇO:

MÊS:

# 1895 OF 80

# 68000 Assembly Language Programming

# 68000 Assembly Language Programming

Gerry Kane

Doug Hawkins

Lance Leventhal

Published by Osborne/McGraw-Hill 2600 Tenth Street Berkeley, California 94710 U.S.A.

For information on translations and book distributors outside of the U. S. A., please write OSBORNE/McGraw-Hill at the above address.

#### **68000 ASSEMBLY LANGUAGE PROGRAMMING**

Copyright © 1981 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

567890 DODO 89876543

ISBN 0-931988-62-4

Cover design by Timothy Sullivan.

Technical editor on this book was Joaquin Miller.

## Acknowledgments

We gratefully acknowledge Motorola Microsystems, Mesa, Arizona and, in particular, Jeff Lavell, their former General Manager, for supplying equipment and information needed to write this book.

Special thanks go to Mr. Hans Kalldall for his excellent work in testing all of the example programs. Mr. Kalldall also suggested numerous corrections and improvements which greatly enhanced this book.

Doug Hawkins wishes to express his gratitude to his loving wife Peggy for the assistance, support, patience and understanding she provided throughout this project.

#### **About the Authors**

Gerry Kane, a member of Osborne/McGraw-Hill's technical staff, is co-author of several volumes of the well-known series, An Introduction to Microcomputers. Most recently, he authored the CRT Controller Handbook and the 68000 Microprocessor Handbook, both part of the new Osborne Handbook Series. He received his B.S. degree from the United States Coast Guard Academy.

Doug Hawkins is Vice President of Engineering for Phoenix Digital Corporation, Phoenix, Arizona with responsibility for the design and implementation of microprocessor-based systems for distributive plant monitoring and process control. Previously, Mr. Hawkins worked for Motorola Microsystems, the primary source for the MC68000, as Manager of Language Systems. He received his BSEE degree from Michigan State University, and MSEE and MBA degrees from Arizona State University.

Lance Leventhal is a partner in Emulative Systems Company, Inc., a San Diego-based consulting firm specializing in microprocessors and microprogramming. He is a national lecturer on microprocessors for the IEEE, the author of ten books and over sixty articles on microprocessors, and a regular contributor to such publications as Simulation and Microcomputing. He also serves as technical editor for the Society for Computer Simulation and as contributing editor for Digital Design magazine.

Dr. Leventhal authored the original books in this series and has just begun work on a new series, Assembly Language Subroutines. He received a B.A. degree from Washington University in St. Louis, and M.S. and Ph.D. degrees from the University of California at San Diego. He is a member of SCS, ACM, IEEE, and the IEEE Computer Society.

#### **Contents**

#### Section I. Fundamental Concepts

#### 1. Introduction Assembly Language Programming

A Computer Program 1-2 High-Level Languages 1-8

#### 2. Assemblers

Features of Assemblers 2-1 Types of Assemblers 2-15 Errors 2-16 Loaders 2-17

#### 3. 68000 Machine Structure and Assembly Language

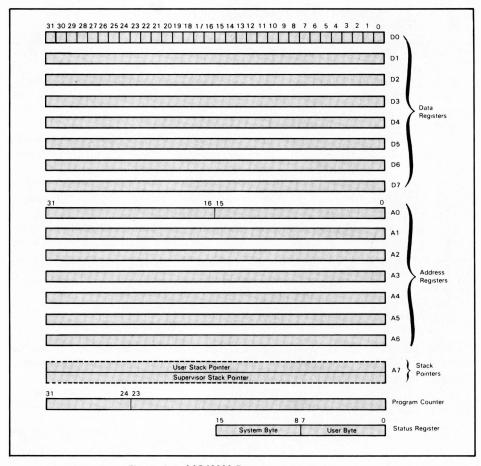

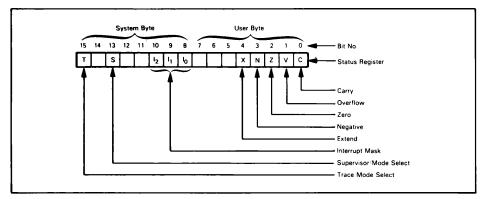

MC68000 Operating Modes 3-3

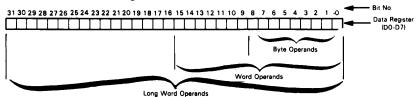

MC68000 Registers and Flags 3-3

MC68000 Memory 3-6

MC68000 Addressing Modes 3-7

MC68000 Addressing Modes 3-7

Addressing Modes Which Do Not

Specify Memory Locations 3-8

Memory Addressing Modes 3-11

MC68000 Instruction Set 3-31

#### Section II. Introductory Problems

#### 4. Beginning Programs

Program Examples 4-1 Problems 4-13

#### 5. Simple Program Loops

Program Examples 5-3 Problems 5-18

#### 6. Character-Coded Data

Handling Data in ASCII 6-1 Program Examples 6-3 Problems 6-19

#### 7. Code Conversion

Program Examples 7-2 Problems 7-13

#### 8. Arithmetic Problems

Multiple-Word and

Decimal Arithmetic 8-1

Program Examples 8-2

Problems 8-14

#### 9. Tables and Lists

Program Examples 9-1 Problems 9-21

#### **Section III. Advanced Topics**

#### 10. Parameter Passing Techniques

#### 11. Subroutines

Program Examples 11-2

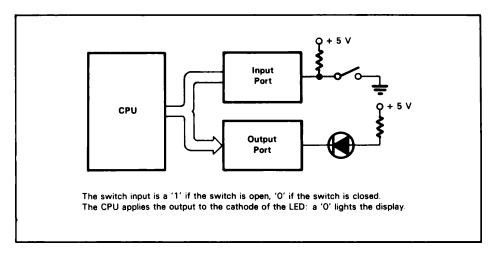

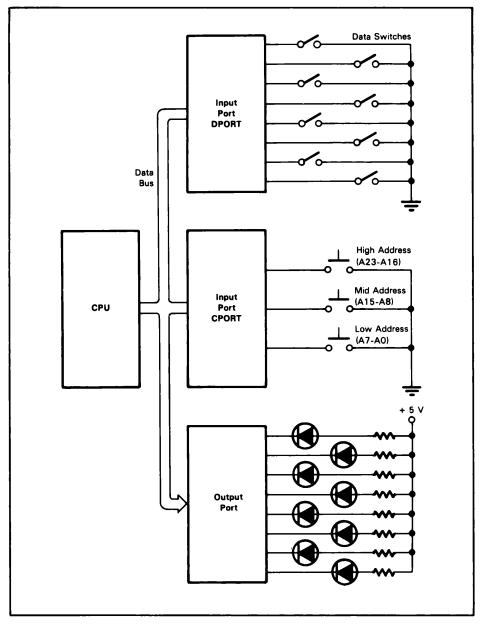

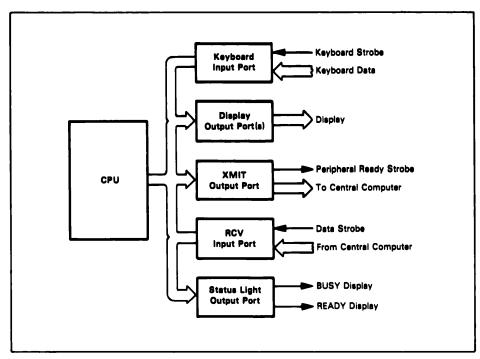

#### 12. Input/Output

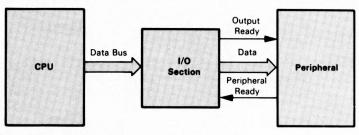

I/O Device Categories 12-2

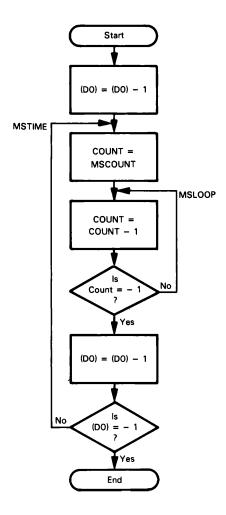

Time Intervals 12-8

Logical and Physical Devices 12-12

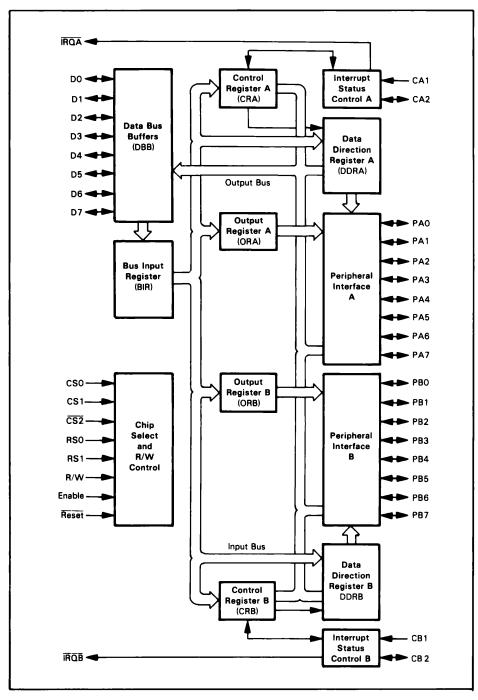

MC68000 Input/Output Chips 12-13

#### 13. Using the 6820 Peripheral Interface Adapter (PIA)

Initializing a PIA 13-6

Using the PIA to Transfer Data 13-11

Program Examples 13-1

More Complex I/O Devices 13-31

Some Final Tips on I/O 13-61

Problems 13-61

## 14. Using the 6850 Asynchronous Communications Interface Adapter (ACIA) Program Examples 14-5

#### 15. Interrupts and Other Exceptions

The MC68000 Exception Processing System 15-3 Program Examples 15-11 More General Service Routines 15-31

#### Section IV. Software Development

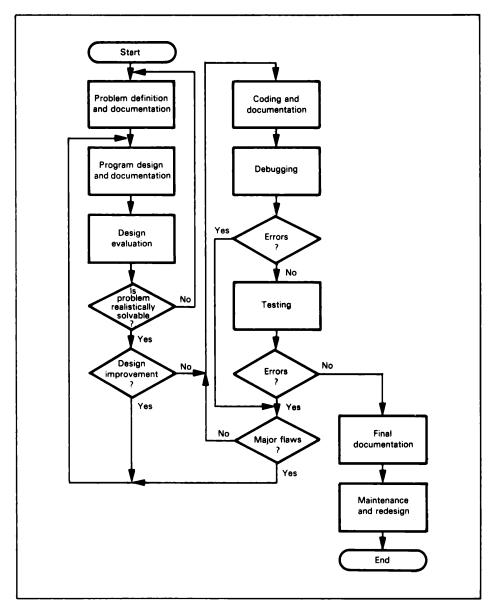

#### 16. Problem Definition

Inputs 16-1

Outputs 16-2

Processing Section 16-2

Error Handling 16-2

Human Factors/Operator Interaction 16-3

Examples 16-4

Review 16-14

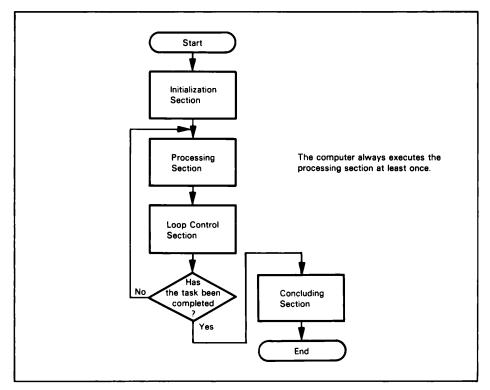

#### 17. Program Design

Basic Principles 17-1

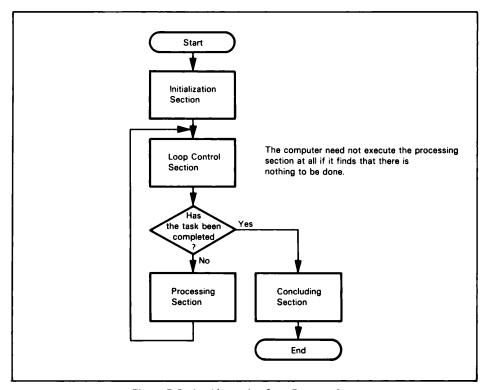

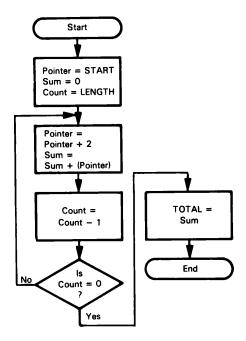

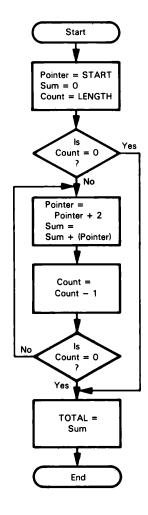

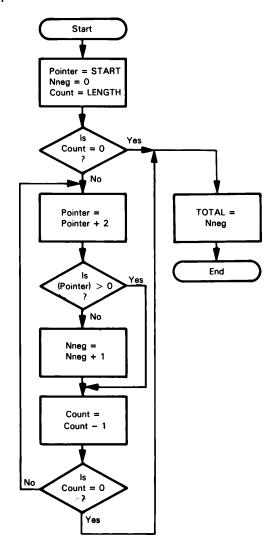

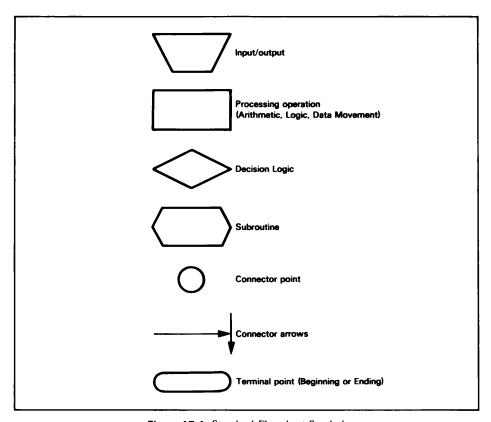

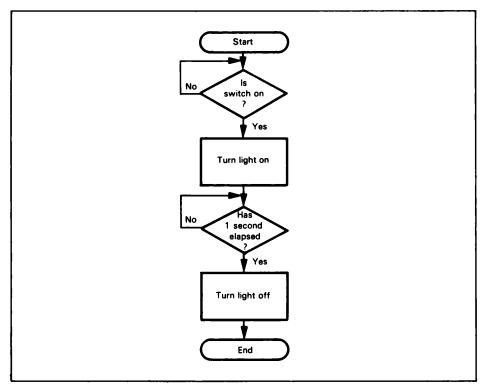

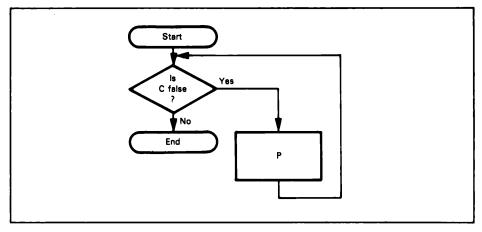

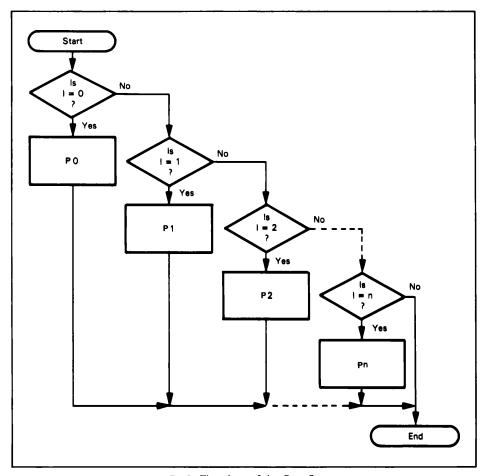

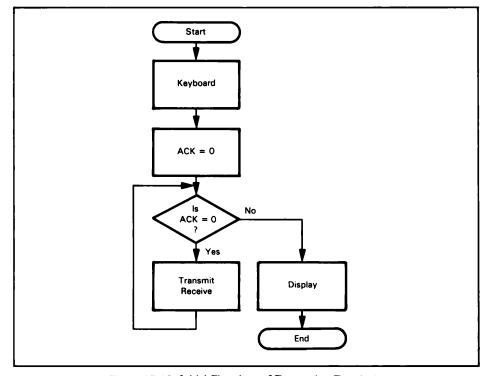

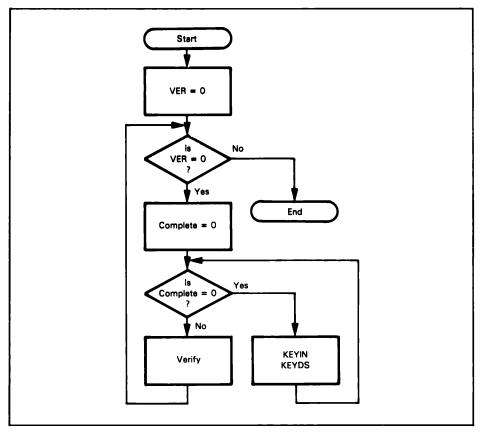

Flowcharting 17-2

Modular Programming 17-11

Structured Programming 17-15

Top-Down Design 17-27

Designing Data Structures 17-32

Review of Problem Definition and Program Design 17-33

#### 18. Documentation

Comments 18-2

Flowcharts as Documentation 18-8

Structured Programs as Documentation 18-8

Memory Maps 18-9

Library Routines 18-10

Total Documentation 18-11

#### 19. Debugging

Simple Debugging Tools 19-2 Advanced Debugging Tools 19-10 Debugging With Checklists 19-12 Looking for Errors 19-13 Examples 19-21

#### 20. Testing

Selecting Test Data 20-2 Examples 20-4 Rules for Testing 20-4 Conclusions 20-5

#### 21. Maintenance and Redesign

Saving Memory 21-2

Saving Execution Time 21-3

Major Reorganization 21-4

#### Section V. 68000 Instruction Set

#### 22. The Instruction Set

#### Section VI. Appendices

- A. Summary of the 68000 Instruction Set

- B. 68000 Instruction Codes, Memory Requirements, and Execution Times

- C. 68000 Instruction Object Codes in Numerical Order

#### Index

#### **Program Examples**

- 4-1. 64-Bit Data Transfer 4-13

- 4-2. 16-Bit Subtraction 4-13

- 4-3. Shift Right Three Bits 4-14

- 4-4. Word Assembly 4-14

- 4-5. Find Smallest of Three Numbers 4-14

- 4-6. Sum of Squares 4-14

- 4-7. Shift Left Variable Number of Bits 4-15

- 5-1. Checksum of Data 5-18

- 5-2. Number of Zero, Positive and Negative Numbers 5-18

- 5-3. Find Minimum 5-19

- 5-4. Count 1 Bits 5-19

- 5-5. Find Element with Most 1 Bits 5-19

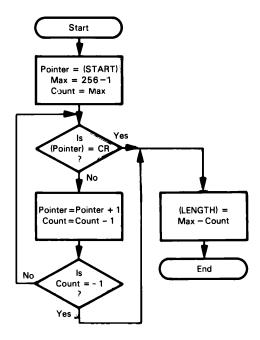

- 6-1. Length of a Teletypewriter Message 6-19

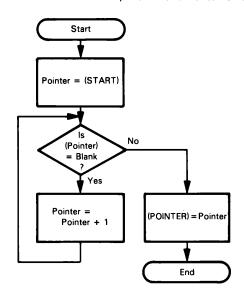

- 6-2. Find Last Non-Blank Character 6-19

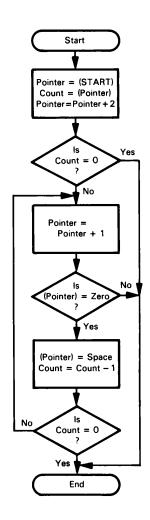

- 6-3. Truncate Decimal Strings to Integer Forms 6-20

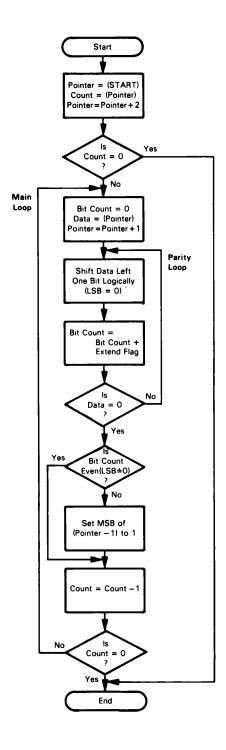

- 6-4. Check Even Parity and ASCII Characters 6-20

- 6-5. String Comparison 6-21

- 7-1. ASCII to Hexadecimal 7-13

- 7-2. Seven-Segment to Decimal 7-13

- 7-3. Decimal to ASCII 7-13

- 7-4. Binary to BCD 7-14

- 7-5. ASCII String to Binary Number 7-14

- 8-1. Multiple Precision Binary Subtraction 8-14

- 8-2. Decimal Subtraction 8-14

- 8-3. 32-Bit by 32-Bit Multiply 8-15

- 9-1. Remove Entry from List 9-21

- 9-2. Add Entry to Ordered List 9-22

- 9-3. Add Element to Queue 9-22

- 9-4. 4-Byte Sort 9-23

- 9-5. Using a Jump Table with a Key 9-24

- 11-1. Converting Hexadecimal to ASCII 11-3

- 11-2. Hex Word to ASCII String 11-6

- 11-3. 64-Bit Addition 11-9

- 11-4. Factorial of a Number 11-11

- 13-1. An On-Off Pushbutton 13-61

- 13-2. Debouncing a Switch in Software 13-61

- 13-3. Control for a Rotary Switch 13-62

- 13-4. Record Switch Positions on Lights 13-62

- 13-5. Count on a Seven-Segment Display 13-63

- 13-6. Separating Closures from an Unencoded Keyboard 13-63

- 13-7. Read a Sentence from an Unencoded Keyboard 13-63

- 13-8. A Variable Amplitude Square Wave Generator 13-63

- 13-9. Averaging Analog Readings 13-64

- 13-10. A 30 Character-Per-Second Terminal 13-64

- 14-1. Receive Data from TTY 14-5

- 14-2. Send Data to TTY 14-6

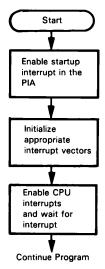

- 15-1. Startup 15-11

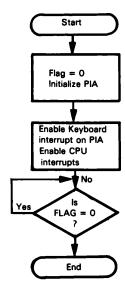

- 15-2. A Keyboard Interrupt 15-14

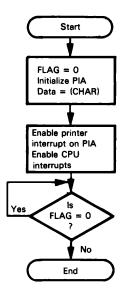

- 15-3. A Printer Interrupt 15-17

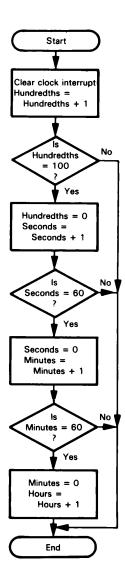

- 15-4. A Real-Time Clock Interrupt 15-21

- 15-5. A Teletypewriter Interrupt 15-26

- 15-6. A Supervisor Call 15-28

- 15-7. Entering User Mode 15-30

- 19-1. Debugging a Code Conversion Program 19-21

- 19-2. Debugging a Sort Program 19-27

## **Fundamental Concepts**

This book describes assembly language programming. It assumes that you are familiar with An Introduction to Microcomputers: Volume 1 — Basic Concepts (Berkeley: Osborne/McGraw-Hill, 1980). Chapters 6 and 7 of that book are especially relevant. This book does not discuss the general features of computers, microcomputers, addressing methods, or instruction sets; you should refer to An Introduction to Microcomputers: Volume 1 for that information.

The chapters in this section provide basic information on assembly language in general and the MC68000 in particular. Chapter 1 discusses the purpose of assembly language and compares it with higher level computer languages. Chapter 2 discusses assemblers and, briefly, loaders. Chapter 3 describes the architecture of the MC68000 microprocessor, compares it with similar processors, and discusses important features of Motorola's MC68000 assemblers.

#### **HOW THIS BOOK HAS BEEN PRINTED**

This book contains both boldface and lightface type. The material in lightface type only expands on information presented in the previous boldface type. Thus you can skip subject areas with which you are familiar by skipping the material in lightface type. When you reach an unfamiliar subject, read both the material in boldface type and the material in lightface type.

# Introduction to Assembly Language Programming

A computer program is ultimately a series of numbers and therefore has very little meaning to a human being. In this chapter we will discuss the levels of human-like language in which a computer program may be expressed. We will also discuss the reasons for and uses of assembly language, which is the subject of this book.

#### THE MEANING OF INSTRUCTIONS

The instruction set of a microprocessor is the set of binary inputs that produce defined actions during an instruction cycle. An instruction set is to a microprocessor what a function table is to a logic device such as a gate, adder, or shift register. Of course, the actions that the microprocessor performs in response to its instruction inputs are far more complex than the actions that logic devices perform in response to their inputs.

#### **Binary Instructions**

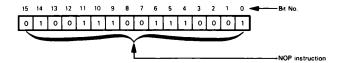

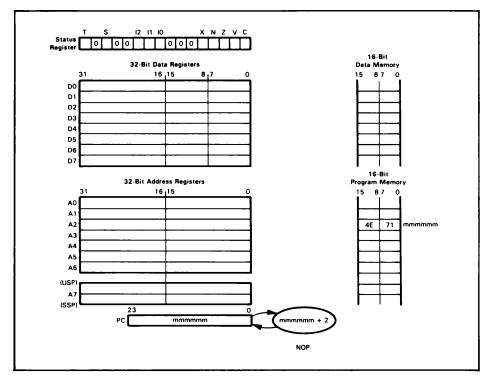

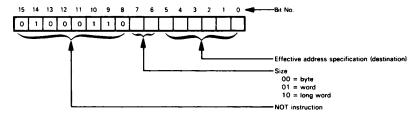

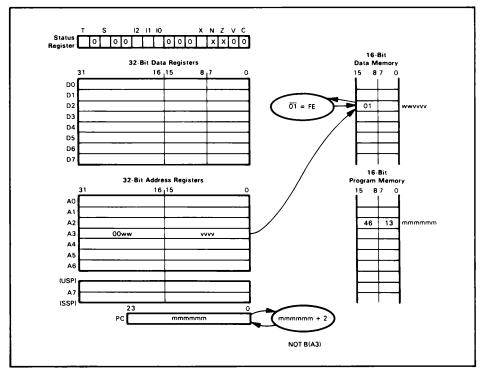

An instruction is a binary digit pattern — it must be available at the data inputs to the microprocessor at the proper time in order to be interpreted as an instruction. For example, when the MC68000 microprocessor receives the 16-bit binary pattern 1101001100000000 as the input during an instruction fetch operation, the pattern means:

"Add the contents of Data Register D0 to Data Register D1."

Similarly, the pattern 0001000000111010000000011111111 means:

"Move 11111111 into Data Register DO."

The microprocessor (like any other computer) only recognizes binary patterns as instructions or data; it does not recognize characters or octal, decimal, or hexadecimal numbers.

#### A COMPUTER PROGRAM

A program is a series of instructions that causes a computer to perform a particular task.

Actually, a computer program includes more than instructions; it also contains the data and the memory addresses that the microprocessor needs to accomplish the tasks defined by the instructions. Clearly, if the microprocessor is to perform an addition, it must have two numbers to add and a place to put the result. The computer program must determine the sources of the data and the destination of the result as well as the operation to be performed.

All microprocessors execute instructions sequentially unless an instruction changes the order of execution or halts the processor. That is, the processor gets its next instruction from the next higher memory address unless the current instruction specifically directs it to do otherwise.

Ultimately, every program is a set of binary numbers. For example, this is a MC68000 program that adds the contents of memory locations 6000<sub>16</sub> and 6002<sub>16</sub> and places the result in memory location 6004<sub>16</sub>:

> 0011000000111000 01100000000000000 11010000011111000 01100000000000010 0011000111000000 0110000000000100

This is a machine language, or object, program. If this program were entered into the memory of a MC68000-based microcomputer, the microcomputer would be able to execute it directly.

#### THE BINARY PROGRAMMING PROBLEM

There are many difficulties associated with creating programs as object, or binary machine language, programs. These are some of the problems:

- · The programs are difficult to understand or debug. (Binary numbers all look the same, particularly after you have looked at them for a few hours.)

- The programs are slow to enter since you must set a front panel switch for each bit and load memory one word at a time.

- · The programs do not describe the task which you want the computer to perform in anything resembling a human-readable format.

- The programs are long and tiresome to write.

- · The programmer often makes careless errors that are very difficult to locate and correct.

For example, the following version of the addition object program contains a single bit error. Try to find it:

```

0011000000111000

01100000000000000

1100000001111000

01100000000000010

0011000111000000

01100000000000100

```

Although the computer handles binary numbers with ease, people do not. People find binary programs long, tiresome, confusing, and meaningless. Eventually, a programmer may start remembering some of the binary codes, but such effort should be spent more productively.

#### **USING OCTAL OR HEXADECIMAL**

We can improve the situation somewhat by writing instructions using octal or hexadecimal numbers, rather than binary. We will use hexadecimal numbers in this book because they are shorter, and because they are the standard for the microprocessor industry. Table 1-1 defines the hexadecimal digits and their binary equivalents. The MC68000 program to add two numbers now becomes:

At the very least, the hexadecimal version is shorter to write and not quite so tiring to examine.

| Equivalent | Decimal<br>Equivalent                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------|

| 0000       | 0                                                                                                     |

| 0001       | 1                                                                                                     |

| 0010       | 2                                                                                                     |

| 0011       | 3                                                                                                     |

| 0100       | 4                                                                                                     |

| 01 '       | 5                                                                                                     |

| 01 ا 0     | 6                                                                                                     |

| 0111       | 7                                                                                                     |

| 1000       | 8                                                                                                     |

| 1001       | 9                                                                                                     |

| 1010       | 10                                                                                                    |

| 1011       | 11                                                                                                    |

| 1100       | 12                                                                                                    |

| 1101       | 13                                                                                                    |

| 1110       | 14                                                                                                    |

| 1111       | 15                                                                                                    |

|            | 0000<br>0001<br>0010<br>0011<br>0100<br>01 '<br>01 10<br>0111<br>1000<br>1001<br>1010<br>1011<br>1110 |

Table 1-1. Hexadecimal Conversion Table

Errors are somewhat easier to find in a sequence of hexadecimal digits. The erroneous version of the addition program, in hexadecimal form, becomes:

The mistake is far more obvious.

What do we do with this hexadecimal program? The microprocessor understands only binary instruction codes. If your front panel has a hexadecimal keyboard instead of bit switches, you can key the hexadecimal program directly into memory — the keyboard logic translates the hexadecimal digits into binary numbers. But what if your front panel has only bit switches? You can convert the hexadecimal digits to binary by yourself, but this is a repetitive, tiresome task. People who attempt it make all sorts of petty mistakes, such as looking at the wrong line, dropping a bit, or transposing a bit or a digit. Besides, once we have converted our hexadecimal program we must still place the bits in memory through the switches on the front panel.

#### Hexadecimal Loader

These repetitive, grueling tasks are, however, perfect jobs for a computer. The computer never gets tired or bored and almost never makes mistakes. The idea is to write a program that accepts hexadecimal numbers, converts them into binary numbers, and places them in memory. This is a standard program provided with many microcomputers; it is called a hexadecimal loader.

The hexadecimal loader is a program like any other. It occupies memory space. In some systems, it resides in memory just long enough to load another program; in others, it occupies a reserved, read-only section of memory. Your microcomputer may not have bit switches on its front panel; it may not even have a front panel. This reflects the machine designer's decision that binary programming is not only impossibly tedious but also wholly unnecessary. The hexadecimal loader in your system may be part of a larger program called a monitor, which also provides a number of tools for program debugging and analysis.

A hexadecimal loader certainly does not solve every programming problem. The hexadecimal version of the program is still difficult to read or understand; for example,

it does not distinguish operations from data or addresses, nor does the program listing provide any suggestion as to what the program does. What does 3038 or 31C0 mean? Memorizing a card full of codes is hardly an appetizing proposition. Furthermore, the codes will be entirely different for a different microprocessor and the program will require a large amount of documentation.

#### INSTRUCTION CODE MNEMONICS

An obvious programming improvement is to assign a name to each instruction code. The instruction code name is called a "mnemonic" or memory jogger. The instruction mnemonic should describe, in a minimum number of characters, what the instruction does.

#### **Devising Mnemonics**

In fact, all microprocessor manufacturers provide a set of mnemonics for the microprocessor instruction set (they cannot remember hexadecimal codes either). You do not have to abide by the manufacturer's mnemonics; there is nothing sacred about them. However, they are standard for a given microprocessor, and therefore understood by all users. These are the instruction codes that you will find in manuals, cards, books, articles, and programs. The problem with selecting instruction mnemonics is that not all instructions have "obvious" names. Some instructions do (for example, ADD, AND, OR), others have obvious contractions (such as SUB for subtraction, XOR for exclusive-OR), while still others have neither. The result is such mnemonics as WMP, PCHL, and even SOB. Most manufacturers come up with some reasonable names and some hopeless ones. However, users who devise their own mnemonics rarely do much better.

#### Standard Mnemonics

There is a proposed standard set of assembly language mnemonics. The amount of use that it will receive is uncertain, but it should at least serve as a basis for comparing instruction sets and for selecting mnemonics for future processors.

Along with the instruction mnemonics, the manufacturer will usually assign names to the CPU registers. As with the instruction names, some register names are obvious (such as A for Accumulator) while others may have only historical significance. Again, we will use the manufacturer's suggestions simply to promote standardization.

#### An Assembly Language Program

If we use standard MC68000 instruction and register mnemonics, as defined by Motorola, our MC68000 addition program becomes:

> MOVE ADD \$6000,D0 D0,\$6004 MOVE

The program is still far from obvious, but at least some parts are comprehensible. ADD is a considerable improvement over D078. The MOVE mnemonics do suggest moving data into a register or memory location. We now see that some parts of the program are operations and others are addresses. Such a program is an assembly language program.

#### THE ASSEMBLER PROGRAM

How do we get the assembly language program into the computer? We have to translate it, either into hexadecimal or into binary numbers. You can translate an assembly language program by hand, instruction by instruction. This is called hand assembly.

The following table illustrates the hand assembly of the addition program:

| Instruction Mnemonic | Register/Memory Location | Hexadecimal Equivalent |

|----------------------|--------------------------|------------------------|

| MOVE                 | \$6000,D0                | 30386000               |

| ADD                  | \$6002,D0                | D0786002               |

| MOVE                 | DO,\$6004                | 31C06004               |

As with hexadecimal-to-binary conversion, hand assembly is a rote task which is uninteresting, repetitive, and subject to numerous minor errors. Picking the wrong line, transposing digits, omitting instructions, and misreading the codes are only a few of the mistakes that you may make. Most microprocessors complicate the task even further by having instructions with different lengths. Some instructions are one word long while others may be two or three. Some instructions require data in the second and third words; others require memory addresses, register numbers, or who knows what?

Assembly is another rote task that we can assign to the microcomputer. The microcomputer never makes any mistakes when translating codes; it always knows how many words and what format each instruction requires. The program that does this job is an "assembler." The assembler program translates a user program, or "source" program written with mnemonics, into a machine language program, or "object" program, which the microcomputer can execute. The assembler's input is a source program and its output is an object program.

An assembler is a program, just as the hexadecimal loader is. However, assemblers are more difficult to write, occupy more memory, and require more peripherals and execution time than do hexadecimal loaders. While users may (and often do) write their own loaders, few care to write their own assemblers.

Assemblers have their own rules that you must learn. These include the use of certain markers (such as spaces, commas, semicolons, or colons) in appropriate places, correct spelling, the proper control of information, and perhaps even the correct placement of names and numbers. These rules are usually simple and can be learned quickly.

#### Additional Features of Assemblers

Early assemblers did little more than translate the mnemonic names of instructions and registers into their binary equivalents. However, most assemblers now provide such additional features as:

- Allowing the user to assign names to memory locations, input and output devices, and even sequences of instructions

- · Converting data or addresses from various number systems (for example,

decimal or hexadecimal) to binary and converting characters into their ASCII or EBCDIC binary codes

- Performing some arithmetic as part of the assembly process

- · Telling the loader program where in memory parts of the program or data should be placed

- Allowing the user to assign areas of memory as temporary data storage and to place fixed data in areas of program memory

- · Providing the information required to include standard programs from program libraries, or programs written at some other time, in the current program

- Allowing the user to control the format of the program listing and the input and output devices employed

#### Choosing an Assembler

All of these features, of course, involve additional cost and memory. Microcomputers generally have much simpler assemblers than do larger computers, but the tendency is always for the size of assemblers to increase. You will often have a choice of assemblers. The important criterion is not how many off-beat features the assembler has, but rather how convenient it is to use in normal practice.

#### DISADVANTAGES OF ASSEMBLY LANGUAGE

The assembler, like the hexadecimal loader, does not solve all the problems of programming. One problem is the tremendous gap between the microcomputer instruction set and the tasks which the microcomputer is to perform. Computer instructions tend to do things like add the contents of two registers, shift the contents of the Accumulator one bit, or place a new value in the Program Counter. On the other hand, a user generally wants a microcomputer to do something like print a number, look for and react to a particular command from a teletypewriter, or activate a relay at the proper time. An assembly language programmer must translate such tasks into a sequence of simple computer instructions. The translation can be a difficult, time-consuming job.

Furthermore, if you are programming in assembly language, you must have detailed knowledge of the particular microcomputer that you are using. You must know what registers and instructions the microcomputers has, precisely how the instructions affect the various registers, what addressing methods the computer uses, and a mass of other information. None of this information is relevant to the task which the microcomputer must ultimately perform.

#### Lack of Portability

In addition, assembly language programs are not portable. Each microcomputer has its own assembly language which reflects its own architecture. An assembly language program written for the MC68000 will not run on a 6809, 8080, or Z8000 microprocessor. For example, the addition program written for the Z8000 would be:

LD R0,%6000 ADD R0,%6002 LD %6004,R0

The lack of portability not only means that you will not be able to use your assembly language program on a different microcomputer, but also that you will not be able to use any programs that were not specifically written for the microcomputer you are using. This is a particular drawback for 16-bit microcomputers like the MC68000, since these devices are new and few assembly language programs exist for them. The result, too frequently, is that you are on your own. If you need a program to perform a particular task, you are not likely to find it in the small program libraries that most manufacturers provide. Nor are you likely to find it in an archive, journal article, or someone's old program file. You will probably have to write it yourself.

#### HIGH-LEVEL LANGUAGES

The solution to many of the difficulties associated with assembly language programs is to use, instead, "high-level" or "procedure-oriented" languages. Such languages allow you to describe tasks in forms that are problem-oriented rather than computer-oriented. Each statement in a high-level language performs a recognizable function; it will generally correspond to many assembly language instructions. A program called a compiler translates the high-level language source program into object code or machine language instructions.

#### FORTRAN — A HIGH-LEVEL LANGUAGE

Many different high-level languages exist for different types of tasks. If, for example, you can express what you want the computer to do in algebraic notation, you can write your program in FORTRAN (Formula Translation Language), the oldest and most widely used of the high-level languages. Now, if you want to add two numbers, you just tell the computer:

```

SUM = NUMB1 + NUM2

```

That is a lot simpler (and a lot shorter) than either the equivalent machine language program or the equivalent assembly language program. Other high-level languages include COBOL (for business applications), Pascal (a language designed for structured programming), PL/I (a combination of FORTRAN and COBOL), APL (designed for writing very compact programs), BASIC (popular for smaller microcomputers), and C (a systems-programming language developed at Bell Telephone Laboratories).

#### ADVANTAGES OF HIGH-LEVEL LANGUAGES

Clearly, high-level languages make programs easier and faster to write. A common estimate is that a programmer can write a program about ten times as fast in a high-level language as in assembly language.<sup>2-4</sup> That is just writing the program; it does not include problem definition, program design, debugging, testing, or documen-

tation, all of which become simpler and faster. The high-level language program is, for instance, partly self-documenting. Even if you do not know FORTRAN, you probably could tell what the statement illustrated above does.

#### Machine Independence

High-level languages solve many other problems associated with assembly language programming. The high-level language has its own syntax (usually defined by a national or international standard). The language does not mention the instruction set, registers, or other features of a particular computer. The compiler takes care of all such details. Programmers can concentrate on their own tasks; they do not need a detailed understanding of the underlying CPU architecture — for that matter, they do not need to know anything about the computer they are programming.

#### **Portability**

Programs written in a high-level language are portable — at least, in theory. They will run on any computer that has a standard compiler for that language.

At the same time, all previous programs written in a high-level language for prior computers are available to you when programming a new computer. This can mean thousands of programs in the case of a common language like FORTRAN or BASIC.

#### DISADVANTAGES OF HIGH-LEVEL LANGUAGES

If all the good things we have said about high-level languages are true — if you can write programs faster and make them portable besides - why bother with assembly languages? Who wants to worry about registers, instruction codes, mnemonics, and all that garbage! As usual, there are disadvantages that balance the advantages.

#### Syntax

One obvious problem is that, as with assembly language, you have to learn the "rules" or "syntax" of any high-level language you want to use. A high-level language has a fairly complicated set of rules. You will find that it takes a lot of time just to get a program that is syntactically correct (and even then it probably will not do what you want). A high-level computer language is like a foreign language. If you have talent, you will get used to the rules and be able to turn out programs that the compiler will accept. Still, learning the rules and trying to get the program accepted by the compiler does not contribute directly to doing your job.

Here, for example, are a few rules for some FORTRAN compilers:

- Labels must be numbers placed in the first five card columns

- Statements must start in column 7

- Integer variables must start with the letters I, J, K, L, M, or N

#### Cost of Compilers

Another obvious problem is that you need a compiler to translate programs written in a high-level language into machine language. Compilers are expensive and use a large amount of memory. While most assemblers occupy 2K to 16K bytes of memory (1K = 1024), compilers occupy 4K to 64K bytes. So the amount of overhead involved in using the compiler is rather large.

#### Adapting Tasks to a Language

Furthermore, only some compilers will make the implementation of your task simpler. FORTRAN, for example, is well-suited to problems that can be expressed as algebraic formulas. If, however, your problem is controlling a display terminal, editing a string of characters, or monitoring an alarm system, your problem cannot be easily expressed in FORTRAN. In fact, formulating the solution in FORTRAN may be more awkward and more difficult than formulating it in assembly language. The answer is, of course, to use a more suitable high-level language. Languages specifically designed for tasks such as those mentioned above do exist — they are called system implementation languages. However, these languages are less widely used and standardized than FORTRAN.

#### Inefficiency

High-level languages do not produce very efficient machine language programs. The basic reason for this is that compilation is an automatic process which is riddled with compromises to allow for many ranges of possibilities. The compiler works much like a computerized language translator - sometimes the words are right but the sentence structures are awkward. A simple compiler cannot know when a variable is no longer being used and can be discarded, when a register should be used rather than a memory location, or when variables have simple relationships. The experienced programmer can take advantage of shortcuts to shorten execution time or reduce memory usage. A few compilers (known as optimizing compilers) can also do this, but such compilers are much larger than regular compilers.

#### SUMMARY OF ADVANTAGES AND DISADVANTAGES

#### Advantages of High-Level Languages:

- Easier to learn (and teach to others)

- · More convenient descriptions of tasks

- Less time spent writing programs

- · Easier documentation

- Standard syntax

- · Independence of the structure of a particular computer

- Portability

- Availability of library and other programs

#### Disadvantages of High-Level Languages:

- Special rules

- Extensive hardware and software support required

- Orientation of common languages to mathematical or business problems

- · Inefficient programs

- Difficulty of optimizing code to meet time and memory requirements

- Inability to use special features of a computer conveniently

#### HIGH-LEVEL LANGUAGES FOR MICROPROCESSORS

Microprocessor users will encounter several special difficulties when using high-level languages. Among these are:

- Few high-level languages exist for microprocessors. This is particularly true for processors that are new, relatively unpopular, or intended for simple control applications.

- · Few standard languages are widely available.

- · Compilers usually require a large amount of memory or even a completely different computer.

- Many microprocessor applications are not well-suited to high-level languages.

- Many microprocessor languages produce no object program. That is, they translate the program and run it line by line — this is referred to as interpreting rather than compiling - or they produce an output that requires special systems software (a run-time package) to execute. Either approach may result in programs that execute slowly and use a large amount of memory. BASIC and PASCAL, the most commonly available high-level languages, generally use one of these approaches.

- · Memory costs are often critical in microprocessor applications.

The relatively small number of high-level languages for microcomputers is a result of the short history of microprocessors and their origin in the semiconductor industry, rather than in the computer industry. Among the high-level languages that are most often available are BASIC5, Pascal 6.7, FORTRAN, C8, and the PL/I-type languages such as PL/M9.

Many of the high-level languages that exist do not conform to recognized standards, so the microprocessor user cannot expect to gain much program portability, access to program libraries, or use of previous experience or programs. The main advantages remaining are the reduction in programming effort, easier documentation, and the smaller amount of detailed understanding of the computer architecture that is necessary.

#### Overhead for High-Level Languages

The overhead involved in using a high-level language with microprocessors is considerable. Until very recently, microprocessors have been better suited to control

applications and slow interactive applications than to the character manipulation and language analysis involved in compilation. Therefore, compilers for some microprocessors will not run on a microprocessor-based system. Instead, they require a much larger computer; that is, they are cross-compilers rather than self-compilers. A user must not only bear the expense of the larger computer, but must also transfer the program from the larger computer to the micro.

Some self-compilers are available. These compilers run on the microcomputer for which they produce object code. Unfortunately, they usually require large amounts of memory, plus special supporting hardware and software.

#### **Unsuitability of High-Level Languages**

High-level languages also are not generally well-suited to certain microprocessor applications. Most of the common languages were devised either to help solve scientific problems or to handle large-scale business data processing. Many microprocessor applications do not fall in either of these areas. Instead they involve sending data and control information to output devices and receiving data and status information from input devices. Often the control and status information consists of a few binary digits with very precise hardware-related meanings. If you try to write a typical control program in a high-level language, you may feel like someone who is trying to eat soup with chopsticks. For tasks in such areas as test equipment, terminals, navigation systems, signal processing, and business equipment, the high-level languages work much better than they do in instrumentation, communications, peripherals, and automotive applications.

#### **Application Areas for Language Levels**

Applications better suited to high-level languages are those which require large memories. If, as in a valve controller, electronic game, appliance controller, or small instrument, the cost of a single memory chip is important, then the inefficient memory use of high-level languages is intolerable. If, on the other hand, as in a terminal or test equipment, the system has many thousands of bytes of memory anyway, this inefficiency is not as important. Clearly the size and volume of the product are important factors as well. A large program will greatly increase the advantages of high-level languages. On the other hand, a high-volume application will mean that fixed software development costs are not as important as memory costs that are part of each system.

#### WHICH LEVEL SHOULD YOU USE?

Which language level you use depends on your particular application. Let us briefly note some of the factors which may favor particular levels:

#### Applications for Machine Language:

Virtually no one programs in machine language because it wastes human time and is difficult to document. An assembler costs very little and greatly reduces programming time.

#### Applications for Assembly Language:

- · Short to moderate-sized programs

- Applications where memory cost is a factor

- Real-time control applications

- · Limited data processing

- High-volume applications

- · Applications involving more input/output or control than computation

#### Applications for High-Level Language:

- Long programs

- Low-volume applications

- Applications where the amount of memory required is already very large

- Applications invoing more computation than input/output or control

- · Compatibility with similar applications using larger computers

- · Availability of specific programs in a high-level language which can be used in the application

- · Programs which are expected to undergo many changes

#### Other Considerations

Many other factors are also important, such as the availability of a large computer for use in development, experience with particular languages, and compatibility with other applications.

If hardware will ultimately be the largest cost in your application, or if speed is critical, you should favor assembly language. But be prepared to spend much extra time in software development in exchange for lower memory costs and higher execution speeds. If software will be the largest cost in your application, you should favor a highlevel language. But be prepared to spend the extra money required for the supporting hardware and software.

Of course, no one except some theorists will object if you use both assembly and high-level languages. You can write the program originally in a high-level language and then patch some sections in assembly language. 10, 11 However, most users prefer not to do this because it can create havoc in debugging, testing, and documentation.

#### **FUTURE TRENDS IN LANGUAGE LEVELS**

We expect the future will favor high-level languages for the following reasons:

- Programs always add extra features and grow larger

- · Hardware and memory are becoming less expensive

- Software and programmers are becoming more expensive

- · Memory chips are becoming available in larger sizes, at lower "per bit" cost, so actual savings in chips are less likely

- More suitable and more efficient high-level languages are being developed

- More compilers are becoming available

- · More standardization of high-level languages will occur

Assembly language programming of microprocessors will not be a dying art any more than it is for large computers. But longer programs, cheaper memory, and more expensive programmers will make software costs a larger part of most applications. The edge in many applications will therefore go to high-level languages.

#### WHY THIS BOOK?

If the future favors high-level languages, why have a book on assembly language programming? The reasons are:

- 1. Most industrial microcomputer users program in assembly language (almost two thirds, according to a recent survey).

- 2. Many microcomputer users will continue to program in assembly language since they need the detailed control that it provides.

- No suitable high-level language has yet become widely available or standardized.

- 4. Many applications require the efficiency of assembly language.

- 5. An understanding of assembly language can help in evaluating high-level languages.

- 6. Almost all microcomputer programmers ultimately find that they need some knowledge of assembly language, most often to debug programs, write I/O routines, speed up or shorten critical sections of programs written in high-level languages, utilize or modify operating system functions, and understand other people's programs.

The rest of this book will deal exclusively with assemblers and assembly language programming. However, we do want readers to know that assembly language is not the only alternative. You should watch for new developments that may significantly reduce programming costs if such costs are a major factor in your application.

#### REFERENCES

- 1. W. P. Fischer, "Microprocessor Assembly Language Draft Standard," *Computer*, December 1979, pp. 96-109.

- 2. M. H. Halstead, Elements of Software Science, American Elsevier, New York, 1977.

- 3. L. H. Putnam and A. Fitzsimmons, "Estimating Software Costs," *Datamation*, September 1979, pp. 189-98.

- 4. M. Phister, Jr., *Data Processing Technology and Economics*, Santa Monica Publishing Co., Santa Monica, Calif., 1976. Also available from Digital Press, Educational Services, Digital Equipment Corp., Bedford, Mass.

- 5. Albrecht, Finkel, and Brown, BASIC for Home Computers, Wiley, New York, 1978.

- 6. G. M. Schneider et al., An Introduction to Programming and Problem Solving with PASCAL, Wiley, New York, 1978.

- 7. K. L. Bowles, Microcomputer Problem Solving Using PASCAL, Springer-Verlag, New York, 1977.

- 8. B. W. Kernighan and D.M. Ritchie, The C Programming Language, Prentice-Hall, Englewood Cliffs, N. J., 1978.

- 9. D. D. McCracken, A Guide to PL/M Programming for Microcomputer Applications, Addison-Wesley, Reading, Mass., 1978.

- 10. P. Caudill, "Using Assembly Coding to Optimize High-Level Language Programs," Electronics, February 1, 1979, pp. 121-24.

- 11. D. B. Wecker et al., "High Level Design Language Develops Low Level Microprocessor-Independent Software," Computer Design, June 1979, pp. 140-49.

# 2 Assemblers

This chapter discusses the functions performed by assemblers, beginning with features common to most assemblers and proceeding through more elaborate capabilities such as macros and conditional assembly. You may wish to skim this chapter for the present and return to it when you feel more comfortable with the material.

#### FEATURES OF ASSEMBLERS

As we mentioned previously, today's assemblers do much more than translate assembly language mnemonics into binary codes. But we will describe how an assembler handles the translation of mnemonics before describing additional assembler features. Finally we will explain how assemblers are used.

#### **ASSEMBLY LANGUAGE FIELDS**

Assembly language instructions (or "statements") are divided into a number of "fields," as shown in Table 2-1.

The operation code field is the only field which can never be empty; it always contains either an instruction mnemonic or a directive to the assembler, sometimes called a "pseudo-instruction," "pseudo-operation," or "pseudo-op."

The operand or address field may contain an address or data, or it may be blank.

| Label<br>Field | Operation Code<br>or Mnemonic<br>Field | Operand or<br>Address<br>Field | Comment Field                      |

|----------------|----------------------------------------|--------------------------------|------------------------------------|

| VALUE1:        | DC.W                                   | \$201E                         | FIRST VALUE                        |

| VALUE2:        | DC.W                                   | \$0774                         | SECOND VALUE                       |

| RESULT:        | DS.W                                   | 1                              | 16-BIT STORAGE FOR ADDITION RESULT |

| •              |                                        |                                |                                    |

| •              |                                        |                                |                                    |

| •              |                                        |                                |                                    |

| START          | MOVE                                   | VALUE1,D0                      | GET FIRST VALUE                    |

|                | ADD                                    | VALUE2,D0                      | ADD SECOND VALUE TO FIRST VALUE    |

|                | MOVE                                   | DO,RESULT                      | STORE RESULT OF ADDITION           |

| NEXT:          | ?                                      | ?                              | NEXT INSTRUCTION                   |

Table 2-1. The Fields of an Assembly Language Instruction

The comment and label fields are optional. A programmer will assign a label to a statement or add a comment as a personal convenience: namely, to make the program easier to read and use.

Of course, the assembler must have some way of telling where one field ends and another begins. Assemblers often require that each field start in a specific column. This is a "fixed format." However, fixed formats are inconvenient when the input medium is paper tape; fixed formats are also a nuisance to programmers. The alternative is a "free format" where the fields may appear anywhere on the line.

#### **Delimiters**

If the assembler cannot use the position on the line to tell the fields apart, it must use something else. Most assemblers use a special symbol or "delimiter" at the beginning or end of each field. The most common delimiter is the space character. Commas, periods, semicolons, colons, slashes, question marks, and other characters which would not otherwise be used in assembly language programs also may serve as delimiters. Table 2-2 lists standard MC68000 assembler delimiters.

You will have to exercise a little care with delimiters. Some assemblers are fussy about extra spaces or the appearance of delimiters in comments or labels. A well-written assembler will handle these minor problems, but many assemblers are not well-written. Our recommendation is simple: avoid potential problems if you can. The following rules will help:

- Do not use extra spaces, in particular, do not put spaces after commas that separate operands.

- Do not use delimiter characters in names or labels.

- Include standard delimiters even if your assembler does not require them. Then it will be more likely that your programs are in correct form for another assembler.

Table 2-2. Standard MC68000 Assembler Delimiters

'space' Between label and operation code, between operation code and address, and before an entry in the comment field

comma Between operands in the address field asterisk Before an entire line of comment

#### Labels

The label field is the first field in an assembly language instruction; it may be blank. If a label is present, the assembler defines the label as equivalent to the address into which the first byte of the object code generated for that instruction will be loaded. You may subsequently use the label as an address or as data in another instruction's address field. The assembler will replace the label with the assigned value when creating an object program.

Motorola's assembler uses two different delimiters to terminate label fields. If the label starts at the beginning of a line, as we discussed in the preceding paragraph, then a space will terminate the label field. However, this assembler also allows you to have the label start anywhere along a line, in which case you must use a colon (:) as the delimiter to terminate the label field.

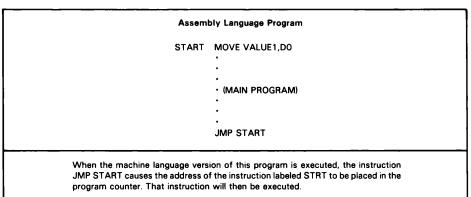

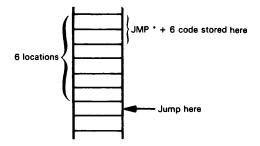

Labels are most frequently used in Jump, Branch or TRAP instructions. These instructions place a new value in the program counter and so alter the normal sequential execution of instructions. JMP  $150_{16}$  means "place the value  $150_{16}$  in the program counter." The next instruction to be executed will be the one in memory location  $150_{16}$ . The instruction JMP START means "place the value assigned to the label START in the program counter." The next instruction to be executed will be the on at the address corresponding to the label START. Table 2-3 contains an example.

#### Why use a label? Here are some reasons:

- · A label makes a program location easier to find and remember.

- The label can easily be moved, if required, to change or correct a program. The

assembler will automatically change all instructions that use the label when the

program is reassembled.

- The assembler or loader can relocate the whole program by adding a constant (a "relocation constant") to each address in which a label was used. Thus we can move the program to allow for the insertion of other programs or simply to rearrange memory.

- The program is easier to use as a library program; that is, it is easier for someone else to take your program and add it to some totally different program.

- You do not have to figure out memory addresses. Figuring out memory addresses is particularly difficult with microprocessors which have instructions that vary in length.

You should assign a label to any instruction that you might want to refer to later.

The next question is how to choose a label. The assembler often places some

Table 2-3. Assigning and Using a Label

restrictions on the number of characters (usually 5 or 6), the leading character (often must be a letter), and the trailing characters (often must be letters, numbers, or one of a few special characters). Beyond these restrictions, the choice is up to you.

Our own preference is to use labels that suggest their purpose, i.e., mnemonic labels. Typical examples are ADDW in a routine that adds one word into a sum, SRCHETX in a routine that searches for the ASCII character ETX, or NKEYS for a location in data memory that contains the number of key entries. Meaningful labels are easier to remember and contribute to program documentation. Some programmers use a standard format for labels, such as starting with L0000. These labels are self-sequencing (you can skip a few numbers to permit insertions), but they do not help document the program.

# Some label selection rules will keep you out of trouble. We recommend the following:

- Do not use labels that are the same as operation codes or other mnemonics.

Most assemblers will not allow this usage; others will, but it is confusing.

- Do not use labels that are longer than the assembler recognizes. Assemblers have various rules, and often ignore some of the characters at the end of a long label

- Avoid special characters (non-alphabetic and non-numeric) and lower-case letters. Some assemblers will not permit them; others allow only certain ones.

The simplest practice is to stick to capital letters and numbers.

- · Start each label with a letter. Such labels are always acceptable.

- Do not use labels that could be confused with each other. Avoid the letters I,

O, and Z and the numbers 0, 1, and 2. Also avoid things like XXXX and

XXXXX. There's no sense in tempting fate and Murphy's Law.

- When you are not sure if a label is legal, do not use it. You will not get any real benefit from discovering exactly what the assembler will accept.

These are recommendations, not rules. You do not have to follow them but don't blame us if you waste time on unnecessary problems.

# ASSEMBLER OPERATION CODES (MNEMONICS)

One main task of the assembler is the translation of mnemonic operation codes into their binary equivalents. The assembler performs this task using a fixed table much as you would if you were doing the assembly by hand.

The assembler must, however, do more than just translate the operation codes. It must also somehow determine how many operands the instruction requires and what type they are. This may be rather complex — some instructions (like a Stop) have no operands, others (like a Jump instruction) have one, while still others (like a transfer between registers or a multiple-bit shift) require two. Some instructions may even allow alternatives; for example, some computers have instructions (like Shift or Clear) which can either apply to a register in the CPU or to a memory location. We will not discuss how the assembler makes these distinctions; we will just note that it must do so.

# ASSEMBLER DIRECTIVES

Some assembly language instructions are not directly translated into machine language instructions. These instructions are directives to the assembler; they assign the program to certain areas in memory, define symbols, designate areas of memory for data storage, place tables or other fixed data in memory, allow references to other programs, and perform minor housekeeping functions.

To use these assembler directives or pseudo-operations a programmer places the directive's mnemonic in the operation code field, and, if the specified directive requires it, an address or data in the address field.

The most common directives are:

DATA

EQUATE or DEFINE

ORIGIN

RESERVE

Linking directives (used to connect separate programs) are:

ENTRY EXTERNAL

Different assemblers use different names for those operations but their functions are the same. Housekeeping directives include:

LIST NAME PAGE SPACE TITLE PUNCH

**END**

We will discuss these pseudo-operations briefly, although their functions are usually obvious.

# The DATA Directive

The DATA or DEFINE CONSTANT directive allows the programmer to enter fixed data into program memory. This data may include:

- · Lookup tables

- Code conversion tables

- Messages

- · Synchronization patterns

- · Thresholds

- Names

- Coefficients for equations

- Commands

- · Conversion factors

- · Weighting factors

- · Characteristic times or frequencies

- · Subroutine addresses

- · Key identifications

- · Test patterns

- · Character generation patterns

- · Identification patterns

- Tax tables

- · Standard forms

- Masking patterns

- · State transition tables

The DATA directive treats the data as a permanent part of the program.

The format of a DATA directive is usually quite simple. An instruction like:

```

DZCON DATA 12

```

will place the number 12 in the next available memory location and assign that location the name DZCON. Every DATA directive usually has a label, unless it is one of a series. The data and label may take any form that the assembler permits.

Most assemblers allow more elaborate DATA directives that handle a large amount of data at one time, for example:

```

EMESS DATA 'ERROR'

SQRS DATA 1,4,9,16,25

```

A single directive may fill many bytes of program memory, limited perhaps by the length of a line or by the restrictions of a particular assembler. Of course, you can always overcome any restrictions by following one DATA directive with another:

```

MESSG DATA 'NOW IS THE'

DATA 'TIME FOR ALL'

DATA 'GOOD MEN'

DATA 'TO COME TO THE'

DATA 'AID OF THEIR'

DATA 'COUNTRY'

```

Microprocessor assemblers typically have some variations of standard DATA directives. DEFINE BYTE or FORM CONSTANT BYTE handles 8-bit numbers; DEFINE WORD or FORM CONSTANT WORD handles 16-bit numbers or addresses. Other special directives may handle character-coded data.

# The EQUATE (or DEFINE) Directive

The EQUATE directive allows the programmer to equate names with addresses or data. This pseudo-operation is almost always given the mnemonic EQU or =. The names may refer to device addresses, numeric data, starting addresses, fixed addresses, etc.

The EQUATE directive assigns the numeric value in its operand field to the label in its label field. Here are two examples:

Most assemblers will allow you to define one label in terms of another, for example:

The label in the operand field must, of course, have been previously defined. Often, the operand field may contain more complex expressions, as we shall see later. Double name assignments (two names for the same data or address) may be useful in patching together programs that use different names for the same variable (or different spellings of what was supposed to be the same name).

Note that an EQU directive does not cause the assembler to place anything in memory. The assembler simply enters an additional name into a table (called a "symbol table") which the assembler maintains.

When do you use a name? The answer is: whenever you have a parameter that you might want to change or that has some meaning besides its ordinary numeric value. We typically assign names to time constants, device addresses, masking patterns, conversion factors, and the like. A name like DELAY, TTY, KBD, KROW, or OPEN not only makes the parameter easier to change, but it also adds to program documentation. We also assign names to memory locations that have special purposes; they may hold data, mark the start of the program, or be available for intermediate storage.

What name do you use? The best rules are much the same as in the case of labels, except that here meaningful names really count. Why not call the teletypewriter TTY instead of X15, a bit time delay BTIME or BTDLY rather than WW, the number of the "GO" key on a keyboard GOKEY rather than HORSE? This advice seems straightforward, but a surprising number of programmers do not follow it.

Where do you place the EQUATE directives? The best place is at the start of the program, under appropriate comment headings such as I/O ADDRESSES, TEM-PORARY STORAGE, TIME CONSTANTS, or PROGRAM LOCATIONS. This makes the definitions easy to find if you want to change them. Furthermore, another user will be able to look up all the definitions in one centralized place. Clearly this practice improves documentation and makes the program easier to use.

Definitions used only in a specific subroutine should appear at the start of the subroutine.

# The ORIGIN Directive

The ORIGIN directive (almost always abbreviated ORG) allows the programmer to specify the memory locations where programs, subroutines, or data will reside. Programs and data may be located in different areas of memory depending on the memory configuration. Startup routines, interrupt service routines, and other required programs may be scattered around memory at fixed or convenient addresses.

The assembler maintains a location counter (comparable to the computer's program counter) which contains the location in memory of the instruction or data item being processed. An ORG directive causes the assembler to place a new value in the location counter, much as a Jump instruction causes the CPU to place a new value in the program counter. The output from the assembler must not only contain instructions and data, but must also indicate to the loader program where in memory it should place the instructions and data.

Microprocessor programs often contain several ORIGIN statements for the following purposes:

- Reset (startup) address

- · Interrupt service addresses

- Trap (software interrupt) addresses

- RAM storage

- Stack

- Main program

- Subroutines

- Memory addresses used for input/output devices or special functions

Still other ORIGIN statements may allow room for later insertions, place tables or data in memory, or assign vacant memory space for data buffers. Program and data memory in microcomputers may occupy widely separate addresses to simplify the hardware.

### Typical ORIGIN statements are:

| ORG | RESET |

|-----|-------|

| ORG | 1000  |

| ORG | INT3  |

Most assemblers assume an origin of zero if the programmer does not put an ORG statement at the start of the program. The convenience is slight; we recommend the inclusion of an ORG statement to avoid confusion.

### The RESERVE Directive

The RESERVE or DEFINE STORAGE directive allows the programmer to allocate memory for various purposes such as data tables, temporary storage, indirect addresses, a Stack, etc.

Using the RESERVE directive, you assign a name to the memory area and declare the number of locations to be assigned. Here are some examples:

| NOKEY | RESERVE | 1     |

|-------|---------|-------|

| TEMP  | RESERVE | 50    |

| VOLTG | RESERVE | 80    |

| BUED  | DESERVE | 1.0 ( |

You can use the RESERVE directive to reserve memory locations in program memory or in data memory; however, the RESERVE directive will normally be used in data memory.

In reality, all the RESERVE directive does is increase the assembler's location counter by the amount declared in the operand field. The assembler does not actually produce any object code.

Note the following features of RESERVE:

1. The label of the RESERVE directive is assigned the value of the first address reserved. For example, the pseudo-operation:

TEMP RESERVE 20

reserves 20 words of memory and assigns the name TEMP to the address of the first byte.

- You must specify the number of locations to be reserved. There is no default case.

- 3. No data is placed in the reserved locations. Any data that, by chance, may be in these locations will be left there.

Some assemblers allow the programmer to specify initial values for the RESERVE area in memory. We strongly recommend that you do not use this feature; it assumes that the program (along with the initial values) will be loaded from an external device (e.g., paper tape or floppy disk) each time it is run. Microprocessor programs, on the other hand, often reside in non-volatile read-only-memory (ROM) and start when power comes on. The data memory (often referred to as random recess memory or 'RAM') in such situations does not retain its contents, nor is it reloaded. Therefore, always include instruction sequences to initialize RAM in your program; this will insure that initialization occurs every time the program is executed and not just during load time.

# **Linking Directives**

We often want statements in one program or subroutine to use names that are defined in a different assembly. Such uses are called "external references"; a special linking program is necessary to actually fill in the values and determine if any names are undefined or doubly defined.

The directive EXTERNAL, usually abbreviated EXT or XREF, signifies that the name is defined elsewhere.

The directive ENTRY, usually abbreviated ENT or XDEF, signifies that the name is available for use elsewhere; that is, it is defined in this program.

The precise way in which linking directives are implemented varies greatly from assembler to assembler. We will not refer to these directives again, but they are very important in actual applications.

# **Output Control Directives**

There are various assembler directives that affect the operation of the assem-

# bler and its program listing rather than the object program itself. Common directives include:

- END, which marks the end of the assembly language source program.

- LIST, which tells the Assembler to print the source program. Some assemblers allow such variations as NO LIST or LIST SYMBOL TABLE.

- NAME or TITLE, which prints a name at the top of each page of the listing.

- PAGE or SPACE, which skips to the next page or next line, respectively, and improves the appearance of the listing, making it easier to read.

- PUNCH, which transfers subsequent object code to the paper tape punch. This

pseudo-operation may in some cases be the default option and therefore

unnecessary.

### When to Use Labels

Users often wonder if or when they can assign a label to an assembler directive. These are our recommendations:

- All EQUATE directives must have labels; they are useless otherwise, since the purpose of an EQUATE is to define its label.

- DATA and RESERVE directives usually have labels. The label identifies the first memory location used or assigned.

- Other directives should not have labels. Some assemblers allow such labels, but we recommend against their use because there is no standard way to interpret them.

### **OPERANDS AND ADDRESSES**

Most assemblers allow the programmer a lot of freedom in describing the contents of the operand or address field. But remember that the assembler has built-in names for registers and instructions and may have other built-in names. We will now describe some common options for the operand field.

### **Decimal Numbers**

Most assemblers assume all numbers to be decimal unless they are marked otherwise. So:

ADD 100

means "add the contents of memory location  $100_{10}$  to the contents of the Accumulator."

# **Other Number Systems**

Most assemblers will also accept binary, octal, or hexadecimal entries. But you must identify these number systems in some way: for example, by preceding or

following the number with an identifying character or letter. Here are some common identifiers:

- B or % for binary

- O, @, Q, or C for octal (the letter O should be avoided because of the confusion with zero)

- H or \$ for hexadecimal (or standard BCD)

- · D for decimal; or no identifiers if it is the default case.

Assemblers often require hexadecimal numbers to start with a digit (for example, 0A36 instead of A36) in order to distinguish between numbers and names or labels. It is good practice to enter numbers in the base in which their meaning is the clearest: that is, decimal constants in decimal; addresses and BCD numbers in hexadecimal; masking patterns or bit outputs in binary if they are short, and in hexadecimal if they are long.

### Names

Names can appear in the operand field; they will be treated as the data that they represent. Remember, however, that there is a difference between operands and addresses. In a MC68000 assembly language program the sequence:

will add the contents of memory location 5 (not necessarily the number 5) to the contents of data register D0. A sequence which adds in the number 5 itself would be

The symbol # tells the assembler that the number represented by the name FIVE is the value of the operand FIVE, itself, instead of the contents of the memory location addressed by FIVE.

### The Location Counter

You can use the current value of the location counter, which is usually referred to as \* or \$. This is useful mainly in Jump instructions; for example:

causes a Jump to the memory location 6 bytes beyond the byte that contains the first byte of the JMP instruction.

One reason to use this technique is to reduce the number of symbols in an assembly language program. This may be necessary if the assembler can handle only a limited number of symbols. Reducing the number of symbols may also decrease assembly time. Such benefits are almost negligible, however, unless your program is extremely large or your assembler rather primitive.

Most microprocessors have many two and three-byte instructions. Thus you will have difficulty determining exactly how far apart two assembly language statements are. Using offsets from the location counter therefore frequently results in errors that you can avoid if you use labels. Therefore, in almost every case, you should not use the location counter symbol.

### Character Codes

Most assemblers allow text to be entered as ASCII strings. Such strings may be surrounded either with single or double quotation marks; some assemblers may also use a beginning or ending symbol such as A or C. A few assemblers also permit EBCDIC strings as used by IBM machines.

We recommend that you use character strings for all text. It improves the clarity and readability of the program.

# **Arithmetic and Logical Expressions**

Assemblers permit combinations of the data forms described above, connected by arithmetic, logical, or special operators. These combinations are called expressions. Almost all assemblers allow simple arithmetic expressions such as START + 1. Some assemblers also permit multiplication, division, logical functions, shifts, etc. Note that the assembler evaluates expressions at assembly time; if a symbol appears in an expression, the address is used (i.e., the location counter or EQUATE value).

Assemblers vary in what expressions they accept and how they interpret them. Complex expressions make a program difficult to read and understand.

### **General Recommendations**

We have made some recommendations during this section but will repeat them and add others here. In general, the user should strive for clarity and simplicity. There is no payoff for being an expert in the intricacies of an assembler or in having the most complex expression on the block. We suggest the following approach:

- · Use the clearest number system or character code for data.

- Masks and BCD numbers in decimal, ASCII characters in octal, or ordinary numerical constants in hexadecimal serve no purpose and therefore should not be used.

- Remember to distinguish data from addresses.

- Don't use offsets from the location counter.

- Keep expressions simple and obvious. Don't rely on obscure features of the assembler

# **CONDITIONAL ASSEMBLY**

Some assemblers allow you to include or exclude parts of the source program, depending on conditions existing at assembly time. This is called conditional assembly; it gives the assembler some of the flexibility of a compiler. Most microcomputer assemblers have limited capabilities for conditional assembly. A typical form is:

```

IF COND

.

. (CONDITIONAL PROGRAM)

.

ENDIF

```

If the expression COND is true at assembly time, the instructions between IF and ENDIF (two pseudo-operations) are included in the program.

## Typical uses of conditional assembly are:

- · To include or exclude extra variables

- · To place diagnostics or special conditions in test runs

- · To allow data of various bit lengths

Unfortunately, conditional assembly tends to clutter programs and make them difficult to read. Use conditional assembly only if it is necessary.

| Assembl                               | er Input                                                 | Assembler Output                             |                                             |                                             |

|---------------------------------------|----------------------------------------------------------|----------------------------------------------|---------------------------------------------|---------------------------------------------|

| Source P                              | rogram                                                   | Object Code                                  | Corresponding Mnemonic                      |                                             |

| (Macro de                             | finition)                                                |                                              |                                             |                                             |

| MACRO<br>ADDQ<br>LSL.L<br>BPL<br>ENDM | #1,D0<br>#1,D1<br>%-6<br>(End of<br>macro<br>definition) |                                              |                                             |                                             |

| LSL.B<br>ADDX                         | #1,D1<br>D0,D0                                           | E309<br>D140<br>4A41<br>66F8                 | LSL.B<br>ADDX<br>TST<br>BNE<br>MAC1         | #1,D1<br>D0,D0<br>D1<br>PARITY LOOP         |

| TST<br>BNE<br>MAC1                    | D1<br>PARITY LOOP                                        | 5240<br>E389<br>6AFA                         | ADDQ<br>LSL.L<br>BPL                        | #1,D0<br>#1,D1<br>%-6                       |

| BTST<br>BNE<br>MAC1                   | #0,D0<br>NEXT CHAR                                       | 80000099<br>00000080<br>5240<br>E389<br>6AFA | MAC1<br>BTST<br>BNE<br>ADDQ<br>LSL.L<br>BPL | #0,D0<br>NEXT CHAR<br>#1,D0<br>#1,D1<br>%-6 |

| BSET                                  | #7,-(A0)                                                 | 08E80007FFFF                                 | BSET #                                      | 7,-1(A0)                                    |

Figure 2-1. Expansion of a Macro by the Assembler

# **MACROS**

You will often find that particular sequences of instructions occur many times in a source program. Repeated instruction sequences may reflect the needs of your program logic, or they may be compensating for deficiencies in your microprocessor's instruction set. You can avoid repeatedly writing out the same instruction sequence by using a "macro."

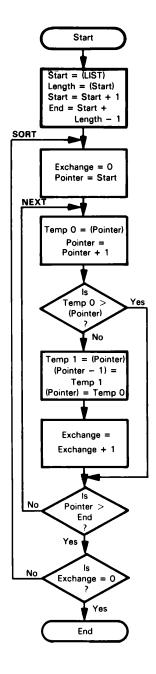

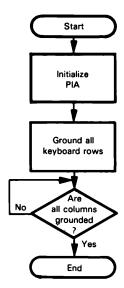

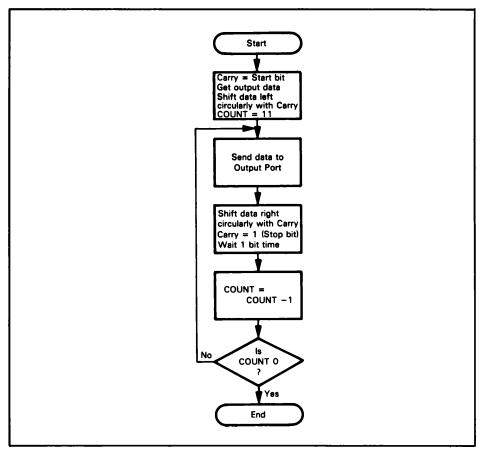

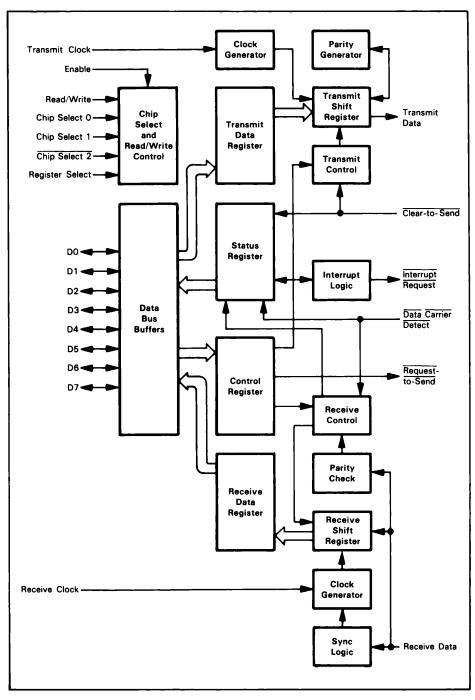

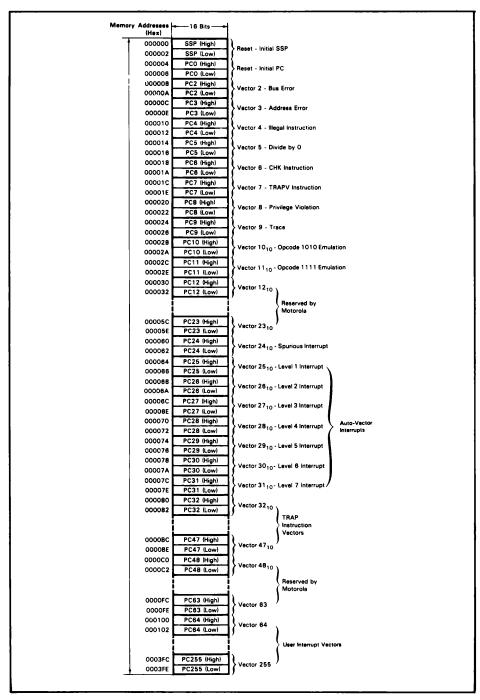

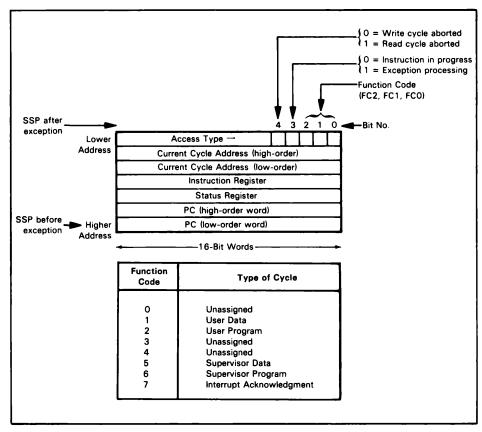

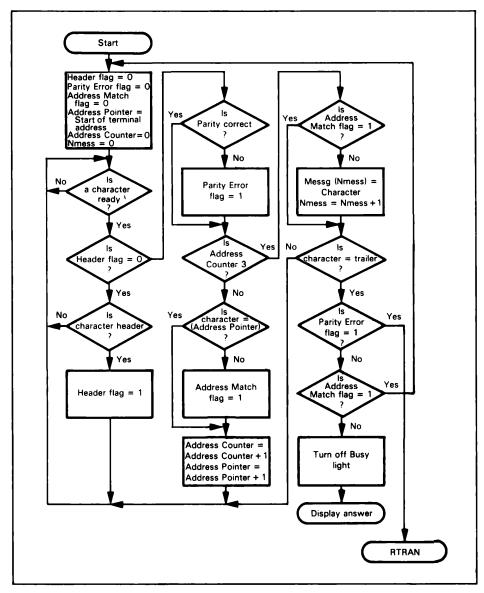

Macros allow you to assign a name to an instruction sequence. You then use the macro name in your source program instead of the repeated instruction sequence. The assembler will replace the macro name with the appropriate sequence of instructions. The shaded parts of Figure 2-1 illustrate the assembler's treatment of a macro in an example program. Do not bother trying to figure out what the program or the instructions do; just observe that the assembler expands the macro MAC1 into the defined sequence.